半导体元件及其形成方法与流程

1.本公开涉及半导体元件及其形成方法。

背景技术:

2.半导体集成电路(integrated circuit,ic)行业经历了指数增长。体集成电路材料和设计的技术进步已经产生了几代体集成电路,其中每一代都比上一代具有更小、更复杂的电路。在体集成电路发展的过程中,功能密度(即,每个晶片区域的互连装置的数量)通常增加了,而几何尺寸(即,可以使用制程产生的最小元件(或线宽))减小了。这种按比例缩小的过程通常透过提高生产效率和降低相关成本来提供益处。

技术实现要素:

3.依据本公开的部分实施例,提供一种半导体元件,包含:基材、第一半导体鳍片、浅沟槽隔离结构、源极/漏极结构、第一埋入式电源线、第一基材通孔、第二基材通孔。基材具有从基材的前表面延伸到基材中的井区。第一半导体鳍片在井区上。浅沟槽隔离结构横向地围绕第一半导体鳍片的下部。源极/漏极结构在第一半导体鳍片上。第一埋入式电源线电耦合到第一半导体鳍片上的源极/漏极结构,第一埋入式电源线的长度沿着第一半导体鳍片的长度方向延伸,并且第一埋入式电源线的高度从浅沟槽隔离结构内延伸到井区内。第一基材通孔从基材的背表面延伸到第一埋入式电源线。第二基材通孔从基材的背表面延伸到井区。

4.依据本公开的部分实施例,提供一种半导体装置,包含:基材、第一半导体鳍片、第二半导体鳍片、第一基材通孔、第二基材通孔。基材具有p型井区和与p型井区相邻的n型井区,其中p型井区和n型井区从基材的前表面延伸到基材中。第一半导体鳍片设置在p型井区上。第二半导体鳍片设置在n型井区上。第一基材通孔从基材的背表面延伸到p型井区。第二基材通孔从基材的背表面延伸到n型井区。

5.依据本公开的部分实施例,提供一种形成半导体装置的方法,包含:形成从基材的前表面延伸到基材中的井区;形成半导体鳍片在井区上;形成源极/漏极结构在半导体鳍片上;刻蚀沟槽于井区中;形成埋入式电源线在井区的沟槽中;形成源极/漏极接触以将源极/漏极结构电连接到埋入式电源线;执行蚀刻制程于基材的背表面上,以形成暴露出埋入式电源线和井区的多个开口;以及使用导电材料填充这些开口以形成多个硅通孔。

附图说明

6.当结合附图阅读时,根据以下详细描述可以最好地理解本公开的各方面。应理解,根据行业中的标准实践,各种特征未按比例绘制。实际上,为了清楚起见,可以任意地增加或减小各种特征的尺寸。

7.图1a和图1b是根据本公开的部分实施例的用于形成半导体元件的方法m1的流程图;

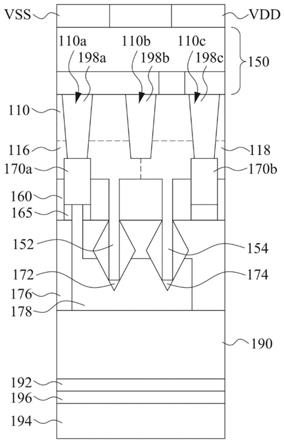

8.图2至图13、图14a、图15至图17、图18a、图19、图20a和图20b绘示根据本公开的部分实施例的用于在各个阶段制造半导体元件的方法;

9.图14b绘示根据本公开的部分其他实施例的处于对应于图14a的阶段的另一晶片;

10.图18b绘示根据本公开的部分其他实施例的处于对应于图18a的阶段的另一晶片;

11.图21绘示根据本公开的部分其他实施例的晶片的俯视图;

12.图22绘示根据本公开的部分其他实施例的晶片的俯视图;

13.图23绘示根据本公开的部分其他实施例的晶片的俯视图;

14.图24是根据本公开的部分实施例的用于形成半导体元件的方法m2的流程图;

15.图25至图36绘示根据本公开的部分实施例的用于在各个阶段制造半导体元件的方法;

16.图37至图45、图46a和图47至图50绘示根据本公开的部分实施例的用于在各个阶段制造半导体元件的方法;

17.图46b绘示根据本公开的部分其他实施例的处于对应于图46a的阶段的另一半导体元件;

18.图51至图56绘示根据本公开的部分实施例的用于在各个阶段制造半导体元件的方法;

19.图57至图63绘示根据本公开的部分实施例的用于在各个阶段制造半导体元件的方法。

20.【符号说明】

21.110:基材

22.110a:基材通孔开口

23.110b:基材通孔开口

24.110c:基材通孔开口

25.110d:背表面

26.110e:基材通孔开口

27.110f:基材通孔开口

28.110g:基材通孔开口

29.116:井区

30.118:井区

31.130:遮罩层

32.150:后段制程型互连堆叠

33.152:半导体鳍片

34.154:半导体鳍片

35.160:隔离介电质

36.160a:沟槽

37.160b:沟槽

38.162:材料

39.164:材料

40.165:隔离介电质

41.170:导电材料

42.170a:埋入式电源轨

43.170b:埋入式电源轨

44.170c:背面端部

45.170d:背面端部

46.172:源极/漏极特征

47.174:源极/漏极特征

48.176:层间介电层

49.176a:通孔开口

50.176b:沟槽

51.176c:通孔开口

52.178:互连

53.178a:互连

54.178b:互连

55.179:互连

56.182:栅极结构

57.184:栅极结构

58.186:栅极间隔物

59.188:栅极

60.190:后段制程堆叠

61.192:结合层

62.194:载体基材

63.196:结合层

64.198a:基材通孔

65.198b:基材通孔

66.198c:基材通孔

67.210:基材

68.210a:基材通孔开口

69.210b:基材通孔开口

70.210d:背表面

71.216:p型井区

72.218:n型井区

73.230:遮罩层

74.250:后段制程型互连堆叠

75.252:半导体鳍片

76.253:半导体鳍片

77.254:半导体鳍片

78.255:半导体鳍片

79.260:隔离介电质

80.263:材料

81.264:材料

82.273:源极/漏极特征

83.274:源极/漏极特征

84.276:层间介电层

85.290:后段制程堆叠

86.292:结合层

87.294:载体基材

88.296:结合层

89.298a:基材通孔

90.298b:基材通孔

91.310:基材

92.310a:基材通孔开口

93.310b:基材通孔开口

94.310c:基材通孔开口

95.310d:基材通孔开口

96.310e:背表面

97.316:p型井区

98.318:n型井区

99.330:遮罩层

100.350:后段制程型互连堆叠

101.352:半导体鳍片

102.353:半导体鳍片

103.354:半导体鳍片

104.355:半导体鳍片

105.356:半导体鳍片

106.357:半导体鳍片

107.358:半导体鳍片

108.360:隔离介电质

109.360a:沟槽

110.360b:沟槽

111.363:材料

112.364:材料

113.365:隔离介电质

114.366:材料

115.367:材料

116.369:遮罩层

117.370:导电材料

118.370a:埋入式电源轨

119.370b:埋入式电源轨

120.371b:互连

121.371c:互连

122.372:层间介电层

123.372a:沟槽

124.372b:沟槽

125.372c:沟槽

126.373:源极/漏极特征

127.374:源极/漏极特征

128.376:源极/漏极特征

129.377:源极/漏极特征

130.378:导电通孔

131.379a:导电接触

132.379b:导电接触

133.390:后段制程堆叠

134.392:结合层

135.394:载体基材

136.396:结合层

137.398a:基材通孔

138.398b:基材通孔

139.398c:基材通孔

140.398d:基材通孔

141.410:基材

142.410a:基材通孔开口

143.410b:基材通孔开口

144.410c:基材通孔开口

145.410e:背表面

146.416:p型井区

147.418:n型井区

148.450:后段制程型互连堆叠

149.452:半导体鳍片

150.453:半导体鳍片

151.454:半导体鳍片

152.455:半导体鳍片

153.456:半导体鳍片

154.457:半导体鳍片

155.458:半导体鳍片

156.460:隔离介电质

157.467:介电质材料

158.468:光阻层

159.469:遮罩层

160.473:源极/漏极特征

161.474:源极/漏极特征

162.476:源极/漏极特征

163.477:源极/漏极特征

164.490:后段制程堆叠

165.492:结合层

166.494:载体基材

167.496:结合层

168.498a:基材通孔

169.498b:基材通孔

170.498c:基材通孔

171.510:基材

172.510a:基材通孔开口

173.510b:基材通孔开口

174.510e:背表面

175.516:p型井区

176.518:n型井区

177.526:掺杂层

178.528:掺杂层

179.536:硅化物层

180.538:硅化物层

181.550:后段制程型互连堆叠

182.552:半导体鳍片

183.553:半导体鳍片

184.554:半导体鳍片

185.555:半导体鳍片

186.560:隔离介电质

187.567:介电质材料

188.568:光阻层

189.569:遮罩层

190.573:源极/漏极特征

191.574:源极/漏极特征

192.576:层间介电层

193.590:后段制程堆叠

194.592:结合层

195.594:载体基材

196.596:结合层

197.598a:基材通孔

198.598b:基材通孔

199.698a:基材通孔

200.698b:基材通孔

201.698c:基材通孔

202.798a:基材通孔

203.798b:基材通孔

204.798c:基材通孔

205.898a:基材通孔

206.898b:基材通孔

207.898c:基材通孔

208.a

‑

a:线

209.b

‑

b:线

210.m1:方法

211.m2:方法

212.s101:方框

213.s102:方框

214.s103:方框

215.s104:方框

216.s105:方框

217.s106:方框

218.s107:方框

219.s108:方框

220.s109:方框

221.s110:方框

222.s111:方框

223.s112:方框

224.s113:方框

225.s114:方框

226.s115:方框

227.s116:方框

228.s117:方框

229.s118:方框

230.s201:方框

231.s202:方框

232.s203:方框

233.s204:方框

234.s205:方框

235.s206:方框

236.s207:方框

237.s208:方框

238.s209:方框

239.s210:方框

240.s211:方框

241.s212:方框

242.t:沟槽

243.t2:深度

244.t3:沟槽

245.t4:深度

246.vss:源极电压

247.vdd:漏极电压

248.w1:晶片

249.w2:晶片

250.w3:晶片

具体实施方式

251.以下公开提供了用于实现本公开的不同特征的许多不同的实施例或示例。以下描述元件和配置的特定示例以简化本公开。当然,这些仅是示例,并不旨在进行限制。例如,在下面的描述中,在第二特征之上或上方形成第一特征可以包括第一特征和第二特征以直接接触形成的实施例,并且还可以包括在第一特征和第二特征之间形成附加的特征,使得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各个示例中重复参考数字和/或文字。此重复是出于简单和清楚的目的,并且其本身并不指示所讨论的各种实施例和/或配置之间的关系。

252.更甚者,空间相对的词汇(例如,“低于”、“下方”、“之下”、“上方”、“之上”等相关词汇)于此用以简单描述如图所示的元件或特征与另一元件或特征的关系。在使用或操作时,除了图中所绘示的转向之外,这些空间相对的词汇涵盖装置的不同转向。再者,这些装置可旋转(旋转90度或其他角度),且在此使用的空间相对的描述语可作对应的解读。

253.如本公开所使用的,“大约”、“大概”、“近似于”或“实质上”通常将意味着在给定值或范围的20%以内,或在10%以内,或在5%以内。在此给出的数值是近似的,意味着如果没有明确说明,则可以推断出术语“大约”、“大概”、“近似于”或“实质上”。

254.除非另有定义,否则本公开中使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域具普通知识者通常所理解的相同含义。还将理解的是,诸如在常用词典中定义的那些术语应被解释为具有与它们在相关领域和本公开的上下文中的含义相一致的含义,并且将不会在理想化或过于正式的情况下被解释,除非在此明确定义。

255.本公开的实施例针对但不限于鳍式场效应晶体管(fin

‑

like field

‑

effect transistor,finfet)装置。鳍式场效应晶体管装置例如可以是互补式金属氧化物半导体(complementary metal

‑

oxide

‑

semiconductor,cmos)装置,包括p型金属氧化物半导体(p

‑

type metal

‑

oxide

‑

semiconductor,pmos)鳍式场效应晶体管装置和n型金属氧化物半导体

enhanced chemical vapor deposition,pecvd)来形成。硬遮罩层在随后的微影制程期间作为硬遮罩。在遮罩层130上形成光阻层,然后对其进行图案化,从而在光阻层中形成开口,从而暴露出遮罩层130的区域。

261.然后,对基材110进行图案化以形成一个或多个半导体鳍片152和154。透过光阻层蚀刻遮罩层130,从而暴露出下面的井区116和118。然后,对暴露的井区116和118进行蚀刻,以形成沟槽t。可以将在相邻沟槽t之间的部分的井区116和118称为半导体鳍片152和154。在蚀刻井区116和118之后,去除光阻层。接下来,可以选择性地执行清洁步骤以去除半导体基材110的原生氧化物。例如,可以使用稀释的氢氟酸(hydrofluoric,hf)来执行清洁。根据本公开的各个方面,半导体鳍片152和154沿着第一方向延伸。在部分实施例中,也可以将半导体鳍片152和154称为氧化物定义(oxide

‑

definition,od)区域。在部分实施例中,作为示例而非限制,井区116和/或118的厚度在例如约10纳米(nm)至约100纳米的范围内。

262.返回图1a,方法m1接着进行到方框s102,其中形成第一隔离介电质以覆盖半导体鳍片。参考图4,在方框s102的部分实施例中,形成隔离介电质160以过度填充沟槽t并覆盖半导体鳍片152和154。沟槽t中的隔离介电质160可以被称为浅沟槽隔离(shallow trench isolation,sti)结构。在部分实施例中,隔离介电质160由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃(fluoride

‑

doped silicate glass,fsg)或其他低介电常数(k)介电质材料制成。在部分实施例中,可以使用高密度电浆(high

‑

density

‑

plasma,hdp)化学气相沉积(chemical vapor deposition,cvd)制程,使用硅甲烷(sih4)和氧气(o2)作为反应前驱物来形成隔离介电质160。在部分其他实施例中,可以使用次大气压的化学气相沉积(sub

‑

atmospheric chemical vapor deposition,sacvd)制程或高深宽比制程(high aspect

‑

ratio process,harp)来形成隔离介电质160,其中制程气体可以包括四乙氧基硅烷(tetraethylorthosilicate,teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(spin

‑

on

‑

dielectric,sod)(例如,含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq))制程来形成隔离介电质160。亦可以使用其他制程和材料。在部分实施例中,隔离介电质160可以具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。之后,可以可选地对隔离介电质160执行热退火。

263.返回图1a,方法m1然后进行到方框s103,其中对第一隔离介电质执行平坦化处理。参考图5,在方框s103的部分实施例中,执行平坦化制程(例如,化学机械平坦化)以去除半导体鳍片152和154上方的多余的隔离介电质160。在部分其他实施例中,当暴露遮罩层130时,停止平坦化制程。在这样的实施例中,遮罩层130可以在平坦化中充当化学机械平坦化停止层。在部分实施例中,平坦化制程还可以去除遮罩层130,使得半导体鳍片152和154的顶表面被暴露。如果遮罩层130没有透过平坦化制程去除,则如果遮罩层130由氮化硅形成,则可以透过使用热磷酸(h3po4)的湿式制程去除,并且如果遮罩层130由氧化硅形成,则可以利用稀释的氢氟酸去除。

264.返回图1a,方法m1然后进行到方框s104,其中形成沟槽以延伸穿过第一隔离介电质进入邻近半导体鳍片的基材中。参考图6,在方框s104的部分实施例中,在隔离介电质160上方形成图案化的遮罩层(未绘示)。在部分实施例中,透过旋涂光阻剂材料,然后进行诸如软烘烤制程(soft baking process)和硬烘烤制程(hard baking process)(也可以称为曝光前烘烤(pre

‑

exposure baking))的制程来形成遮罩层(例如,遮罩层也可以被称为光阻

层)。在部分实施例中,遮罩层是深紫外光(duv)光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层是i

‑

line光阻剂、极紫外光(euv)光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂(chemically amplified resist,car),其包含受酸不稳定基团(acid labile groups,alg)保护的主链聚合物并且还包含光酸产生剂(photo

‑

acid generators,pag)。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂的溶解度。在部分实施例中,遮罩层是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

265.在隔离介电质160上涂覆遮罩层之后,透过遮罩将遮罩层暴露于辐射。在完成使遮罩层暴露于辐射之后,对暴露的遮罩层进行一个或多个曝光后烘烤(post

‑

exposure baking,peb)制程。然后,执行显影制程,从而去除部分暴露的遮罩层,并且此遮罩层可以作为蚀刻遮罩以保护隔离介电质160的其余部分免受蚀刻制程的影响。参照图6,当蚀刻制程完成时,形成穿过隔离介电质160并且具有底部在井区116和118中的沟槽160a和160b。在部分实施例中,作为示例而非限制,在井区116和/或118中的沟槽160a和/或160b具有在约30纳米至约200纳米范围内的深度t2。

266.在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻(reactive

‑

ion etching,rie)制程或原子层蚀刻(atomic layer etching,ale)制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6))、含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

267.返回图1a,方法m1然后进行到方框s105,其中在第一隔离介电质上方形成导电材料并使其填充在沟槽中。参考图7,在方框s105的部分实施例中,使用导电材料170填充沟槽160a和160b。在部分实施例中,导电材料170可以包括金属(例如,钨(w)、钌(ru)、铝(al)、铜(cu)或其他合适的导电材料)。在部分实施例中,可以透过化学气相沉积、物理气相沉积(physical vapor deposition,pvd)、溅镀沉积或适合于沉积导电材料的其他技术来沉积导电材料170。

268.返回图1a,方法m1然后进行到方框s106,其中对导电材料进行平坦化处理。参考图8,在方框s106的部分实施例中,执行平坦化制程(例如,化学机械平坦化(chemical mechanical polish,cmp))以去除在隔离介电质160上方的多余的导电材料170。在部分其他的实施例中,当隔离介电质160被暴露时停止平坦化制程。在这样的实施例中,隔离介电质160可以在平坦化中充当化学机械平坦化停止层。

269.返回图1a,方法m1然后进行到方框s107,其中将沟槽中的导电材料蚀刻至给定的深度,在沟槽中留下一部分的导电材料,从而形成在此高度的埋入式电源轨。参考图9,在方框s107的部分实施例中,执行蚀刻制程以使导电材料170变薄,使得导电材料170的顶面降低到低于隔离介电质160的顶面的高度,从而形成埋入式电源轨170a和170b。在部分实施例中,埋入式电源轨170a和170b也可以被称为导电轨170a和170b。在部分实施例中,埋入式电源轨170a和/或170b也可以被称为供电电源轨和/或接地参考轨。例如,埋入式电源轨170a

可以被称为接地参考轨,并且埋入式电源轨170b可以被称为供电电源轨。如图2所示,埋入式电源轨170a和/或170b沿着半导体鳍片152和/或154的长度方向延伸。在部分实施例中,导电材料170的变薄可以包括干式蚀刻制程或其他合适的蚀刻制程。在部分实施例中,蚀刻制程包括使用选择性地蚀刻导电材料170而不会显著地蚀刻周围结构(即,隔离介电质160)的技术和蚀刻剂。

270.在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或原子层蚀刻)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、三氟化氮(nf3)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6)和/或八氟环丁烷(c4f8))、含氯气体(例如,氯气(cl2)、盐酸(hcl)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

271.返回图1a,方法m1然后进行到方框s108,其中在第一隔离介电质上方形成第二隔离介电质,并在沟槽中填充第二隔离介电质使其在埋入式电源轨上。参考图10,在方框s108的部分实施例中,形成隔离介电质165以过度填充沟槽160a和160b,使其在埋入式电源轨170a和170b上并覆盖隔离介电质160。沟槽160a和160b中的隔离介电质165可以被称为浅沟槽隔离(shallow trench isolation,sti)结构。在部分实施例中,隔离介电质165由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃或其他低介电常数介电质材料制成。在部分实施例中,隔离介电质165具有与隔离介电质160不同的材料。在部分实施例中,隔离介电质165具有与隔离介电质160相同的材料。

272.在部分实施例中,可以使用高密度电浆化学气相沉积制程,使用硅甲烷(sih4)和氧气(o2)作为反应前驱物来形成隔离介电质165。在部分其他实施例中,可以使用次大气压的化学气相沉积制程或高深宽比制程来形成隔离介电质165,其中制程气体可以包括四乙氧基硅烷(teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(例如,含氢硅氧烷(hsq)或甲基硅氧烷(msq))制程来形成隔离介电质165。亦可以使用其他制程和材料。在部分实施例中,隔离介电质165可具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。之后,可以选择性地对隔离介电质165执行热退火。

273.返回图1a,方法m1然后进行到方框s109,其中去除在第一隔离介电质上方的第二隔离介电质。参考图11,在方框s109的部分实施例中,执行平坦化制程(例如,化学机械平坦化)以去除在隔离介电质160上方的多余的隔离介电质165。在部分其他实施例中,当暴露隔离介电质160时,停止平坦化制程。在这样的实施例中,隔离介电质160可以在平坦化中充当化学机械平坦化停止层。在部分其他实施例中,当暴露遮罩层130时,停止平坦化制程。在这样的实施例中,遮罩层130可以在平坦化中充当化学机械平坦化停止层。在部分实施例中,平坦化制程还可以去除遮罩层130,以暴露半导体鳍片152和154的顶表面。

274.返回到图1a,方法m1然后进行到方框s110,其中使第一隔离介电质和第二隔离介电质凹陷。参考图12,在方框s110的部分实施例中,例如透过蚀刻操作使隔离介电质160和165凹陷,其中可以将稀释的氢氟酸、硅钴镍(siconi)(包括氢氟酸(hf)和氨(nh3))等作为蚀刻剂。在使隔离介电质165凹陷之后,半导体鳍片152的一部分和半导体鳍154的一部分高于隔离介电质160的顶表面并且高于隔离介电质165的顶表面。

275.应当理解,上述的方框s101至s110仅仅是形成半导体鳍片152和154、隔离介电质

160和165以及埋入式电源轨170a和170b的示例。在其他实施例中,可以在基材110的顶表面上方形成介电层;可以蚀刻穿过介电层以形成沟槽;可以在沟槽中磊晶生长同质磊晶结构;并且可以使介电层凹陷,使得同质磊晶结构从介电层突出以形成鳍片。在其他实施例中,可以使用异质磊晶结构作为鳍片。例如,可以使半导体鳍片152和154凹陷,并且可以在此位置上磊晶生长与凹陷的半导体鳍片152和154不同的材料。在其他的实施例中,可以在基材110的顶表面上方形成介电层;可以蚀刻穿过介电层形成沟槽;可以使用与基材110不同的材料在沟槽中磊晶生长异质磊晶结构;并且可以使介电层凹陷,使得异质磊晶结构从介电层突出以形成鳍片。在磊晶生长同质磊晶或异质磊晶结构的部分实施例中,尽管可以一起使用原位(in

‑

situ)和布植掺杂,然而在生长期间原位掺杂生长的材料可能会消除鳍片先前的布植掺杂。在部分实施例中,半导体鳍片152或半导体鳍片154可以包括硅锗((si

x

ge1‑

x

),其中x可以在大约0与1之间)、碳化硅、纯或实质上纯的锗、iii

‑

v族化合物半导体、ii

‑

vi化合物半导体等。例如,用于形成iii

‑

v族化合物半导体的可用材料包括但不限于砷化铟(inas)、砷化铝(alas)、砷化镓(gaas)、磷化铟(inp)、氮化镓(gan)、砷镓化铟(ingaas)、砷铝化铟(inalas)、鍗化镓(gasb)、鍗化铝(alsb)、磷化铝(alp)、磷化镓(gap)等。

276.如本公开中所使用的,术语“原位(in

‑

situ)”用于描述当装置或基材保持在制程系统(例如,包括负载锁定室、传送室、处理室或任何其他流体地耦合的腔室)内的同时例如在其中制程系统允许基材保持在真空条件下执行的过程。如此,术语“原位”也可以用于指被处理的装置或基材在不暴露于外部环境(例如,在制程系统外部)的过程。

277.接着是图2所示的栅极形成,其可以透过诸如替换栅极技术的技术来实现。如图2所示,形成垂直于半导体鳍片152和154的栅极结构182和184。

278.返回图1b,方法m1然后进行到方框s111,在其中在半导体鳍片上形成源极/漏极特征。参考图13,在方框s111的部分实施例中,可以透过执行磊晶生长制程来形成源极/漏极特征172和174,此磊晶生长制程提供覆盖半导体鳍片152和154的部分的磊晶材料162和164。源极/漏极特征172和174形成在基材110上并与图2所示的栅极结构182和184相邻。源极/漏极特征172和174包括透过在暴露的半导体鳍片152和154上磊晶生长半导体材料而形成的材料162和164。换句话说,材料162和164形成在与图2所示的栅极结构182和184相邻的半导体鳍片152和154的周围;可以将此称为在半导体鳍片152和154周围形成“包覆层(cladding)”。因此,形成了包含半导体鳍片152和154和磊晶生长的材料162和164的源极/漏极特征172和174。应理解,可以在不使半导体鳍片152和154凹陷的情况下形成这些特征。

279.在各个实施例中,生长的半导体材料162和164可以包括锗(ge)、硅(si)、砷化镓(gaas)、砷化镓铝(algaas)、硅锗(sige)、磷化砷镓(gaasp)、硅磷(sip)或其他合适的材料。在部分实施例中,材料162和164可以在磊晶生长制程期间被原位掺杂。例如,在部分实施例中,磊晶生长的材料162和164可以掺杂有硼。在部分实施例中,磊晶生长的材料162和164可以掺杂有碳以形成硅:碳(si:c)源极/漏极特征,掺杂有磷以形成硅:磷(si:p)源极/漏极特征,或掺杂有碳和磷两者以形成硅碳磷(sicp)源极/漏极特征。在一个实施例中,半导体鳍片152和154由硅制成,并且磊晶生长的材料162和164也为硅。在部分实施例中,半导体鳍片152和154以及磊晶生长的材料162和164可以包括相似的材料,但是掺杂有不同的物质。在其他实施例中,半导体鳍片152和154包括第一半导体材料,磊晶生长的材料162和164包括与第一半导体材料不同的第二半导体。在部分实施例中,磊晶生长的材料162和164不是原

位掺杂的而是(例如)执行布植制程以掺杂磊晶生长的材料162和164。

280.在部分实施例中,在形成源极/漏极特征172和174之前,形成包括栅极介电质和位于栅极介电质上方的栅极的虚设栅极结构(未绘示),以使其在半导体鳍片152和154上延伸。在部分实施例中,为了形成虚设栅极结构,在半导体鳍片152和154上方形成栅极介电层,接着形成虚设栅极层。然后,对栅极介电层和虚设栅极层进行图案化,以分别形成栅极介电质和栅极。出于制程原因,可以在虚设栅极结构上形成硬遮罩,其中,硬遮罩可以包括氮化硅。半导体鳍片152和154的通道部分被虚设栅极结构覆盖,并且半导体鳍片152和154的源极/漏极部分未被虚设栅极结构覆盖。换句话说,虚设栅极结构形成在半导体鳍片152和154的通道部分上方。

281.在部分实施例中,在形成源极/漏极特征172和174之前,分别在虚设栅极结构的相对侧壁上形成如图20b所示的多个栅极间隔物186。在部分实施例中,至少一些栅极间隔物186包括单层或多层。可以透过在先前形成的结构上毯覆式沉积一个或多个介电层(未绘示)来形成栅极间隔物186。介电层可以包括氮化硅(sin)、氮氧化物、硅化碳(sic)、氮氧化硅(sion)、氧化物等,并且可以透过诸如化学气相沉积、电浆增强化学气相沉积、溅镀和其他合适的方法以形成些层。然后可以例如透过一种或多种蚀刻来图案化栅极间隔物186,以从结构的水平表面去除部分的介电层。

282.在图13中,层间介电(interlayer dielectric,ild)层176形成在源极/漏极特征172和174以及虚设栅极结构上。也就是说,在稍后执行的制程期间,源极/漏极特征172和174被层间介电层176覆盖和保护。此外,层间介电层176形成在图20b所示的栅极间隔物186和虚设栅极结构上。执行化学机械平坦化制程以去除部分的层间介电层176。在化学机械平坦化制程期间,暴露虚设栅极结构。层间介电层176的其余部分覆盖源极/漏极特征172和174。层间介电层176可以包括氧化硅、氮氧化物或其他合适的材料。

283.在部分实施例中,采用替换栅极(replacement gate,rpg)制程方案。在替换栅极制程方案中,预先形成虚设栅极结构并且之后由金属栅极代替。在部分实施例中,去除虚设栅极结构(未绘示)以在栅极间隔物186之间形成开口。可以透过干式蚀刻、湿式蚀刻或干式和湿式蚀刻的组合来去除虚设栅极结构。例如,湿式蚀刻制程可以包括暴露于含氢氧化物的溶液(例如,氢氧化铵)、去离子水和/或其他合适的蚀刻剂溶液。在部分实施例中,虚设栅极结构在半导体鳍片152和154的通道部分上提供约束力。在去除虚设栅极结构之后,施加在半导体鳍片152和154的通道部分上的约束力相应地消失,因此,可以增强由源极/漏极特征172和174引起的在半导体鳍片152和154的通道部分上的面内拉伸应变。

284.如图20b所示,在栅极间隔物186之间的开口中分别形成多个栅极188。换句话说,虚设栅极结构被栅极188代替,因而使间隔物186设置在栅极188的侧壁上。栅极188形成在半导体鳍片152和154的通道部分上方。栅极188可以包括金属、金属合金和/或金属硅化物。另外,栅极188的形成可以包括沉积以形成各种栅极材料、一个或多个衬垫层,并包括一种或多种化学机械平坦化制程以去除过量的栅极材料并由此使栅极188的顶表面平坦化。

285.在部分其他实施例中,包括在栅极188中的功函数金属层可以是n型或p型功函数层。示例性的p型功函数金属包括氮化钛(tin)、氮化钽(tan)、钌(ru)、钼(mo)、铝(al)、氮化钨(wn)、硅化锆(zrsi2)、硅化钼(mosi2)、硅化钽(tasi2)、硅化镍(nisi2)、氮化钨(wn)、其他合适的p型功函数材料或其组合。示例性的n型功函数金属包括钛(ti)、银(ag)、铝化钽

(taal)、碳铝化钽(taalc)、氮铝化钛(tialn)、碳化钽(tac)、氮碳化钽(tacn)、氮硅化钽(tasin)、锰(mn)、锆(zr)、其他合适的n型功函数材料或其组合。功函数层可以包括多个层。功函数层可以透过化学气相沉积、物理气相沉积、电镀和/或其他合适的制程来沉积。在部分实施例中,栅极188可以是包括p型功函数层的p型金属栅极。在部分实施例中,包括在栅极188中的覆盖层可以包括难熔金属及其氮化物(例如,氮化钛(tin)、氮化钽(tan)、氮化钨(w2n)、氮硅化钛(tisin)、氮硅化钽(tasin))。可以透过物理气相沉积、化学气相沉积、金属有机化学气相沉积(metal

‑

organic chemical vapor deposition,mocvd)和原子层沉积来沉积覆盖层。在部分实施例中,包括在栅极188中的填充层可以包括钨(w)。可以透过原子层沉积、物理气相沉积、化学气相沉积或其他合适的制程来沉积金属层。

286.对栅极188进行去除制程,以部分地去除栅极188。蚀刻制程可以包括湿式蚀刻、干式蚀刻和/或其组合。作为示例,湿式蚀刻溶液可以包括硝酸(hno3)、氨水(nh4oh)、氢氧化钾(koh)、氟化氢(hf)、盐酸(hcl)、氢氧化钠(naoh)、磷酸(h3po4)和/或其他合适的湿式蚀刻溶液和/或其组合。亦或是,干式蚀刻制程可以使用含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)、和/或三氯化硼(bcl3))、含溴气体(例如、溴化氢(hbr)和/或三溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。在部分实施例中,选择蚀刻制程以选择性地蚀刻栅极188,而实质上不会蚀刻层间介电层176和栅极间隔物186。在部分实施例中,控制蚀刻制程以使得剩余的栅极188的顶表面低于层间介电层176和栅极间隔物186的顶表面。本公开所用的术语“实质上”可以用于修饰任何定量表示,此定量表示可以允许变化而不会导致与的相关的基本功能发生变化。

287.返回图1b,方法m1然后进行到方框s112,其中形成互连以连接源极/漏极特征和埋入式电源轨。参考图14a,在方框s112的部分实施例中,在层间介电层176中形成沟槽176b以暴露源极/漏极特征172和174,并且形成通孔开口176a使其从沟槽176b的底部向下延伸至埋入式电源轨170a。沟槽176b和通孔开口176a可以透过类似双镶嵌的技术(例如,先沟槽图案化方法或先通孔图案化方法)形成。可以在先沟槽图案化方法或先通孔图案化方法中采用适当的微影和蚀刻技术。在图14a中,沟槽176b的底部位置高于源极/漏极特征172和174的最大宽度。在部分实施例中,沟槽176b的底部位置可以低于源极/漏极特征172和174的最大宽度并高于隔离介电质160的顶表面。在部分实施例中,沟槽176b的底部可以与隔离介电质160的顶表面齐平。然后,形成填充在层间介电层176的通孔开口176a和沟槽176b中的导电材料以形成互连178a,此互连将源极/漏极特征172和174连接到埋入式电源轨170a。在部分实施例中,形成填充在层间介电层176的沟槽中的导电材料,以形成互连源极/漏极特征的互连178b,如图2所示。

288.图14b绘示根据本公开的部分其他实施例在对应于图14a的阶段的另一晶片,其绘示互连的不同轮廓。如图14b所示,形成了从沟槽176b的底部垂直地向下延伸到埋入式电源轨170a的通孔开口176c。图14a和图14b之间的区别在于,通孔开口176c暴露出隔离介电质160的侧表面。因此,在其中形成的互连179与隔离介电质160接触。

289.返回图1b,方法m1然后进行到方框s113,其中在基材上形成后段制程堆叠,并在后段制程堆叠上形成结合层。透过在半导体晶片上进行前段制程(front end of line,feol)和后段制程(back end of line,beol)制程来制造晶片,此前段制程包括用于生产埋入式电源轨170a和170b以及互连178a的上述步骤。如上所述,将埋入式电源轨170a/170b连接到

漏极电压(vdd)、源极电压(vss)和互连178a。参考图15,在方框s113的部分实施例中,后段制程堆叠190形成在基材110上方并且以示意性方式绘示出而没有详细地描述互连。使用后段制程形成后段制程堆叠190。后段制程包括在晶片w1中的装置结构之间形成金属布线,以使它们互连,其包括形成接触、互连线、通孔结构和介电结构。然后,在后段制程堆叠190上方形成结合层192。在部分实施例中,结合层192可以包括氧化硅、氮碳化硅(sicn)或用于实现直接介电质至介电质结合的任何其他材料。

290.返回图1b,方法m1然后进行到方框s114,其中将晶片接合到载体基材上。参考图16,在方框s114的部分实施例中,晶片w1透过结合层192结合到载体基材194。在部分实施例中,载体基材194上还设有结合层196。结合层196可以包括氧化硅、氮碳化硅(sicn)或用于实现直接的介电质至介电质结合的任何其他材料。透过直接接合(direct bonding)技术将晶片w1接合到载体基材194,从而获得如图16所示的接合的晶片堆叠。

291.返回图1b,方法m1然后进行到方框s115,其中使晶片的基材变薄。参考图17,在方框s115的部分实施例中,作为示例而非限制方式,晶片w1的基材110可透过研磨和/或湿式或干式蚀刻技术变薄。作为示例而非限制,剩余的基材厚度在约50纳米(nm)至约500纳米的范围内。在部分实施例中,作为示例而非限制,接着进一步减小厚度,直到半导体的厚度约为1微米(μm)。在部分实施例中,可以透过将可以充当蚀刻停止层的掺杂层并入到装置晶片中来实现变薄。作为示例而非限制,然后施加在掺杂层上停止的选择性湿式蚀刻步骤,以将半导体晶片减薄至所需的约1微米的厚度。

292.返回图1b,方法m1然后进行到方框s116,其中形成穿过基材直到到达埋入式电源轨和井区的基材通孔(through substrate via,tsv)开口。参考图18a,在方框s116的部分实施例中,形成穿过基材110直到到达连接到电源或接地的埋入式电源轨170a和/或170b的基材通孔开口110a和/或110c。形成穿过基材110直到到达井区116和/或118的基材通孔开口110b,并且此基材通孔开口110b可以作为导电路径以在静电放电(electrostatic discharge,esd)事件期间释放高电流和电流密度,以避免电路崩溃。

293.更详细地,作为示例而非限制,在基材110中形成具有大于约5的高深宽比的基材通孔开口110a、110b和/或110c。在限定基材通孔开口110a、110b和/或110c时,在基材110上方形成硬遮罩层(未绘示),随后在其上形成图案化的光阻层(未绘示)。作为示例而非限制,硬遮罩层可以是氮化硅层、氮氧化硅层等。透过曝光、烘烤、显影和/或其他微影制程将光阻层图案化以提供暴露硬遮罩层的开口。然后,透过湿式蚀刻或干式蚀刻制程,使用图案化的光阻层作为遮罩元件以提供开口,来蚀刻暴露的硬遮罩层。使用硬遮罩层和图案化的光阻层作为遮罩元件,执行蚀刻制程以蚀刻暴露的基材110,从而形成穿过基材110的基材通孔开口110a、110b和/或110c。埋入式电源轨170a和170b还可以在蚀刻基材110时作为蚀刻停止层,直到暴露出埋入式电源轨170a和170b。因为同时形成基材通孔开口110a、110b和/或110c,所以基材通孔开口110b的底部可以与基材通孔开口110a和/或110c的底部齐平,并且可以与透过基材通孔开口110a和/或110c而暴露的电源轨170a和/或170b的表面齐平。

294.在部分实施例中,可以使用任何合适的蚀刻方法来蚀刻基材通孔开口110a、110b和/或110c,在此所指的合适的蚀刻方法包括诸如电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材110。蚀刻制程可以从晶片w1的背表面110d蚀刻大约几十微米到几百微米而形成基材通孔开口110a、110b

和/或110c。在部分实施例中,蚀刻制程可导致在与基材通孔开口110a、110b和/或110c的侧壁相邻的基材110上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口110a、110b和/或110c的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口110a、110b和/或110c的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口110a、110b和/或110c的深宽比可大于约10。在部分实施例中,在基材110中创建具有高深宽比的基材通孔开口110a、110b和/或110c时,可能会在基材110的侧壁上产生一系列蚀刻的大扇贝形(未绘示),其尺寸可以根据制程参数而改变。微扇贝形侧壁将在随后的热氧化过程中被平滑化。

295.在部分实施例中,基材通孔开口110a、110b和/或110c具有如图2所示的矩形平面图轮廓(或俯视图轮廓),其宽度小于埋入式电源轨170a和170b的宽度。在部分实施例中,基材通孔开口110a、110b和/或110c的宽度大于埋入式电源轨170a和170b的宽度。亦或是,基材通孔开口110a、110b和/或110c可具有圆形的平面轮廓,其直径小于埋入式电源轨170a和170b的宽度。在部分实施例中,基材通孔开口110a、110b和/或110c的直径大于埋入式电源轨170a和170b的宽度。

296.图18b绘示根据本公开的部分其他实施例的处于对应于图18a的阶段的另一晶片,其绘示出基材通孔开口的不同轮廓。如图18b所示,形成从基材110的背表面110d垂直地向下延伸至埋入式电源轨170a的基材通孔开口110e、110f和/或110g。图18a和图18b之间的区别在于,基材通孔开口110e和/或110f的背面底端低于埋入式电源轨170a和/或170b的背面端部170c和/或170d,使得基材通孔开口110e和/或110f暴露埋入式电源轨170a和/或170c的侧壁,这将允许增加埋入式电源轨170a和/或170b与将在基材通孔开口110e和/或110f中形成的基材通孔之间的接触面积。因为同时形成基材通孔开口110e、110f和/或110g,所以基材通孔开口110f的底部可以与基材通孔开口110e和/或110g的底部齐平并且低于埋入式电源轨170a和/或170b的背面端部170c和/或170d。

297.返回图1b,方法m1然后进行到方框s117,其中在基材通孔开口中形成基材通孔(through substrate vias,tsvs)。参考图19,在方框s117的部分实施例中,基材通孔198a和/或198c形成在基材110的基材通孔开口110a和/或110c中,并与埋入式电源轨170a和/或170b接触,以连接到电源或接地。基材通孔198b形成在基材通孔开口110b中并且与井区116和/或118接触。在部分实施例中,基材通孔198b可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片w1的前侧上未形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔198b可以作为晶片w1的散热器,以将半导体元件产生的热量从井区释放到晶片w1的外部。

298.更详细地,透过使用金属化制程以及使用金属电镀技术来填充高深宽比开口以避免接缝或空隙缺陷而形成基材通孔198a、198b和/或198c。在部分实施例中,为了避免金属从基材通孔金属扩散到硅基材中,在绝缘层和基材通孔金属之间使用阻挡层(未绘示)。阻挡层可以做为基材通孔开口110a、110b和/或110c的衬垫。阻挡层可作为防止金属扩散的扩散阻挡层,并且可作为金属与介电质之间的粘合层。作为示例但非限制,难熔金属、难熔金属氮化物、难熔金属硅氮化物及其组合可用于阻挡层(例如,氮化钽(tan)、钽(ta)、钛(ti)、氮化钛(tin)、氮硅化钛(tisin)、氮化钨(wn)或其组合)。在部分实施例中,阻挡层可以包括

氮化钽(tan)层和钽(ta)层。在部分实施例中,阻挡层是氮化钛(tin)层。在部分实施例中,阻挡层是钛(ti)层。在部分实施例中,接着在阻挡层上形成金属晶种层(metal seed layer)(未绘示)。在部分实施例中,作为示例而非限制,金属晶种层是铜晶种层,此铜晶种层可以透过物理气相沉积的方式形成。

299.接着,可以将晶片w1转移至电镀工具(例如,电化学电镀(electrochemical plating,ecp)工具)并透过电镀制程在晶片w1上电镀导电层以填充基材通孔开口110a、110b和/或110c。尽管本公开描述了电化学电镀制程,然而实施例不限于电化学电镀沉积的金属。导电层可以包括选自包括但不限于铜和铜基合金的导体材料群组的低电阻率的导体材料。亦或是,导电层可以包括各种材料(例如,钨、钌、铝、金、银等)。在部分实施例中,导电层是形成在铜晶种层上方的含铜层。

300.随后,透过蚀刻、化学机械平坦化等去除导电层、金属晶种层和阻挡层的多余部分,从而使金属填充的开口的上表面实质上与基材110的背表面齐平。基材通孔开口110a、110b和/或110c中的导电层和阻挡层的其余部分形成基材通孔198a、198b和/或198c。

301.基材通孔198b与井区116和/或118接触并且电耦合在埋入式电源轨170a和170b之间。当在埋入式电源轨170b上发生静电放电事件时,基材通孔198b用以在埋入式电源轨170a和170b之间提供导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。在部分实施例中,基材通孔198b也可以被称为静电放电保护电路。

302.返回图1b,方法m1然后进行到方框s118,其中形成后段制程型互连堆叠和在后段制程型互连堆叠上的端子以连接埋入式电源轨。参考图20a和图20b,在方框s118的部分实施例中,形成后段制程型互连堆叠150以及在后段制程型互连堆叠150上方的端子vdd和vss,以连接埋入式电源轨170a和170b。更详细地,执行一系列镶嵌制程步骤以产生后段制程型互连堆叠150,其透过低电阻电路将基材通孔198a和198c连接至晶片w1的背面上的端子vdd和vss。在部分实施例中,后段制程型互连堆叠150也可以被称为晶片w1的电源供应网络(power delivery network)。

303.图21绘示根据本公开的部分其他实施例的与图2相对应的另一晶片的俯视图,其绘示出基材通孔的不同轮廓。如图21所示,形成与埋入式电源轨170a和/或170b接触的基材通孔698a和/或698c,以连接到电源或接地。形成与井区116和/或118接触的基材通孔698b。形成图21所示的基材通孔698a、698b和/或698c的操作与如图2至图20b所示在方法m1的方框s101至s118中形成晶片w1的基材通孔198a、198b和/或198c的操作实质上相同,并且可以参考前述段落中的相关详细描述,在此不再赘述。

304.如图21所示,垂直地重叠栅极结构182的基材通孔698b,在沿栅极结构182的长度方向横向地位于半导体鳍片152和154之间,和/或在沿半导体鳍片152的长度方向横向地位于互连178a和178b之间。在部分实施例中,基材通孔698b与源极/漏极特征172和174不重叠。基材通孔698a和/或698c与互连178a和/或178b不重叠。在部分实施例中,基材通孔698a、698b和698c沿着栅极结构182的长度方向配置。在部分实施例中,基材通孔698b可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于没有在晶片的正面上形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔698b可以作为晶片的散热器,以将半导体元件产生的热量从井区释放到晶片外部。在部分实施例中,基材通孔698b也可以被称为静电放电保护电

路。

305.图22绘示根据本公开的部分其他实施例的与图2相对应的另一晶片的俯视图,其绘示出基材通孔的不同轮廓。如图22所示,形成与埋入式电源轨170a和/或170b接触的基材通孔798a和/或798c,以便连接到电源或接地。形成与井区116和/或118接触的基材通孔798b。形成图22所示的基材通孔798a、798b和/或798c的操作与形成如图2至图20b所示在方法m1的方框s101至s118中形成晶片w1的基材通孔198a、198b和/或198c的操作实质上相同,因此可以参考前述段落中的相关详细描述,在此不再赘述。

306.如图22所示,与栅极结构182垂直地重叠的基材通孔798b在沿栅极结构182的长度方向上横向地位于半导体鳍片152和154之间,和/或在沿着半导体鳍片152的长度方向上横向地位于互连178a和178b之间。在部分实施例中,基材通孔798b不与源极/漏极特征172和174重叠。基材通孔798a和/或798c与互连178a和/或178b重叠。在部分实施例中,基材通孔798a、798b和798c在栅极结构182的长度方向上不重叠。在部分实施例中,基材通孔798b可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片的正面上不形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔798b可以作为晶片的散热器,以将半导体元件产生的热量从井区释放到晶片外部。在部分实施例中,基材通孔798b也可以被称为静电放电保护电路。

307.图23绘示根据本公开的部分其他实施例的与图2相对应的另一晶片的俯视图,其绘示出基材通孔的不同轮廓。如图23所示,形成与埋入式电源轨170a和/或170b接触的基材通孔898a和/或898c,以便连接到电源或接地。形成与井区116和/或118接触的基材通孔898b。图23所示的用于形成基材通孔898a、898b和/或898c的操作与如图2至图20b所示在方法m1的方框s101至s118中用于形成晶片w1的基材通孔198a、198b和/或198c的操作实质上相同,因此可以参考前述段落中的相关详细描述,在此不再赘述。

308.如图23所示,基材通孔898b垂直地重叠互连178a和/或沿着栅极结构182的长度方向横向地位于半导体鳍片152和154之间。在部分实施例中,基材通孔898b与栅极结构182不重叠。基材通孔898a和/或898c与互连178a和/或178b不重叠。在部分实施例中,基材通孔898a、898b和898c在栅极结构182的长度方向上未对准。在部分实施例中,基材通孔898b可以作为传导路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于没有在晶片的正面上形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔898b可以作为晶片的散热器,以将由半导体元件产生的热量从井区释放到晶片的外部。在部分实施例中,基材通孔898b也可以被称为静电放电保护电路。

309.现在参考图24,其绘示根据部分实施例的用于制造半导体元件的示例性方法m2。方法m2包括整个制造过程的相关部分。应当理解,可以在图24所示的操作之前、之中和之后提供附加操作,并且以下描述的一些操作可以被代替或消除以作为此方法的附加实施例。操作/过程的顺序可以互换。应理解,为了更好地理解所公开的实施例,已经简化了图24。

310.图25至图36绘示根据本公开的部分实施例在方法m2的各个阶段的晶片w2。方法m2开始于方框s201,其中在基材上形成半导体鳍片。参照图25,在方框s201的部分实施例中,晶片w2经历一系列沉积和微影制程,从而在晶片w2的基材210上形成图案化的光阻层(未绘

示)和遮罩层230。在部分实施例中,遮罩层230包括硬遮罩层和衬垫层。在部分实施例中,基材210是半导体基材(例如,体半导体、绝缘体上半导体基材等)。绝缘体上半导体基材包括形成在绝缘体层上的半导体材料层。绝缘体层可以是例如埋入氧化物层、氧化硅层等。绝缘体层设置在基材、硅或玻璃基材上。亦可以使用其他基材(例如,多层或梯度基材)。在部分实施例中,基材210的半导体材料可以包括硅;锗;化合物半导体(包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟);合金半导体(包括硅锗(sige)、磷砷化镓(gaasp)、砷铟化铝(alinas)、砷镓化铝(algaas)、砷铟化镓(gainas)、磷铟化镓(gainp)和/或磷砷化铟镓(gainasp));或其组合。

311.如图25所示,基材210中的p型井区216和n型井区218将基材210划分为用于不同类型的装置或晶体管的单独区域。p型井区216和n型井区218的示例性材料包括但不限于掺杂有各种类型的p型掺杂剂和/或n型掺杂剂的半导体材料。在部分实施例中,p型井区216包括p型掺杂剂,而n型井区218包括n型掺杂剂。在图25的示例性配置中,n型井区218是用于形成p通道金属氧化物半导体晶体管的区域,并且p型井区216是用于形成n通道金属氧化物半导体晶体管的区域。这里描述的井区216和218的导电性是一个例子。其他配置亦在各种实施例的范围内。

312.在部分实施例中,衬垫层是包括使用诸如热氧化过程形成的氧化硅的薄膜。衬垫层可以作为基材210和硬遮罩层之间的粘合层。衬垫层还可以作为用于蚀刻硬遮罩层的蚀刻停止层。在部分实施例中,硬遮罩层由例如使用低压化学气相沉积或电浆增强化学气相沉积的氮化硅形成。硬遮罩层在随后的微影制程期间作为硬遮罩。在遮罩层230上形成光阻层,然后对其进行图案化,从而在光阻层中形成开口,从而暴露出遮罩层230的区域。

313.然后,对基材210进行图案化以形成一个或多个半导体鳍片252、253、254和255。透过光阻层蚀刻遮罩层230以暴露出下面的基材210。然后,对暴露的基材210进行蚀刻,以形成沟槽t3。相邻沟槽t3之间的p型井区216的一部分可以被称为半导体鳍片253。相邻沟槽t3之间的n型井区218的一部分可以被称为半导体鳍片254。可以将在横向上围绕p型井区216和n型井区218并且邻近于相邻沟槽t3的部分的基材210称为半导体鳍片252和255。在蚀刻基材210之后,去除光阻层。接下来,可以可选地执行清洁步骤以去除半导体基材210的原生氧化物。例如,可以使用稀释的氢氟酸来执行清洁。根据本公开的各个方面,半导体鳍片252至255沿着第一方向延伸。在部分实施例中,半导体鳍片252至255也可以被称为氧化物定义区域。在部分实施例中,作为示例而非限制,p型井区216和/或n型井区218的厚度在例如约10纳米至约100纳米的范围内。

314.返回图24,方法m2然后进行到方框s202,其中形成隔离介电质以覆盖半导体鳍片。参考图26,在方框s202的部分实施例中,形成隔离介电质260以过度地填充沟槽t3并覆盖半导体鳍片252至255。沟槽t3中的隔离介电质260可以被称为浅沟槽隔离结构。在部分实施例中,隔离介电质260由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃或其他低介电常数介电质材料制成。在部分实施例中,可以使用高密度电浆化学气相沉积制程,使用硅甲烷(sih4)和氧气(o2)作为反应前驱物来形成隔离介电质260。在部分其他实施例中,隔离介电质260可以使用低于大气压的化学气相沉积制程或高深宽比制程形成,其中制程气体可以包括四乙氧基硅烷(teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(例如,含氢硅氧烷(hsq)或甲基硅氧烷(msq))制程来形成隔离介电质260。亦可以使用其他制程和材

料。在部分实施例中,隔离介电质260可以具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。之后,可以可选地对隔离介电质260执行热退火。

315.返回图24,方法m2然后进行到方框s203,其中对第一隔离介电质执行平坦化制程。参考图27,在方框s203的部分实施例中,执行诸如化学机械平坦化之类的平坦化制程以去除在半导体鳍片252至255上方的多余的隔离介电质260。在部分其他实施例中,当暴露遮罩层230时,停止平坦化制程。在这样的实施例中,遮罩层230可以在平坦化中充当化学机械平坦化停止层。在部分实施例中,平坦化制程还可以去除遮罩层230,以暴露半导体鳍片252至255的顶表面。如果没有透过平坦化制程去除遮罩层230,则如果遮罩层230由氮化硅形成,则可以透过使用热磷酸(h3po4)的湿式制程去除,并且如果遮罩层230由氧化硅形成,则可以利用稀释的氢氟酸去除。

316.返回图24,然后方法m2前进到方框s204,其中使隔离介电质凹陷。参考图28,在方框s204的部分实施例中,例如透过蚀刻操作使隔离介电质260凹陷,其中可以将稀释的氢氟酸、硅钴镍(siconi)(包括氢氟酸(hf)和氨(nh3))等作为蚀刻剂。在使隔离介电质260凹陷之后,半导体鳍片252至255的一部分高于隔离介电质260的顶表面。

317.应当理解,上述的方框s201至s204仅仅是如何形成半导体鳍片252至255和隔离介电质260的示例。在其他实施例中,可以在基材210的顶表面上方形成介电层;可以透过蚀刻介电层形成沟槽;可以在沟槽中磊晶生长同质磊晶结构;并且可以使介电层凹陷,使得同质磊晶结构从介电层突出以形成鳍片。在其他实施例中,鳍片可使用异质磊晶结构。例如,可以使半导体鳍片252至255凹陷,并且在其位置磊晶生长与凹陷的半导体鳍片252至255不同的材料。在进一步的实施例中,可以在基材210的顶表面上方形成介电层;可以透过蚀刻介电层形成沟槽;可以使用与基材210不同的材料在沟槽中磊晶生长异质磊晶结构;可以使介电层凹陷,使得异质磊晶结构从介电层突出以形成鳍片。在磊晶生长同质磊晶或异质磊晶结构的部分实施例中,尽管可以一起使用原位(in

‑

situ)和布植掺杂,然而在生长期间原位掺杂生长的材料可能会消除鳍片先前的布植掺杂。在部分实施例中,半导体鳍片252、253、254或255可以包括硅锗((si

x

ge1‑

x

),其中x可以在大约0与1之间)、碳化硅、纯或实质上纯的锗、iii

‑

v族化合物半导体、ii

‑

vi族化合物半导体等。例如,用于形成iii

‑

v族化合物半导体的可用材料包括但不限于砷化铟(inas)、砷化铝(alas)、砷化镓(gaas)、磷化铟(inp)、氮化镓(gan)、砷镓化铟(ingaas)、砷铝化铟(inalas)、鍗化镓(gasb)、鍗化铝(alsb)、磷化铝(alp)、磷化镓(gap)等。

318.返回图24,方法m2然后进行到方框s205,其中在半导体鳍片上形成源极/漏极特征。参考图29,在方框s205的部分实施例中,在半导体鳍片252、253、254和255上方形成图案化的遮罩层(未绘示)。在部分实施例中,透过旋涂光阻剂材料,然后进行诸如软烘烤制程和硬烘烤制程(也可以称为曝光前烘烤)的制程来形成遮罩层(例如,遮罩层也可以被称为光阻层)。在部分实施例中,遮罩层是深紫外光光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层是i

‑

line光阻剂、极紫外光光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂,其包含受酸不稳定基团保护的主链聚合物并且还包含光酸产生剂。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂

的溶解度。在部分实施例中,遮罩层是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

319.在半导体鳍片252、253、254和255上涂覆遮罩层之后,透过遮罩将遮罩层暴露于辐射。在将遮罩层暴露于辐射之后,对暴露的遮罩层进行一个或多个曝光后烘烤制程。然后,执行显影制程,从而去除暴露的遮罩层的一部分,并且此遮罩层作为遮罩以保护半导体鳍片252和255免受随后的磊晶生长制程的影响。当蚀刻制程完成时,形成沟槽以穿过遮罩层并暴露半导体鳍片253和254以及隔离介电质260的顶表面。在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或原子层蚀刻制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6))、含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

320.然后,可以透过执行磊晶生长制程来形成源极/漏极特征273和274,此磊晶生长制程提供覆盖部分的半导体鳍片253和254的磊晶材料263和264。源极/漏极特征273和274包括透过在暴露的半导体鳍片253和254上磊晶生长半导体材料而形成的材料263和264。换句话说,材料263和264形成在半导体鳍片253和254的周围;可以将此称为在半导体鳍片253和254周围形成“包覆层”。因此,源极/漏极特征273和274包括半导体鳍片253和254和所形成的磊晶生长的材料263和264。应理解,可以在不使半导体鳍片253和254凹陷的情况下形成这些特征。在形成源极/漏极特征273和274之后,去除覆盖半导体鳍片252和255的图案化的遮罩层。

321.在各个实施例中,生长的半导体材料263和264可以包括锗(ge)、硅(si)、砷化镓(gaas)、砷化镓铝(algaas)、硅锗(sige)、磷化砷镓(gaasp)、硅磷(sip)或其他合适的材料。在部分实施例中,材料263和264可以在磊晶制程期间被原位掺杂。例如,在部分实施例中,磊晶生长的材料263和264可以掺杂有硼。在部分实施例中,磊晶生长的材料263和264可以掺杂有碳以形成硅:碳(si:c)源极/漏极特征,掺杂有磷以形成硅:磷(si:p)源极/漏极特征,或掺杂有碳和磷两者以形成硅碳磷(sicp)源极/漏极特征。在一个实施例中,半导体鳍片253和254由硅制成,并且磊晶生长的材料263和264也为硅。在部分实施例中,半导体鳍片253和254以及磊晶生长的材料263和264可以包括相似的材料,但是被不同地掺杂。在其他实施例中,半导体鳍片253和254包括第一半导体材料,而磊晶生长的材料263和264包括与第一半导体材料不同的第二半导体。在部分实施例中,磊晶生长的材料263和264不是原位掺杂的,而是(例如)执行布植制程以掺杂磊晶生长的材料263和264。

322.在部分实施例中,在形成源极/漏极特征273和274之前,形成在半导体鳍片253和254上延伸的虚设栅极结构(未绘示),其中此虚设栅极结构包括栅极介电质和位于栅极介电质上方的栅极。在部分实施例中,为了形成虚设栅极结构,在半导体鳍片253和254上方形成栅极介电层,接着形成虚设栅极层。然后,对栅极介电层和虚设栅极层进行图案化,以分别形成栅极介电质和栅极。出于制程原因,可以在虚设栅极结构上形成硬遮罩,其中,硬遮罩可以包括氮化硅。半导体鳍片253和254的通道部分被虚设栅极结构覆盖,并且半导体鳍片253和254的源极/漏极部分未被虚设栅极结构覆盖。换句话说,虚设栅极结构形成在半导体鳍片253和254的通道部分上方。

323.返回图24,方法m2然后进行到方框s206,其中在源极/漏极特征上形成层间介电层,并在层间介电层上形成后段制程堆叠。参考图30,在方框s206的部分实施例中,层间介电层276形成在半导体鳍片252、253、254和255、源极/漏极特征273和274以及虚设栅极结构之上。也就是说,在稍后执行的制程期间,源极/漏极特征273和274被层间介电层276覆盖和保护。此外,层间介电层276形成在虚设栅极结构上方。执行化学机械平坦化制程以去除部分的层间介电层276。在化学机械平坦化制程期间,暴露虚设栅极结构。层间介电层276的其余部分分别覆盖源极/漏极特征273和274。层间介电层276可以包括氧化硅、氮氧化物或其他合适的材料。

324.采用替换栅极制程方案。在替换栅极制程方案中,预先形成虚设栅极结构并由金属栅极代替。在部分实施例中,去除虚设栅极结构(未绘示)。可以透过干式蚀刻、湿式蚀刻或干式和湿式蚀刻的组合来去除虚设栅极结构。例如,湿式蚀刻制程可以包括暴露于含氢氧化物的溶液(例如,氢氧化铵)、去离子水和/或其他合适的蚀刻剂溶液。在部分实施例中,虚设栅极结构在半导体鳍片253和254的通道部分上提供约束力。在去除虚设栅极结构之后,施加在半导体鳍片253和254的通道部分上的约束力相应地消失,因此,可以增强由源极/漏极特征273和274在半导体鳍片253和254的通道部分上引起的面内拉伸应变。

325.然后,形成栅极以替换虚设栅极结构。栅极形成在半导体鳍片252至254的通道部分上方。栅极188可以包括金属、金属合金和/或金属硅化物。另外,栅极的形成可以包括沉积以形成各种栅极材料、一个或多个衬垫层,并可包括一种或多种化学机械平坦化制程以去除过量的栅极材料并由此使栅极的顶表面平坦化。

326.在部分其他实施例中,包括在栅极中的功函数金属层可以是n型或p型功函数层。示例性的p型功函数金属包括氮化钛(tin)、氮化钽(tan)、钌(ru)、钼(mo)、铝(al)、氮化钨(wn)、硅化锆(zrsi2)、硅化钼(mosi2)、硅化钽(tasi2)、硅化镍(nisi2)、氮化钨(wn)、其他合适的p型功函数材料或其组合。示例性的n型功函数金属包括钛(ti)、银(ag)、铝化钽(taal)、碳铝化钽(taalc)、氮铝化钛(tialn)、碳化钽(tac)、氮碳化钽(tacn)、氮硅化钽(tasin)、锰(mn)、锆(zr)、其他合适的n型功函数材料或其组合。功函数层可以包括多个层。功函数层可以透过化学气相沉积、物理气相沉积、电镀和/或其他合适的制程来沉积。在部分实施例中,栅极可以是包括p型功函数层的p型金属栅极。在部分实施例中,包括在栅极188中的覆盖层可以包括难熔金属及其氮化物(例如,氮化钛(tin)、氮化钽(tan)、氮化钨(w2n)、氮硅化钛(tisin)、氮硅化钽(tasin))。可以透过物理气相沉积、化学气相沉积、金属有机化学气相沉积和原子层沉积来沉积覆盖层。在部分实施例中,包括在栅极中的填充层可以包括钨(w)。可以透过原子层沉积、物理气相沉积、化学气相沉积或其他合适的制程来沉积金属层。

327.对栅极执行去除制程以部分地去除栅极。蚀刻制程可以包括湿式蚀刻、干式蚀刻和/或它们的组合。作为示例,湿式蚀刻溶液可以包括硝酸(hno3)、氨水(nh4oh)、氢氧化钾(koh)、氟化氢(hf)、盐酸(hcl)、氢氧化钠(naoh)、磷酸(h3po4)和/或其他合适的湿式蚀刻溶液和/或其组合。亦或是,干式刻蚀制程可以使用含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。在部分实施例中,选择蚀刻制程以选择性地蚀刻栅极而实质上不蚀刻层间介电层276。在部分实施例中,控制蚀刻制

程以使得剩余的栅极的顶面低于层间介电层276的顶表面。

328.前段制程包括上述步骤。然后,在基材210上方形成后段制程堆叠290并连接源极/漏极特征273和274,其以示意性方式表达而无详细说明互连。使用后段制程形成后段制程堆叠290。后段制程包括在晶片w2中的装置结构之间形成金属布线以使它们互连,其中包括形成接触、互连线、通孔结构和介电结构。

329.返回图24,方法m2然后进行到方框s207,其中在后段制程堆叠上形成结合层。参考图31,在方框s207的部分实施例中,在后段制程堆叠290上方形成结合层292。在部分实施例中,结合层292可以包括氧化硅、氮碳化硅(sicn)或适用于现有封装技术的直接接合技术的任何其他材料。

330.返回图24,方法m2然后进行到方框s208,其中将晶片结合到载体基材上。参考图32,在方框s208的部分实施例中,晶片w2透过结合层292结合到载体基材294。在部分实施例中,载体基材294上还设置有结合层296。结合层296可以包括氧化硅、氮碳化硅(sicn)或适用于最先进的封装技术的直接接合技术的任何其他材料。透过直接接合技术将晶片w2结合到载体基材294,从而获得如图32所示的结合的晶片堆叠。

331.返回图24,方法m2然后进行到方框s209,其中使晶片的基材变薄。参考图33,在方框s209的部分实施例中,作为示例而非限制,可以使用研磨和/或湿式或干式蚀刻技术来使晶片w2的基材210变薄。作为示例而非限制,剩余的基材厚度在约50纳米至约500纳米的范围内。在部分实施例中,作为示例而非限制,接着进一步减小厚度,直到半导体的厚度为约1微米。在部分实施例中,透过将可以作为蚀刻停止层的掺杂层并入到装置晶片中来实现减薄。作为示例而非限制,接着执行在掺杂层上停止的选择性湿式蚀刻步骤,以将半导体晶片减薄至所需的约1微米的厚度。

332.返回图22,方法m2然后前进到方框s210,其中形成穿过基材直到到达基材中的p型井区和n型井区的基材通孔开口。参考图34,在方框s210的部分实施例中,形成穿过基材210到达p型井区216和n型井区218的基材通孔开口210a和210b,并且基材通孔开口210a和210b可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。

333.更详细地,作为示例而非限制,在基材210中以大于约5的高深宽比形成基材通孔开口210a和110b。在限定基材通孔开口210a和210b时,在基材210上方形成硬遮罩层(未绘示),随后在其上形成图案化的光阻层(未绘示)。作为示例而非限制,硬遮罩层可以是氮化硅层、氮氧化硅层等。透过曝光、烘烤、显影和/或其他微影制程将光阻层图案化以提供暴露硬遮罩层的开口。然后,透过湿式蚀刻或干式蚀刻制程,使用图案化的光阻层作为遮罩元件来提供开口以蚀刻暴露的硬遮罩层。使用硬遮罩层和图案化的光阻层作为遮罩元件,执行蚀刻制程以蚀刻暴露的基材210,从而形成穿过基材210的基材通孔开口210a和210b。

334.在部分实施例中,可以使用任何合适的蚀刻方法(例如,电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程)来蚀刻基材通孔开口210a和210b。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材210。蚀刻制程可以从晶片w2的背表面210d蚀刻大约数十微米到数百微米的深度而形成基材通孔开口210a和210b。在部分实施例中,蚀刻制程可能会导致在与基材通孔开口210a和210b的侧壁相邻的基材210上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口210a和/

或210b的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口210a和/或210b的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口210a和/或210b的深宽比可以大于约10。在部分实施例中,在基材210中产生具有高深宽比的基材通孔开口210a和/或210b时,可能会在基材210的侧壁上形成一系列蚀刻的大扇贝形(未绘示),其根据制程参数的不同,可能会有不同的尺寸。微扇贝形侧壁将在随后的热氧化过程中被平滑化。在部分实施例中,基材通孔开口210a和/或210b具有如图2所示的矩形的平面轮廓(或俯视图轮廓)。亦或是,基材通孔开口210a和/或210b可以具有圆形横截面。

335.返回图24,方法m2然后进行到方框s211,其中在基材通孔开口中形成基材通孔。参考图35,在方框s211的部分实施例中,基材通孔298a和/或298b形成在基材210的基材通孔开口210a和/或210b中并与p型井区216和/或n型井区218接触。在部分实施例中,基材通孔298a和/或298b可以作为传导路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片w2的前侧不形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔298a和/或298b可以作为晶片w2的散热器,以将半导体元件产生的热量从井区释放到晶片w2的外部。

336.更详细地,透过使用金属化制程以及使用金属电镀技术填充高深宽比开口以避免接缝或空隙缺陷来形成基材通孔298a和/或298b。在部分实施例中,为了避免金属从基材通孔金属扩散到硅基材中,在绝缘层和基材通孔金属之间使用阻挡层(未绘示)。阻挡层可以作为基材通孔开口210a和/或210b的衬垫。阻挡层作为防止金属扩散的扩散阻挡层,并且作为金属与介电质之间的粘合层。作为示例但非限制,阻挡层可使用难熔金属、难熔金属氮化物、难熔金属硅氮化物及其组合(例如,氮化钽(tan)、钽(ta)、钛(ti)、氮化钛(tin)、氮硅化钛(tisin)、氮化钨(wn)或其组合)。在部分实施例中,阻挡层可以包括氮化钽(tan)层和钽(ta)层。在部分实施例中,阻挡层是氮化钛(tin)层。在部分实施例中,阻挡层是钛(ti)层。在部分实施例中,接着在阻挡层上形成金属晶种层(未绘示)。在部分实施例中,作为示例但非限制,金属晶种层是铜晶种层,此铜晶晶层可以透过物理气相沉积的方式形成。

337.然后,可以将晶片w1转移到电镀工具(例如,电化学电镀工具)并且透过电镀制程在晶片w1上电镀导电层以填充基材通孔开口210a和/或210b。尽管在此描述了电化学电镀制程,然而实施例并不限于电化学电镀沉积的金属。作为示例而非限制,导电层可以包括选自铜和铜基合金的导体材料的群组的低电阻率的导体材料。亦或是,导电层可以包括各种材料(例如,钨、钌、铝、金、银等)。在部分实施例中,导电层是形成在铜晶种层上方的含铜层。

338.随后,透过蚀刻、化学机械平坦化等去除导电层、金属晶种层和阻挡层的多余部分,从而使金属填充开口的顶表面与基材210的背表面210d实质上齐平。在基材通孔开口210a和/或210b中的导电层和阻挡层的其余部分形成基材通孔298a和/或298b。

339.基材通孔298a与p型井区216接触,而基材通孔298b与n型井区218接触。当发生静电放电事件时,基材通孔298a和/或298b用以提供导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。在部分实施例中,基材通孔298a和/或298b也可以被称为静电放电保护电路。

340.返回图24,方法m2然后前进到方框s212,其中形成后段制程型互连堆叠和后段制

程型互连堆叠上的端子以连接基材通孔。参考图36,在方框s212的部分实施例中,形成后段制程型互连堆叠250以及后段制程型互连堆叠250上方的端子vdd和vss以连接基材通孔298a和/或298b。更详细地,执行一系列镶嵌制程步骤以产生后段制程型互连堆叠250,此后段制程型互连堆叠250透过低电阻电路将基材通孔298a和298b连接至晶片w2的背面上的端子vdd和vss。在部分实施例中,后段制程型互连堆叠250也可以被称为晶片w2的电力输送网络。

341.图37至图50绘示根据本公开的部分实施例在制造晶片w3的各个阶段中的方法。用于形成晶片w3的在图37所示结构之前的操作与在图25至图27中方法m2的方框s201至s203中所示的用于形成晶片w2的操作实质上相同,因此可以参考前述段落中的相关详细描述,在此不再赘述。例如,基材310、p型井区316、n型井区318、半导体鳍片352、353、354和355、遮罩层330和隔离介电质360的材料和制造方法可以与如图25至图27所示的基材210、p型井区216、n型井区218、半导体鳍片252、253、254和255、遮罩层230和隔离介电质260实质上相同,因此相关的详细描述可以参考前述段落,在此不再赘述。本实施例与图25至图27中的实施例之间的区别在于,本实施例的附加的半导体鳍片356、357和358从基材310向上延伸,并且半导体鳍片356、357和358的材料和制造方法可以与半导体鳍片352、353、354和355实质上相同。

342.参考图37。在隔离介电质360上方形成图案化的遮罩层369。在部分实施例中,透过旋涂光阻剂材料,然后进行诸如软烘烤制程和硬烘烤制程(也可以称为曝光前烘烤)的制程来形成遮罩层369(例如,遮罩层也可以被称为光阻层)。在部分实施例中,遮罩层369是深紫外光光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层是i

‑

line光阻剂、极紫外光光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂,其包含受酸不稳定基团保护的主链聚合物并且还包含光酸产生剂。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂的溶解度。在部分实施例中,遮罩层369是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

343.在隔离介电质360上涂覆遮罩层369之后,遮罩层369透过遮罩暴露于辐射。在完成将遮罩层369暴露于辐射之后,暴露的遮罩层369经历一个或多个曝光后烘烤制程。然后,执行显影制程,从而去除部分暴露的遮罩层369,以暴露在半导体鳍片352和356之间和在半导体鳍片357和358之间的部分的隔离介电质360。遮罩层369可以作为蚀刻遮罩以保护隔离介电质360的其余部分免受随后蚀刻制程的影响。

344.参考图38。透过遮罩层369对隔离介电质360进行蚀刻制程,以形成延伸穿过隔离介电质360进入基材310的沟槽360a和360b。当蚀刻制程完成后,所形成的沟槽360a和360b的底部位置在基材310中,并且与p型井区316和n型井区318的最低边界齐平。在部分实施例中,沟槽360a和360b的底部位置可能会低于p型井区316和n型井区318的最低边界的位置。在部分实施例中,沟槽360a和360b的底部位置可能会高于p型井区316和n型井区318的最低边界的位置。作为示例而非限制,井区316和/或318中的沟槽360a和/或360b的深度t4在大约30纳米至大约200纳米范围内。

345.在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或

原子层蚀刻制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6))、含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

346.参考图39。导电材料370形成在隔离介电质360上方并填充在沟槽360a和360b中。在部分实施例中,导电材料370可以包括金属(例如,钨(w)、钌(ru)、铝(al)、铜(cu)或其他合适的导电材料)。在部分实施例中,可以透过化学气相沉积、物理气相沉积、溅镀沉积或适合于沉积导电材料的其他技术来沉积导电材料370。

347.参考图40。对导电材料370进行平坦化制程。在部分实施例中,可以执行诸如化学机械平坦化的平坦化制程以去除在隔离介电质360上多余的导电材料370。在部分其他实施例中,当隔离介电质360被暴露时,停止平坦化制程。在这样的实施例中,隔离介电质360可以在平坦化中充当化学机械平坦化停止层。

348.参考图41。在沟槽360a和360b中将导电材料370蚀刻至给定的深度,以在沟槽360a和360b中留下一部分的导电材料370,从而使埋入式电源轨370a和370b形成在这个高度。在部分实施例中,埋入式电源轨370a和370b也可以被称为导电轨370a和370b。在部分实施例中,埋入式电源轨370a和/或370b也可以被称为供电电源轨和/或接地参考轨。例如,埋入式电源轨370a可以被称为接地参考轨,并且埋入式电源轨370b可以被称为供电电源轨。如图2所示的埋入式电源轨170a和/或170b,埋入式电源轨370a和/或370b沿着半导体鳍片352至358的长度方向延伸。在部分实施例中,导电材料370的变薄可以包括干式蚀刻制程或其他合适的蚀刻制程。在部分实施例中,蚀刻制程包括选择使用会蚀刻导电材料370而不会显著地蚀刻周围的结构(即,隔离介电质360)的技术和蚀刻剂。

349.在图41中,埋入式电源轨370a和/或370b的底表面位置与p型井区316和/或n型井区318的最低边界齐平。在部分实施例中,埋入式电源轨370a和/或370b的底表面位置可能会低于p型井区316和/或n型井区318的最低边界。在部分实施例中,埋入式电源轨370a和/或370b的底部位置可能会高于p型井区316和/或n型井区318的最低边界。

350.在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或原子层蚀刻制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、三氟化氮(nf3)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6)和/或八氟环丁烷(c4f8))、含氯气体(例如,氯气(cl2)、盐酸(hcl)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

351.参考图42。隔离介电质365形成在隔离介电质360上方,并填充在沟槽360a和360b中以位在在埋入式电源轨370a和370b上。沟槽360a和360b中的隔离介电质365可以被称为浅沟槽隔离结构。在部分实施例中,隔离介电质365由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃或其他低介电常数介电质材料形成。在部分实施例中,隔离介电质365具有与隔离介电质360不同的材料。在部分实施例中,隔离介电质365具有与隔离介电质360相同的材料。

352.在部分实施例中,可以使用高密度电浆化学气相沉积制程,使用硅甲烷(sih4)和

氧气(o2)作为反应前驱物来形成隔离介电质365。在部分其他实施例中,可以使用次大气压的化学气相沉积制程或高深宽比制程来形成隔离介电质365,其中制程气体可以包括四乙氧基硅烷(teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(例如,含氢硅氧烷(hsq)或甲基硅氧烷(msq))制程来形成隔离介电质365。亦可以使用其他制程和材料。在部分实施例中,隔离介电质365可以具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。之后,可以可选地对隔离介电质365执行热退火。

353.参考图43。去除隔离介电质360上方的隔离介电质365。在部分实施例中,可以执行诸如化学机械平坦化的平坦化制程以去除在隔离介电质360上方过量的隔离介电质365。在部分其他实施例中,当暴露隔离介电质360时,停止平坦化制程。在这样的实施例中,隔离介电质360可以在平坦化中充当化学机械平坦化停止层。在部分其他实施例中,当暴露遮罩层330时,停止平坦化制程。在这样的实施例中,遮罩层330可以在平坦化中充当化学机械平坦化停止层。在部分实施例中,平坦化制程还可以去除遮罩层330,以暴露半导体鳍片352至358的顶表面。

354.参考图44。例如,透过蚀刻操作使隔离介电质360和365凹陷,其中可以将稀释的氢氟酸、硅钴镍(siconi)(包括氢氟酸(hf)和氨(nh3))等作为蚀刻剂。在使隔离介电质365凹陷之后,部分的半导体鳍片352至358高于隔离介电质360的顶表面并且高于隔离介电质365的顶表面。接着,形成栅极(未绘示)(例如,图2所示的栅极结构182和184),其可以透过诸如替换栅极技术来完成。所形成的栅极垂直于半导体鳍片352至358。

355.参考图45。在半导体鳍片353、354、356和357上形成源极/漏极特征373、374、376和377。更详细地,在半导体鳍片352至358上形成图案化的遮罩层(未绘示)。在部分实施例中,透过旋涂光阻材料,然后进行诸如软烘烤制程和硬烘烤制程(也可以称为曝光前烘烤)的制程来形成遮罩层(例如,遮罩层也可以被称为光阻层)。在部分实施例中,遮罩层是深紫外光光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层是i

‑

line光阻剂、极紫外光光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂,其包含受酸不稳定基团保护的主链聚合物并且还包含光酸产生剂。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂的溶解度。在部分实施例中,遮罩层是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

356.在半导体鳍片352至358上涂覆遮罩层之后,遮罩层透过遮罩暴露于辐射。在将遮罩层暴露于辐射之后,对暴露的遮罩层进行一个或多个曝光后烘烤制程。然后,执行显影制程,从而去除暴露的遮罩层的一部分,并且此遮罩层作为遮罩以保护半导体鳍片352、355和358免受随后的磊晶生长制程的影响。当蚀刻制程完成时,形成沟槽以穿过遮罩层并暴露半导体鳍片353、354、356和357以及隔离介电质360的顶表面。在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或原子层蚀刻制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6))、含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

357.然后,可以透过执行磊晶生长制程来形成源极/漏极特征373、374、376和377,此磊晶生长制程提供覆盖部分的半导体鳍片353、354、356和357的磊晶材料363、364、366和367。源极/漏极特征373、374、376和377包括材料363、364、366和367,此材料透过在暴露的半导体鳍片353、354、356和357上磊晶生长半导体材料而形成。换句话说,在半导体鳍片353、354、356和357的周围形成材料363、364、366和367;可将此称为在半导体鳍片353、354、356和357周围形成“包覆层”。因此,源极/漏极特征373、374、376和377包括半导体鳍片353、354、356和357和所形成的磊晶生长的材料363、364、366和367。应理解,可以在不使半导体鳍片353、354、356和357凹陷的情况下形成这些特征。在形成源极/漏极特征373、374、376和377之后,去除覆盖半导体鳍片353、354、356和357的图案化的遮罩层。

358.在各个实施例中,生长的半导体材料363、364、366和367可以包括锗(ge)、硅(si)、砷化镓(gaas)、砷化镓铝(algaas)、硅锗(sige)、磷化砷镓(gaasp)、硅磷(sip)或其他合适的材料。在部分实施例中,材料363、364、366和367可以在磊晶制程期间被原位掺杂。例如,在部分实施例中,磊晶生长的材料363、364、366和367可以掺杂有硼。在部分实施例中,磊晶生长的材料363、364、366和367可以掺杂有碳以形成硅:碳(si:c)源极/漏极特征,掺杂有磷以形成硅:磷(si:p)源极/漏极特征,或掺杂有碳和磷两者以形成硅碳磷(sicp)源极/漏极特征。在一个实施例中,半导体鳍片353、354、356和357由硅形成,并且磊晶生长的材料363、364、366和367也由硅形成。在部分实施例中,半导体鳍片353、354、356和357以及磊晶生长的材料363、364、366和367可以包括相似的材料,但是被不同地掺杂。在其他实施例中,半导体鳍片353、354、356和357包括第一半导体材料,磊晶生长的材料363、364、366和367包括与第一半导体材料不同的第二半导体。在部分实施例中,磊晶生长的材料363、364、366和367不是原位掺杂的,而是,例如,执行布植制程来掺杂磊晶生长的材料363、364、366和367。

359.在部分实施例中,在形成源极/漏极特征373、374、376和377之前,形成横跨半导体鳍片352至358并包括栅极介电质和在栅极介电质上的栅极的栅极结构(未绘示)。在部分实施例中,为了形成虚设栅极结构,在半导体鳍片353、354、356和357上方形成栅极介电层,接着形成虚设栅极层。然后,对栅极介电层和虚设栅极层进行图案化,以分别形成栅极介电质和栅极。出于制程原因,可以在虚设栅极结构上形成硬遮罩,其中,硬遮罩可以包括氮化硅。半导体鳍片353、354、356和357的通道部分被虚设栅极结构覆盖,并且半导体鳍片353、354、356和357的源极/漏极部分未被虚设栅极结构覆盖。换句话说,虚设栅极结构形成在半导体鳍片353、354、356和357的通道部分上方。

360.参考图46a。在源极/漏极特征373、374、376和377以及虚设栅极结构上方形成层间介电层372。也就是说,在稍后执行的制程期间,源极/漏极特征373、374、376和377被层间介电层372覆盖和保护。此外,层间介电层372形成在虚设栅极结构上方。然后,执行化学机械平坦化制程以去除部分的层间介电层372。在化学机械平坦化制程期间,虚设栅极结构被暴露。层间介电层372的其余部分覆盖源极/漏极特征373、374、376和377。层间介电层372可以包括氧化硅、氮氧化物或其他合适的材料。

361.在部分实施例中,采用替换栅极制程方案。在替换栅极制程方案中,预先形成虚设栅极结构并且之后由金属栅极代替。可以透过干式蚀刻、湿式蚀刻或干式和湿式蚀刻的组合来去除虚设栅极结构。例如,湿式蚀刻制程可以包括暴露于含氢氧化物的溶液(例如,氢氧化铵)、去离子水和/或其他合适的蚀刻剂溶液。金属栅极可以包括金属、金属合金和/或

金属硅化物。另外,金属栅极的形成可以包括沉积制程以形成各种栅极材料、一个或多个衬垫层,以及一种或多种化学机械平坦化制程以去除过量的栅极材料并由此平坦化金属栅极的顶表面。

362.在图46a中,形成穿过隔离介电质365并位在埋入式电源轨370b上的导电通孔378。将导电接触379a和379b形成在源极/漏极特征377和376上。在图46a中,形成在层间介电层372中的导电接触379b透过导电通孔378进一步连接到埋入式电源轨370b。在另一视图中,导电接触379a还连接到埋入式电源轨370a。

363.图46b绘示根据本公开的部分其他实施例的处于对应于图46a的阶段的另一晶片,其绘示源极/漏极特征376和埋入式电源轨370b之间的互连的不同轮廓。如图46b所示,透过用第一图案化的遮罩层蚀刻层间介电层372和隔离介电质365来形成从层间介电层372的顶表面垂直地向下延伸到埋入式电源轨370b的沟槽372a。此外,透过用第二图案化的遮罩层蚀刻层间介电层372来形成从层间介电层372的顶表面向下延伸至源极/漏极特征376和377的沟槽372b和372c。在图46b中,沟槽372b和372c的底部位于比源极/漏极特征376和377的最大宽度高的位置。在部分实施例中,沟槽372b和372c的底部可以位于比源极/漏极特征376和377的最大宽度低并高于隔离介电质360的顶表面的位置。在部分实施例中,沟槽372b和372c的底部可以与隔离介电质360的顶表面齐平。然后,形成导电材料以填充层间介电层372的沟槽372a、372b和372c,以形成将源极/漏极特征376连接到埋入式电源轨370b的互连371b和将源极/漏极特征377连接到埋入式电源轨370a的互连371c。

364.参考图47。透过在半导体晶片上进行前段制程和后段制程来制造晶片w3,此前段制程包括上述步骤。如上所述,将埋入式电源轨370a/370b连接到vdd、vss、导电通孔378以及导电接触379a和379b。后段制程堆叠390形成在基材310上方并且以示意性方式示出,而没有详细地描述互连。使用后段制程形成后段制程堆叠190。后段制程包括在晶片w1中的装置结构之间形成金属布线以使它们互连,其包括形成接触、互连线、通孔结构和介电结构。然后,在后段制程堆叠390上方形成结合层392。在部分实施例中,结合层392可以包括氧化硅、氮碳化硅(sicn)或在现有技术封装技术中应用的直接接合技术中适用的任何其他材料。

365.参考图48。晶片w3透过结合层392结合到载体基材394。在部分实施例中,载体基材394上还设置有结合层396。结合层396可以包括氧化硅、氮碳化硅(sicn)或在现有技术封装技术中应用的直接接合技术中适用的任何其他材料。透过直接接合技术将晶片w3结合到载体基材394,从而获得如图48所示的结合的晶片堆叠。

366.在部分实施例中,作为示例而非限制,在结合晶片w3之后,可以透过研磨和/或湿式或干式蚀刻技术的方式使晶片w3的基材310变薄。作为示例而非限制,剩余的基材厚度在约50纳米至约500纳米的范围内。在部分实施例中,作为示例而非限制,接着使厚度进一步减小,直到半导体的厚度为约1微米。在部分实施例中,可以透过将可以充当蚀刻停止层的掺杂层加入到装置晶片中来实现变薄。作为示例而非限制,然后执行在掺杂层上停止的选择性湿式蚀刻步骤,以将半导体晶片减薄至所需的约1微米的厚度。

367.在图48中,形成贯穿基材310直到到达连接到电源或接地的埋入式电源轨370a和/或370b的基材通孔开口310a和/或310b。形成贯穿基材310直到到达p型井区316和/或n型井区318的基材通孔开口310c和/或310d,并且基材通孔开口310c和/或310d可以作为传导路

径,以在发生静电放电事件时减小高电流和电流密度,以避免电路崩溃。

368.更详细地,作为示例而非限制,在基材310中以大于约5的高深宽比形成基材通孔开口310a、310b、310c和/或310d。在限定基材通孔开口310a、310b、310c和/或310d时,在基材310上方形成硬遮罩层(未绘示),随后在其上形成图案化的光阻层(未绘示)。作为示例而非限制,硬遮罩层可以是氮化硅层、氮氧化硅层等。透过曝光、烘烤、显影和/或其他微影制程将光阻层图案化以提供暴露硬遮罩层的开口。然后,透过湿式蚀刻或干式蚀刻制程,使用图案化的光阻层作为遮罩元件来蚀刻暴露的硬遮罩层,以提供开口。使用硬遮罩层和图案化的光阻层作为遮罩元件,执行蚀刻制程以蚀刻暴露的基材310,从而形成穿过基材310的基材通孔开口310a、310b、310c和/或310d。埋入式电源轨370a和370b亦可以作为蚀刻基材310的蚀刻停止层,直到暴露出埋入式电源轨370a和370b。因为基材通孔开口310a、310b、310c和/或310d同时形成,所以基材通孔开口310c和/或310d的底部可以与基材通孔开口310a和/或310b的底部齐平,并且可以与透过基材通孔开口310a和/或310b而暴露的电源轨370a和/或370b的表面齐平。

369.在部分实施例中,可以使用任何合适的蚀刻方法来蚀刻基材通孔开口310a、310b、310c和/或310d,所述方法包括例如电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材310。蚀刻制程可以从晶片w3的背表面310e蚀刻大约几十微米到几百微米的深度而形成基材通孔开口310a、310b、310c和/或310d。在部分实施例中,蚀刻制程可能会导致在与基材通孔开口310a、310b、310c和/或310d的侧壁相邻的基材310上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口310a、310b、310c和/或310d的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口110a、110b和/或110c的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口310a、310b、310c和/或310d的深宽比可以大于约10。在部分实施例中,在基材310中建立具有高深宽比的基材通孔开口310a、310b、310c和/或310d时,可能会在基材310的侧壁上形成一系列蚀刻的大扇贝形(未绘示)(其可以根据制程参数改变尺寸)。微扇贝形侧壁将在随后的热氧化过程中被平滑化。

370.在部分实施例中,基材通孔开口310a、310b、310c和/或310d具有如图2所示的矩形的平面图轮廓(或俯视图轮廓),其宽度小于埋入式电源轨370a和370b的宽度。在部分实施例中,基材通孔开口310a、310b、310c和/或310d的宽度大于埋入式电源轨370a和370b的宽度。亦或是,基材通孔开口310a、310b、310c和/或310d可以具有圆形的平面图轮廓,其直径小于埋入式电源轨370a和370b的宽度。在部分实施例中,基材通孔开口310a、310b、310c和/或310d的直径大于埋入式电源轨370a和370b的宽度。

371.参考图49。在基材310的基材通孔开口310a、310b、310c和310d中形成基材通孔398a、398b、398c和398d。如图49所示,在基材310的基材通孔开口110a和/或110b中形成基材通孔398a和/或398b,并使其与埋入式电源轨370a和/或370b接触以连接至电源或接地。基材通孔398c和/或398d形成在基材通孔开口310c和/或310d中,并与p型井区316和/或n型井区318接触。在部分实施例中,基材通孔398c和/或398d可作为传导路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片w3的正面不形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔

398c和/或398d可以作为晶片w3的散热器,以将由半导体元件产生的热量从井区释放到晶片w3的外部。

372.更详细地,透过使用金属化制程以及使用金属电镀技术填充高深宽比开口以避免接缝或空隙缺陷来形成基材通孔398a、398b、398c和/或398d。在部分实施例中,为了避免金属从基材通孔金属扩散到硅基材中,在绝缘层和基材通孔金属之间使用阻挡层(未绘示)。阻挡层可以作为基材通孔开口310a、310b、310c和/或310d的衬垫。阻挡层可作为防止金属扩散的扩散阻挡层,并且可作为在金属与介电质之间的粘合层。作为示例但非限制,阻挡层可以是难熔金属、难熔金属氮化物、难熔金属硅氮化物及其组合(例如,氮化钽(tan)、钽(ta)、钛(ti)、氮化钛(tin)、氮硅化钛(tisin)、氮化钨(wn)或其组合)。在部分实施例中,阻挡层可以包括氮化钽(tan)层和钽(ta)层。在部分实施例中,阻挡层是氮化钛(tin)层。在部分实施例中,阻挡层是钛(ti)层。在部分实施例中,接着在阻挡层上形成金属晶种层(未绘示)。在部分实施例中,作为示例而非限制,金属晶种层是铜晶种层,此铜晶种层可以透过物理气相沉积的方式形成。

373.然后,可以将晶片w3转移到电镀工具(例如,电化学电镀工具),并且透过电镀制程在晶片w3上电镀导电层以填充基材通孔开口310a、310b、310c和/或310d。尽管本公开描述了电化学电镀制程,但是实施例并不限于电化学电镀沉积的金属。导电层可以包括选自包括但不限于铜和铜基合金的导体材料的群组的低电阻率的导体材料。亦或是,导电层可以包括各种材料(例如,钨、钌、铝、金、银等)。在部分实施例中,导电层是形成在铜晶种层上方的含铜层。

374.随后,透过蚀刻、化学机械平坦化等去除导电层、金属晶种层和阻挡层的多余部分,从而使金属填充的开口的上表面实质上与基材310的背表面310e共平面。在基材通孔开口310a、310b、310c和/或310d中的导电层和阻挡层的其余部分形成基材通孔398a、398b、398c和/或398d。

375.基材通孔398c和/或398d与p型井区316和/或n型井区318接触并且电耦合在埋入式电源轨370a和370b之间。当在埋入式电源轨370b上发生静电放电事件时,基材通孔398c和/或398d用以在埋入式电源轨370a和370b之间提供导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。在部分实施例中,基材通孔398c和/或398d也可以被称为静电放电保护电路。

376.参考图50。形成后段制程型互连堆叠350以及后段制程型互连堆叠350上的端子vdd和vss以连接埋入式电源轨370a和370b以及基材通孔398c和/或398d。更详细地,执行一系列镶嵌制程步骤以产生后段制程型互连堆叠350,其透过低电阻电路将基材通孔398a、398b、398c和398d连接至晶片w3背面上的端子vdd和vss。在部分实施例中,后段制程型互连堆叠350也可以被称为晶片w3的电力输送网络。

377.图51至图56绘示根据本公开的部分实施例的在制造晶片w4的各个阶段中的方法。用于形成晶片w4的在图51所示结构之前的操作与在图37至图47所示的用于形成晶片w3的操作实质上相同,因此相关的详细描述可以参考前述段落,在此不再赘述。例如,基材410、p型井区416、n型井区418、半导体鳍片452至458和隔离介电质460、源极/漏极特征473、474、476和477、层间介电层476、后段制程堆叠490、结合层492和载体基材494的材料和制造方法可以与如图37至图47所示的基材310、p型井区316、n型井区318、半导体鳍片352至358和隔

离介电质360、源极/漏极特征373、374、376和377、层间介电层372、后段制程堆叠390、结合层392和载体基材394实质上相同,因此相关的详细描述可以参考前述段落,在此不再赘述。本实施例与图37至图47所示的实施例之间的区别在于在本实施例中省略了在图37至图47所示的晶片w3的埋入式电源轨370a和370b、导电通孔378以及导电接触379a和379b。

378.参考图51。在基材410的背表面410e上方形成图案化的遮罩层469。在部分实施例中,透过旋涂光阻剂材料,然后进行诸如软烘烤制程和硬烘烤制程(也可以称为曝光前烘烤)的制程来形成遮罩层469(例如,遮罩层也可以被称为光阻层)。在部分实施例中,遮罩层469是深紫外光光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层469是i

‑

line光阻剂、极紫外光光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层469是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂,其包含受酸不稳定基团保护的主链聚合物并且还包含光酸产生剂。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂的溶解度。在部分实施例中,遮罩层469是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

379.在基材410上方涂覆遮罩层469之后,遮罩层469透过遮罩暴露于辐射。在完成将遮罩层469暴露于辐射之后,暴露的遮罩层469经历一个或多个曝光后烘烤制程。然后,执行显影制程,以去除部分的暴露的遮罩层469,以暴露在p型井区416和n型井区418正上方的部分的材310。遮罩层469可以作为刻蚀遮罩,以保护基材410的其余部分免受随后的蚀制程的影响。

380.然后,在基材410中形成穿过遮罩层469直到到达p型井区416和n型井区418的基材通孔开口410b和/或410c,并且此基材通孔开口410b和/或410c可以作为导电路径,从而可以在静电放电事件期间减轻高电流和电流密度,以避免电路崩溃。更详细地,作为示例而非限制,在基材410中形成具有大于约5的高深宽比的基材通孔开口410b和/或410c。

381.在部分实施例中,可以使用任何合适的蚀刻方法来蚀刻基材通孔开口410b和/或410c,所述的合适的蚀刻方法包括诸如电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材410。蚀刻制程可以从晶片w4的背表面410e蚀刻大约几十微米到几百微米的深度而形成基材通孔开口410b和/或410c。在部分实施例中,蚀刻制程可导致在与基材通孔开口410b和/或410c的侧壁相邻的基材410上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口410b和/或410c的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口410b和/或410c的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口410b和/或410c的深宽比可大于约10。在部分实施例中,在基材410中创建具有高深宽比的基材通孔开口410b和/或410c时,可以在基材410的侧壁上形成一系列蚀刻的大扇贝形(未绘示),其根据制程参数的不同,可能会有不同的尺寸。微扇贝形侧壁将在随后的热氧化过程中被平滑化。在部分实施例中,基材通孔开口410b和/或410c具有如图2所示的矩形平面视图轮廓(或俯视图轮廓)。亦或是,基材通孔开口410b和/或410c可以具有圆形横截面。在形成基材通孔开口410b和/或410c之后,去除遮罩层469。

382.参照图52。可以形成介电质材料467(例如,旋转涂布玻璃(spin

‑

on

‑

glass,sog)),

以覆盖基材410的背表面410e并填充基材通孔开口410b和/或410c。介电质材料467可以透过诸如旋转涂布制程、微影制程和蚀刻制程来限定。在部分实施例中,介电质材料467可以由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃或其他低介电常数介电质材料制成。在部分实施例中,可以使用高密度电浆化学气相沉积制程,使用硅甲烷(sih4)和氧气(o2)作为反应前驱物来形成介电质材料467。在部分其他实施例中,介电质材料467可以使用次大气压的化学气相沉积制程或高深宽比制程形成,其中制程气体可以包括四乙氧基硅烷(teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(例如,含氢硅氧烷(hsq)或甲基硅氧烷(msq))制程来形成介电质材料467。亦可以使用其他制程和材料。在部分实施例中,介电质材料467可以具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。之后,可以可选地对介电质材料467执行热退火。

383.参考图53。在介电质材料467上形成图案化的光阻层468。然后,执行穿过图案化的光阻层的蚀刻制程,从而形成穿过基材410和隔离介电质460以到达后段制程堆叠490中的互连的基材通孔开口410a。在部分实施例中,蚀刻制程是各向异性干式蚀刻制程(例如,反应离子蚀刻制程或原子层蚀刻制程)。作为示例而非限制,干式刻蚀制程可以使用含氧气体、含氟气体(例如,四氟化碳(cf4)、六氟化硫(sf6)、二氟甲烷(ch2f2)、三氟甲烷(chf3)和/或六氟乙烷(c2f6))、含氯气体(例如,氯气(cl2)、三氯甲烷(chcl3)、四氯化碳(ccl4)和/或三氯化硼(bcl3))、含溴气体(例如,溴化氢(hbr)和/或溴甲烷(chbr3))、含碘气体、其他合适的气体和/或电浆和/或其组合。

384.参考图54。在形成基材通孔开口410a之后,去除介电质材料467和光阻层468。

385.参考图55。在基材通孔开口410a、410b和410c中形成基材通孔498a、498b或498c。如图55所示,基材通孔498a形成在基材410的基材通孔开口410a中并与后段制程堆叠490中的互连接触。基材通孔498b和/或498c形成在基材通孔开口410b和/或410c中并且与p型井区416和/或n型井区418接触。在部分实施例中,基材通孔498b和/或498c可以作为传导路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片w4的正面上不形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔498b和/或498c可以作为晶片w4的散热器,以将由半导体元件产生的热量从井区释放到晶片w4的外部。

386.更详细地,透过使用金属化制程以及使用金属电镀技术填充高深宽比开口以避免接缝或空隙缺陷来形成基材通孔498a、498b和/或498c。在部分实施例中,为了避免金属从基材通孔金属扩散到硅基材中,在绝缘层和基材通孔金属之间使用阻挡层(未绘示)。阻挡层可以作为基材通孔开口410a、410b和/或410c的衬垫。阻挡层作为防止金属扩散的扩散阻挡层,并且作为金属与介电质之间的粘合层。作为示例但非限制,阻挡层可以使用难熔金属、难熔金属氮化物、难熔金属硅氮化物及其组合(例如,氮化钽(tan)、钽(ta)、钛(ti)、氮化钛(tin)、氮硅化钛(tisin)、氮化钨(wn)或其组合)。在部分实施例中,阻挡层可以包括氮化钽(tan)层和钽(ta)层。在部分实施例中,阻挡层是氮化钛(tin)层。在部分实施例中,阻挡层是钛(ti)层。在部分实施例中,接着在阻挡层上形成金属晶种层(未绘示)。在部分实施例中,作为示例而非限制,金属晶种层是铜晶种层,此铜晶种层可以透过物理气相沉积的方式形成。

387.然后,可以将晶片w4转移到电镀工具(例如,电化学电镀工具),并透过电镀制程在

晶片w4上电镀导电层以填充基材通孔开口410a、410b和/或410c。尽管本公开描述了电化学电镀制程,但是实施例不限于电化学电镀沉积的金属。导电层可以包括选自包括但不限于铜和铜基合金的导体材料的群组的低电阻率的导体材料。亦或是,导电层可以包括各种材料(例如,钨、钌、铝、金、银等等)。在部分实施例中,导电层是形成在铜晶种层上方的含铜层。

388.随后,透过蚀刻、化学机械平坦化等去除导电层、金属晶种层和阻挡层的多余部分,从而使金属填充的开口的上表面实质上与基材410的背表面410e共平面。在基材通孔开口410a、410b和/或410c中的导电层和阻挡层的其余部分实质上形成基材通孔498a、498b和/或498c。

389.基材通孔498b和/或498c与p型井区416和/或n型井区418接触,并且电连接至与后段制程堆叠490连接的基材通孔498a。当在基材通孔498a上发生静电放电事件时,基材通孔498b和/或498c用以向基材通孔498a提供通导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。在部分实施例中,基材通孔498b和/或498c也可以被称为静电放电保护电路。

390.参考图56。形成后段制程型互连堆叠450以及后段制程型互连堆叠450上的端子vdd和vss以连接基材通孔498a、498b和498c。更详细地,执行一系列镶嵌制程步骤以产生后段制程型互连堆叠450,其透过低电阻电路将基材通孔498a、498b和498c连接至在晶片w4的背面上的端子vdd和vss。在部分实施例中,也可将后段制程型互连堆叠450称为晶片w4的电力输送网络。

391.图57至图63绘示根据本公开的部分实施例在制造晶片w5的各个阶段中的方法。用于形成晶片w5的在图57所示结构之前的操作与在图25至图33在方法m2的方框s201至s209所示的用于形成晶片w2的操作实质上相同,因此相关的详细描述可以参考前述段落,在此不再赘述。例如,基材510、p型井区516、n型井区518、半导体鳍片552、553、554和555、隔离介电质560、源极/漏极特征573和574、层间介电层576、后段制程堆叠590、结合层592、载体基材594和结合层596的材料和制造方法可以与在图25至图33中所绘示的基材210、p型井区216、n型井区218、半导体鳍片252、253、254和255、隔离介电质260、源极/漏极特征273和274、层间介电层276、后段制程堆叠290、结合层292、载体基材294、结合层296实质上相同,因此相关的详细描述可以参考前述段落,在此不再赘述。

392.参考图57。在基材510的背表面510e上形成图案化的遮罩层569。在部分实施例中,透过旋涂光阻剂材料,然后进行诸如软烘烤制程和硬烘烤制程(也可以称为曝光前烘烤)的制程来形成遮罩层569(例如,遮罩层也可以被称为光阻层)。在部分实施例中,遮罩层569是深紫外光光阻剂(例如,氟化氪(krf)光阻剂或氟化氩(arf)光阻剂)。在部分实施例中,遮罩层569是i

‑

line光阻剂、极紫外光光阻剂、电子束(e

‑

beam)光阻剂或离子束光阻剂。在部分实施例中,遮罩层569是正型光阻剂。正型光阻剂不溶于显影剂,但在辐射下变为可溶的。一种示例性的正型光阻剂是化学性增强光阻剂,其包含受酸不稳定基团保护的主链聚合物并且还包含光酸产生剂。光酸产生剂可以在辐射时产生酸,并且此酸可以催化酸不稳定基团从主链聚合物上裂解,从而增加聚合物对正型显影剂的溶解度。在部分实施例中,遮罩层569是负型光阻剂。负型光阻剂可溶于显影剂,但在辐射下不溶。

393.在基材510上涂覆遮罩层569之后,遮罩层569透过遮罩暴露于辐射。在完成将遮罩

层569暴露于辐射之后,暴露的遮罩层469经历一个或多个曝光后烘烤制程。然后,执行显影制程,从而去除暴露的遮罩层569的部分以在n型井区518正上方暴露部分的基材510。遮罩层569可以作为蚀刻遮罩以保护基材510的其余部分免受随后的蚀刻制程的影响。

394.然后,在基材510中形成穿过遮罩层569直到到达n型井区518为止的基材通孔开口510b,并且此基材通孔开口510b可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。更详细地,作为示例而非限制,在基材510中以大于约5的高深宽比形成基材通孔开口510b。

395.在部分实施例中,可以使用任何合适的蚀刻方法来蚀刻基材通孔开口510b,所述的合适的蚀刻方法包括诸如电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材510。蚀刻制程可以是从晶片w5的背表面510e将基材通孔开口510b蚀刻至大约几十倍微米至数百微米的深度。在部分实施例中,蚀刻制程可以导致在与基材通孔开口510b的侧壁相邻的基材510上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口510b的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口510b的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口510b的深宽比可以大于约10。在部分实施例中,在基材510中形成具有高深宽比的基材通孔开口510b,会在基材510的侧壁上形成一系列蚀刻的大扇贝形(未绘示),其尺寸可以根据制程参数而变化。微扇贝形侧壁将在随后的热氧化过程中被平滑化。在部分实施例中,基材通孔开口510b具有如图2所示的矩形的平面轮廓(或俯视图轮廓)。亦或是,基材通孔开口510b可以具有圆形横截面。

396.在形成基材通孔开口510b之后,在由基材通孔开口510b暴露的n型井区518上形成掺杂层528,这可使将要在基材通孔开口510b中形成的基材通孔具有改善的欧姆接触。在部分实施例中,透过离子布植制程形成掺杂层528。作为示例而非限制,可以透过布植制程形成掺杂层528,此布植制程的剂量可以在大约1e14原子/厘米2至大约5e15原子/厘米2的范围内,并且其他剂量范围亦在本公开的范围内。作为示例而非限制,可以透过布植制程形成掺杂层528,此布植制程的剂量浓度可以在大约1e19原子/厘米3至大约2e21原子/厘米3的范围内,并且其他的剂量范围亦在本公开的范围内。在部分实施例中,透过选择性扩散形成掺杂层528。作为示例而非限制,掺杂层528可以包括n型掺杂剂(例如,磷(p)、砷(as)、锑(sb)或其组合)。在形成掺杂层528之后,去除遮罩层469。

397.参照图58。可以形成介电质材料567(例如,旋转涂布玻璃),以覆盖基材510的背表面510e并填充基材通孔开口510b。介电质材料567可以透过例如旋转涂布制程、微影制程和蚀刻制程来限定。在部分实施例中,介电质材料567可以由氧化硅、氮化硅、氮氧化硅、掺杂氟的硅酸盐玻璃或其他低介电常数介电质材料制成。在部分实施例中,可以使用高密度电浆化学气相沉积制程,使用硅甲烷(sih4)和氧气(o2)作为反应前驱物来形成介电质材料567。在部分其他实施例中,介电质材料567可以使用次大气压的化学气相沉积制程或高深宽比制程形成,其中制程气体可以包括四乙氧基硅烷(teos)和臭氧(o3)。在其他实施例中,可以使用旋涂介电质(例如,含氢硅氧烷(hsq)或甲基硅氧烷(msq))制程来形成介电质材料567。亦可以使用其他制程和材料。在部分实施例中,介电质材料567可以具有多层结构(例如,具有氮化硅形成在其上的热氧化衬垫层)。此后,可以可选地对介电质材料567执行热退

火。

398.参考图59。在介电质材料567上形成图案化的光阻层568。然后,透过图案化的光阻层568进行蚀刻制程,从而在基材510中形成穿过光阻层568直到到达p型井区516为止的基材通孔开口510a,并且此基材通孔开口510a可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。更详细地,作为示例而非限制,在基材510中以大于约5的高深宽比形成基材通孔开口510a。

399.在部分实施例中,可以使用任何合适的蚀刻方法来蚀刻基材通孔开口510a,所述的合适的蚀刻方法包括诸如电浆蚀刻、化学湿式蚀刻、激光钻孔和/或其他制程。在部分实施例中,蚀刻制程包括深反应离子蚀刻制程以蚀刻基材510。蚀刻制程可以使得从晶片w5的背表面510e蚀刻基材通孔开口510a以达到大约数十微米到数百微米的深度。在部分实施例中,蚀刻制程可能会导致在与基材通孔开口510a的侧壁相邻的基材510上的一系列蚀刻的大扇贝形。微扇贝形侧壁将在随后的制程中被平滑化。作为示例而非限制,基材通孔开口510a的深度在大约1微米至大约100微米的范围内,并且直径在大约0.1微米至大约10微米的范围内。作为示例而非限制,基材通孔开口510a的深宽比在大约5至大约10的范围内。在部分实施例中,基材通孔开口510a的深宽比可以大于约10。在基材510中形成具有高深宽比的基材通孔开口510a可能会在基材510的侧壁上形成一系列蚀刻的大扇贝形(未绘示),其尺寸可以根据制程参数而变化。微扇贝形侧壁将在随后的热氧化过程中被平滑化。在部分实施例中,基材通孔开口510a具有如图2所示的矩形的平面轮廓(或俯视图轮廓)。亦或是,基材通孔开口510a可以具有圆形横截面。

400.参考图60。在形成基材通孔开口510a之后,在由基材通孔开口510a暴露的p型井区516上形成掺杂层526,从而允许将在基材通孔开口510a中形成的基材通孔具有改善的欧姆接触。在部分实施例中,透过离子布植制程形成掺杂层526。作为示例而非限制,可以透过布植制程形成掺杂层526,此布植制程的剂量可以在大约1e14原子/厘米2至大约5e15原子/厘米2的范围内,并且其他剂量的浓度范围亦在本公开的范围内。作为示例而非限制,可以透过布植制程形成掺杂层526,此布植制程的剂量浓度可以在大约1e19原子/厘米3至大约2e21原子/厘米3的范围内,并且其他剂量的浓度范围亦在本公开的范围内。在部分实施例中,透过选择性扩散形成掺杂层526。作为示例而非限制,掺杂层526可包括p型掺杂剂(例如,硼(b)、镓(ga)或其组合)。在形成掺杂层526之后,去除介电质材料567和光阻层568。

401.参考图61。透过金属硅化制程在掺杂层526和/或528上形成硅化物层536和/或538。金属硅化制程是在金属和硅(或多晶硅)之间进行反应。在图61中,在掺杂层526和528上形成金属层。然后,关于金属硅化制程,可以在诸如氩气(ar)、氦气(he)、氮气(n2)或其他惰性气体中并在第一温度下(例如,低于200℃至300℃)进行第一快速热退火(first rapid thermal annealing,rta)制程,以将沉积的金属层转化为金属硅化物。随后进行蚀刻制程以从中去除未反应的金属层。蚀刻制程可以包括湿式蚀刻、干式蚀刻和/或它们的组合。作为示例,湿式蚀刻的蚀刻剂可以包括硫酸(h2so4)、双氧水(h2o2)、水(h2o)和/或其他合适的湿式蚀刻溶液和/或其混合溶液。然后,在高于第一温度的第二温度(例如,400℃至500℃)下进行第二退火或快速热退火步骤,从而形成具有低电阻的稳定的硅化物层536和/或538。在部分实施例中,硅化物层536和/或538可以包括硅化钛(tisi)、硅化镍(nisi)、硅化钴(cosi)、镍铂(ni

‑

pt)或它们的组合。

402.参考图62。基材通孔598a和598b形成在基材510的基材通孔开口510a和510b中,并与硅化物层536和538接触。在部分实施例中,基材通孔598a和598b可作为传导路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于在晶片w5的前表面上不形成静电放电装置,因此可以在减小几何尺寸的同时增加功能密度。在部分实施例中,基材通孔598a和598b可以作为晶片w5的散热器,以将由半导体元件产生的热量排放到晶片w5的外部。

403.更详细地,透过使用金属化制程以及使用金属电镀技术填充高深宽比开口以避免接缝或空隙缺陷来形成基材通孔598a和/或598b。在部分实施例中,为了避免金属从基材通孔金属扩散到硅基材中,在绝缘层和基材通孔金属之间使用阻挡层(未绘示)。阻挡层可以作为基材通孔开口510a和/或510b的衬垫。阻挡层作为防止金属扩散的扩散阻挡层,并且作为金属与介电质之间的粘合层。作为示例但非限制,难熔金属、难熔金属氮化物、难熔金属硅氮化物及其组合可用于阻挡层(例如,氮化钽(tan)、钽(ta)、钛(ti)、氮化钛(tin)、氮硅化钛(tisin)、氮化钨(wn)或其组合)。在部分实施例中,阻挡层可以包括氮化钽(tan)层和钽(ta)层。在部分实施例中,阻挡层是氮化钛(tin)层。在部分实施例中,阻挡层是钛(ti)层。在部分实施例中,然后在阻挡层上形成金属晶种层(未绘示)。在部分实施例中,金属晶种层是铜晶种层,此铜晶种层可以透过物理气相沉积的方式形成,但不限于此。

404.然后,可以将晶片w5转移到电镀工具(例如,电化学电镀工具),并且透过电镀制程在晶片w1上电镀导电层以填充基材通孔开口510a和/或510b。尽管在本公开中描述了电化学电镀制程,然而实施例并不限于电化学电镀沉积的金属。导电层可以包括选自包括但不限于铜和铜基合金的导体材料的群组的低电阻率的导体材料。亦或是,导电层可以包括各种材料(例如,钨、钌、铝、金、银等等)。在部分实施例中,导电层是形成在铜晶种层上方的含铜层。

405.随后,透过蚀刻、化学机械平坦化等去除导电层、金属晶种层和阻挡层的多余部分,从而使金属填充的开口的上表面与基材510的背表面510e实质上共平面。在基材通孔开口510a和/或510b中的导电层和阻挡层的其余部分形成基材通孔598a和/或598b。

406.基材通孔598a和/或598b与p型井区516和/或n型井区518接触。当发生静电放电事件时,基材通孔598a和/或598b用以提供导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。在部分实施例中,也可将基材通孔598a和/或598b称为静电放电保护电路。

407.参考图63。形成后段制程型互连堆叠550和后段制程型互连堆叠550上的端子vdd和vss以连接埋入式电源轨。更详细地,执行一系列镶嵌制程步骤以产生后段制程型互连堆叠550,此后段制程型互连堆叠550透过低电阻电路将基材通孔598a和598b连接至晶片w5的背面上的端子vdd和vss。在部分实施例中,也可以将后段制程型互连堆叠550称为晶片w5的电力输送网络。

408.基于以上讨论,可以看出本公开提供了益处。然而,应当理解,其他的实施例可以提供附加的益处,并且在本公开中不必公开所有益处,并且对于所有实施例不需要特定的益处。本公开形成从晶片的背面延伸以嵌入在井区中硅穿孔。其中一个益处在于,本公开的基材通孔可以作为导电路径,从而可以在静电放电事件期间缓解高电流和电流密度,以避免电路崩溃。因此,由于没有在晶片的正面上形成静电放电装置,因此可以在减小几何尺寸

的同时增加功能密度。另一个益处是,本公开的基材通孔可作为晶片的散热器,以将由半导体元件产生的热量从井区释放到晶片的外部。

409.在部分实施例中,半导体元件包括基材、半导体鳍片、浅沟槽隔离结构、源极/漏极结构、第一埋入式电源线、接触、第一基材通孔和第二个基材通孔。基材具有井区,此井区从基材的前表面延伸到基材中。半导体鳍片位于井区上。浅沟槽隔离结构横向地围绕半导体鳍片的下部。源极/漏极结构在半导体鳍片上。第一埋入式电源线电耦合到第一半导体鳍片上的源极/漏极结构。第一埋入式电源线具有沿着第一半导体鳍片的长度方向延伸的长度和从浅沟槽隔离结构内延伸到井区内的高度。第一基材通孔从基材的背表面穿过基材延伸到第一埋入式电源线。第二基材通孔从基材的背表面延伸到井区。在部分实施例中,在平面图中,第二基材通孔在第一半导体鳍片和第一埋入式电源线之间。在部分实施例中,半导体元件还包括在井区上的第二半导体鳍片,其中,在平面图中,第二基材通孔在第一半导体鳍片和第二半导体鳍片之间。在部分实施例中,半导体元件还包括第二埋入式电源线,此第二埋入式电源线的长度沿着第一半导体鳍片的长度方向延伸,其中第一半导体鳍片在第二埋入式电源线和第一埋入式电源线之间。在部分实施例中,在平面图中,第二基材通孔与第一半导体鳍片不重叠。在部分实施例中,半导体元件还包括跨过第一半导体鳍片延伸的栅极结构,其中,在平面图中,第二基材通孔与栅极结构重叠。在部分实施例中,第二基材通孔具有与第一基材通孔实质上相同的深度。在部分实施例中,由第一基材通孔和第一埋入式电源线形成的界面与由井区和第二基材通孔形成的界面实质上齐平。在部分实施例中,井区是n型井区。在部分实施例中,井区是p型井区。

410.在部分实施例中,半导体元件包括基材、第一半导体鳍片、第二半导体鳍片、第一基材通孔和第二基材通孔。基材具有p型井区和与p型井区相邻的n型井区,其中p型井区和n型井区从基材的前表面延伸进入基材中。第一半导体鳍片配置在p型井区上。第二半导体鳍片配置在n型井区上。第一基材通孔从基材的背表面延伸到p型井区。第二基材通孔从基材的背面延伸到n型井区。在部分实施例中,半导体元件还包括第三半导体鳍片、源极/漏极结构、埋入式电源线、源极/漏极接触和第三基材通孔。第三半导体鳍片在基材上。源极/漏极结构在第三半导体鳍片上。埋入式电源线部分地嵌入基材中。源极/漏极接触将源极/漏极结构电连接到埋入式电源线。第三基材通孔从基材的背表面延伸到埋入式电源线。在部分实施例中,半导体元件还包括第三半导体鳍片、第一源极/漏极结构和第二源极/漏极结构、后段制程堆叠和第三基材通孔。第三半导体鳍片在基材上方。第一源极/漏极结构和第二源极/漏极结构分别在第一半导体鳍片和第三半导体鳍片上。后段制程堆叠位于第一源极/漏极结构和第二源极/漏极结构上方。第三基材通孔从基材的背表面延伸到后段制程堆叠。在部分实施例中,半导体元件还包括在第一基材通孔和p型井区之间并且掺杂有p型掺杂剂的掺杂层。在部分实施例中,半导体元件还包括在第二基材通孔与n型井区之间并且掺杂有n型掺杂剂的掺杂层。在部分实施例中,半导体元件还包括在第一基材通孔和p型井区之间的金属硅化物层。

411.在部分实施例中,一种用于形成半导体元件的方法包括:形成从基材的前表面延伸到基材中的井区;在井区上形成半导体鳍片;在半导体鳍片上形成源极/漏极结构;在井区中刻蚀沟槽;在井区的沟槽中形成埋入式电源线;形成源极/漏极接触,以将源极/漏极结构电连接到埋入式电源线;在基材的背表面上执行蚀刻制程,以形成多个开口,以暴露出埋

入式电源线和井区;用导电材料填充多个开口,以形成多个硅通孔。在部分实施例中,在蚀刻制程期间将埋入式电源线作为蚀刻停止层。在部分实施例中,此方法还包括:在执行蚀刻制程之后,透过开口用掺杂剂掺杂井区。在部分实施例中,在执行蚀刻制程之后,透过开口在井区上形成金属硅化物层。

412.前述内容概述了几个实施例的特征,使得本领域具普通知识者可以更好地理解本公开的各方面。本领域具普通知识者应该理解,他们可以容易地将本公开作为设计或修改其他过程和结构的基础,以实现与本公开介绍的实施例相同的目的和/或实现相同的益处。本领域具普通知识者还应该理解,这样的等效构造并不脱离本公开的精神和范围,并且在不脱离本公开的精神和范围的情况下,它们可以在本公开中进行各种改变、替换和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1