集成电路的制作方法

集成电路

1.本技术基于2020年9月29日在韩国知识产权局提交的第10-2020-0127482号韩国专利申请并要求其优先权,该韩国专利申请的公开内容通过引用全部包含于此。

技术领域

2.本公开涉及一种集成电路,更具体地,涉及一种包括逻辑单元和去耦单元的集成电路以及设计集成电路的方法。

背景技术:

3.为了集成电路的操作,集成电路可以消耗从电源提供的电流。当电流消耗迅速增加或减少时,正电源电压与负电源电压之间的电位差(例如,参考电位)可能波动。由电位差的波动引起的噪声可能导致系统故障。因此,在集成电路中采用包括去耦电容器的去耦单元,其用于稳定地保持参考电位与电源电位之间的电位差而无论集成电路的操作如何。

技术实现要素:

4.一个或更多个示例实施例提供了一种包括非对称去耦单元的集成电路以及设计集成电路的方法。

5.根据示例实施例的一个方面,提供了一种集成电路,所述集成电路包括至少一个去耦单元,其中,所述至少一个去耦单元包括:多个p型金属氧化物半导体场效应晶体管(mosfet),沿第一方向布置;以及多个n型mosfet,在垂直于第一方向的第二方向上与所述多个p型mosfet间隔开并且沿第一方向布置,其中,所述多个p型mosfet包括至少一个p型去耦mosfet,所述多个n型mosfet包括至少一个n型去耦mosfet,并且所述至少一个p型去耦mosfet的第一数量不同于所述至少一个n型去耦mosfet的第二数量。

6.根据示例实施例的一个方面,提供了一种集成电路,所述集成电路包括具有在第一方向上的第一高度的第一去耦单元,其中,第一去耦单元包括:多个第一p型金属氧化物半导体场效应晶体管,沿垂直于第一方向的第二方向布置;以及多个第一n型mosfet,在第一方向上与所述多个第一p型mosfet间隔开并且沿第二方向布置,其中,所述多个第一p型mosfet包括至少一个第一p型去耦mosfet和至少一个第一p型虚设mosfet,所述多个第一n型mosfet包括至少一个第一n型去耦mosfet和至少一个第一n型虚设mosfet,并且所述至少一个第一p型去耦mosfet的第一数量不同于所述至少一个第一n型去耦mosfet的第二数量。

7.根据示例实施例的一个方面,提供了一种集成电路,所述集成电路包括至少一个去耦单元,其中,所述至少一个去耦单元包括:第一导电类型去耦金属氧化物半导体场效应晶体管;以及第二导电类型去耦mosfet,并且与第一导电类型去耦mosfet相关的第一电容大于与第二导电类型去耦mosfet相关的第二电容。

附图说明

8.根据以下结合附图对示例实施例的详细描述,将更清楚地理解上述和/或其它方

面,在附图中:

9.图1是示出根据示例实施例的集成电路的布局图;

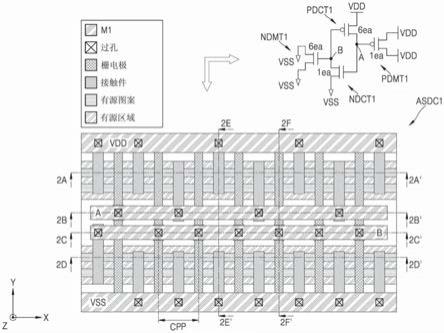

10.图2是示出根据示例实施例的非对称去耦单元的示例的布局图;

11.图3a至图3f是根据示例实施例的单元的结构的示例的剖视图;

12.图4a至图4d是用于描述根据一些其它示例实施例的非对称去耦单元的示例的图;

13.图5是用于描述根据一些其它示例实施例的非对称去耦单元的示例的图;

14.图6是用于描述根据一些其它示例实施例的非对称去耦单元的示例的图;

15.图7是用于描述根据一些其它示例实施例的非对称去耦单元的示例的图;

16.图8是示出根据示例实施例的集成电路的布局图;以及

17.图9是根据示例实施例的制造集成电路(ic)的方法的流程图。

具体实施方式

18.图1是示出根据示例实施例的集成电路的布局图。

19.根据示例实施例,集成电路1可以包括具有正常单元区域2和空区域(也被称为“虚设栅极区域”)3的逻辑块。集成电路1还可以包括围绕逻辑块的边缘的外围电路区域4。

20.集成电路1可以包括布置在正常单元区域2上的多个单元。单元是集成电路中包括的布局的单位,可以被设计为执行预定的功能,并且还可以被称为标准单元。集成电路1可以包括具有各种功能的多个单元,并且单元可以根据多个行对齐并布置。

21.包括p型金属氧化物半导体场效应晶体管(mosfet)和n型mosfet的互补mosfet(cmosfet)可以形成在正常单元区域2上。cmosfet的组合可以构成用于执行预定的功能的逻辑电路。

22.与正常单元区域2中的p型mosfet和n型mosfet类似的p型mosfet和n型mosfet可以形成在空区域3上。包括用作去耦电容器的p型mosfet和n型mosfet的非对称去耦单元可以设置在空区域3的至少一部分中。在下文中,将更详细地描述非对称去耦单元。

23.图2是示出根据示例实施例的非对称去耦单元asdc1的示例的布局图。详细地,图2的上部示出了非对称去耦单元asdc1的电路图,并且图2的下部示出了非对称去耦单元asdc1的布局。在本公开中,电路图中的“nea”(n为自然数)表示n个连接的(例如串联连接的和/或并联连接的)元件(例如,晶体管)。当n=1时,“1ea”表示一个元件(例如,晶体管)。

24.包括x轴和y轴的平面可以被称为水平平面,相对于其它组件在正(+)z方向上设置的组件可以被称为在其它组件上方,并且相对于其它组件在负(-)z方向上设置的组件可以被称为在其它组件下方。此外,组件的面积可以指在平行于水平平面的平面中由组件占据的尺寸,并且组件的高度可以指组件在y轴方向上长度。在本说明书的附图中,为了便于说明,可以示出仅一些层,并且即使过孔在布线层的图案下方也可以示出过孔,以表示布线层的图案与其下方的图案之间的连接。

25.在行的边界处分别施加正电源电压vdd和负电源电压(或地电位)vss的图案(其在此可以被称为电力线)可以沿x轴方向延伸,并且其中形成p型mosfet的第一有源区域rx1(参照图3e)和其中形成n型mosfet的第二有源区域rx2(参照图3e)可以沿x轴方向延伸。在一些实施例中,提供电源电压的图案被包括在一个或更多个布线层中。

26.如图2中所示,至少一个有源图案可以在有源区域上沿x轴方向延伸。有源图案可

以与沿y轴方向延伸的栅电极相交并且构成晶体管。当鳍型有源图案沿x轴方向延伸时,由鳍型有源图案和栅电极形成的晶体管可以被称为finfet。如下面参照图3a至图3e所描述的,将通过主要集中于包括finfet的单元来描述示例实施例,但是将理解的是,该描述也可以应用于包括具有不同于finfet的结构的晶体管的单元。例如,有源图案可以包括在z轴方向上彼此间隔开并沿x轴方向延伸的多个纳米片,并且单元可以包括其中纳米片构成栅电极的多桥沟道fet(mbcfet)。此外,单元可以包括其中用于p型晶体管的纳米片和用于n型晶体管的纳米片通过介电壁彼此分离的forkfet,因此,n型晶体管和p型晶体管具有相邻的结构。此外,单元可以包括垂直fet(vfet),垂直fet(vfet)具有其中源极/漏极区(s/d区)在z轴方向上彼此间隔开且使沟道区位于源极/漏极区之间并且栅电极围绕沟道区的结构。此外,单元可以包括场效应晶体管(fet)(如互补fet(cfet)、负fet(ncfet)和碳纳米管(cnt)fet),并且还可以包括双极结型晶体管和其它三维(3d)晶体管。

27.非对称去耦单元asdc1可以是用于维持正电源电压vdd与负电源电压(或地电位)vss之间的恒定电压差的单元。根据示例实施例,非对称去耦单元asdc1可以不包括已经形成在第一布线层m1中的输入引脚和输出引脚。

28.在本实施例中,非对称去耦单元asdc1可以包括7个n型mosfet和7个p型mosfet。根据示例实施例,n型mosfet可以包括一个或更多个n型去耦mosfet ndct1以及一个或更多个n型虚设mosfet ndmt1。根据示例实施例,p型mosfet可以包括一个或更多个p型去耦mosfet pdct1以及一个或更多个p型虚设mosfet pdmt1。

29.非对称去耦单元asdc1可以具有非对称电路构造。根据示例实施例,p型去耦mosfet pdct1的数量可以与n型去耦mosfet ndct1的数量不同。非对称去耦单元asdc1可以使用p型mosfet作为主去耦电容器。这里,使用p型mosfet作为主去耦电容器的非对称去耦单元asdc1表示用作去耦电容器的p型mosfet的数量大于用作去耦电容器的n型mosfet的数量。根据一些实施例,p型去耦mosfet pdct1的数量可以大于n型去耦mosfet ndct1的数量。例如,如图2中所示,p型去耦mosfet pdct1的数量可以是6,而n型去耦mosfet ndct1的数量可以是1。

30.根据示例实施例,p型虚设mosfet pdmt1的数量可以与n型虚设mosfet ndmt1的数量不同。根据示例实施例,p型虚设mosfet pdmt1的数量可以小于n型虚设mosfet ndmt1的数量。例如,如图2中所示,p型虚设mosfet pdmt1的数量可以是1,而n型虚设mosfet ndmt1的数量可以是6。

31.非对称去耦单元asdc1可以包括沿x方向延伸的4个有源图案。根据示例实施例,非对称去耦单元asdc1可以具有与8个栅极节距cpp对应的宽度(在x方向上的长度)。在此,x方向、y方向和z方向可以分别与x轴方向、y轴方向和z轴方向可互换地使用。

32.随着工艺技术发展,当单元的高度(即,在y方向上的长度)减小时,由于第一有源区域与第二有源区域之间的空间的减小,去耦单元中可能没有足够的空间来使在第一有源区域上的栅极和在第二有源区域上的栅极分离和重新布线。因此,在x方向上定位在相同位置处(或者在y方向上彼此叠置)的p型mosfet和n型mosfet中的仅一个可以用作去耦电容器。

33.这里,p型去耦mosfet的电容可以类似于n型去耦mosfet的电容。另一方面,由于p型去耦mosfet和n型去耦mosfet的栅极隧穿引起的漏电流可以根据集成电路的特性(例如,

栅极节距cpp)而变化。例如,当集成电路的栅极节距cpp在第一范围(例如,从约1nm到约10nm)内时,由于一个p型mosfet引起的漏电流可以小于由于一个n型mosfet引起的漏电流。在另一示例中,当集成电路的最小节距在不同于第一范围的第二范围内时,由于一个n型mosfet引起的漏电流可以小于由于一个p型mosfet引起的漏电流。

34.根据示例实施例,可以通过主要使用在p型mosfet与n型mosfet之中具有优异漏电流特性的mosfet来构造去耦单元。详细地,通过使用具有根据集成电路的特性(例如,最小节距)的小漏电流特性的导电型mosfet作为主去耦电容器,可以提供具有相同的电容的水平和改进的漏电流特性的去耦单元。另一方面,在非对称去耦单元中,使用p型去耦mosfet和n型去耦mosfet中的具有优异漏电流特性的一者作为主去耦电容器可以不限于其数量更大,而只要与所述一者相关的第一电容大于与p型去耦mosfet和n型去耦mosfet中的另一者相关的第二电容即可。可以通过去耦mosfet的不同数量(参见图2等)、有源区域的不同面积(参见图7等)等来实现上述不同的电容。

35.图3a至图3f是根据示例实施例的单元的结构的示例的剖视图。详细地,图3a是沿着图2的线2a-2a'截取的剖视图,图3b是沿着图2的线2b-2b'截取的剖视图,图3c是沿着图2的线2c-2c'截取的剖视图,图3d是沿着图2的线2d-2d'截取的剖视图,图3e是沿着图2的线2e-2e'截取的剖视图,并且图3f是沿着图2的线2f-2f'截取的剖视图。

36.尽管在图3a至图3f中未示出,但是栅极间隔件可以形成在栅电极的侧表面上,并且栅极介电层可以形成在栅电极与栅极间隔件之间并且形成在栅电极的底表面上。此外,阻挡层可以形成在接触件的表面和/或过孔上。在下文中,将参照图2描述图3a至图3e,并且将省略已经参照图3a至图3e给出的描述。

37.参照图3a,基底10可以包括体硅或绝缘体上硅(soi)。作为非限制性示例,基底10可以包括sige、绝缘体上硅锗(sgoi)、insb、pbte化合物、inas、磷化物、gaas或gasb。第一鳍f1可以在基底10上沿x轴方向延伸。第一源极/漏极区至第八源极/漏极区sd11、sd12、sd13、sd14、sd15、sd16、sd17和sd18可以形成在第一鳍f1中。第一层间绝缘层至第四层间绝缘层31、32、33和34可以形成在第一鳍f1上。

38.第一源极/漏极区sd11和第二源极/漏极区sd12以及第一栅电极g1可以构成p型虚设mosfet pdmt1。第二源极/漏极区sd12和第三源极/漏极区sd13以及第二栅电极g2可以构成p型去耦mosfet pdct1。第三源极/漏极区sd13和第四源极/漏极区sd14以及第三栅电极g3可以构成p型去耦mosfet pdct1。第四源极/漏极区sd14和第五源极/漏极区sd15以及第四栅电极g4可以构成p型去耦mosfet pdct1。第五源极/漏极区sd15和第六源极/漏极区sd16以及第五栅电极g5可以构成p型去耦mosfet pdct1。第六源极/漏极区sd16和第七源极/漏极区sd17以及第六栅电极g6可以构成p型去耦mosfet pdct1。第七源极/漏极区sd17和第八源极/漏极区sd18以及第七栅电极g7可以构成p型去耦mosfet pdct1。因此,非对称去耦单元asdc1可以包括6个p型去耦mosfet pdct1和1个p型虚设mosfet pdmt1。

39.第一源极/漏极接触件至第八源极/漏极接触件ca11、ca12、ca13、ca14、ca15、ca16、ca17和ca18可以穿透第二层间绝缘层32,并且可以顺序地分别连接到第一源极/漏极区至第八源极/漏极区sd11、sd12、sd13、sd14、sd15、sd16、sd17和sd18。第一源极/漏极接触件至第八源极/漏极接触件ca11、ca12、ca13、ca14、ca15、ca16、ca17和ca18中的至少一个可以包括穿透第一层间绝缘层31的下源极/漏极接触件和穿透第二层间绝缘层32的上源极/

漏极接触件。

40.第一源极/漏极接触件至第八源极/漏极接触件ca11、ca12、ca13、ca14、ca15、ca16、ca17和ca18可以通过穿透第三层间绝缘层33的过孔连接到第一布线层m1的图案中的任何一个。根据一些实施例,第一源极/漏极接触件ca11、第二源极/漏极接触件ca12、第四源极/漏极接触件ca14、第六源极/漏极接触件ca16和第八源极/漏极接触件ca18可以连接到施加正电源电压vdd的第一图案p11。因此,正电源电压vdd可以施加到第一源极/漏极区sd11、第二源极/漏极区sd12、第四源极/漏极区sd14、第六源极/漏极区sd16和第八源极/漏极区sd18。其中形成有第一图案p11和第四层间绝缘层34的层可以被称为第一布线层m1。在第一布线层m1中,还可以形成稍后描述的第二图案至第四图案p12、p13和p14(参照图3e)。

41.参照图3b,器件隔离层iso可以形成在基底10上。器件隔离层iso可以如下面参照图3e和图3f所描述的使有源区域分离。第一层间绝缘层31至第四层间绝缘层34可以形成在器件隔离层iso上。第一栅极接触件cb1可以穿透第二层间绝缘层32并连接到第一栅电极g1。第一栅极过孔vb1可以穿透第三层间绝缘层33并连接到第一栅极接触件cb1和第二图案p12。第二图案p12对应于图2的电路图中的节点a。

42.第三源极/漏极接触件ca13、第五源极/漏极接触件ca15和第七源极/漏极接触件ca17可以穿透第二层间绝缘层32。第三源极/漏极过孔va13、第五源极/漏极过孔va15和第七源极/漏极过孔va17可以穿透第三层间绝缘层33并连接到第二图案p12。第三源极/漏极过孔va13、第五源极/漏极过孔va15和第七源极/漏极过孔va17可以顺序地分别连接到第三源极/漏极接触件ca13、第五源极/漏极接触件ca15和第七源极/漏极接触件ca17。因此,图3a中所示的第三源极/漏极区sd13、第五源极/漏极区sd15和第七源极/漏极区sd17可以在节点a处与第一栅电极g1电短路。

43.在一些实施例中,与如图3b中所示的不同,可以省略第一栅极接触件cb1,并且第二图案p12可以通过穿透第二层间绝缘层32和第三层间绝缘层33的栅极过孔电连接到第一栅电极g1。

44.参照图3c,第二栅极接触件至第七栅极接触件cb2、cb3、cb4、cb5、cb6和cb7可以穿透第二层间绝缘层32并且顺序地分别连接到第二栅电极至第七栅电极g2、g3、g4、g5、g6和g7。第二栅极过孔至第七栅极过孔vb2、vb3、vb4、vb5、vb6和vb7可以穿透第三层间绝缘层33并且分别连接到第二栅电极至第七栅电极g2、g3、g4、g5、g6和g7。第二栅极过孔至第七栅极过孔vb2、vb3、vb4、vb5、vb6和vb7还可以连接到第三图案p13。第三图案p13对应于图2的电路图中的节点b。

45.第一源极/漏极接触件ca21可以穿透第二层间绝缘层32。第一源极/漏极过孔va21可以穿透第三层间绝缘层33并连接到第三图案p13和第一源极/漏极接触件ca21。因此,形成在nmos区域上的第一源极/漏极区sd31(参照图3d)可以在节点b处与第二栅电极至第七栅电极g2、g3、g4、g5、g6和g7电短路。

46.在一些实施例中,与如图3c中所示的不同,可以省略第二栅极接触件至第七栅极接触件cb2、cb3、cb4、cb5、cb6和cb7,并且第三图案p13可以经由穿透第二层间绝缘层32和第三层间绝缘层33的栅极过孔连接到第二栅电极至第七栅电极g2、g3、g4、g5、g6和g7。

47.参照图3d,第一源极/漏极区至第八源极/漏极区sd31、sd32、sd33、sd34、sd35、sd36、sd37和sd38可以形成在第三鳍f3中。第一层间绝缘层至第四层间绝缘层31、32、33和

34可以形成在第三鳍f3上。

48.第一源极/漏极区sd31和第二源极/漏极区sd32以及第一栅电极g1可以构成n型去耦mosfet ndct1。第二源极/漏极区sd32和第三源极/漏极区sd33以及第二栅电极g2可以构成n型虚设mosfet ndmt1。第三源极/漏极区sd33和第四源极/漏极区sd34以及第三栅电极g3可以构成n型虚设mosfet ndmt1。第四源极/漏极区sd34和第五源极/漏极区sd35以及第四栅电极g4可以构成n型虚设mosfet ndmt1。第五源极/漏极区sd35和第六源极/漏极区sd36以及第五栅电极g5可以构成n型虚设mosfet ndmt1。第六源极/漏极区sd36和第七源极/漏极区sd37以及第六栅电极g6可以构成n型虚设mosfet ndmt1。第七源极/漏极区sd37和第八源极/漏极区sd38以及第七栅电极g7可以构成n型虚设mosfet ndmt1。因此,非对称去耦单元asdc1可以包括1个n型去耦mosfet ndct1和6个n型虚设mosfet ndmt1。

49.第一源极/漏极接触件至第八源极/漏极接触件ca21、ca22、ca23、ca24、ca25、ca26、ca27和ca28可以穿透第二层间绝缘层32,并且可以顺序地分别连接到第一源极/漏极区至第八源极/漏极区sd31、sd32、sd33、sd34、sd35、sd36、sd37和sd38。第一源极/漏极接触件至第八源极/漏极接触件ca21、ca22、ca23、ca24、ca25、ca26、ca27和ca28中的至少一个可以包括穿透第一层间绝缘层31的下源极/漏极接触件和穿透第二层间绝缘层32的上源极/漏极接触件。

50.第一源极/漏极接触件至第八源极/漏极接触件ca21、ca22、ca23、ca24、ca25、ca26、ca27和ca28可以通过穿透第三层间绝缘层33的过孔连接到第一布线层m1的图案中的任何一个。根据一些实施例,第二源极/漏极接触件ca22至第八源极/漏极接触件ca28可以连接到施加有负电源电压(或地电位)vss的第四图案p14。因此,负电源电压(或地电位)vss可以施加到第二源极/漏极区sd32至第八源极/漏极区sd38。

51.参照图3e,场绝缘层20可以形成在基底10上。作为非限制性示例,场绝缘层20可以包括sio2、sin、sion、siocn和其组合中的任何一种。在一些实施例中,场绝缘层20可以如图3d中所示围绕有源图案(即,鳍)的一些侧表面。第一层间绝缘层至第四层间绝缘层31、32、33和34可以形成在场绝缘层20上。第一鳍至第四鳍f1、f2、f3和f4可以在场绝缘层20上沿x轴方向延伸。

52.源极/漏极区sd14、sd24、sd34和sd44可以分别布置在第一鳍至第四鳍f1、f2、f3和f4上。沿x方向延伸的隔离层iso可以设置在第一鳍f1和第二鳍f2与第三鳍f3和第四鳍f4之间。第一有源区域rx1和第二有源区域rx2可以通过器件隔离层iso彼此分离。

53.第四源极/漏极接触件ca14可以穿透第二层间绝缘层32并连接到两个源极/漏极区sd14和sd24,因此,两个源极/漏极区sd14和sd24可以彼此电连接。此外,第四源极/漏极接触件ca24可以穿透第二层间绝缘层32并连接到两个源极/漏极区sd34和sd44,因此,两个源极/漏极区sd34和sd44可以彼此电连接。

54.第四源极/漏极过孔va14可以穿透第三层间绝缘层33并连接到第四源极/漏极接触件ca14和第一图案p11。因此,正电源电压vdd可以施加到源极/漏极区sd14和sd24。第四源极/漏极过孔va24可以穿透第三层间绝缘层33并连接到第四源极/漏极接触件ca24和第四图案p14。因此,负电源电压(或地电位)vss可以施加到源极/漏极区sd34和sd44。上文所描述的第一图案至第四图案p11、p12、p13和p14可以形成在第一布线层m1中。

55.参照图3f,场绝缘层20可以形成在基底10上,并且穿透场绝缘层20的第一鳍至第

四鳍f1、f2、f3和f4可以与沿y轴方向延伸的第五栅电极g5相交。例如,第五栅电极g5可以包括如ti、ta、w、al或co的金属或其组合。在另一示例中,第五栅电极g5可以包括如si或sige的半导体材料。在另一示例中,第五栅电极g5可以包括其中堆叠有两种或更多种导电材料的多层结构。例如,根据一些实施例,第五栅电极g5可以包括共形沉积结构的功函数层和填充导电膜,功函数层包括tin、tan、tic、tac和tialc中的任何一种,填充导电膜填充共形沉积结构的功函数层的内部并且包括w或al。

56.如上所述,第五栅电极g5可以通过第五栅极接触件cb5和第五栅极过孔vb5电连接到第三图案p13。

57.图4a至图4d是用于描述根据一些其它示例实施例的非对称去耦单元的示例的图。

58.图4a是用于描述根据一些其它实施例的非对称去耦单元asdc1a的示例的图。详细地,图4a的上部示出了与非对称去耦单元asdc1a对应的电路图,并且图4a的下部示出了与非对称去耦单元asdc1a对应的布局。

59.为了便于解释,将省略与上面参照图2至图3e已经给出的描述相同的描述,并且下面的描述将集中于与图2至图3e的不同之处。

60.参照图4a,非对称去耦单元asdc1a可以包括7个n型mosfet和7个p型mosfet。与图2的非对称去耦单元asdc1不同,非对称去耦单元asdc1a可以包括5个p型去耦mosfet pdct1、2个p型虚设mosfet pdmt1、2个n型去耦mosfet ndct1和5个n型虚设mosfet ndmt1。根据示例实施例,非对称去耦单元asdc1a主要以具有优异电流泄漏特性的p型mosfet构造。然而,因为p型去耦mosfet pdct1的数量和n型去耦mosfet ndct1的数量可以自由地改变,所以设计的自由度可以提高。

61.图4b是用于描述根据一些其它实施例的非对称去耦单元asdc1b的示例的图。详细地,图4b的上部示出了与非对称去耦单元asdc1b对应的电路图,并且图4b的下部示出了与非对称去耦单元asdc1b对应的布局。

62.为了便于解释,将省略与上面参照图2至图3e已经给出的描述相同的描述,并且下面的描述将集中于与图2至图3e的不同之处。

63.参照图4b,非对称去耦单元asdc1b可以包括7个n型mosfet和7个p型mosfet。与图2的非对称去耦单元asdc1不同,非对称去耦单元asdc1b可以包括4个p型去耦mosfet pdct1、3个p型虚设mosfet pdmt1、3个n型去耦mosfet ndct1和4个n型虚设mosfet ndmt1。

64.图4c是用于描述根据一些其它实施例的非对称去耦单元asdc1c的示例的图。详细地,图4c的左部示出了与非对称去耦单元asdc1c对应的电路图,并且图4c的右部示出了与非对称去耦单元asdc1c对应的布局。

65.为了便于解释,将省略与上面参照图2至图3e已经给出的描述相同的描述,并且下面的描述将集中于与图2至图3e的不同之处。

66.参照图4c,与图2中不同,非对称去耦单元asdc1c可以具有4个栅极节距cpp。根据示例实施例,非对称去耦单元asdc1c可以包括3个n型mosfet和3个p型mosfet。与图2的非对称去耦单元asdc1不同,非对称去耦单元asdc1c可以包括2个p型去耦mosfet pdct1、1个p型虚设mosfet pdmt1、1个n型去耦mosfet ndct1和2个n型虚设mosfet ndmt1。

67.根据示例实施例,基于参照图2至图3f和图4c给出的描述,本领域普通技术人员可以容易地实现可以具有5个至7个栅极节距cpp或者9个或更多个栅极节距cpp的非对称去耦

单元。

68.图4d是用于描述根据一些其它实施例的非对称去耦单元asdc1d的示例的图。详细地,图4d的上部示出了与非对称去耦单元asdc1d对应的电路图,并且图4d的下部示出了与非对称去耦单元asdc1d对应的布局。

69.为了便于解释,将省略与上面参照图2至图3e已经给出的描述相同的描述,并且下面的描述将集中于与图2至图3e的不同之处。

70.参照图4d,非对称去耦单元asdc1d可以具有8个栅极节距cpp。根据示例实施例,非对称去耦单元asdc1d可以包括7个n型mosfet和7个p型mosfet。与图2的非对称去耦单元asdc1不同,非对称去耦单元asdc1d可以包括1个p型去耦mosfet pdct1、6个p型虚设mosfet pdmt1、6个n型去耦mosfet ndct1和1个n型虚设mosfet ndmt1。

71.根据示例实施例,非对称去耦单元asdc1d中的n型mosfet的泄漏特性可以优于p型mosfet的泄漏特性。因此,非对称去耦单元asdc1d可以使用n型mosfet作为主去耦电容器。

72.图5是用于描述根据示例实施例的非对称去耦单元asdc2的示例的图。详细地,图5的上部示出了与非对称去耦单元asdc2对应的电路图,并且图5的下部示出了与非对称去耦单元asdc2对应的布局。

73.为了便于解释,将省略与上面参照图2至图3e已经给出的描述相同的描述,并且下面的描述将集中于与图2至图3e的不同之处。

74.参照图5,非对称去耦单元asdc2可以包括7个p型去耦mosfet pdct2和7个n型虚设mosfet ndmt2。根据示例实施例,正电源电压vdd可以施加到p型去耦mosfet pdct2的源极和漏极,并且负电源电压(或地电位)vss可以施加到p型去耦mosfet pdct2的栅极。根据示例实施例,n型虚设mosfet ndmt2的源极和漏极可以浮置。

75.尽管图5示出了非对称去耦单元asdc2包括8个栅极节距cpp,但是实施例不限于此。例如,非对称去耦单元asdc2可以包括2个至7个栅极节距cpp或者9个或更多个栅极节距cpp。

76.根据示例实施例,当图2的非对称去耦单元asdc1使用p型去耦mosfet pdct1作为主去耦电容器时,需要使用至少一个n型mosfet作为去耦电容器以提供负电源电压(或地电位)vss作为偏置。

77.另一方面,因为负电源电压(或地电位)vss施加到用作去耦电容器的p型去耦mosfet pdct2的栅电极,所以非对称去耦单元asdc2可以不使用n型mosfet中的任何一个作为去耦电容器用于偏置。因此,非对称去耦单元asdc2中的所有p型mosfet可以用作去耦电容器,并且非对称去耦单元asdc2中的所有n型mosfet可以是n型虚设mosfet ndmt2。换言之,非对称去耦单元asdc2可以不包括p型虚设mosfet并且不包括n型去耦mosfet。

78.图6是用于描述根据示例实施例的非对称去耦单元asdc3的示例的图。详细地,图6的上部示出了与非对称去耦单元asdc3对应的电路图,并且图6的下部示出了与非对称去耦单元asdc3对应的布局。

79.为了便于解释,将省略与上面参照图5已经给出的描述相同的描述,并且下面的描述将集中于与图5的不同之处。

80.参照图6,非对称去耦单元asdc3可以包括7个p型虚设mosfet pdmt3和7个n型去耦mosfet ndct3。与图5的非对称去耦单元asdc2不同,非对称去耦单元asdc3可以使用n型

mosfet作为主去耦电容器。因此,根据示例实施例,负电源电压(或地电位)vss可以施加到n型mosfet的源极和漏极,并且正电源电压vdd可以施加到n型mosfet的栅极。根据示例实施例,p型mosfet的源极和漏极可以浮置。根据示例实施例,非对称去耦单元asdc3可以不包括p型去耦mosfet并且不包括n型虚设mosfet。

81.图7是用于描述根据示例实施例的非对称去耦单元asdc4的示例的图。详细地,图7的上部示出了与非对称去耦单元asdc4对应的电路图,并且图7的下部示出了与非对称去耦单元asdc4对应的布局。

82.为了便于解释,将省略与上面参照图6已经给出的描述相同的描述,并且下面的描述将集中于与图6的不同之处。

83.参照图7,非对称去耦单元asdc4可以包括7个p型mosfet和7个n型mosfet。根据示例实施例,p型mosfet可以是p型去耦mosfet pdct4,并且n型mosfet可以是n型去耦mosfet ndct4。根据示例实施例,沿y方向对齐的p型去耦mosfet pdct4和n型去耦mosfet ndct4可以共用栅电极。正电源电压vdd可以施加到p型去耦mosfet pdct4的源极和漏极。负电源电压(或地电位)vss可以施加到n型去耦mosfet ndct4的源极和漏极。

84.根据示例实施例,第一有源区域rx1'的高度(即,在y方向上的长度)可以大于第二有源区域rx2'的高度(即,在y方向上的长度)。在图7中所示的实施例中,第一有源区域rx1'的高度可以是第二有源区域rx2'的高度的两倍或更大(例如,3倍)。根据示例实施例,布置在第一有源区域rx1'上的有源图案的数量可以大于布置在第二有源区域rx2'上的有源图案的数量。例如,布置在第一有源区域rx1'上的有源图案的数量可以是3,并且布置在第二有源区域rx2'上的有源图案的数量可以是1。然而,实施例不限于此。

85.根据示例实施例,通过将第一有源区域rx1'(第一有源区域rx1'是用于形成具有优异漏电流特性的p型mosfet的区域)形成为比第二有源区域rx2'(第二有源区域rx2'是用于形成n型mosfet的区域)大,可以提供具有改进的漏电流特性同时提供等量水平的电容的非对称去耦单元asdc4。

86.图8是用于描述根据示例实施例的集成电路11的布局的示例的图。

87.根据一些实施例,集成电路11可以包括具有不同的高度的多个非对称去耦单元asdc1、asdc5和asdc6。图8仅示出了第一布线层m1、过孔、栅电极和有源区域。

88.非对称去耦单元asdc1可以与上面参照图2至图3e描述的非对称去耦单元asdc1基本相同。根据示例实施例,非对称去耦单元asdc5的高度可以是非对称去耦单元asdc1的高度的约两倍。根据示例实施例,非对称去耦单元asdc6的高度可以是非对称去耦单元asdc1的高度的约3倍。

89.根据示例实施例,非对称去耦单元asdc5可以包括与非对称去耦单元asdc1基本相同的第一子单元asdc5_1。非对称去耦单元asdc5可以包括与其中非对称去耦单元asdc5_1相对于平行于x方向的轴反转的结构基本相同的第二子单元asdc5_2。因此,与第一子单元asdc5_1和第二子单元asdc5_2对应的电路图与图2的上部中所示的电路图相同。第一子单元asdc5_1和第二子单元asdc5_2可以共用第一布线层m1以提供负电源电压(或地电位)vss。

90.基于非对称去耦单元asdc5的描述,本领域普通技术人员可以容易地实现具有非对称去耦单元asdc1的高度的约两倍的高度并且包括共用正电源电压vdd的第一单元和第

二单元的非对称去耦单元。

91.非对称去耦单元asdc6可以包括第一有源区域rx1”和第二有源区域rx2”。第二有源区域rx2”可以设置为单个单元,并且可以具有与非对称去耦单元asdc1的第二有源区域rx2的高度基本相同的高度。器件隔离层iso”可以位于第一有源区域rx1”与第二有源区域rx2”之间。器件隔离层iso”的高度可以与非对称去耦单元asdc1的器件隔离层iso的高度基本相同。

92.第一有源区域rx1”可以被设置为单个单元,并且第一有源区域rx1”的高度可以大于第二有源区域rx2”的高度,例如,第一有源区域rx1”的高度可以是第二有源区域rx2”的高度的至少两倍;但是实施例不限于此。例如,可以设置多个第一有源区域rx1",并且器件隔离层可以位于第一有源区域rx1"之间。

93.非对称去耦单元asdc6的第一有源区域rx1”的高度可以大于非对称去耦单元asdc1的第一有源区域rx1的高度。包括在非对称去耦单元asdc6中的第一有源区域rx1”的高度可以大于图2的非对称去耦单元asdc1的第一有源区域rx1的高度的三倍。

94.根据示例实施例,在包括在第一布线层m1中的图案之中,用于供应正电源电压vdd的两个图案p61和p63以及用于供应负电源电压(或地电位)vss的两个图案p62和p64可以交替地布置在非对称去耦单元asdc6上。

95.根据示例实施例,第一图案至第三图案p61、p62和p63可以在第一有源区域rx1”上沿x方向延伸。根据示例实施例,第一图案至第三图案p61、p62和p63的部分可以在z方向上与第一有源区域rx1”叠置。根据示例实施例,与在非对称去耦单元asdc1中不同,在非对称去耦单元asdc6中,器件隔离层iso”可以不设置在第一图案p61与第二图案p62之间以及第二图案p62与第三图案p63之间之间。因此,因为有源区域与栅电极之间的面对面积增加,所以可以增大相对于非对称去耦单元asdc6的面积的电容。

96.图9是根据示例实施例的制造集成电路(ic)的方法的流程图。详细地,图9的流程图示出了制造包括去耦单元的ic的方法的示例。如图9中所示,制造ic的方法可以包括多个操作s20、s40、s60和s80。

97.单元库(或标准单元库)d12可以包括关于单元的信息,例如,功能信息、特性信息、布局信息等。如图9中所示,单元库d12可以包括第一数据d_asdc1至第六数据d_asdc6,第一数据d_asdc1至第六数据d_asdc6是用于定义上面参照图2至图8所描述的非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6的数据。

98.在操作s20中,可以执行用于从rtl数据d11生成网表d13的逻辑综合操作。例如,半导体设计工具(例如,逻辑综合工具)可以参照单元库d12从以vhsic硬件描述语言(vhdl)和verilog组成的rtl数据d11执行逻辑综合,从而生成包括比特流或网表的网表d13。半导体设计工具可以基于ic的条件从单元库d12中选择非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6中的任何一个。

99.在操作s40中,可以执行用于从网表d13生成布局数据d14的放置&布线(p&r)操作。例如,对于ic的布图规划(floor plan),半导体设计工具(例如,p&r工具)可以确定其中布置有非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6的区域的数量,与非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6对应的行的数量。

100.接下来,半导体设计工具可以从网表d13参照单元库d12,并且将非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6布置在用于布置非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6的区域中。半导体设计工具可以生成定义非对称去耦单元asdc1、asdc1a、asdc1b、asdc1c、asdc1d、asdc2、asdc3、asdc4、asdc5和asdc6的布局数据d14。布局数据d14可以具有如gdsii的格式,并且可以包括关于单元和互连的几何信息。可以将操作s40单独称为设计ic的方法或者将操作s20和操作s40统称为设计ic的方法,并且下面将参照图7描述操作s40的示例。

101.在操作s60中,可以执行用于制造掩模的操作。例如,可以对布局数据d14应用用于校正由于光刻中的光的特性(例如,折射)引起的失真的光学邻近校正(opc)。可以基于opc施加的数据来限定掩模上的图案以形成要布置在多个层中的图案,并且可以制造用于形成每个层的图案的至少一个掩模(或光掩模)。在一些实施例中,可以在操作s60中有限制地修改ic的布局,并且操作s60中的ic的有限制的修改是用于优化ic的结构的后处理,并且可以被称为设计抛光。

102.在操作s80中,可以执行用于制造ic的操作。例如,可以通过使用在操作s60中制造的至少一个掩模通过使多个层图案化来制造ic。例如,前端制程(feol)可以包括平坦化并清洁晶片、形成沟槽、形成阱、形成栅电极以及形成源极和漏极,并且可以通过feol在基底上形成如晶体管、电容器和电阻器的个体器件。此外,例如,后端制程(beol)可以包括如栅极、源极区和漏极区的硅化、添加电介质、平坦化、形成孔、添加金属层、形成过孔以及形成钝化层的操作,并且如晶体管、电容器和电阻器的个体器件可以通过beol彼此连接。在一些实施例中,可以在feol与beol之间执行中部制程(mol),并且可以在个体元件上形成接触件。接下来,可以将ic封装在半导体封装件中并用作用于各种应用的组件。

103.尽管已经参照其实施例具体地示出并描述了本公开,但是将理解的是,在不脱离权利要求的精神和范围的情况下,可以在其中进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1