垂直电子熔丝元件及其制备方法与流程

1.本技术案主张2020年7月7日申请的美国正式申请案第16/922,628号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开是关于一种电子熔丝(e-fuse)元件及其制备方法。特别是有关于一种垂直电子熔丝元件及其制备方法。

背景技术:

3.集成电路(ic)元件通常在制造制程期间与所有电子内部连接组件一起制造。然而,由于用于形成如此ic元件的发展成本高、制造时间长以及制造工具成本高,所以使用者通常要求可在现场配置或编程电路。如此的电路是称为可编程电路,且其通常包含可编程链(programmable links)。所述可编程链为电子内连接,在ic元件已经被制造与封装以便活化(activate)或去活化(deactivate)各个选定的电子节点之后,使用者在选定的电子节点处折断或创建了电子内部连接。

4.所述可编程链的其中一种是为一电子熔丝(e-fuse)元件。电子熔丝元件是利用在用于各式不同应用的半导体集成电路中,举例来说,所述半导体集成电路是包括存储器阵列冗余(memory array redundancy)、电路的制造后编程以及封装识别编码(package identification coding)。然而,电子熔丝元件使用现有互补金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)技术的制造是需要多个沉积与遮罩(masking)步骤,其是昂贵又耗费时间。因此,应当降低包含制造集成电子熔丝元件的所述处理步骤的复杂度,以降低制造具有电子熔丝的ic元件的成本及时间。再者,应当可最小化被所述电子熔丝元件所占据的覆盖面积(footprint area)。

5.上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现要素:

6.本公开的一实施例提供一种垂直电子熔丝元件。该垂直电子熔丝元件具有一熔丝链(fuse link),设置在一半导体基板(semiconductor base)上。该熔丝链的材料以及该半导体基板的材料为相同。该垂直电子熔丝元件亦具有一第一下阳极/阴极区以及一第二下阳极/阴极区,该第一下阳极/阴极区与该第二下阳极/阴极区设置在该半导体基板上。该熔丝链的一下部夹置在该第一下阳极/阴极区与该第二下阳极/阴极区之间。该垂直电子熔丝元件还具有一上阳极/阴极区,设置在该熔丝链上。

7.在一实施例中,该上阳极/阴极区具有一刻面部(faceted portion)。在一实施例中,该熔丝链是掺杂有一n型掺杂物。在一实施例中,从顶视图来看,该熔丝链与该上阳极/阴极区是呈环形形状。在一实施例中,该垂直电子熔丝元件还包括一硅化物层,设置在该第一下阳极/阴极区上;以及一下间隙子层,设置在该硅化物层上,其中该硅化物层与该熔丝

链是通过该下间隙子层而分开设置。

8.在一实施例中,该垂直电子熔丝元件还包括一第一熔丝介电层,设置在该第一下阳极/阴极区上;以及一第二熔丝介电层,设置在该第二下阳极/阴极区上,其中该第一下阳极/阴极区与该第一熔丝介电层直接接触该熔丝链的一第一侧壁,以及该第二下阳极/阴极区与该第二熔丝介电层直接接触该熔丝链的一第二侧壁。在一实施例中,该垂直电子熔丝元件还包括一第一导电层,设置在该第一熔丝介电层上,其中该第一导电层与该熔丝链是通过该第一熔丝介电层而分开设置;以及一第二导电层,设置在该第二熔丝介电层上,其中该第二导电层与该熔丝链是通过该第二熔丝介电层而分开设置。

9.本公开的另一实施例提供一种垂直电子熔丝元件。该垂直电子熔丝元件具有一环形熔丝链,设置在一半导体基板上。该环状熔丝链的材料与该半导体基板的材料是相同。该垂直电子熔丝元件亦具有一第一下阳极/阴极区,是被该环状熔丝链的一下部所围绕;以及一第二下阳极/阴极区,围绕该环状熔丝链的该下部设置。该垂直电子熔丝元件还具有一上阳极/阴极区,设置在该环状熔丝链上。

10.在一实施例中,该上阳极/阴极区呈环状,以及该上阳极/阴极区直接接触该环状熔丝链的一上表面。在一实施例中,该第一下阳极/阴极区邻接该环状熔丝链的一内侧壁,以及该第二下阳极/阴极区邻接该环状熔丝链的一外侧壁。在一实施例中,该垂直电子熔丝元件还包括一第一硅化物层,设置在该第一下阳极/阴极区上;以及一第二硅化物层,设置在该第二下阳极/阴极区上,其中该第一硅化物层与该第二硅化物层是与该环状熔丝链分开设置。在一实施例中,该垂直电子熔丝元件还包括一第一熔丝介电层,设置在该环状熔丝链的一内侧壁上,其中该第一熔丝介电层延伸在该第一下阳极/阴极区上;以及一第二熔丝介电层,设置在该环状熔丝链的一外侧壁上,其中该第二熔丝介电层延伸在该第二下阳极/阴极区上。

11.在一实施例中,该垂直电子熔丝元件还包括一第一导电层,设置在该第一熔丝介电层上;以及一第二导电层,设置在该第二熔丝介电层上,其中该第一导电层与该第二导电层是与该环状熔丝链分开设置。在一实施例中,该垂直电子熔丝元件还包括一下间隙子层,设置在该第一下阳极/阴极区与该第一熔丝介电层之间,以及在该第二下阳极/阴极区与该第二熔丝介电层之间;以及一上间隙子层,覆盖该第一熔丝介电层、该第一导电层、该第二熔丝介电层以及该第二导电层。

12.本公开的再另一实施例提供一种垂直电子熔丝元件的制备方法。该制备方法包括:形成一遮罩层在一半导体基底上;以及蚀刻该半导体基底并使用该遮罩层当作一遮罩,以形成一熔丝链在一半导体基板上。该方法亦包括外延生长一第一下阳极/阴极区以及一第二下阳极/阴极区在该半导体基板上以及邻近该熔丝链的一下部处。该熔丝链位在该第一下阳极/阴极区与该第二下阳极/阴极区之间。该方法还包括外延生长一上阳极/阴极区,以取代该遮罩层。

13.在一实施例中,从顶视图来看,该遮罩层与该熔丝链具有重叠的环形形状。在一实施例中,形成该遮罩层还包括:形成一环状结构在该半导体基底上;以及形成一遮罩材料以覆盖该半导体基底通过该环状结构暴露的一部分。此外,形成该遮罩层包括:沉积一内间隙子层以及一外间隙子层在该遮罩材料上,其中该环状结构的一内侧壁是被该内间隙子层所覆盖,以及该环状结构的一外侧壁是被该外间隙子层所覆盖;以及蚀刻该遮罩材料并使用

该内间隙子层与该外间隙子层当作一遮罩,以形成该遮罩层在该半导体基底上。

14.在一实施例中,该方法还包括:植入具有一n型掺杂物的该熔丝链;以及移除该内间隙子层与该外间隙子层,其是在该熔丝链的植入之后执行。在一实施例中,该方法还包括:形成一第一硅化物层在该第一下阳极/阴极区上以及形成一第二硅化物层在该第二下阳极/阴极区上;以及形成一下间隙子层以覆盖该第一硅化物层与该第二硅化物层,其是在该上阳极/阴极区生长之前执行。在一实施例中,该方法还包括:形成一第一熔丝介电层以及一第二熔丝介电层在该下间隙子层上以及在该熔丝链的各相对侧壁上;以及形成一第一导电层在该第一熔丝介电层上以及形成一第二导电层在该第二熔丝介电层上。此外,该方法包括形成一上间隙子层以覆盖该第一导电层与该第二导电层,其是在该上阳极/阴极区生长之前执行。

15.本公开提供多个实施例的垂直电子熔丝元件。该垂直电子熔丝元件具有一熔丝链以及多个下阳极/阴极区,而该熔丝链与所述下阳极/阴极区设置一半导体基板上,且该熔丝链的一下部夹置在所述下阳极/阴极区之间。该垂直电子熔丝元件亦具有一上阳极/阴极区,设置在该熔丝链上。由于该熔丝链配置在所述下阳极/阴极区与该上阳极/阴极区之间的垂直方向上,所以该垂直电子熔丝元件可与其他半导体元件整合在一起,例如一鳍式场效晶体管(finfet)元件,且该垂直电子熔丝元件可与所述finfet元件一体形成,而无须额外的处理步骤。

16.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

17.参阅实施方式与权利要求合并考量图式时,可得以更全面了解本技术案的揭示内容,图式中相同的元件符号是指相同的元件。

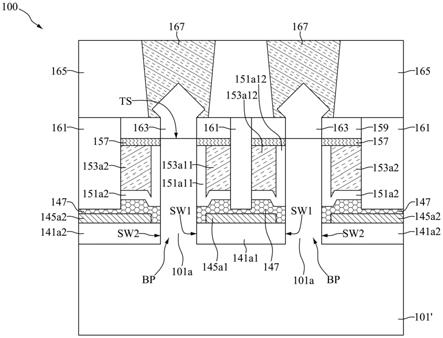

18.图1为依据本公开一些实施例一种垂直电子熔丝元件的剖视示意图。

19.图2为依据本公开一些实施例一种垂直电子熔丝元件的制备方法的流程示意图。

20.图3为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个环状结构在一半导体基底(semiconductor substrate)上的一中间阶段的顶视示意图。

21.图4为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个环状结构在一半导体基底上的一中间阶段的剖视示意图。

22.图5为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成一遮罩材料的一中间阶段的顶视示意图。

23.图6为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成一遮罩材料的一中间阶段沿图5的剖线i-i’的剖视示意图。

24.图7为依据本公开一些实施例在形成该垂直电子熔丝元件期间,沉积多个内间隙子层以及多个外间隙子层的一中间阶段的顶视示意图。

25.图8为依据本公开一些实施例在形成该垂直电子熔丝元件期间,沉积多个内间隙子层以及多个外间隙子层的一中间阶段沿图7的剖线i-i’的剖视示意图。

26.图9为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个熔丝链在一半导体基板上的一中间阶段的顶视示意图。

27.图10为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个熔丝链在一半导体基板上的一中间阶段沿图9的剖线i-i’的剖视示意图。

28.图11为依据本公开一些实施例在形成该垂直电子熔丝元件期间,植入所述熔丝链的一中间阶段的剖视示意图。

29.图12为依据本公开一些实施例在形成该垂直电子熔丝元件期间,移除所述内间隙子层与所述外间隙子层的一中间阶段的顶视示意图。

30.图13为依据本公开一些实施例在形成该垂直电子熔丝元件期间,移除所述内间隙子层与所述外间隙子层的一中间阶段沿图12的剖线i-i’的剖视示意图。

31.图14为在图13中的区域a的部分放大剖视示意图,且图14为依据本公开一些实施例在形成该垂直电子熔丝元件期间,外延生长多个下阳极/阴极区在该半导体基板上的一中间阶段的示意图。

32.图15为在图13中的区域a的部分放大剖视示意图,且图15为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成所述内间隙子层与所述外间隙子层的一中间阶段的示意图。

33.图16为在图13中的区域a的部分放大剖视示意图,且图16为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个硅化物层在所述下阳极/阴极区上的一中间阶段的示意图。

34.图17为在图13中的区域a的部分放大剖视示意图,且图17为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成一下间隙子层在所述硅化物层上的一中间阶段的示意图。

35.图18为在图13中的区域a的部分放大剖视示意图,且图18为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个熔丝介电层与多个导电层在该下间隙子层上的一中间阶段的示意图。

36.图19为在图13中的区域a的部分放大剖视示意图,且图19为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成一上间隙子层在所述熔丝介电层与所述导电层上的一中间阶段的示意图。

37.图20为在图13中的区域a的部分放大剖视示意图,且图20为依据本公开一些实施例在形成该垂直电子熔丝元件期间,形成多个介电层以穿经所述导电层的一中间阶段的示意图。

38.图21为在图13中的区域a的部分放大剖视示意图,且图21为依据本公开一些实施例在形成该垂直电子熔丝元件期间,外延生长一上阳极/阴极以取代该遮罩层的一中间阶段的示意图。

39.其中,附图标记说明如下:

40.10:方法

41.100:垂直电子熔丝元件

42.101:半导体基底

43.101’:半导体基板

44.101a:熔丝链

45.101b:熔丝链

46.101c:熔丝链

47.101d:熔丝链

48.103a:圆柱形结构

49.103b:圆柱形结构

50.105a:环状结构

51.105b:环状结构

52.107:遮罩材料

53.107’:遮罩层

54.110a:开口

55.110b:开口

56.113a1:内间隙子层

57.113a2:外间隙子层

58.113b1:内间隙子层

59.113b2:外间隙子层

60.120a:开口

61.120b:开口

62.130a1:凹陷

63.130a2:凹陷

64.130b1:凹陷

65.130b2:凹陷

66.130c:凹陷

67.135:离子植入制程

68.141a1:下阳极/阴极区

69.141a2:下阳极/阴极区

70.145a1:硅化物层

71.145a2:硅化物层

72.147:下间隙子层

73.151a1:熔丝介电层

74.151a11:熔丝介电层

75.151a12:熔丝介电层

76.151a2:熔丝介电层

77.153a1:导电层

78.153a11:导电层

79.153a12:导电层

80.153a2:导电层

81.157:上间隙子层

82.159:层间介电层

83.161:介电层

84.163:上阳极/阴极区

85.165:介电层

86.167:导电接触点

87.a:区域

88.bp:下部

89.s11:步骤

90.s13:步骤

91.s15:步骤

92.s17:步骤

93.s19:步骤

94.s21:步骤

95.s23:步骤

96.s25:步骤

97.s27:步骤

98.s29:步骤

99.s31:步骤

100.s33:步骤

101.sw1:侧壁

102.sw2:侧壁

103.sw3:内侧壁

104.sw4:外侧壁

105.ts:上表面

具体实施方式

106.以下描述了组件和配置的具体范例,以简化本公开的实施例。当然,这些实施例仅用以例示,并非意图限制本公开的范围。举例而言,在叙述中第一部件形成于第二部件之上,可能包含形成第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一和第二部件之间,使得第一和第二部件不会直接接触的实施例。另外,本公开的实施例可能在许多范例中重复参照标号及/或字母。这些重复的目的是为了简化和清楚,除非内文中特别说明,其本身并非代表各种实施例及/或所讨论的配置之间有特定的关系。

107.此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所绘示的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

108.图1为依据本公开一些实施例一种垂直电子熔丝元件100的剖视示意图。如图1所

示,垂直电子熔丝元件100包括一熔丝链101a与下阳极/阴极区141a1、141a2,以及一上阳极/阴极区163,熔丝链101a与下阳极/阴极区141a1、141a2设置在一半导体基板101’上,上阳极/阴极区163则设置在熔丝链101a上。

109.在一些实施例中,由于如图1所示的熔丝链101a的两区段为一连续环状(annular)结构的不同部分,所以该两区段是实体连接在一起,其是将于后详细描述。熔丝链101a亦被称为一环状熔丝链。在此例中,下阳极/阴极区414a1是被熔丝链101a的一下部bp所围绕,以及如图1所示的下阳极/阴极区141a2的两区段是为一连续环状结构的不同部分,该连续环状结构是围绕熔丝链101a的下部bp。

110.在一些实施例中,熔丝链101a的下部bp是夹置在下阳极/阴极区141a1与141a2之间。尤其是,下阳极/阴极区141a1邻接熔丝链101a的侧壁sw1,以及下阳极/阴极区141a2邻接熔丝链101a的侧壁sw2。侧壁sw1亦被称为熔丝链101a的内侧壁。侧壁sw2亦被称为熔丝链101a的外侧壁。类似地,如图1所示的上阳极/阴极区163的两区段可为一连续环状结构的不同的两部分。在一些实施例中,上阳极/阴极区136直接接触熔丝链101a的上表面ts。

111.再者,垂直电子熔丝元件100包括硅化物层145a1、145a2以及一下间隙子层147,硅化物层145a1、145a2设置在下阳极/阴极区141a1、141a2上,下间隙子层147覆盖硅化物层145a1、145a2。在一些实施例中,硅化物层145a1设置在下阳极/阴极区141a1上,以及如图1所示的硅化物层145a2的两区段为设置在下阳极/阴极区141a2上的一连续环状结构的不同两部分,而下阳极/阴极区141a2亦为一连续环状结构。在一些实施例中,硅化物层145a1、145a2是共形被下间隙子层147所覆盖,以及硅化物层145a1、145a2与熔丝链101a的侧壁sw1、sw2通过下间隙子层147而分开设置。

112.仍请参考图1,垂直电子熔丝元件100包括熔丝介电层151a11、151a12、151a2以及导电层153a11、153a12、153a2,熔丝介电层151a11、151a12、151a2设置在下间隙子层147上,导电层153a11、153a12、153a2设置在熔丝介电层151a11、151a12、151a2上。在一些实施例中,熔丝介电层151a11与151a12设置在熔丝链101a的侧壁sw1上,且熔丝介电层151a11与151a12延伸到下间隙子层147被熔丝链101a所围绕的部分上。在一些实施例中,如图1所示的熔丝介电层151a2的两区段是实体连接在一起,并设置在熔丝链101a的侧壁sw2上,且熔丝介电层151a2延伸到下间隙子层147围绕熔丝链101a的部分上。

113.类似于熔丝介电层151a2,依据一些实施例,导电层153a2的两区段是实体连接在一起,其原因是它们为一连续环状结构的不同两部分。在一些实施例中,导电层153a11、153a12、153a2与熔丝链101a及下间隙子层147是通过熔丝介电层151a11、151a12、151a2而分开设置。

114.此外,垂直电子熔丝元件100包括一上间隙子层157、一层间介电层159以及一介电层161,上间隙子层157是覆盖导电层153a11、153a12、153a2,层间介电层159设置在上间隙子层157上并围绕上阳极/阴极区163设置,介电层161穿经层间介电层159与上间隙子层157。在一些实施例中,熔丝介电层151a11以及导电层153a11是与熔丝介电层151a12以及导电层153a12通过介电层161而分开设置。在一些实施例中,介电层161并未延伸进入硅化物层145a1与145a2中。换言之,下间隙子层147的一部分是夹置在介电层161与硅化物层145a1、145a2之间。

115.再者,垂直电子熔丝元件100包括一导电接触点167以及另一个介电层165,导电接

触点167设置在上阳极/阴极区163上,层间介电层165设置在介电层161与层间介电层159上并围绕导电接触点147。在一些实施例中,如图1所示的导电接触点167的两区段是实体连接在一起,其原因是该两区段为一连续环状结构的不同部分。在一些实施例中,导电接触点167电性连接到上阳极/阴极区163。

116.图2为依据本公开一些实施例一种垂直电子熔丝元件100的制备方法10的流程示意图,方法10包括步骤s11、s13、s15、s17、s19、s21、s23、s25、s27、s29、s31以及s33。方法10的步骤s11到s33是结合下列图式进行详细说明。

117.图3、图5、图7、图9及图12为依据一些实施例中形成垂直电子熔丝元件100的各中间阶段的顶视示意图,以及图4、图6、图8、图10、图11及图13为依据一些实施例中形成垂直电子熔丝元件100的各中间阶段的剖视示意图。应当理解,图4、图6、图8、图10、图11及图13分别为沿图3、图5、图7、图9及图12的剖线i-i’的剖视示意图。

118.如图3及图4所示,是提供一半导体基底101。半导体基底101可为一半导体晶圆,例如一硅晶圆。另外或此外,半导体基底101可包括元素(elementary)半导体材料、化合物(compound)半导体材料,及/或合金半导体材料。元素半导体材料的例子可包括晶体硅、多晶硅、非晶硅、锗及/或钻石,但并不以此为限。化合物半导体元件的例子可包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟,及/或锑化铟(indium antimonide),但并不以此为限。合金半导体材料可包括sige、gaasp、alinas、algaas、gainas、gainp,及/或gainasp,但并不以此为限。

119.在一些实施例中,半导体基底101具有一外延层(epitaxial layer)。举例来说,半导体基底101具有一外延层,是铺设在一块状(bulk)半导体上。在一些实施例中,半导体基底101为一绝缘体上覆半导体基底,其是可具有一基底、一埋入氧化物层以及一半导体层,该埋入式氧化物层是位在该基底上,该半导体层是位在该埋入式氧化物层上,而该绝缘体上覆半导体基底是例如一绝缘体上覆硅(soi)基底、一绝缘体上覆硅锗(sgoi)基底,或绝缘体上覆锗(goi)基底。绝缘体上覆半导体基底可使用植氧分离(separation by implantation of oxygen,simox)技术、晶圆接合(wafer bonding)或其他适合的方法进行制造。

120.仍请参考图3及图4,依据一些实施例,圆柱形结构103a、103b是形成在半导体基底101上,以及形成环状结构105a、105b以分别围绕圆柱形结构103a、103b。对应的步骤是绘示在如图2所示的方法10中的步骤s11。虽然仅绘示两个圆柱形结构以及两个环状结构,但应当理解,多于两个圆柱形结构以及多于两个环状结构是可实施在垂直电子熔丝元件100中。

121.在一些实施例中,圆柱形结构103a、103b的材料包括氧化硅、氮化硅、碳化硅、氮氧化硅、碳氧化硅(silicon oxycarbide,sioc)、碳氮化硅(silicon carbonitride,sicn)、碳氮氧化硅(silicon oxide carbonitride,siocn)、其他可应用的材料或其组合。再者,圆柱形结构103a、103b可通过一沉积制程以及一图案化制程所形成。举例来说,一材料层(图未示)可沉积在半导体基底101上,以及可图案化该材料层以形成圆柱形结构103a、103b。

122.沉积制程可包括一化学气相沉积(cvd)制程、一物理气相沉积(pvd)制程、一原子层沉积(ald)制程、一旋转涂布制程、其他可应用的制程或其组合。图案化制程可包括一微影制程以及一接下来的蚀刻制程。微影制程可形成多个光阻图案(图未示)在该材料层的一上表面上。微影制程可包括光阻涂布(例如旋转涂布)、软烘烤(soft baking)、遮罩对准

(mask aligning)、曝光、曝光前烘烤(post-exposure baking)、显影光阻、冲洗(rising)以及干燥(例如硬烘烤(hard baking))。蚀刻制程可为一干蚀刻制程、一湿蚀刻制程或其组合。

123.在一些实施例中,圆柱形结构103a、103b的各侧壁是分别完全被环状结构105a、105b所围绕,且圆柱形结构103a、103b的各侧壁是分别直接接触环状结构105a、105b。使用于形成环状结构105a、105b的一些材料与制程是类似于或相同于使用于形成圆柱形结构103a、103b的材料与制程,且在文中不再重复详细描述。然而,应当理解,环状结构105a、105b的材料是不同于圆柱形结构103a、103b的材料。

124.然后,如图5及图6所示,依据一些实施例,移除圆柱形结构103a、103b以形成开口110a、110b在环状结构105a、105b内,以及一遮罩材料107是形成在半导体基底101上以及在环状结构105a、105b上。对应的步骤是绘示在如图2所示的方法10中的步骤s13。

125.在一些实施例中,圆柱形结构103a、103b是通过一蚀刻制程而被移除,例如一干蚀刻制程。如前所述,圆柱形结构103a、103b的材料是不同于环状结构105a、105b的材料,以及选择所述材料以使圆柱形结构103a、103b相对于环状结构105a、105b的蚀刻选择性是高的。因此,圆柱形结构103a、103b可通过蚀刻制程所移除,同时环状结构105a、105b可被大致留下,并获得暴露半导体基底101的开口110a、110b。

126.用于形成遮罩材料107的一些材料与制程是类似于或相同于使用于形成圆柱形结构103a、103b的材料与制程,且在文中不再重复详细描述。在一些实施例中,遮罩材料107的材料是不同于环状结构105a、105b的材料。在一些实施例中,遮罩材料107是通过选择地生长或沉积一介电材料在环状结构105a、105b的各上表面上以及在半导体基底101通过环状结构105a、105b而暴露的所述部分上所形成。在一些实施例中,环状结构105a、105b的各侧壁是部分暴露。意即,环状结构105a、105b的各侧壁的所述部分并未被遮罩材料107所覆盖。在一些实施例中,遮罩材料107是通过一外延(epitaxial(epi))制程所形成。

127.接着,如图7及图8所示,依据一些实施例,内间隙子层113a1、113b1以及外间隙子层113a2、113b2设置在遮罩材料107上。对应的步骤是绘示在如图2所示的方法10中的步骤s15。在一些实施例中,内间隙子层113a1、113b1沉积在环状结构105a、105b上的各内侧壁sw3上,并直接接触环状结构105a、105b的各内侧壁sw3;外间隙子层113a2、113b2沉积在环状结构105a、105b的各外侧壁sw4上,并直接接触环状结构105a、105b的各外侧壁sw4。

128.再者,一开口120a是被内间隙子113a1所围绕,以及另一开口120b是被内间隙子层113b1所围绕。使用于形成内间隙子层113a1、113b1与外间隙子层113a2、113b2的一些材料与制程,是类似于或相同于使用于形成圆柱形结构103a、103b的材料与制程,且在文中不再重复详细描述。在一些实施例中,内间隙子层113a1、113b1与外间隙子层113a2、113b2是同时形成,且由相同材料所制。然而,应当理解,依据一些实施例,内间隙子层113a1、113b1与外间隙子层113a2、113b2的材料是不同于遮罩材料107的材料与环状结构105a、105b的材料。

129.接下来,如图9及图10所示,依据一些实施例,遮罩材料107是通过使用内间隙子层113a1、113b1与外间隙子层113a2、113b2当作一遮罩而蚀刻,以形成一遮罩层107’在半导体基底101上,然后,半导体基底101是通过使用遮罩层107’当作一遮罩而蚀刻,以形成熔丝链101a、101b、101c、101d在半导体基板101’上。对应的步骤是绘示在如图2所示的方法10中的

步骤s17及步骤s19。每一蚀刻制程可包括一干蚀刻制程、一湿蚀刻制程或其组合。

130.应当理解,是移除环状结构105a、105b与遮罩材料107通过内间隙子层113a1、113b1与外间隙子层113a2、113b2而暴露(例如并未被覆盖)的所述部分。在一些实施例中,是选择环状结构105a、105b、遮罩材料107、内间隙子层113a1、113b1以及外间隙子层113a2、113b2的材料,以使遮罩材料107与环状结构105a、105b相对于内间隙子层113a1、113b1与外间隙子层113a2、113b2的蚀刻选择性是高的。因此,环状结构105a、105b以及遮罩材料107的所述暴露部分是通过蚀刻制程而移除,同时内间隙子层113a1、113b1与外间隙子层113a2、113b2可大致地留下。

131.仍请参考图9及图10,凹陷130a1、130a2、130b1、130b2、130c是形成在半导体基底101中以及在半导体基板101’上。在一些实施例中,凹陷130a1是被熔丝链101a所围绕,以及熔丝链101a是被凹陷130a2所围绕。在一些实施例中,凹陷130b1是被熔丝链101b所围绕,以及熔丝链101b是被凹陷130b2所围绕。再者,依据一些实施例,凹陷130c是形成在熔丝链101c与101d之间。

132.应当理解,熔丝链101a、101b、101c、101d是从半导体基底101所形成。因此,熔丝链101a、101b、101c、101d的材料与半导体基底101的材料(例如半导体基板101’的材料)是为相同。此外,遮罩层107’是从遮罩材料107所形成。在一些实施例中,并未蚀刻遮罩材料107与半导体基底101在外间隙子层113a2、113b2的各周围区中的一些部分。

133.如图11所示,依据一些实施例,在凹陷130a1、130a2、130b1、130b2、130c形成之后,是执行一离子植入制程,以经由凹陷130a1、130a2、130b1、130b2、130c布植多个掺杂物进入熔丝链101a、101b、101c、101d。对应的步骤是绘示在如图2所示的方法10中的步骤s21。在一些实施例中,n型掺杂物是布植进入熔丝链101a、101b、101c、101d中,而n型掺杂物是例如磷(p)或砷(as)。在一些其他实施例中,p型掺杂物是布植进入熔丝链101a、101b、101c、101d中,而p型掺杂物是例如硼(b)、镓(ga)或铟(in)。熔丝链101a、101b、101c、101d。的导电形态是取决于垂直电子熔丝元件100的设计需求。

134.如图12及图13所示,依据一些实施例,在离子植入制程135执行之后,是移除内间隙子层113a1、113b1与外间隙子层113a2、113b2。在一些实施例中,内间隙子层113a1、113b1与外间隙子层113a2、113b2是通过一蚀刻制程而移除。蚀刻制程可为一湿蚀刻制程、一干蚀刻制程或其组合。

135.图14到图21为在图13中的区域a的部分放大剖视示意图,其是绘示依据一些实施例形成垂直电子熔丝元件100的各依序的中间阶段。虽然图14到图21仅绘示在图12及图13中的结构的一部分,但应当理解,其是易于图例说明;而且在图12及图13中的结构的其他部分可具有类似于在图14到图21中所图例的各特征。

136.如图14所示,依据一些实施例,在内间隙子层113a1、113b1与外间隙子层113a2、113b2移除之后,下阳极/阴极区141a1、141a2是外延生长在半导体基板101’上以及邻近熔丝链101a处。对应的步骤是绘示在如图2所示的方法10中的步骤s23。在一些实施例中,下阳极/阴极区141a1、141a2是分别外延生长在凹陷130a1、130a2中。

137.如上所述,如图14所示的下阳极/阴极区141a2的两区段是为一连续环状结构的不同两部分。在一些实施例中,下阳极/阴极区141a1是被熔丝链101a的下部bp所围绕,而且熔丝链101a的下部bp是被下阳极/阴极区141a2所围绕。在一些实施例中,下阳极/阴极区

141a1、141a2是直接接触熔丝链101a的相对侧壁sw1与sw2(例如内侧壁sw1以及外侧壁sw2)。

138.在一些实施例中,一应变材料(strained material)是通过一外延制程而生长位在半导体基板101’的凹陷130a1、130a2上,以形成下阳极/阴极区141a1、141a2。在一些实施例中,下阳极/阴极区141a1、141a2包括ge、sige、inas、ingasa、insb、gaas、gasb、inalp、inp或类似物。外延制程可包括一快速热化学气相沉积(rtcvd)制程、一超高真空化学气相沉积(uhvcvd)制程、一分子束外延法(mbe)制程、一金属有机空化学气相沉积(mocvd),或其他可应用的制程。

139.接着,如图15所示,依据一些实施例,另一个内间隙子层143a1形成在熔丝链101a的侧壁sw1上,并直接接触熔丝链101a的侧壁sw1;且另一个外间隙子层143a2形成在熔丝链101a的侧壁sw2上,并直接接触熔丝链101a的侧壁sw2。在一些实施例中,内间隙子层143a1形成在下阳极/阴极区141a1上,以及外间隙子层143a2形成在下阳极/阴极区141a2上。在内间隙子层143a1与外间隙子层143a2形成之后,熔丝链101a的侧壁sw1与sw2是完全被覆盖。

140.在一些实施例中,内间隙子层143a1与外间隙子层143a2是由介电材料所制,例如氧化硅、氮化硅、碳化硅、氮氧化硅、碳氧化硅(silicon oxycarbide,sioc)、碳氮化硅(silicon carbonitride,sicn)、碳氮氧化硅(silicon oxide carbonitride,siocn)、其他可应用的材料或其组合。在一些实施例中,内间隙子层143a1与外间隙子层143a2的材料是不同于遮罩层107’的材料。再者,内间隙子层143a1与外间隙子层143a2可通过一cvd制程、一pvd制程、一ald制程、其他可应用的制程或其组合所形成。

141.如图16所示,依据一些实施例,在内间隙子层143a1与外间隙子层143a2形成之后,硅化物层145a1、145a2分别形成在下阳极/阴极区141a1、141a2上。对应的步骤是绘示在如图2所示的方法10中的步骤s25。在一些实施例中,硅化物层145a1是直接接触内间隙子层143a1,以及硅化物层145a2是直接接触外间隙子层143a2。

142.在一些实施例中,硅化物层145a1、145a2是由一金属硅化物材料所制,例如硅化钴、硅化钛、硅化钽、硅化镍、硅化铜、硅化钨、硅化钼或其他可应用的材料。再者,硅化物层145a1、145a2可通过一硅化(silicidation)制程所形成。在一些实施例中,硅化制程包括依序执行的一金属材料沉积制程以及一退火制程。在一些实施例中,硅化制程的沉积制程包括一pvd制程、一ald制程或其他可应用的制程。在一些实施例中,在一温度下执行硅化制程的退火制程,该温度是介于大约400℃到大约700℃之间。在退火制程之后,是移除未反应的金属材料。

143.然后,如图17所示,依据一些实施例,移除内间隙子层143a1与外间隙子层143a2,以及形成一下间隙子层147以覆盖硅化物层145a1、145a2。对应的步骤是绘示在如图2所示的方法10中的步骤s27。在一些实施例中,下间隙子层147是直接接触熔丝链101a的侧壁sw1与sw2。

144.在一些实施例中,通过一选择蚀刻制程以移除内间隙子层143a1与外间隙子层143a2,例如一反应性离子蚀刻(rie)制程。内间隙子层143a1与外间隙子层143a2的移除是暴露熔丝链101a的侧壁sw1与sw2,且多个环状间隙(图未示)形成在硅化物层145a1与熔丝链101a之间以及形成在硅化物层145a2与熔丝链101a之间。然后,下间隙子层147沉积在硅化物层145a1、145a2上,以及下间隙子层147的一些部分延伸进入所述环状间隙。因此,下间

隙子层147是夹置在硅化物层145a1、145a2与熔丝链101a之间。在一些实施例中,硅化物层145a1、145a2与熔丝链101a的侧壁sw1、sw2是通过下间隙子层147而分开设置。

145.在一些实施例中,下间隙子层147是由一介电材料所制,例如氧化硅、氮化硅、碳化硅、氮氧化硅、碳氧化硅(silicon oxycarbide,sioc)、碳氮化硅(silicon carbonitride,sicn)、碳氮氧化硅(silicon oxide carbonitride,siocn)、其他可应用的材料或其组合。此外,下间隙子层147是通过一定向(directional)沉积制程所形成,例如一高密度等离子体(hdp)沉积制程、一气体团簇离子束(gas cluster ion beam,gcib)沉积制程或其他可应用的沉积制程。定向沉积制程较佳地沉积下间隙子层147的材料在多个暴露的水平表面,而不是在侧向的各侧壁上。在接下来的平坦化制程期间,将在之后移除形成在遮罩层107’的各上表面上的下间隙子层147的材料,而平坦化制程是例如化学机械研磨(cmp)制程。

146.接下来,如图18所示,依据一些实施例,熔丝介电层151a1、151a2形成在下间隙子层147上,以及导电层153a1、153a2形成在熔丝介电层151a1、151a2上。对应的步骤是绘示在如图2所示的方法10中的步骤s29。在一些实施例中,熔丝介电层151a1、151a2的一些部分是延伸到熔丝链101a的侧壁sw1与sw2上,以及导电层153a1、153a2与熔丝链101a的侧壁sw1、sw2是通过熔丝介电层151a1、151a2而分开设置。

147.每一熔丝介电层151a1、151a2可为一单一层或多层。在一些实施例中,熔丝介电层151a1、151a2是由氧化硅、氮化硅、氮氧化硅(sion)、具有高介电常数(high-k)的介电材料或其组合。在一些实施例中,熔丝介电层151a1、151a2是通过一cvd制程、一pvd制程、一ald制程、一等离子体加强化学气相沉积(pecvd)制程、一旋转涂布制程或其他可应用的制程所沉积。

148.再者,依据一些实施例,导电层153a1、153a2是由一导电材料所制,例如铝(al)、铜(cu)、钨(w)、钛(ti)、钽(ta)或其他可应用的材料。导电层153a1、153a2可通过一沉积制程所形成,而沉积制程是例如一cvd制程、一pvd制程、一ald制程、一hdpcvd制程、一mocvd制程或一pecvd制程。

149.在熔丝介电层151a1、151a2与导电层153a1、153a2的材料沉积之后,是通过一单一蚀刻制程或多个蚀刻制程移除熔丝介电层151a1、151a2与导电层153a1、153a2的多余材料,而蚀刻制程是例如干蚀刻制程。因此,熔丝介电层151a1、151a2的各上表面与导电层153a1、153a2的各上表面是较低于遮罩层107’的上表面。在一些实施例中,熔丝介电层151a1、151a2与导电层153a1、153a2的各上表面是较低于熔丝链101a的上表面,以使熔丝链101a的侧壁sw1与sw2部分暴露。

150.接着,如图19所示,依据一些实施例,形成一上间隙子层157以覆盖熔丝介电层151a1、151a2与导电层153a1、153a2,以及一层间介电层159形成在上间隙子层157上。对应的步骤是绘示在如图2所示的方法10中的步骤s31。在一些实施例中,上间隙子层157是直接接触熔丝链101a的侧壁sw1与sw2的各上部。用于形成上间隙子层157的一些材料与制程是类似于或相同于使用于形成下间隙子层147的材料与制程,且在文中不再重复其详细描述。

151.层间介电层159可为一单一层或多层。在一些实施例中,层间介电层159的材料包括氧化硅、氮化硅、氮氧化硅、四乙氧基硅烷(tetraethoxysilane,teos)氧化物、磷硅酸盐玻璃(phosphosilicate glass,psg)、硼磷硅酸盐玻璃(borophosphosilicate glass,bpsg)、低介电材料或其他可应用的介电材料。层间介电层159可由一cvd制程、一pvd制程、

一ald制程、一旋转涂布制程或其他可应用制程所形成。后来,一平坦化制程可执行在层间介电层15上,直到遮罩层107’的上表面暴露为止,而平坦化制程是例如一cmp制程。

152.如图20所示,依据一些实施例,形成一介电层161以穿经层间介电层159、上间隙子层157、导电层153a1与153a2以及熔丝介电层151a1与151a2。介电层161可由下列材料所制:氧化硅、氮化硅、氮氧化硅或其他可应用的介电材料;以及介电层161的形成可包括形成一图案化遮罩(图未示)在图19的结构上;蚀刻层间介电层159、上间隙子层157、导电层153a1与153a2以及熔丝介电层151a1与151a2,以通过使用图案化遮罩当作一遮罩而形成多个开口(图未示);沉积一介电材料在所述开口中以及在层间介电层159与遮罩层107’上;以及研磨介电材料,直到遮罩层107’的上表面暴露为止。

153.在一些实施例中,在用于形成介电层161的蚀刻制程期间,是部分蚀刻下间隙子层147。因此,介电层161的下表面可较低于下间隙子层147的上表面。然而,应当理解,介电层161并未穿经下间隙子层147。意即,介电层161与硅化物层145a1、145a2是通过下间隙子层147而分开设置。在介电层161形成之后,是获得导电层153a1、153a2以及熔丝介电层151a11、151a12。

154.如图21所示,依据一些实施例,在层间介电层161形成之后,是外延生长一上阳极/阴极区163以取代遮罩层107’。对应的步骤是绘示在如图2所示的方法10中的步骤s33。更特别地是,依据一些实施例,是移除遮罩层107’,以及上阳极/阴极区163是外延生长在熔丝链101a的上表面上。

155.在一些实施例中,通过一蚀刻制程以移除遮罩层107’,而蚀刻制程是如一湿蚀刻制程。依据一些实施例,在遮罩层107’移除之后,熔丝链101a的上表面ts以及层间介电层159的各侧壁是通过一环状开口(图未示)而暴露,以及上阳极/阴极区163是外延生长在环状开口中。用于形成上阳极/阴极区163的一些材料与制程是类似于或相同于使用于形成下阳极/阴极区141a1、141a2的材料与制程,且在文中不再重复其详细描述。

156.在一些实施例中,在其外延生长期间,上阳极/阴极区163是原位掺杂n型或p型掺杂物。在一些实施例中,在其外延生长期间,上阳极/阴极区163并未掺杂。反而是,在上阳极/阴极区163生长之后,上阳极/阴极区163是在接下来的制程中掺杂,例如一离子植入制程。特别是,如图21所示,依据一些实施例,在其外延生长期间,由于上阳极/阴极区163在(111)定向表面上具有较慢的生长率,所以上阳极/阴极区163具有多个刻面部(faceted portions)。在一些实施例中,上阳极/阴极区163是直接接触熔丝链101a的上表面tp。

157.如图1所示,依据一些实施例,在上阳极/阴极区163外延生长之后,一层间介电层165形成在图21的结构上,以及一导电接触点形成在层间介电层165中以及在上阳极/阴极区163上。在一些实施例中,导电接触点167是覆盖并直接接触上阳极/阴极区163的所述刻面部。使用于形成层间介电层1654的一些材料与制程是类似于或相同于使用于形成层间介电层159的材料与制程,且在文中不再重复其详细叙述。

158.在一些实施例中,导电接触点167是由下列材料所制:铜(cu)、铜合金、铝(al)、铝合金、钨(w)、钨合金、钛(ti)、钛合金、钽(ta)、钽合金或其组合。或者是,可使用其他可应用的材料。再者,导电接触点167的形成可包括形成一图案化遮罩(图未示)在层间介电层165上;通过使用图案化遮罩当作一遮罩而蚀刻层间介电层165,以形成一开口(图未示),进而部分暴露上阳极/阴极区163;沉积导电接触点167的材料在开口中以及在层间介电层165

上;以及研磨导电接触点167的材料,直到层间介电层165的上表面暴露为止。在导电接触点167形成之后,是获得垂直电子熔丝元件100。

159.在本公开中是提供一垂直电子熔丝元件100的多个实施例。由于垂直电子熔丝元件100的熔丝链101a配置在下阳极/阴极区141a1、141a2与上阳极/阴极区163之间的垂直方向上,所以垂直电子熔丝元件100可与其他半导体元件整合在一起,例如一鳍式场效晶体管(finfet)元件,且垂直电子熔丝元件100可与所述finfet元件一体形成,而无须额外的处理步骤。

160.在本公开的一实施例中,是提供一种垂直电子熔丝元件。该垂直电子熔丝元件具有一熔丝链(fuse link),设置在一半导体基板(semiconductor base)上。该熔丝链的材料以及该半导体基板的材料为相同。该垂直电子熔丝元件亦具有一第一下阳极/阴极区以及一第二下阳极/阴极区,该第一下阳极/阴极区与该第二下阳极/阴极区设置在该半导体基板上。该熔丝链的一下部夹置在该第一下阳极/阴极区与该第二下阳极/阴极区之间。该垂直电子熔丝元件还具有一上阳极/阴极区,设置在该熔丝链上。

161.在本公开的另一实施例中,是提供一种垂直电子熔丝元件。该垂直电子熔丝元件具有一环形熔丝链,设置在一半导体基板上。该环状熔丝链的材料与该半导体基板的材料是相同。该垂直电子熔丝元件亦具有一第一下阳极/阴极区,是被该环状熔丝链的一下部所围绕;以及一第二下阳极/阴极区,围绕该环状熔丝链的该下部设置。该垂直电子熔丝元件还具有一上阳极/阴极区,设置在该环状熔丝链上。

162.在本公开的再另一实施例中,是提供一种垂直电子熔丝元件的制备方法。该制备方法包括:形成一遮罩层在一半导体基底上;以及蚀刻该半导体基底并使用该遮罩层当作一遮罩,以形成一熔丝链在一半导体基板上。该方法亦包括外延生长一第一下阳极/阴极区以及一第二下阳极/阴极区在该半导体基板上以及邻近该熔丝链的一下部处。该熔丝链位在该第一下阳极/阴极区与该第二下阳极/阴极区之间。该方法还包括外延生长一上阳极/阴极区,以取代该遮罩层。

163.在本公开的所述实施例具有一些有益的优点。通过该熔丝链延伸在所述下阳极/阴极区与该上阳极/阴极区之间的垂直方向上,所以该垂直电子熔丝元件可与其他半导体元件整合在一起,例如一鳍式场效晶体管(finfet)元件,且该垂直电子熔丝元件可与所述finfet元件一体形成,而无须额外的处理步骤。

164.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

165.再者,本技术案的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本技术案的权利要求内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1