次级感测放大器与半导体存储装置的制作方法

1.本发明涉及一种存储器装置布局,且特别是涉及一种次级感测放大器与半导体存储装置。

背景技术:

2.动态随机存取存储器(dynamic random access memory,dram)是一种随机存取的半导体存储器。一般来说,dram配置有多个存储单元阵列、次级x解码器和感测放大器电路。为了提升操作速度,感测放大器电路可以包括感测放大器和次级感测放大器。

3.由于次级感测放大器具有较为复杂的连线,因此面积比其他电路大,并且因此对芯片尺寸的小型化发展造成冲击。此外,由于芯片成本的关系,次级感测放大器的面积越大,整体成本越高。

技术实现要素:

4.本发明提供一种次级感测放大器,具有较小的布局以降低成本。

5.本发明另提供一种半导体存储装置,以获得高品质的次级感测放大器特性。

6.本发明的次级感测放大器,包括半导体基板、第一对互补晶体管、第二对互补晶体管以及至少一接地晶体管。第一对互补晶体管形成于所述半导体基板上,所述第一对互补晶体管以次级感测放大器的一中心线为对称轴而呈线对称地配置,并且所述第一对互补晶体管的栅极耦合至一节点。第二对互补晶体管形成于所述半导体基板上,所述第二对互补晶体管以次级感测放大器的中心线为对称轴而呈线对称地配置,其中所述第一对互补晶体管的源极耦合至所述第二对互补晶体管的栅极,且所述第一对互补晶体管的漏极耦合至所述第二对互补晶体管的源极。接地晶体管形成于所述半导体基板上,所述接地晶体管与所述第二对互补晶体管串联。所述第二对互补晶体管中的一个晶体管的电流方向与另一个晶体管的电流方向相同。

7.在本发明的一实施例中,上述第一对互补晶体管中的一个晶体管的电流方向与另一个晶体管的电流方向相同。

8.在本发明的一实施例中,上述至少一接地晶体管是第三对互补晶体管,且所述第三对互补晶体管以所述次级感测放大器的所述中心线为所述对称轴而呈线对称地配置。

9.在本发明的一实施例中,上述次级感测放大器还可包括第一扩散区与第二扩散区。第一扩散区位于所述半导体基板内,其中第一对互补晶体管的一个晶体管与第二对互补晶体管的一个晶体管设置在所述第一扩散区内。第二扩散区位于所述半导体基板内,其中第一对互补晶体管的另一个晶体管与第二对互补晶体管的另一个晶体管设置在所述第二扩散区内。

10.在本发明的一实施例中,上述第一扩散区和上述第二扩散区分离。

11.在本发明的一实施例中,上述第一对互补晶体管与上述第二对互补晶体管设置在垂直于所述中心线的方向上的第三对互补晶体管之间。

12.在本发明的一实施例中,上述第三对互补晶体管中的一个晶体管的电流方向与另一个晶体管的电流方向相同。

13.在本发明的一实施例中,上述次级感测放大器还可包括第三扩散区,位于所述半导体基板内,其中第二对互补晶体管与第三对互补晶体管设置在所述第三扩散区内。

14.在本发明的一实施例中,上述第二对互补晶体管与上述第三对互补晶体管设置在垂直于所述中心线的方向上的第一对互补晶体管之间。

15.在本发明的一实施例中,上述至少一接地晶体管是单一晶体管。

16.在本发明的一实施例中,上述次级感测放大器还可包括第四扩散区,位于所述半导体基板内,其中所述第二对互补晶体管与所述单一晶体管设置在所述第四扩散区内。

17.在本发明的一实施例中,上述第二对互补晶体管与上述单一晶体管设置在垂直于所述中心线的方向上的第一对互补晶体管之间。

18.在本发明的一实施例中,上述次级感测放大器还可包括用于内连线的数个接触窗与数条布线。

19.在本发明的一实施例中,用于连接第一对互补晶体管中的一个晶体管的源极至第二对互补晶体管中的一个晶体管的栅极的所述接触窗的数量等同于用于连接第一对互补晶体管中的另一个晶体管的源极至第二对互补晶体管中的另一个晶体管的栅极的所述接触窗的数量。

20.在本发明的一实施例中,用于连接第一对互补晶体管中的一个晶体管的漏极至第二对互补晶体管中的一个晶体管的源极的所述接触窗的数量等同于用于连接第一对互补晶体管中的另一个晶体管的漏极至第二对互补晶体管中的另一个晶体管的源极的所述接触窗的数量。

21.在本发明的一实施例中,用于连接第一对互补晶体管中的一个晶体管的源极至第二对互补晶体管中的一个晶体管的栅极的所述布线的电阻等同于用于连接第一对互补晶体管中的另一个晶体管的源极至第二对互补晶体管中的另一个晶体管的栅极的所述布线的电阻。

22.在本发明的一实施例中,用于连接第一对互补晶体管中的一个晶体管的漏极至第二对互补晶体管中的一个晶体管的源极的所述布线的电阻等同于用于连接第一对互补晶体管中的另一个晶体管的漏极至第二对互补晶体管中的另一个晶体管的源极的所述布线的电阻。

23.本发明的半导体存储装置,包括数个存储单元阵列、第一感测放大器与第二感测放大器、感测放大器驱动器以及次级感测放大器。次级感测放大器为上述实施例中的次级感测放大器。每个存储单元阵列具有相对的一对第一侧边与一对第二侧边。第一感测放大器与第二感测放大器沿第一方向设置于接近所述存储单元阵列的第一侧边,其中所述第一方向平行于第一侧边。感测放大器驱动器设置于第一感测放大器与第二感测放大器之间,其中所述感测放大器驱动器具有平行于第二方向的宽度,第二方向垂直于所述第一方向。上述次级感测放大器设置在第一感测放大器与第二感测放大器之间的所述感测放大器驱动器旁,其中所述次级感测放大器具有与感测放大器驱动器的宽度相同的宽度,且所述次级感测放大器的中心线平行于所述第二方向。

24.在本发明的另一实施例中,上述半导体存储装置还可包括次级x解码器沿所述第

二方向设置于接近存储单元阵列的第二侧边。

25.在本发明的另一实施例中,上述感测放大器驱动器的所述宽度是根据设计规则(design rule)定义的最小空间。

26.基于上述,由于本发明提供了一种具有相同电流方向的互补晶体管的次级感测放大器,因此可以避免读取延迟或失效(malfunction),并且获得高品质的次级感测放大器。

27.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

28.图1a是本发明的第一实施例的一种次级感测放大器的俯视图;

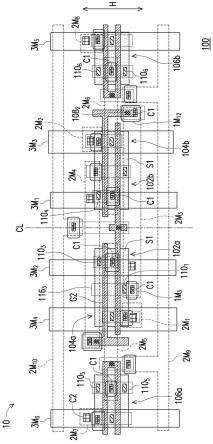

29.图1b是图1a的次级感测放大器及其上层连线的俯视图;

30.图1c是图1b的次级感测放大器及其上层连线的俯视图;

31.图1d是图1b的次级感测放大器上方的上层连线的俯视图;

32.图2是图1c的次级感测放大器的电路图;

33.图3a是本发明的第二实施例的一种次级感测放大器的俯视图;

34.图3b是图3a的次级感测放大器及其上层连线的俯视图;

35.图3c是图3b的次级感测放大器及其上层连线的俯视图;

36.图3d是图3b的次级感测放大器上方的上层连线的俯视图;

37.图4a是本发明的第三实施例的一种次级感测放大器的俯视图;

38.图4b是图4a的次级感测放大器及其上层连线的俯视图;

39.图4c是图4b的次级感测放大器及其上层连线的俯视图;

40.图4d是图4b的次级感测放大器上方的上层连线的俯视图;

41.图5是图4c的次级感测放大器的电路图;

42.图6是本发明第四实施例的一种半导体存储器元件的方块图。

43.符号说明

44.10、30、40、608:次级放大感测器

45.100:半导体基板

46.102a、102b、602(sa1):第一对互补晶体管

47.104a、104b、604(sa2):第二对互补晶体管

48.106a、106b:第三对互补晶体管

49.108

1-3

:栅极接触窗

50.110

1-6

:场接触窗

51.112:第一扩散区

52.114:第二扩散区

53.116

1-18

:导线

54.1m

1-18

:第一金属层

55.2m

1-10

:第二金属层

56.3m

1-6

:第三金属层

57.300:第三扩散区

58.400:单一晶体管

59.402:第四扩散区

60.60:半导体存储装置

61.600:存储单元阵列

62.600a:第一侧边

63.600b:第二侧边

64.606:感测放大器驱动器

65.610:次级x轴解码器

66.c1、c2:接触窗

67.cl:中心线

68.d1:漏极

69.g1、g2:栅极

70.h:宽度

71.i1a、i1b、i2a、i2b、i3a、i3b、i4:电流方向

72.n1:节点

73.r1-r8、r51、r52:连线电阻

74.s1、s2:源极

具体实施方式

75.以下实施例中所附的附图是为了能更完整地描述本发明的实施例,然而本发明仍可使用许多不同的形式来实施,不应被解释为限于以下描述的实施例。在不超出本发明的范围的情况下,可以利用其他实施例,并且进行结构上、逻辑上和电路上的改变。为了清楚起见,各个区域或膜层的相对厚度、距离及位置可能缩小或放大。另外,在附图中使用相似或相同的元件符号表示相似或相同的部位或特征的存在。

76.图1a是根据本发明的第一实施例的一种次级感测放大器的俯视图。

77.请参照图1a,所述次级感测放大器10包括半导体基板100、第一对互补晶体管102a与102b、第二对互补晶体管104a与104b以及至少一接地晶体管,其中所述至少一接地晶体管例如第三对互补晶体管106a与106b。第一对互补晶体管102a与102b形成于半导体基板100上并以次级感测放大器10的中心线cl为对称轴而呈线对称地配置,并且所述第一对互补晶体管102a与102b的两个栅极g1都通过一栅极接触窗1081耦合至一节点n1,其中所述节点n1可与中心线cl对齐。上述第一对互补晶体管中的一个晶体管102a的电流方向i1a与另一个晶体管102b的电流方向i1b相同。

78.第二对互补晶体管104a与104b形成于所述半导体基板100上,并以次级感测放大器10的中心线cl为对称轴而呈线对称地配置,并且所述第二对互补晶体管中的一个晶体管104a的电流方向i2a与另一个晶体管104b的电流方向i2b相同。在第一实施例中,所述第一对互补晶体管102a与102b的漏极d1耦合至所述第二对互补晶体管104a与104b的源极s2。第一对互补晶体管中的一个晶体管102a的源极s1通过上层连线(如栅极接触窗1082、场接触窗1101以及后续描述的连线)耦合至第二对互补晶体管中的另一个晶体管104b的栅极g2。第一对互补晶体管中的另一个晶体管102b的源极s1通过上层连线(如栅极接触窗1083、场

接触窗1102以及后续描述的连线)耦合至第二对互补晶体管中的一个晶体管104a的栅极g2。在本实施例中,所述互补晶体管如102a与102b、104a与104b或106a与106b都被设计为具有相同的时序(timing)与电流承受能力(current capability)来运作。

79.第三对互补晶体管106a与106b(亦即接地晶体管)形成于所述半导体基板100上,并通过上层连线(未示出)与第二对互补晶体管104a与104b串联,并且所述第三对互补晶体管106a与106b也以次级感测放大器10的中心线cl为对称轴而呈线对称地配置。因此,所有晶体管包含102a、102b、104a、104b、106a与106b都可形成在宽度h的范围内,宽度h是由感测放大器驱动器(未示出)的宽度的设计规则(design rule)定义的最小空间。

80.请继续参照图1a,次级感测放大器10还可包括位于半导体基板100内的第一扩散区112与第二扩散区114,且第一扩散区112是和第二扩散区114分离的。第一对互补晶体管的一个晶体管102a与第二对互补晶体管的一个晶体管104a设置在所述第一扩散区112内。第一对互补晶体管的另一个晶体管102b与第二对互补晶体管的另一个晶体管104b设置在所述第二扩散区114内。第一扩散区112与第二扩散区114可为阱区,且因此第一对互补晶体管的一个晶体管102a的源极s1以及第二对互补晶体管的一个晶体管104a的源极s2都形成于第二扩散区114内;依此类推。第一对互补晶体管102a与102b以及第二对互补晶体管104a与104b则是设置在垂直于中心线cl的方向上的第三对互补晶体管106a与106b之间。

81.图1b是图1a的次级感测放大器及其上层连线的俯视图,且图1c是图1b的次级感测放大器及其上层连线的俯视图。这两个图是为了阐明本发明的第一实施例的次级感测放大器的内连线而绘制。

82.请参照图1b,在图1a的结构上方的上层连线例如有导线116

1-15

、第一金属层1m

1-15

以及用来连接导线116

1-15

、第一金属层1m

1-15

与上层的金属(例如图1c的2m

1-10

)的接触窗c1。导线116

1-15

例如是由钨(w)制成的。

83.请参照图1c,在图1b的结构上方的上层连线例如有第二金属层2m

1-10

、第三金属层3m

1-6

以及用来连接2m

1-10

与3m

1-6

的接触窗c2。因此,在一实施例中,互补晶体管102a的源极s1与互补晶体管104b的栅极g2之间的内连线包括场接触窗1101、导线1163、一个接触窗c1、第一金属层1m3、第二金属层2m3、第一金属层1m

12

、另一个接触窗c1、导线116

12

与栅极接触窗1082。

84.图2是图1c的次级感测放大器的电路图。

85.请参照图2,为了获得高品质的次级感测放大器10,需求一种具有一致的电阻和电流方向的互补晶体管的品质布局(quality layout)。例如,希望使连线电阻r1和r2、r3和r4、r5和r6、r7和r8具有相同的数值,因此接触窗的数量和/或位置以及布线的类型和宽度可以设计成相同的。例如,在图1c中,第二金属层2m5和2m6(即布线)具有相同的类型和宽度,并且用于将互补晶体管104a连接到互补晶体管106a的接触窗c1和场接触窗110

3-6

的数量和/或位置与那些用于将互补晶体管104b连接到互补晶体管106b的相同,因此连线电阻r5和r6的数值相同。此外,布线的电阻可以在宽度和长度上进行调整,以使其相同。

86.为了明确电路图与布局之间的连线电阻r1-r8的相对位置,请参照图1d。图1d是图1b的次级感测放大器上方的上层连线的俯视图。举例来说,连线电阻r4是形成在第二金属层2m3,第二金属层2m3是用来连接互补晶体管102b的源极s1与互补晶体管104a的栅极g2;依此类推。

87.图3a是根据本发明的第二实施例的一种次级感测放大器的俯视图,其中使用第一实施例的元件符号来表示相同或类似的构件。相同的构件的说明可参照上述的相关内容,于此不再赘述。

88.请继续参照图3a,所述次级感测放大器30同样包括半导体基板100、第一对互补晶体管102a与102b、第二对互补晶体管104a与104b以及第三对互补晶体管106a与106b(亦即接地晶体管)。然而,第二对互补晶体管104a与104b以及第三对互补晶体管106a与106b是设置在垂直于中心线cl的方向上的第一对互补晶体管102a与102b之间。因此,第二对互补晶体管中的一个晶体管104a的电流方向i2a与另一个晶体管104b的电流方向i2b相同,且第三对互补晶体管中的一个晶体管106a的电流方向i3a与第三对互补晶体管中的另一个晶体管106b的电流方向i3b相同。所述第一对互补晶体管102a与102b的两个栅极g1都通过栅极接触窗1081与后续描述的连线耦合至一节点(未示出)。此外,次级感测放大器30还包括一第三扩散区300位于所述半导体基板100内,且第二对互补晶体管104a与104b以及第三对互补晶体管106a与106b是设置在所述第三扩散区300内。第二扩散区300可为阱区,且因此第二对互补晶体管的一个晶体管104a的源极/漏极以及第三对互补晶体管的一个晶体管106a的源极/漏极都可形成于第三扩散区300内;依此类推。在第二实施例中,所述互补晶体管如102a与102b、104a与104b或106a与106b也都被设计为具有相同的时序与电流承受能力来运作。

89.图3b是图3a的次级感测放大器及其上层连线的俯视图,且图3c是图3b的次级感测放大器及其上层连线的俯视图。这两个图是为了阐明本发明的第二实施例的次级感测放大器的内连线而绘制,且使用第一实施例的元件符号来表示相同或类似的构件。

90.请参照图3b,在图3a的结构上方的上层连线例如有导线116

1-18

、第一金属层1m

1-18

以及用来连接导线116

1-18

、第一金属层1m

1-18

与上层的金属(例如图3c的2m

1-8

)的接触窗c1。导线116

1-18

例如是由钨(w)制成的。

91.请参照图3c,在图3b的结构上方的上层连线例如有第二金属层2m

1-8

、第三金属层3m

1-6

以及用来连接2m

1-8

与3m

1-6

的接触窗c2。因此,第一对互补晶体管102a与102b的两个栅极g1之间的内连线包括一个栅极接触窗1081、导线1169、一个接触窗c1、第一金属层1m9、第二金属层2m8、第一金属层1m

18

、另一个接触窗c1、导线116

18

与另一个栅极接触窗1081。

92.图3c的次级感测放大器的电路图与图2所示的相同,且为了明确电路图与布局之间的连线电阻r1-r8的相对位置,请参照图3d。

93.图3d是图3b的次级感测放大器上方的上层连线的俯视图。举例来说,连线电阻r4是形成在第二金属层2m4,且第二金属层2m4是用来连接互补晶体管102b的源极s1与互补晶体管104a的栅极g2;依此类推。如同第一实施例,接触窗的数量和/或位置以及布线的类型和宽度可以设计成相同的,以使连线电阻r1和r2、r3和r4、r5和r6、r7和r8具有相同的数值。

94.图4a是根据本发明的第三实施例的一种次级感测放大器的俯视图,其中使用第二实施例的元件符号来表示相同或类似的构件。相同的构件的说明可参照上述的相关内容,于此不再赘述。

95.请参照图4a,所述次级感测放大器40包括半导体基板100、第一对互补晶体管102a与102b、第二对互补晶体管104a与104b以及作为接地晶体管的单一晶体管400。第二对互补晶体管104a与104b与单一晶体管400设置在垂直于中心线cl的方向上的第一对互补晶体管

102a与102b之间。次级感测放大器40还可包括一第四扩散区402位于所述半导体基板100内,其中第二对互补晶体管104a与104b与单一晶体管400设置在所述第四扩散区402内。第四扩散区402可为阱区。由于次级感测放大器40的布局与次级感测放大器30类似,所以第二对互补晶体管中的一个晶体管104a的电流方向i2a也与第二对互补晶体管中的另一个晶体管104b的电流方向i2b相同,且单一晶体管400的电流方向i4与电流方向i2a相同。

96.在第三实施例中,所述互补晶体管如102a与102b或104a与104b也都被设计为具有相同的时序与电流承受能力来运作。

97.图4b是图4a的次级感测放大器及其上层连线的俯视图,且图4c是图4b的次级感测放大器及其上层连线的俯视图。这两个图是为了阐明本发明的第三实施例的次级感测放大器的内连线而绘制,且使用第二实施例的元件符号来表示相同或类似的构件。第三实施例与第二实施例的差异在于第四扩散区402的范围以及接地晶体管是单一晶体管400。

98.图4c的次级感测放大器的电路图如图5所示,且为了明确电路图与布局之间的连线电阻r1~r6的相对位置,请参照图4d。

99.图4d是图4b的次级感测放大器上方的上层连线的俯视图。举例来说,连线电阻r6是形成在第二金属层2m5,第二金属层2m5是用来连接单一晶体管400的漏极d4到第三金属层3m1;依此类推。如同第一实施例,接触窗的数量和/或位置以及布线的类型和宽度可以设计成相同的,以使连线电阻r1和r2、r3和r4、r51和r52具有相同的数值。

100.图6是根据本发明第四实施例的一种半导体存储器元件的方块图。

101.请参照图6,所述半导体存储装置60包括数个存储单元阵列600,且每个存储单元阵列600具有彼此相对的一对第一侧边600a与一对第二侧边600b。半导体存储装置60还包括第一感测放大器(sa1)602与第二感测放大器(sa2)604、感测放大器驱动器606以及次级感测放大器608,其中次级感测放大器608可以是上述实施例中的一种次级感测放大器。第一感测放大器602与第二感测放大器604沿第一方向设置于接近所述存储单元阵列600的第一侧边600a,其中所述第一方向平行于第一侧边600a。感测放大器驱动器606设置于第一感测放大器602与第二感测放大器604之间,其中所述感测放大器驱动器606具有平行于第二方向的宽度h,第二方向垂直于所述第一方向,其中感测放大器驱动器606的宽度h例如是根据设计规则(design rule)定义的最小空间。所述次级感测放大器608设置在第一感测放大器602与第二感测放大器604之间的感测放大器驱动器606旁,其中次级感测放大器608具有与感测放大器驱动器606的宽度h相同的宽度,且所述次级感测放大器608的中心线平行于所述第二方向。在一实施例中,半导体存储装置60还可包括次级x解码器(sub x-decoder)610,沿所述第二方向设置于接近存储单元阵列600的第二侧边600b。

102.综上所述,本发明的次级感测放大器具有与感测放大器驱动器的宽度相同的宽度,因此芯片成本可因为次级感测放大器的小面积而降低。此外,本发明的次级感测放大器包括具有相同电流方向的互补晶体管,即使在通道和侧壁形状上存在制造差异,也可以保持晶体管的操作速率(operating speed)。因此,可以避免读取操作上的延迟或失效。

103.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1