ONO工艺中的HTO氧化层工艺方法与流程

ono工艺中的hto氧化层工艺方法

1.技术领域

2.本发明涉及半导体器件的制造及测试领域,特别是指一种存储器的ono工艺中的氧化层厚度补偿方法。

背景技术:

3.非挥发性存储器(nvm)技术,主要有浮栅(floating gate)技术、分压栅(split gate)技术以及sonos(silicon

‑

oxide

‑

nitride

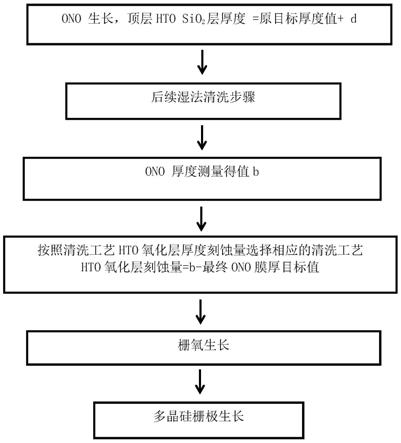

‑

oxide

‑

silicon)技术。sonos技术应用广泛,具有操作电压低、速度快、容量大、抗擦写能力强、低工作电压和低功耗等优点。具有低操作电压、更好的coms工艺兼容性的sonos技术被广泛用于各种嵌入式电子产品如金融ic卡、汽车电子等应用。

4.目前半导体制造技术中常用的sonos存储器剖面如图1所示,1是衬底,2是多晶硅栅极,3是氧化层/氮化硅/氧化层三明治结构(ono,oxide

‑

nitride

‑

oxide,包括顶部氧化层303,中间氮化硅层302,沟道氧化层(底层氧化层)301)。其中氮化硅层302用于电荷存储,沟道氧化层301为电荷擦写通道,顶部氧化层303用于防止存储电荷挥发。4是n型源、漏注入区,5是绝缘介质侧墙(氮化硅或氧化硅材质)。ono层如图2所示。

5.sonos闪存器件读写过程是通过对cg(control gate,控制栅)施加一个电压使得电子通过隧道氧化层存储于氮化层中,因此ono结构的制备至关重要。其中,隧道氧化层的质量、均一性以及si/sio2界面的完整性会影响隧穿过程,以及sio2的氮化层中n含量控制等等都会影响到读写速率、数据保持能力(date retention),进而影响器件可靠性(reliability)。12寸工艺高压、低压氧化及退火这些大量的热过程会对sonos闪存的超薄隧道氧化层以及存储层的负面影响指数上升。

6.ono结构的现有制造工艺中,底部二氧化硅一般采用热生长(消耗硅衬底)或lpcvd (low pressure chemical vapor deposition,低压化学气相沉积)淀积工艺(不消耗硅衬底),一般包括炉管热氧化、掺氮、热退火等步骤,二氧化硅表面通过离子注入和热退火,或通过炉管 n2o高温氮化表面二氧化硅和热退火引入si

‑

n键,提高二氧化硅的可靠性,以及和氮化硅的结合强度;夹层氮化硅的制造工艺一般采用炉管 lpcvd 淀积,为了得到较好均匀度和可控性的夹层氮化硅,常采用低温氮化硅工艺,后加高温氮化硅致密化工艺来实现;顶层二氧化硅一般采用炉管的 hto工艺(high temperature oxidation,高温氧化)淀积,再经过hto致密化工艺,通常的反应气体是二氯硅烷和一氧化二氮,反应方程式:sih2cl2+n2o

→

sio2+n2+hcl。

7.对于sonos型嵌入式存储器而言,其存储单元栅极介质层采用ono结构,ono中的每一层的厚度都必须严格控制,否则对于存储单元的vt窗口(写入和擦除后的vt之差)会有直接的影响。而存储单元的vt窗口就是存储单元用来区分“0”和“1”的依据。更进一步的,ono厚度变化对于存储单元的可靠性也可能造成影响。

8.在sonos型嵌入式存储器制造过程中,在硅衬底上生长ono层之后,还需要经过很多湿法清洗步骤才能在ono上生长多晶硅层,至此ono层才算被覆盖保护住。而这中间的湿法清洗步骤会对ono层中的最上层o即hto 氧化层产生腐蚀,从而造成最终的ono层的总体厚度减薄,造成存储单元的vt窗口的不一致。如图3所示,显示编程电压vtp与顶层hto氧化层厚度之间的关系,图4所示为擦除电压vte与顶层hto氧化膜厚度之间的关系,数据显示1

å

厚度的hto氧化膜厚度差异会带来30mv的 vte电压变化以及30mv的vtp电压变化,整体就是60mv的存储单元vt窗口。而现有的工艺中,假如ono膜厚度生长误差为

±1å

,这个误差已经没有减小的余地,无法调整;后续湿法腐蚀工艺去除15

å

厚度的膜层,湿法腐蚀工艺误差

±

10%,这又会导致有

±

1.5

å

的厚度差异,整体就是

±

(1

å

+1.5

å

)=

±

2.5

å

的hto氧化膜厚度变化,带来

±

150mv差异的存储单元vt窗口。

技术实现要素:

9.本发明所要解决的技术问题在于提供一种ono工艺中的hto氧化层工艺方法,使ono层总体厚度保持一定的工艺稳定性。

10.为解决上述问题,本发明所述的ono工艺中的hto氧化层工艺方法,在进行ono工艺时,顶层氧化层实际生长的厚度比设计厚度目标值增加厚度d;在此基础上:步骤一,ono层生长,完成后整体的ono层厚度为原目标厚度值+ d;工艺误差

±1å

。

11.步骤二,湿法清洗步骤,目标刻蚀量为c,误差

±

10%。

12.步骤三, 测量ono层的整体厚度,ono层厚度测量值为b。

13.步骤四,根据步骤三中计算出的刻蚀最终目标值选择相应的栅氧化层生长前的清洗工艺,栅氧化层生长前清洗工艺的刻蚀量= b

‑

最终ono膜厚目标值。

14.步骤五,栅氧化层生长。

15.步骤六,生长制作栅极的多晶硅层。

16.在本发明中,所述的顶层氧化层实际生长的厚度比设计厚度目标值增加的厚度d,d的取值范围为1~10

å

范围内的任意值,一般典型值为3

ꢀå

。

17.所述的顶层氧化层实际生长的厚度比设计厚度目标值增加的厚度d,d的取值范围为1~10

å

范围内的任意值。

18.本发明中,上述的顶层氧化层实际生长的厚度比设计厚度目标值增加的厚度d的典型值为3

å

。

19.进一步的改进是,所述的ono层为顶层氧化硅层

‑

中间氮化硅层

‑

底层氧化硅层;所述的顶层氧化硅层采用热氧化法形成,形成工艺为hto工艺。

20.进一步的改进是,所述的顶层氧化硅层的生长厚度控制误差在

±1å

。

21.进一步的改进是,所述的栅氧化层生长的清洗步骤会导致顶层氧化硅层有10%以内的厚度损耗。

22.本发明所述的ono工艺中的氧化层厚度补偿方法,针对ono层中最顶层的hto氧化层的工艺参数进行调整,在淀积形成ono层时使形成的最顶层的hto氧化层的实际厚度比设计目标厚度略高一些,根据经验数据,消除淀积厚度误差以及清洗、湿法刻蚀误差所累积带来的最终ono层总体厚度低于设计目标值的问题,保证了存储器单元vt窗口一致性的问题。

附图说明

23.图1 是现有的sonos存储器的剖面结构示意图。

24.图2 是ono层的剖面结构示意图。

25.图3 是vtp编程电压与ono层中hto氧化层厚度之间的关系曲线。

26.图4 是vte擦除电压与ono层中hto氧化层厚度之间的关系曲线。

27.图5 是本发明技术方案流程图。

具体实施方式

28.下面将结合附图,对本发明中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。应当理解,本发明能够以不同形式实施,而不应当解释为局限于这里提出的实施例。相反地,提供这些实施例将使公开彻底和完全,并且将本发明的范围完全地传递给本领域技术人员。

29.在此使用的术语的目的仅在于描述具体实施例并且不作为本发明的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

30.本发明所述的ono工艺中的hto氧化层工艺方法,在进行ono工艺时,顶层氧化层实际生长的厚度比设计厚度目标值增加厚度d,即顶层hto sio2层厚度 =原目标厚度值+ d;d的取值范围为1~10

å

范围内的任意值;即:步骤一,ono层生长,完成后整体的ono层厚度为原目标厚度值+ d;工艺误差

±1å

。

31.步骤二,湿法清洗步骤,目标刻蚀量为c ,误差

±

10%。

32.步骤三, 测量ono层的整体厚度,ono层厚度测量值为b。

33.步骤四,根据步骤三中计算出的刻蚀最终目标值选择相应的栅氧化层生长前的清洗工艺,栅氧化层生长前清洗工艺的刻蚀量= b

‑

最终ono膜厚目标值。

34.步骤五,栅氧化层生长。

35.步骤六,生长制作栅极的多晶硅层。

36.上述的工艺中,在ono层淀积完成之后形成栅氧化层之前会进行湿法的清洗工艺,而清洗工艺会对顶层膜层产生10%以内的厚度损耗。

37.以某一sonos存储器产品为例,按照现有工艺存在的最终产品上的的ono膜厚的误差计算举例如下:1.ono膜生长步骤:目标生长厚度150

å

,生长控制误差:

±1å

;所以厚度为150

±1å

。

38.2.后续湿法刻蚀步骤造成的ono膜中顶层氧化膜层hto厚度的刻蚀误差:目标刻蚀量c=15

å

,工艺误差

±

10%,因此厚度误差

±

1.5

å

。

39.所以总体的ono膜厚为:150

‑

15=135

å

;工艺误差

±

(1+1.5

å

) =

±

2.5

å

。3.这个ono膜厚的误差无法由栅氧生长前的清洗步骤(pre goxclean)来消除,这

是因为: pre gox clean目标值很少,仅为1

å

的顶层氧化膜层hto的刻蚀量,没有减小余地,无法进行相应的加减调整。所以最终ono膜厚目标值t及误差值为:135

‑

1=134

å

(目标值)

±

2.5

å

(工艺误差)。

40.这个误差相当于造成在产品上的闪存擦写开启电压vt(檫除后的开启电压vte,写入后的开启电压vtp)窗口损失(vt

‑

vte)为:

±

150mv。

41.采用本发明工艺后,其ono层顶层hto氧化层的厚度目标值为150

å

,那么在实际生长时,将顶层的hto氧化层的实际生长厚度增加3

å

,那么栅氧化层淀积的清洗步骤前的hto氧化层刻蚀就要比原定的刻蚀量目标值多3

å

,则现在的工艺误差计算如下:1.ono膜生长步骤,顶层氧化膜层比原定目标值多生长3

å

,即d=3

å

:150+3=153

å

,工艺误差:

±1å

。

42.2.后续湿法刻蚀步骤造成的ono膜中顶层氧化膜层的刻蚀量15

å

,工艺误差为

±

10% ,即

±

1.5

å

,这与传统工艺相同。

43.3.栅氧生长前的清洗步骤(pre gox clean)顶层氧化膜层的刻蚀量比原先多刻蚀3

å

:1+3=4

å

。在此基础上,根据栅氧生长前的清洗步骤pre gox clean 之前的膜厚测量步骤测量的得到的ono膜厚值与ono膜厚目标值进行对比,进行pre gox clean刻蚀量的调整,从而保证最终ono膜厚不变。

44.例如:若此时测得的ono膜厚值为138

å

;最终ono膜厚目标值t=134

ꢀå

(不变): 那么pre gox clean的刻蚀量为 138

‑

134=4

å

。

45.若此时测得的ono膜厚值为136

åꢀ

;最终ono膜厚目标值t=134

ꢀå

(不变): 那么pre gox clean的刻蚀量为 136

‑

134=2

å

。

46.若此时测得的ono膜厚值为140

åꢀ

;最终ono膜厚目标值t=134

ꢀå

(不变): 那么pre gox clean的刻蚀量为 140

‑

134=6

å

。

47.所以最终产品上ono膜厚始终为:134

å

(目标值)。

48.考虑到刻蚀量调整的局限,如果当前膜厚每相差1

å

,进行刻蚀量的调整,那么相应的误差可以轻易的控制在

±‑

1/2=0.5

å

之内。这个误差相当于造成在产品上的闪存擦写开启电压vt(檫除后的开启电压vte, 写入后的开启电压vtp)窗口损失(vt

‑

vte)为:

±

30mv。

49.由背景技术部分的记载可知,

±

0.5

å

的hto波动造成的存储单元vt窗口变化只有

±

30mv,这比传统工艺方法减少了

±

120mv的vt窗口变化,对于sonos器件来说,这是非常显著的改善。

50.以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1