一种阵列基板、制备方法以及显示装置与流程

1.本发明涉及显示技术领域。更具体地,涉及一种阵列基板、制备方法以及显示装置。

背景技术:

2.随着显示技术的进步,越来越多的有源矩阵有机发光二极管(active matrix organic light emitting diode,简称:amoled)显示装置进入市场,相对于传统的薄膜晶体管液晶显示装置(thin film transistor liquid crystal display,简称:tft

‑

lcd),amoled显示装置具有更快的反应速度、更高的对比度以及更广大的视角,因此amoled显示装置受到越来越多的面板厂商的重视。

3.然而,现有技术中应用于amoled的包括像素驱动电路的阵列基板,通常采用高电压、高剂量的离子注入工艺形成薄膜晶体管的掺杂区以及其他区域,从而导致产生巨大的面电阻,使得薄膜晶体管之间的电流电阻增大,影响薄膜晶体管之间的电流移动,进而影响amoled显示装置的显示质量,降低amoled显示装置的竞争力。

技术实现要素:

4.本发明的目的在于提供一种阵列基板、制备方法以及显示装置,以解决现有技术存在的问题中的至少一个。

5.为达到上述目的,本发明采用下述技术方案:

6.本发明第一方面提供一种阵列基板的制备方法,所述阵列基板包括多个薄膜晶体管,包括:

7.在衬底上形成图案化的有源材料层,所述图案化的有源材料层包括待形成的薄膜晶体管的沟道区以及对应所述薄膜晶体管的源漏电极的非沟道区;

8.在衬底上形成金属层,所述金属层使得所述多个薄膜晶体管的非沟道区电连接;

9.在所述金属层和所述图案化的有源材料层上形成栅极绝缘层、栅极以及与所述非沟道区电连接的源漏电极,以形成所述多个薄膜晶体管。

10.本发明第一方面所提供的阵列基板的制备方法,通过形成将多个薄膜晶体管的非沟道区电连接的金属层,而且金属层的面电阻较小,从而降低制备得到的阵列基板的薄膜晶体管之间的电流电阻,可有效改善薄膜晶体管之间的电流移动,即,能提高薄膜晶体管之间的电流流动速度,同时获得稳定的驱动能力的薄膜晶体管,进而提高装载有该阵列基板的显示装置的显示质量,提高该显示装置的市场竞争力;再者,金属层与非沟道区位于同一层中且与非沟道区电连接,从而简化金属排线区的排线复杂度和排线量,简化阵列基板的制备工艺,同时,金属层的形成工艺简单,与现有的阵列基板的形成工艺匹配良好。

11.可选地,所述有源材料层的材料为多晶硅。

12.可选地,所述金属层的材料为具有与si类似的电子亲和性的金属。

13.该可选的实施方式通过采用具有与si类似的电子亲和性的金属作为金属层的材

料,从而使得金属层与非沟道区更好适配,更有助于改善薄膜晶体管之间电流移动的散射。

14.可选地,所述金属层的材料为ti或al。

15.可选地,所述在衬底上形成图案化的有源材料层进一步包括:

16.在衬底上形成非晶硅层;

17.通过激光晶化方法使得所述非晶硅层晶体化,从而形成多晶硅层;

18.对所述多晶硅层图案化,形成图案化的多晶硅层。

19.该可选的实施方式中通过激光晶化的方法形成多晶硅层,从而使得激光脉冲的瞬间能量被非晶硅层表面吸收并转化为相变能,避免过多的热能传导至衬底上,从而对衬底起到保护的作用。

20.可选地,所述金属层的厚度小于晶体化的多晶硅层最薄处的厚度。

21.该可选的实施方式中金属层的厚度小于多晶硅层最薄处的厚度,从而可有效避免多晶硅层之间的金属排线区出现较大的断差而导致断线的情况。

22.可选地,所述金属层的厚度小于40nm。

23.可选地,所述在所述金属层和所述图案化的有源材料层上形成栅极绝缘层、栅极以及与所述非沟道区电连接的源漏电极,以形成所述多个薄膜晶体管,包括:

24.形成栅极绝缘层,以覆盖所述金属层和所述图案化的有源材料层;

25.在所述栅极绝缘层上形成栅极,所述栅极与所述沟道区在所述衬底的正投影位置相对应;

26.形成层间介电层,以覆盖所述栅极和露出的栅极绝缘层;

27.对所述层间介电层进行开孔,以露出所述非沟道区;

28.对所述非沟道区进行离子注入,形成掺杂区;

29.形成源漏电极,所述源漏电极通过所述开孔与所述掺杂区电连接。

30.可选地,所述方法还包括:

31.在所述栅极绝缘层上形成栅极的同时,在所述栅极绝缘层上形成第一电容金属层;

32.在所述层间介电层上形成第二电容金属层,其中所述第二电容金属层在所述衬底上的正投影与所述第一电容金属层在所述衬底上的正投影对齐,所述第一电容金属层和第二电容金属层构成所述薄膜晶体管的存储电容。

33.本发明第二方面提供一种阵列基板,包括多个薄膜晶体管,包括:

34.衬底;

35.在衬底上形成的图案化的有源材料层,其中所述图案化的有源材料层包括薄膜晶体管的沟道区以及对应所述薄膜晶体管的源漏电极的非沟道区;

36.在衬底上形成的金属层,所述金属层使得所述多个薄膜晶体管的非沟道区电连接;

37.在所述金属层和所述图案化的有源材料层上形成的栅极绝缘层、栅极以及与所述非沟道区电连接的源漏电极。

38.可选地,所述有源材料层的材料为多晶硅。

39.可选地,所述金属层的材料为具有与si类似的电子亲和性的金属。

40.可选地,所述金属层的材料为ti或al。

41.可选地,所述金属层的厚度小于所述多晶硅最薄处的厚度。

42.可选地,所述薄膜晶体管包括第一复位薄膜晶体管、补偿薄膜晶体管、驱动薄膜晶体管、开关薄膜晶体管、第一发光控制薄膜晶体管、第二发光控制薄膜晶体管、第二复位薄膜晶体管以及存储电容,以形成7t1c驱动电路。

43.本发明第三方面提供一种显示装置,包括本发明第二方面所提供的阵列基板。

44.本发明的有益效果如下:

45.针对现有技术存在的技术问题,本发明的实施例提供一种阵列基板、制备方法以及显示装置,通过形成将多个薄膜晶体管的非沟道区电连接的金属层,而且金属层的面电阻较小,从而降低制备得到的阵列基板的薄膜晶体管之间的电流电阻,可有效改善薄膜晶体管之间的电流移动,提高薄膜晶体管之间的电流流动速度,同时获得稳定的驱动能力的薄膜晶体管,进而提高装载有该阵列基板的显示装置的显示质量,提高该显示装置的市场竞争力;再者,金属层与非沟道区位于同一层中且与非沟道区电连接,从而简化阵列基板的金属排线区的排线复杂度和排线量,简化阵列基板的制备工艺,同时,金属层的形成工艺简单,与现有的阵列基板的形成工艺匹配良好。

附图说明

46.下面结合附图对本发明的具体实施方式作进一步详细的说明。

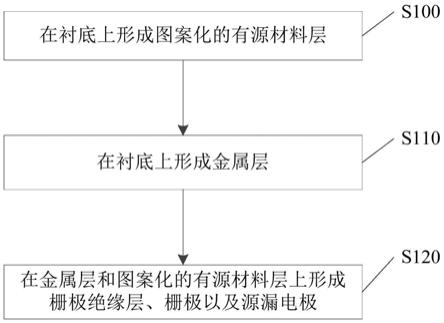

47.图1示出本发明的一个实施例中的阵列基板的制备方法流程图。

48.图2

‑

4示出本发明的一个实施例中的阵列基板的制备流程主要步骤对应的结构俯视图。

49.图5示出本发明的一个实施例中的阵列基板的结构截面图。

50.图6示出本发明的一个实施例中多晶硅层与金属层的结构截面图。

51.图7示出本发明的一个实施例中的7t1c像素电路的电路图。

具体实施方式

52.为了更清楚地说明本发明,下面结合实施例和附图对本发明做进一步的说明。附图中相似的部件以相同的附图标记进行表示。本领域技术人员应当理解,下面所具体描述的内容是说明性的而非限制性的,不应以此限制本发明的保护范围。

53.本发明中所述的“在

……

上”、“在

……

上形成”和“设置在

……

上”可以表示一层直接形成或设置在另一层上,也可以表示一层间接形成或设置在另一层上,即两层之间还存在其它的层。

54.需要说明的是,虽然术语“第一”、“第二”等可以在此用于描述各种部件、构件、元件、区域、层和/或部分,但是这些部件、构件、元件、区域、层和/或部分不应受到这些术语限制。而是,这些术语用于将一个部件、构件、元件、区域、层和/或部分与另一个相区分。因而,例如,下面讨论的第一部件、第一构件、第一元件、第一区域、第一层和/或第一部分可以被称为第二部件、第二构件、第二元件、第二区域、第二层和/或第二部分,而不背离本发明的教导。

55.在本发明中,除非另有说明,所采用的术语“同层设置”指的是两个层、部件、构件、元件或部分可以通过相同制备工艺(例如构图工艺等)形成,并且,这两个层、部件、构件、元

件或部分一般由相同的材料形成。例如两个或更多个功能层同层设置指的是这些同层设置的功能层可以采用相同的材料层并利用相同制备工艺形成,从而可以简化显示基板的制备工艺。

56.在本发明中,除非另有说明,表述“构图工艺”一般包括光刻胶的涂布、曝光、显影、刻蚀、光刻胶的剥离等步骤。表述“一次构图工艺”意指使用一块掩模板形成图案化的层、部件、构件等的工艺。

57.需要说明的是,现有技术中通常将栅极作为掩膜板使用,采用高电压、高剂量的离子注入工艺形成薄膜晶体管的掺杂区以及其他区域,以pmosfet(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,金属

‑

氧化物半导体场效应晶体管)为示例,通过将硼离子以35

‑

40kev的电压、约1e+15ions/cm2剂量注入,以形成薄膜晶体管的掺杂区,仍会产生大概3000

‑

5000ω/

□

的面电阻rs(rs=ρ/t,ρ为电阻率,t为厚度),不可避免地产生数千倍的走线电阻,从而影响薄膜晶体管之间的电流移动,导致显示装置的驱动电压升高,影响显示装置的显示质量。

58.为解决现有技术中存在的技术问题,本发明的一个实施例提供一种阵列基板100的制备方法,该阵列基板100包括多个薄膜晶体管。该阵列基板100可根据实际工况需要应用于包括不同发光器件的显示装置内。在一个具体示例中,该阵列基板100例如为应用于amoled显示装置的阵列基板。在另一些具体示例中,上述阵列基板例如还可为应用于oled(organic light

‑

emitting diode)显示装置的阵列基板,或者为应用于量子点发光二极管(quantum dot light emitting diodes,简称qled)显示装置的阵列基板,或者也可为微发光二极管(micro light emitting diodes,简称micro led)显示装置的阵列基板。

59.如图1所示,该阵列基板100的制备方法包括如下步骤:

60.s100、在衬底110上形成图案化的有源材料层120,图案化的有源材料层120包括待形成的薄膜晶体管的沟道区121以及对应薄膜晶体管的源漏电极130的非沟道区122,以形成如图2所示的结构。

61.在一个具体示例中,衬底110可以为聚酰亚胺(pi)、聚萘二甲酸乙二醇酯(pen)、热塑性聚酯(pet)等材料;在另一个具体示例中,衬底110可以为玻璃、石英等刚性材料。在另一个具体示例中,有源材料层120的材料为多晶硅。

62.在一个具体示例中,该薄膜晶体管例如可为pmosfet,也可以为nmosfet,ltps(low temperature poly

‑

silicon,低温多晶硅晶体管)、氧化物tft(thin film transistor)或tft等。本发明实施例对此不作进一步限定。

63.其中,对应于待形成的薄膜晶体管的源漏电极130的非沟道区122在后续工艺中可进行掺杂,以形成掺杂区122。在一个具体示例中,该掺杂区122可以为n型掺杂区,此时掺杂的例如可以为硼离子;在另一个具体示例中,该掺杂区122可以为p型掺杂区,此时掺杂的例如可以为磷离子,即掺杂杂质的类型对应于薄膜晶体管的类型。

64.另外,上述对非沟道区122进行的掺杂工艺例如可为离子注入工艺或者扩散工艺。在一个具体示例中,可对非沟道区122进行离子注入,以形成掺杂区。离子注入工艺具有在较低的温度下将各种杂质掺入到不同半导体中,能够精确控制掺入离子的浓度分布和注入深度,以及可实现大面积均匀掺杂等优点。

65.在一种可能的实现方式中,有源材料层120的材料为多晶硅,步骤s100在衬底110

上形成图案化的有源材料层120进一步包括:

66.s101、在衬底110上形成非晶硅层;

67.在一个具体示例中,可采用等离子增强化学气相沉积法(plasma enhanced chemical vapor deposition,pecvd)在衬底110上沉积一层非晶硅层(amorphous silicon,a

‑

si),并采用高温烤箱对非晶硅层进行脱氢工艺处理,以防止在晶化过程中出现氢爆现象以及降低晶化后内部的缺陷态密度作用。

68.s102、通过激光晶化方法使得非晶硅层晶体化,从而形成多晶硅层;

69.在一个具体示例中,可采用准分子激光退火(excimer laser annealing,ela)工艺使非晶硅层晶体化,以形成多晶硅层。准分子激光退火工艺是将高功率的激光束作用于待晶化的非晶硅层的表面,由于硅极强的紫外光吸收能力,在极短时间内(50ns

‑

150ns)可使得非晶硅层表面在瞬间达到1000摄氏度以上的高温而变成熔融状态,激光脉冲停止后,融化的非晶硅冷却结晶变为多晶硅。在一个具体示例中,为提高准分子激光退火工艺ela的效果,可在进行激光退火工艺之前对非晶硅层进行预处理,以使得非晶硅层表面生成一层氧化硅薄膜。

70.可理解的是,也可以采用金属诱导结晶工艺(mic)、固相结晶工艺(spc)等结晶化工艺对非晶硅层进行晶体化处理,以形成多晶硅层。

71.s103、对多晶硅层图案化,形成图案化的多晶硅层120。

72.具体地,如图2所示,采用光刻工艺对多晶硅层进行图案化,以使得图案化后的多晶硅层120包括待形成的薄膜晶体管的沟道区121以及与待形成的薄膜晶体管的源漏电极130所对应的非沟道区122,以便后续对非沟道区122进行掺杂。

73.该可能的实现方式通过激光晶化的方法形成图案化的多晶硅层120,从而使得激光脉冲的瞬间能量被非晶硅层表面吸收并转化为相变能,避免过多的热能传导至衬底110上,从而对衬底110起到保护的作用。

74.s110、在衬底110上形成金属层140,金属层140使得多个薄膜晶体管的非沟道区122电连接,以形成如图3所示的结构。

75.在一个具体示例中,步骤s110在衬底110上形成金属层140进一步包括:

76.s111、通过采用溅射工艺(sputtering)在衬底110上形成金属层140并通过曝光刻蚀金属层140,以使得金属层140与多个薄膜晶体管的非沟道区122电连接,如图3所示,金属层140形成在除包括待形成的薄膜晶体管的沟道区121以及对应薄膜晶体管的源漏电极130的非沟道区122的有源材料层120以外的区域,从而金属层140起到走线的作用,可实现不同的薄膜晶体管的源极或漏极130之间相互联接。

77.s120、在金属层140和图案化的有源材料层120上形成栅极绝缘层150、栅极160以及与非沟道区122电连接的源漏电极130,以形成多个薄膜晶体管。

78.在一种可能的实现方式中,步骤s120在金属层140和图案化的有源材料层120上形成栅极绝缘层150、栅极160以及与非沟道区122电连接的源漏电极130,以形成多个薄膜晶体管,进一步包括:

79.s121、形成栅极绝缘层150,以覆盖金属层140和图案化的有源材料层120;

80.在一个具体示例中,栅极绝缘层150例如可为氧化硅、氮化硅或者氮氧化硅等无机绝缘材料。

81.s122、在栅极绝缘层150上形成栅极160,栅极160与沟道区121在衬底110的正投影位置相对应;

82.在一个具体示例中,栅极160的材料例如可为铝、钛、钴等金属或者合金材料。在制备栅极160时,首先采用溅射或者蒸镀等方式在栅极绝缘层150上形成一层栅极材料层,随后对栅极材料层进行构图工艺,以使得形成的栅极160在衬底110上的正投影与有源材料层120中的沟道区121在衬底110上的正投影相对应。

83.s123、形成层间介电层170,以覆盖栅极160和露出的栅极绝缘层150;

84.在一个具体示例中,层间介电层170的材料例如可为氧化硅、氮化硅或者氮氧化硅等无机绝缘材料。

85.s124、对层间介电层170进行开孔,以露出非沟道区122,以形成如图4所示的结构,该开孔180用于连接非沟道区122和源漏电极130,其中,图4中的t1

‑

t7为多个薄膜晶体管。

86.s125、对非沟道区122进行离子注入,形成掺杂区;

87.在一个具体示例中,例如可通过将杂质离子以35

‑

40kev的电压、约1e+15ions/cm2剂量注入有源材料层120的非沟道区122中,以形成掺杂区,从而降低配线电阻。

88.s126、形成源漏电极130,源漏电极130通过形成在层间介电层170和栅极绝缘层150上的开孔180与掺杂区122电连接,最终形成如图5所示的结构。

89.在一个具体示例中,通过在层间介电层170上形成源漏金属层,源漏金属层覆盖形成在层间介电层170和栅极绝缘层150上的开孔180,随后通过对源漏金属层进行图案化工艺,形成源漏电极130,源漏电极130的材料包括但不限于mo,或mo/al/mo等。

90.需要说明的是,本技术的实施例对各功能层的材料不做限定,各功能层的材料并不局限于上述示例。

91.在一个具体示例中,在形成多个薄膜晶体管后,还可在层间介电层170和源漏电极130上依次形成平坦化层、阳极层、发光材料层、阴极层以及封装层(图中未显示),其中,源电极或漏电极通过形成在平坦化层上的开孔与阳极连接。

92.在一个具体示例中,平坦化层的材料例如可为有机材料,可通过气相热沉积的方式形成平坦化层;在另一个具体示例中,阳极层的材料为全反射的金属材质,例如ito、izo等金属氧化物或者ag、al、mo等金属或其合金。在又一个具体示例中,阴极为半反射材料,可包括mg、ca、li或al等金属或其合金,或者izo、zto等金属氧化物,又或者pedot/pss(聚3,4

‑

乙烯二氧噻吩/聚苯乙烯磺酸盐)等具有导电性能有机材料。

93.该实施例所提供的阵列基板100的制备方法通过在形成有源材料层120之后,在形成栅极绝缘层150之前在衬底110上形成与多个薄膜晶体管的非沟道区122电连接的金属层140,金属层140起到走线的作用,实现不同的薄膜晶体管的源极或漏极130之间相互联接,而且金属层140的面电阻较小,从而降低制备得到的阵列基板100的薄膜晶体管之间的电流电阻,可有效改善薄膜晶体管之间的电流移动,即,能提高薄膜晶体管之间的电流流动速度,同时获得稳定的驱动能力的薄膜晶体管,进而提高装载有该阵列基板100的显示装置的显示质量,提高该显示装置的市场竞争力;再者,金属层140与非沟道区122位于同一层中且与非沟道区122电连接,无需在源漏电极上额外形成连接线以连接不同的薄膜晶体管,从而简化阵列基板100的金属排线区的排线复杂度和排线量,简化阵列基板100的制备工艺,同时,金属层140的形成工艺简单,采用现有技术中常用的工艺即可实现,与现有的阵列基板

的形成工艺匹配良好。

94.在一种可能的实现方式中,有源材料层120的材料为多晶硅,金属层140的材料为具有与si类似的电子亲和性的金属,即该金属的电子亲和性与si的电子亲和性接近,该金属具有与si的电子亲和性相似范围的电子亲和性,例如,金属层140的材料的电子亲和性功函数(work function)约为4.1ev,与si的电子亲和性功函数类似。在一个具体示例中,金属层140的材料为ti或al。通过采用具有与si类似的电子亲和性的金属作为金属层140的材料,使得与si具有相似的电子亲和性的金属材料所构成的金属层140与有源材料层120中除沟道区121外的非沟道区122连接,非沟道区122与金属层140的金属导体电离更近,金属层140与多晶硅材料的非沟道区122更好适配,更有助于改善像素内薄膜晶体管之间电流移动的散射。

95.如图6所示,通过准分子激光退火工艺结晶化形成后的多晶硅层(即有源材料层120)的表面会形成若干个突起或凹陷。在如图6所示的示例中,其中,厚度最低的多晶硅层120的厚度约为40nm,而厚度最高的多晶硅层120的厚度约为100nm。在一种可能的实现方式中,金属层140的厚度小于晶体化的多晶硅层120最薄处的厚度,从而可有效避免多晶硅层120之间所形成的金属排线区出现较大的断差,容易导致金属排线断线,影响显示装置的显示质量的情况。在一个具体示例中,金属层140的厚度小于40nm,即金属层140的厚度小于如图6所示的示例中的多晶硅层120的厚度最低处的厚度。

96.在一种可能的实现方式中,该阵列基板100的制备方法还包括:

97.在栅极绝缘层150上形成栅极160的同时,在栅极绝缘层150上形成第一电容金属层190;

98.在层间介电层170上形成第二电容金属层1100,其中第二电容金属层1100在衬底110上的正投影与第一电容金属层190在衬底110上的正投影对齐,第一电容金属层190和第二电容金属层1100构成薄膜晶体管的存储电容。

99.在一个具体示例中,薄膜晶体管的存储电容包括位于栅极绝缘层150上的第一电容金属层190以及位于层间介电层170上的第二电容金属层1100,层间介电层170位于第一电容金属层190和第二电容金属层1100之间。存储电容由第一电容金属层190和第二电容金属层1100之间的电压确定。该实现方式通过形成存储电容从而使得即便在高分辨率下也能保证充分的存储电容。

100.在又一个具体示例中,第一电容金属层190和栅极160呈同层设置,即第一电容金属层190的材料与栅极160相同,均可为铝、钛、钴等金属或者合金材料,另外,第一电容金属层190和栅极160可通过同样的工艺形成,而且,第一电容金属层190和栅极160位于同一层上。

101.在另一个具体示例中,第二电容金属层1100与源漏电极130的材料相同且第二电容金属层1100与源漏电极130的形成工艺相同,而且,第二电容金属层1100与源漏电极130位于同一层。

102.本发明的另一个实施例提供一种如图5所示的阵列基板100,该阵列基板100包括多个薄膜晶体管,包括衬底110;在衬底110上形成的图案化的有源材料层120,其中图案化的有源材料层120包括薄膜晶体管的沟道区121以及对应薄膜晶体管的源漏电极130的非沟道区122;在衬底110上形成的金属层140,金属层140使得多个薄膜晶体管的非沟道区122电

连接;在金属层140和图案化的有源材料层120上形成的栅极绝缘层150、栅极160以及与非沟道区122电连接的源漏电极130。

103.该实施例的阵列基板100可有效降低薄膜晶体管之间的电流电阻,改善薄膜晶体管之间的电流移动,同时提高薄膜晶体管之间的电流流动速度,同时获得稳定的驱动能力的薄膜晶体管,进而提高装载有该阵列基板100的显示装置的显示质量,提高该显示装置的市场竞争力。

104.在一个具体示例中,该薄膜晶体管例如可为pmosfet,也可以为nmosfet,ltps(low temperature poly

‑

silicon,低温多晶硅晶体管)、氧化物tft(thin film transistor)或tft等。在又一个具体示例中,该阵列基板100例如为应用于amoled显示装置的阵列基板。在另一些具体示例中,上述阵列基板例如还可为应用于oled(organic light

‑

emitting diode)显示装置的阵列基板,或者为应用于量子点发光二极管(quantum dot light emitting diodes,简称qled)显示装置的阵列基板,或者也可为微发光二极管(micro light emitting diodes,简称micro led)显示装置的阵列基板,也就是说,该阵列基板100可根据实际工况需要应用于包括不同发光器件的显示装置内。

105.在一个可能的实现方式中,有源材料层120的材料为多晶硅。在一个具体示例中,可通过上述的激光退火工艺使非晶硅层晶体化,从而形成多晶硅层,再通过曝光刻蚀工艺对多晶硅层进行图案化,从而形成有源材料层120(即图案化的多晶硅层)。

106.在一个可能的实现方式中,金属层140的材料为具有与si类似的电子亲和性的金属。例如,金属层140的材料的电子亲和性功函数约为4.1ev。在另一个可能的实现方式中,金属层140的材料为ti或al。

107.在一个可能的实现方式中,金属层140的厚度小于多晶硅最薄处的厚度,即金属层140的厚度小于如图6所示的示例中的多晶硅层120的厚度最低处的厚度。从而可有效避免多晶硅层之间所形成的金属排线区出现较大的断差,容易导致金属排线断线,影响显示装置的显示质量的情况。

108.在一种可能的实现方式中,该阵列基板100还包括位于衬底110与有源材料层120之间的缓冲层1110,在有源材料层120的制作过程中需要经过高温退火处理,缓冲层1110位于衬底110上,可有效避免在高温退火处理时对衬底110产生影响。

109.在一个可能的实现方式中,薄膜晶体管包括第一复位薄膜晶体管、补偿薄膜晶体管、驱动薄膜晶体管、开关薄膜晶体管、第一发光控制薄膜晶体管、第二发光控制薄膜晶体管、第二复位薄膜晶体管以及存储电容,以形成7t1c驱动电路,如图7所示。

110.参见图7,reset为复位信号端,em为发光控制信号端,vinit为初始化电压端,vss为第二电压信号端,且第一电压信号端vdd用于提供第一电压信号,第二电压信号端vss用于提供第二电压信号,第一电压信号相对于第二电压信号为高电平信号,t1为第一复位薄膜晶体管,t2为补偿薄膜晶体管、t3为驱动薄膜晶体管、t4为开关薄膜晶体管、t5为第一发光控制薄膜晶体管、t6为第二发光控制薄膜晶体管、t7为第二复位薄膜晶体管。第一复位晶体管t1的控制极与复位信号端reset电连接,第一复位薄膜晶体管t1的第一极与初始化电压端vinit电连接,第一复位薄膜晶体管t1的第二极通过第三节点n3与补偿薄膜晶体管t2的第二极电连接,第一复位薄膜晶体管t1的第二极通过第四节点n4与驱动薄膜晶体管t3的控制极电连接,并同时与存储电容的一块极板电连接,补偿薄膜晶体管t2的第一极通过第

五节点与驱动薄膜晶体管t3的第二极与第二发光控制薄膜晶体管t6的第一极电连接。开关薄膜晶体管t4的第二极通过第六节点与驱动薄膜晶体管t3的第一极和第一发光控制晶体管t5的第二极电连接,开关薄膜晶体管t4的第一极与数据输入端电连接,开关薄膜晶体管t4的控制极与扫描信号端电连接。第一发光控制薄膜晶体管t5的第一极通过第七节点n7与存储电容的另一块极板电连接,同时第一发光控制薄膜晶体管t5的第一极与第一电压信号端电连接,第一发光控制薄膜晶体管t5的控制极与发光控制信号端电连接。第二发光控制薄膜晶体管t6的控制极与发光控制信号端电连接,第二发光控制薄膜晶体管t6的第二极通过第八节点n8与第二复位薄膜晶体管t7的第二极电连接,同时,第二复位薄膜晶体管t7的第一极与另一初始化电压端电连接,第二复位薄膜晶体管t7的控制极与另一个复位信号端电连接。

111.其中,上述控制极为薄膜晶体管的栅极,第一极为薄膜晶体管的源极和漏极中一个,第二极为薄膜晶体管的源极和漏极中另一个。

112.在一个具体示例中,在如图3所示的7t1c的像素电路中,驱动薄膜晶体管t3例如可为低温多晶硅薄膜晶体管,与驱动晶体管电连接t3的第一复位薄膜晶体管t1和补偿薄膜晶体管t2例如可为氧化物薄膜晶体管,除了第一复位薄膜晶体管t1、补偿薄膜晶体管t2和驱动薄膜晶体管t3,图7中的其他薄膜晶体管可以但不限于ltps晶体管。

113.需要说明的是,在本发明的实施例中,上述实施例中的7t1c像素电路的连接方式仅为示例,该实施例的阵列基板也可包括2t1c、6t1c像素电路,本发明的实施例对此不做进一步限定。

114.本发明的再一个实施例中提供一种显示装置,包括如上述实施例中所提供的阵列基板100。其中,显示装置可以为电子纸、手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件,本实施例对此不做限定。

115.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于本领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围之列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1