半导体结构及其形成方法与流程

1.本发明涉及半导体技术领域,更具体地,涉及一种半导体结构及其形成方法。

背景技术:

2.针对扇出基板(fosub)结构,大尺寸(例如,110mmx110mm)的基板具有低周期时间及低成本方面的优势。但是,针对现行的大尺寸构建(built up)基板却存在成品率低的潜在问题。目前针对大尺寸的基板,因为缺陷比率(defect ratio)是固定的,所以当尺寸越大时,则其基板制程良率越低,导致整体生产成本增加。

3.一种现行技术使用基板分离(substrate partition)的方式,将原始大尺寸的基板(例如,110mmx110mm)拆解成多个小尺寸的基板,这样基板的良率会随着尺寸缩小而提高。然而现行的基板分离的方式必须再进一步藉由形成rdl(重布线层)以互连多个小尺寸基板之间的通信,这会导致通信距离较长且rdl成本较高的问题。

技术实现要素:

4.针对相关技术中的上述问题,本发明提出一种半导体结构及其形成方法,能够避免上述通信距离较长且rdl成本较高的问题。

5.本发明的实施例的一个方面,提供了一种半导体结构,包括:

6.第一基板,

7.第二基板,与第一基板间隔设置并且通过第一线路与第一基板电连接;

8.线路层,位于第一基板和第二基板上方,并且第一基板还通过线路层与第二基板电连接,其中,第一线路的导电路径小于第一基板通过线路层电连接到第二基板的导电路径。

9.在一些实施例中,第一线路不包括晶种层。

10.在一些实施例中,第一线路为接合引线结构。

11.在一些实施例中,半导体结构还包括绝缘层,绝缘层位于线路层与第一基板和第二基板之间,并且绝缘层包覆第一线路。

12.在一些实施例中,半导体结构还包括贯通孔,贯通孔穿过绝缘层和线路层,其中,第一基板通过贯通孔和线路层与第二基板电连接。

13.在一些实施例中,在从线路层朝向第一基板和第二基板的方向上,贯通孔具有逐渐缩小的宽度。

14.在一些实施例中,线路层具有内部通孔,其中,在从线路层朝向第一基板和第二基板的方向上,内部通孔具有逐渐增加的宽度。

15.在一些实施例中,半导体结构还包括黏着层,黏着层位于线路层的朝向第一基板和第二基板的表面处,其中,贯通孔穿过黏着层。

16.在一些实施例中,第一基板和第二基板之间具有间隔,间隔由绝缘材料填充。

17.在一些实施例中,间隔的宽度在25微米至500微米的范围内。

18.在一些实施例中,第一基板和第二基板之间具有间隔,第一基板和第二基板的表面上分别具有邻近间隔设置的第一焊盘和第二焊盘,第一线路跨过间隔上方分别连接第一焊盘和第二焊盘。

19.在一些实施例中,线路层是扇出线路层。

20.在一些实施例中,线路层覆盖在第一基板和第二基板的全部表面上方。

21.本发明的实施例的另一个方面,还提供了一种形成半导体结构的方法,包括:在载体上提供间隔设置的第一基板和第二基板;利用非黄光制程将第一基板与第二基板电连接;将线路层接合在第一基板和第二基板上方。

22.在一些实施例中,利用非黄光制程将第一基板与第二基板电连接,包括:利用引线接合制程将第一基板与第二基板电连接。

23.在一些实施例中,利用非黄光制程将第一基板与第二基板电连接,还包括:通过模制物包封引线接合制程形成的接合引线结构。

24.在一些实施例中,还将模制物填充在第一基板和第二基板之间的间隔内。

25.在一些实施例中,将线路层接合在第一基板和第二基板上方包括:形成穿过线路层的第一贯通孔和第二贯通孔,第一贯通孔电连接线路层与第一基板,第二贯通孔电连接线路层与第二基板。

26.在一些实施例中,线路层是扇出线路层。

附图说明

27.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应当注意,根据工业中的标准实践,各个部件并非按比例绘制。事实上,为了清楚讨论,各个部件的尺寸可以任意增大或减小。

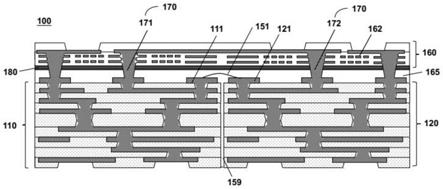

28.图1是根据本发明实施例的半导体结构的侧视示意图。

29.图2是根据本发明实施例的半导体结构的立体图。

30.图3是图1中的半导体结构的局部放大的示意图。

31.图4a至图4e是根据本发明实施例的形成半导体结构的方法的各个阶段的示意图。

具体实施例

32.下列公开提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面将描述元件和布置的特定实例以简化本发明。当然这些仅仅是实例并不旨在限定本发明。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件直接接触的实施例,也可以包括在第一部件和第二部件之间形成额外的部件使得第一部件和第二部件可以不直接接触的实施例。而且,本发明在各个实例中可重复参考数字和/或字母。这种重复仅是为了简明和清楚,其自身并不表示所论述的各个实施例和/或配置之间的关系。

33.图1是根据本发明实施例的半导体结构的侧视示意图。图2是根据本发明实施例的半导体结构的立体图。结合图1和图2所示,半导体结构100包括第一基板110和第二基板120,第二基板120与第一基板110间隔设置。第一线路151连接在第一基板110与第二基板120之间,第一线路151形成在第一基板110和第二基板120之间的导电路径,第二基板120通

过第一线路151与第一基板110电连接。此外,第一基板110和第二基板120上方设置有线路层160。线路层160中的部分线路在第一基板110和第二基板120上方也形成在第一基板110和第二基板120之间的导电路径,第一基板110还通过线路层160与第二基板120电连接。第一线路151的导电路径小于第一基板110通过线路层160电连接到第二基板120的导电路径。在一些实施例中,线路层160是扇出(fanout)线路层。

34.本发明的上述技术方案提供的半导体结构100,通过将半导体基板分割为小尺寸的第一基板110和第二基板120,并且进一步通过非线路层中的线路(例如非rdl线路)的第一线路151互连第一基板110和第二基板120,因此与现行的以rdl(重布线层)互连多个小尺寸基板之间的通信的基板分离方式相比,可避免通信距离较长且rdl成本较高的问题。

35.在一些实施例中,第一线路151可以是不包括晶种层的线路结构。在示出的实施例中,第一线路151为接合引线结构。第一基板110和第二基板120之间具有间隔159。在一些实施例中,间隔159的宽度在25微米至500微米的范围内。在一些实施例中,间隔159的宽度在25微米至75微米的范围内。在其他实施例中,间隔159也可以具有其他尺寸配置。第一基板110和第二基板120的表面上分别具有邻近间隔159设置的第一焊盘111和第二焊盘121,第一线路151跨过间隔159上方分别连接第一焊盘111和第二焊盘121以电连接第一基板110和第二基板120。

36.如图2所示,第一线路151的数量可以是连接在第一基板110和第二基板120之间的多个线路,例如为多个接合引线。此外,在图2的实施例中,将线路层160下方的基板分割为四个小尺寸基板,包括第一基板110、第二基板120、第三基板130和第四基板140。第一基板110、第二基板120、第三基板130和第四基板140中的任意相邻两个基板之间都具有间隔(例如第一基板110和第二基板120之间的间隔159)。在这样的实施例中,第一基板110与第三基板130之间通过跨越第一基板110与第三基板130之间的间隔159的第二线路152进行连接。第二线路152的数量可以是多个。第二基板120与第四基板140之间通过跨越第二基板120与第四基板140之间的间隔159的第三线路153进行连接。第三线路153的数量可以是多个。第三基板130与第四基板140之间通过跨越第三基板130与第四基板140之间的间隔159的第四线路154进行连接。第四线路154的数量可以是多个。应理解,图2所示的基板数量仅是示例,在其他实施例中基板的数量也可以是任意的其他数量,并且任意相邻基板之间可以以类似于第一线路151、第二线路152、第三线路153和第四线路154的线路进行连接。

37.第一基板110和第二基板120之间的间隔159可以由绝缘材料165(也可以称为绝缘层)填充。在一些实施例中,绝缘材料165可以是树脂材料或模制物。绝缘材料165还位于线路层160与第一基板110和第二基板120之间,并且绝缘材料165包覆第一线路151。线路层160可以覆盖在第一基板110和第二基板120的全部表面上方。

38.图3是图1中的半导体结构的局部放大的示意图。结合图1和图3所示,半导体结构100还包括穿过绝缘层和线路层160的贯通孔170。第一基板110是通过贯通孔170和线路层160与第二基板120电连接。贯通孔170可以包括第一贯通孔171和第二贯通孔172,第一贯通孔171电连接线路层160与第一基板110,第二贯通孔172电连接线路层160与第二基板120。第一贯通孔171和第二贯通孔172可以再也线路层160中的线路连接,而使得第一基板110可以通过第一贯通孔171、第二贯通孔172和线路层160中的线路(例如图1中连接在第一贯通孔171和第二贯通孔172之间的线路层160中的线路)与第二基板120电连接。

39.贯通孔170可以具有锥形侧壁。在从线路层160朝向第一基板110和第二基板120的方向上,贯通孔170具有逐渐缩小的宽度。在一些实施例中,贯通孔170的宽度可以在10微米至100微米的范围内。在一些实施例中,贯通孔170的深度可以在25微米至100微米的范围内。在其他实施例中,贯通孔170也可以具有其他的尺寸配置。另外,在线路层160的朝向第一基板110和第二基板120的表面处设置有黏着层180。更具体的,黏着层180设置在线路层160和绝缘材料165之间。贯通孔170也穿过黏着层180。在一些实施例中,黏着层180可以用作管芯附接膜。

40.线路层160内具有内部通孔162。内部通孔162也具有锥形侧壁,与贯通孔170不同的,在从线路层160朝向第一基板110和第二基板120的方向上,内部通孔162具有逐渐增加的宽度。

41.图4a至图4e是根据本发明实施例的形成半导体结构的方法的各个阶段的示意图。首先参考图4a所示,在载板105上形成包括第一基板110和第二基板120的多个基板。在图1所示的实施例中,多个基板还包括第三基板130和第四基板140。第一基板110、第二基板120、第三基板130和第四基板140彼此间隔设置。应理解,在其他实施例中,多个基板的数量也可以是其他任意数量。

42.如图4b所示,可以利用非黄光制程将第一基板110、第二基板120、第三基板130和第四基板140电连接。在一些实施例中,可以利用引线接合制程形成多个接合引线来将第一基板110、第二基板120、第三基板130和第四基板140电连接。具体的,第一基板110与第二基板120之间通过第一线路151进行连接。第一基板110与第三基板130之间通过第二线路152进行连接。第二基板120与第四基板140之间通过第三线路153进行连接。第三基板130与第四基板140之间通过第四线路154进行连接。然后,可以去除载板105。

43.如图4c所示,通过绝缘材料165包封引线接合制程形成的接合引线结构。在此步骤中,还将绝缘材料165填充在第一基板110、第二基板120、第三基板130和第四基板140之间的间隔159内。绝缘材料165可以是树脂材料或模制物。

44.然后如图4d所示,在第一基板110、第二基板120、第三基板130和第四基板140上方覆盖黏着层180,黏着层180可以例如是管芯附接膜。在图4e中,利用黏着层180将管芯195附接至第一基板110、第二基板120、第三基板130和第四基板140。

45.将线路层160接合在第一基板110、第二基板120、第三基板130和第四基板140上方。在一些实施例中,线路层160是扇出线路层。具体的,通过黏着层180将线路层160接合至第一基板110、第二基板120、第三基板130和第四基板140,以形成图1所示的半导体结构100。因此返回参考图1,在附接线路层160之后,还可以形成穿过线路层160、管芯附接膜和绝缘材料165并连接至第一基板110、第二基板120、第三基板130和第四基板140的贯通孔170。以使得第一基板110、第二基板120、第三基板130和第四基板140之间除了通过第一线路151、第二线路152、第三线路153和第四线路154进行连接之外,也可以通过线路层160中的线路和贯通孔170进行连接。

46.本发明的形成半导体结构的方法,通过使用接合引线的方式将多个基板连接,再进行线路层附接制程,最后再开设贯通孔以电连接多个基板和线路层。因此与现行的以rdl互连多个小尺寸基板之间的通信的基板分离方式相比,可避免通信距离较长且rdl成本较高的问题。

47.上述内容概括了几个实施例的特征使得本领域技术人员可更好地理解本公开的各个方面。本领域技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他的处理和结构以用于达到与本发明所介绍实施例相同的目的和/或实现相同优点。本领域技术人员也应该意识到,这些等效结构并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1