电感器器件和堆叠式电源拓扑的制作方法

1.本公开的各实施例总体上涉及电感器器件和堆叠式电源拓扑。

背景技术:

2.常规的开关电源电路有时包括诸如电感器的能量存储部件来产 生为负载供电的输出电压。例如,为了将输出电压的幅度保持在期望 范围内,控制器控制流过一个或多个电感器来产生为负载供电的输出 电压的电流的切换。

3.通常,常规电感器是包括导线或其他导电材料的部件,导线或其 他导电材料被成形为线圈或螺旋线来增加通过相应电路路径的磁通 量。将导线缠绕为多匝线圈是有用的,因为它增加了相应电感器部件 中相应磁通线的数量,从而增大了磁场并且因此增大了相应电感器部 件的总电感。

技术实现要素:

4.本公开包括观察到常规电感器部件适用于平面电路应用,在平面 电路应用中,电源电路板的相应平面表面被填充有多个不同部件,多 个不同部件进而经由平面表面上设置的电路迹线而彼此耦合。这样的 拓扑(在电源电路板中提供水平功率流)不可避免地导致难以创建紧 凑、高效和大电流输出的电源电路。因此,经由绕组实现一个或多个 电感器的常规电源电路有时是不合需要的。

5.与常规技术相比,本文的实施例提供了新颖并且改进的电感器部 件、电感器组装件、电源、堆叠式电路拓扑等。

6.更具体地,本文的一个实施例包括制造n相电感器器件(组装 件),其中电感器器件包括任意数量的n(n=1、2、3、4、5、6、7、

…

) 个电感器相。制造者接收可导磁的芯材料。制造者将至少第一导电路 径设置为从电感器器件的近端穿过芯材料,到达电感器器件的远端。 可导磁芯材料可操作为限制由流过第一导电路径的电流生成的第一 磁通量。制造者还将芯材料制造为包括间隙,间隙具有与芯材料不同 的磁导率。间隙用于在电流流过第一导电路径的情况下控制芯材料中 的通量幅度。

7.请注意,芯材料可以由任何合适的材料制成。在一个实施例中, 芯材料由铁氧体材料薄片制成,一个或多个导电路径借助铁氧体材料 薄片制成。

8.芯材料中的间隙(部分)可以被制造为可导磁材料的空隙(例如, 气隙、真空等)。备选地,芯材料是第一可导磁材料,并且间隙是第 二可导磁材料。

9.本文的又一实施例包括将电感器器件制造为在芯材料中包括至 少第二导电路径。类似于第一导电路径,第二导电路径从电感器器件 的近端延伸穿过芯材料,到达电感器器件的远端。芯材料可操作为限 制由流过第二导电路径的第二电流生成的第二磁通量。

10.在又一示例实施例中,第一导电路径是n相直接耦合电感器器件 的第一电感器相;第二导电路径是n相直接耦合电感器器件的第二电 感器相。

11.在更又一示例实施例中,芯材料具有大于80的相对磁导率。但 是其可以根据实施

例而变化。

12.在又一示例实施例中,经由在芯材料中放置间隙,第一导电路径 与第二导电路径之间的磁耦合因子小于10%。

13.根据又一示例实施例,其中间隙对第二导电路径和第一导电路径 之间的磁耦合因子进行控制。

14.根据更又一实施例,制造者制造穿过芯材料的一对导电路径。例 如,制造者将电感器器件生产为还包括第二导电路径,第二导电路径 从电感器器件的近端延伸穿过芯材料,到达电感器器件的远端;第二 导电路径与第一导电路径相邻(诸如平行)。制造者将电感器器件生 产为在电感器器件中包括一个或多个间隙(诸如,第一间隙和第二间 隙),用于控制与导电路径(电感路径)相关联的相应参数(诸如, 电感、饱和阈值等)。

15.在一个实施例中,制造者将第一间隙生产为在第一方向上,从第 一导电路径径向向外延伸;制造者将第二间隙生产为在与第一方向相 对的第二方向上,从第二导电路径径向向外延伸。间隙(磁导率与芯 材料不同的芯材料的一个或多个区域或体积)的存在控制了电感路径 (第一导电路径和第二导电路径)的参数,诸如每个电感路径的电感、 与每个电感路径相关联的饱和阈值、第一电感路径和第二电感路径之 间的磁耦合等。

16.在又一示例实施例中,制造者将间隙生产为横穿芯材料中围绕第 一导电路径的同心路径。根据右手定则,同心路径传送由通过第一导 电路径的电流生成的磁通量。制造者控制与间隙相关联的尺寸(诸如, 厚度、体积、放置等)的制造,以调整与相应电感路径(即,导电路 径)相关联的参数,诸如电感、磁饱和阈值、磁耦合等。

17.如前所述,本文的实施例包括将电感器器件制造为包括从电感器 器件的近端延伸到远端的第二导电路径。在一个实施例中,第二导电 路径是返回路径,返回路径可操作为传送借助第一导电路径传送的第 一电流或第一电流的小于全部的部分。

18.本文的另外的实施例包括在芯材料中制造一对导电路径,该对包 括第一导电路径和至少第二导电路径。制造者围绕一对导电路径的周 边设置一个或多个导电路径的集合。类似于第一导电路径和第二导电 路径,一个或多个导电路径的集合也从电感器器件的近端延伸到远 端。

19.根据需要,如本文所述,如本文所述的电感器器件可以包括奇数 数量的导电路径(电感路径)。

20.本文中更另外的实施例包括将电感器器件(也被称为电感器组装 件)制造为包括导电路径(电感路径)对。例如,在一个实施例中, 制造者在芯材料中制造第一对导电路径(诸如,第一导电路径和第二 导电路径)。第二导电路径与第一导电路径间隔开。第一对中的导电 路径中的每个导电路径从电感器器件的近端延伸到远端。制造者在芯 材料中制造第二对导电路径。第二对中的导电路径中的每个导电路径 从近端延伸到远端。第四导电路径与第三导电路径间隔开。第二对导 电路径包括第三导电路径和第四导电路径。制造者将电感器器件制造 为包括在第二导电路径与第三导电路径之间至少部分地延伸的间隙。

21.在又一些实施例中,电感器器件是为相应负载供电的功率转换器 的一部分。在一个实施例中,电路制造者接收衬底(诸如电路板)。 如前所述,电路制造者接收电感器器件(第一电路部件)。电路制造 者将第一电路部件附贴到衬底。电路板制造者接收第二电路部件(诸 如负载)。电路板制造者将第二电路部件附贴到第一电路部件。在功 率转换器操作

期间,电路板上的电源控制器控制电流从一个或多个电 压源传送通过电感器器件(经由导电路径形成的一个或多个电感路 径),以产生为第二电路部件(负载)供电的输出电压。

22.以下更详细地公开了这些和其他更具体的实施例。

23.注意,如本文所讨论的在系统中实现的任何资源(诸如制造者) 可以包括用于执行和/或支持本文中所公开的方法操作中的任一个或 全部的一个或多个计算机化设备、控制器、移动通信设备、手持式或 膝上型计算机等。换言之,一个或多个计算机化设备或处理器可以被 编程和/或被配置为如本文所解释的进行操作来执行如本文所描述的 不同实施例。

24.本文中的其他实施例包括用于执行以上概括并在以下详细公开 的步骤和操作的软件程序。一个这样的实施例包括计算机程序产品, 计算机程序产品包括非暂态计算机可读存储介质(即,任何计算机可 读硬件存储介质),软件指令可以在非暂态计算机可读存储介质上被 编码来供后续执行。指令在具有处理器的计算机化设备(硬件)中执 行时,将处理器(硬件)编程为和/或使得处理器(硬件)执行本文所 公开的操作。这样的布置通常被提供为在非暂态计算机可读存储介质 (诸如,光学介质(例如,cd-rom)、软盘、硬盘、记忆棒、存储 器设备等)或者其他介质(诸如,一个或多个rom、ram、prom 等中的固件)上布置或编码的软件、代码、指令和/或其他数据(例如, 数据结构)或者被提供为专用集成电路(asic)等。软件或固件或者 其他这样的配置可以被安装到计算机化设备上,以使得计算机化设备 执行本文中解释的技术。

25.因此,本文的实施例针对支持如本文所讨论的操作的方法、系统、 计算机程序产品等。

26.一个实施例包括制造者(诸如包括其上存储有指令的计算机可读 存储介质和/或系统)制造电感器器件。指令在由计算机处理器硬件执 行时,使得计算机处理器硬件(诸如一个或多个共同定位或不同定位 的处理器设备或硬件):接收芯材料,芯材料是可导磁材料;设置第 一导电路径,该第一导电路径从电感器器件的近端穿过芯材料、到达 电感器器件的远端,芯材料可操作为限制由流过第一导电路径的电流 生成的第一磁通量;以及将芯材料制造为包括间隙,间隙具有与芯材 料不同的磁导率。

27.为清楚起见,添加了上述步骤的顺序。注意,本文中讨论的任何 处理步骤可以以任何合适的顺序来执行。

28.本公开的其他实施例包括软件程序和/或相应的硬件来执行以上 概述和以下详细公开的方法实施例步骤和操作中的任一个。

29.应当理解,如本文所讨论的系统、方法、装置、计算机可读存储 介质上的指令等也可以诸如在处理器(硬件或软件)内或在操作系统 内或在软件应用程序内被严格地体现为软件程序、固件、软件、硬件 和/或固件的混合体或者单独作为硬件。

30.另外注意,虽然本文中讨论的实施例适用于开关电源,但是本文 中所公开的概念可以有利地应用于任何其他合适的拓扑。

31.另外,请注意,尽管本文中的每个不同特征、技术、配置等可以 在本公开的不同地方讨论,但意图是在合适的情况下,每个概念可以 可选地彼此独立地或者彼此组合来执行。因此,如本文所述的一个或 多个本发明可以以许多不同的方式来体现和观察。

32.此外,请注意,本文中对实施例的初步讨论(发明内容部分)并 未特意指定本公开

或所要求保护的(多个)发明的每个实施例和/或增 加的新颖方面。相反,该简要描述仅呈现整体实施例和相对于常规技 术的对应新颖点。对于(多个)发明的附加细节和/或可能的观点(排 列),读者可以参考如下文进一步讨论的本公开的具体实施方式(其 是实施例的概述)和对应附图。

附图说明

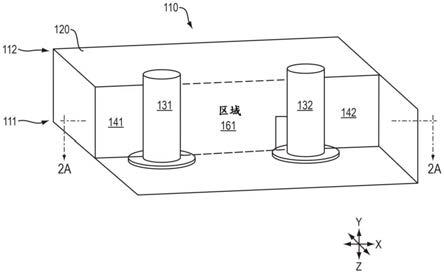

33.图1是图示了根据本文实施例的包括多个电感路径的电感器器件 的三维(透视)视图的示例图。

34.图2a是图示了根据本文实施例的电感器器件的顶部视图的示例 图。

35.图2b是根据本文实施例的电感器器件的示例截面侧视图。

36.图2c是根据本文实施例的电感器器件的示例侧视图。

37.图3是图示了根据本文实施例的电感器器件的属性的示例图。

38.图4是图示了根据本文实施例的电感器器件的焊盘的顶部视图的 示例图。

39.图5是图示了根据本文实施例的电感器器件的焊盘的顶部视图的 示例图。

40.图6是图示了根据本文实施例的电源中的电路部件的连接的示例 图。

41.图7是图示了根据本文实施例的图6中的电源的示例侧视图,图 6中的电源支持竖直功率流。

42.图8是图示了根据本文实施例的电感器器件的截面图的示例图。

43.图9是图示了根据本文实施例的电感器器件的焊盘的视图的示例 图。

44.图10是图示了根据本文实施例的电感器器件的磁耦合属性的示 例图。

45.图11a是图示了根据本文实施例的电感器器件的截面图的示例 图。

46.图11b是图示了根据本文实施例的电感器器件的焊盘的视图的 示例图。

47.图12a是图示了根据本文实施例的电感器器件的截面图的示例 图。

48.图12b是图示了根据本文实施例的电感器器件的焊盘的视图的 示例图。

49.图13是图示了根据本文实施例的电感器器件的磁耦合属性的示 例图。

50.图14a是图示了根据本文实施例的电感器器件的截面图的示例 图。

51.图14b是图示了根据本文实施例的电感器器件的焊盘的视图的 示例图。

52.图15是图示了根据本文实施例的电感器器件(在图14a和14b 中)的磁耦合属性的示例图。

53.图16是图示了可操作为执行根据本文实施例的一个或多个方法 的示例计算架构(制造者系统、硬件等)的示例图。

54.图17是图示了根据本文实施例的制造电感器器件的方法的示例 图。

55.本文实施例的前述和其他目的、特征和优点将从本文中如附图中 所示的以下更具体的描述中变得明显,在附图中,相同的附图标记在 不同的视图中指代相同的部分。附图不一定按比例绘制,而是重点放 在图示实施例、原理、概念等上。

具体实施方式

56.本文中的某些实施例涉及从dc输入电压为计算处理器供电的功 率转换级。由于高功率需求、非常高的动态负载变化、所产生的输出 电压的窄容差,功率级需要被放置在

与负载的最小物理距离处。本文 中的实施例包括在有源衬底或备选地中介层或备选地pcb板内的处 理器下方堆叠功率级和磁性元件的竖直功率流。

57.在最先进的技术中,电压调节器模块(vrm)被横向布置到负载, 其中功率级和磁性元件作为表面贴装器件(smd)而被放置在主板上。

58.如本文所述的所提议的磁性器件(电感器器件)使得能够:

[0059]-接近数字负载的高功率密度-》减少pdn(供电网络)中的损耗;

[0060]-改进瞬态性能;

[0061]-减少磁性器件中的铜损耗。

[0062]

通过在电感器器件的芯材料中使用高磁导率材料(即,相对磁导 率,μ_r》80),可以将通量成形,从而以有利的方式设计磁性器件。 如本文所述的通量抵消导致芯损耗减少或者磁性材料体积减少(即, 因为可以收缩芯的某些部分)。在一个实施例中,如本文所述的间隙 的存在降低了芯材料中的有效磁导率并且修改了电感器器件的电感。

[0063]

另外,某些应用可以受益于内置在同一芯中的电感之间的低耦 合。在芯材料中放置一个或多个(空气)间隙降低了相之间的耦合因 子,从而降低了系统损耗。直接耦合可以被用于改进瞬态。没有到增 加的铜损耗的直接联系,这简化了减少系统损耗的陈述。

[0064]

现在,参考附图,图1是图示了根据本文实施例的电感器器件的 三维(透视)视图的示例图。

[0065]

如图所示,图1中的电感器器件110包括:芯材料120和导电路 径131和132。如本文进一步讨论的,芯材料120可以包括至少从近 端111延伸到远端112的任何数量的导电路径。

[0066]

在一个实施例中,导电路径131和132中的每个导电路径轴向延 伸(诸如沿着y轴或直线、非缠绕的等)穿过芯材料120。如本文进 一步讨论的,与常规绕组相反,每个导电路径131、132等的电感由 围绕芯材料120(可导磁材料)的存在而产生。

[0067]

通常,除了与导电路径131相关联的间隙141(诸如,相ph1) 以及与导电路径132相关联的间隙142(诸如,相ph2)之外,芯材 料120包封(包围)导电路径131和132中的每个导电路径。在导电 路径与对应的芯材料120之间可以存在小间隙。

[0068]

注意,芯材料120可以由任何合适的材料制成。在一个实施例中, 芯材料120是由铁氧体材料薄片制成的固体材料块,一个或多个导电 路径借助铁氧体材料薄片来制造。

[0069]

芯材料120可以具有任何合适的磁导率。在一个实施例中,作为 非限制性示例实施例,芯材料120具有25-350亨利/米之间的磁通导 率。在一个实施例中,如先前所讨论的,具有高于80的相对磁导率μ_r 的任何材料可以被用于制造电感器器件110。

[0070]

在另外的示例实施例中,每个导电路径(131、132等)的电感由 对应的气隙(141、142等)长度和面积以及芯材料120的磁导率来限 定。

[0071]

在另外的实施例中,芯材料120中的导电路径131、132等中的 每个导电路径由任何合适的导电材料(诸如,金属、金属合金等)制 成。

[0072]

如图所示,在芯材料120中存在导电路径131和132,将导电路 径131变换为第一电感路径并且将导电路径132变换为第二电感路 径。因此,电感器器件110包括多个电感器。在一个实施例中,很少 需要或不需要耦合。

[0073]

根据需要,导电路径131和132中的每个导电路径的外表面被绝 缘材料层或气隙

(诸如非导电材料,不与芯材料120接触)围绕。备 选地,导电路径中的每个导电路径与芯材料120接触。在以下附图中 示出了电感器器件110的附加细节。

[0074]

图2a是图示了根据本文实施例的电感器器件的顶部视图的示例 图。

[0075]

在该示例实施例中,制造者140将电感器器件110生产为包括如 先前所讨论的导电路径131和132以及对应的间隙141和142。

[0076]

如进一步所示,制造者140将电感器器件110生产为包括一个或 多个附加导电路径151、152、153和154的集合,该集合用作电流返 回路径、电压感测路径等(也被称为由金属制成的导电返回路径)。 在一个实施例中,导电路径151、152、153和154关于围绕导电路径131和132组合的周边或关于导电路径131和132的组合而设置。

[0077]

在一个实施例中,返回路径151、152、153和154可操作为传送 借助第一导电路径131传送的第一电流的全部或少于全部的部分,以 及借助第二导电路径132传送的第二电流的全部或一部分。

[0078]

在该示例实施例中,制造者140接收可导磁的芯材料120。制造 者将至少第一导电路径131设置为从电感器器件110的近端111穿过 芯材料120,到达电感器器件110的远端。

[0079]

导电路径131和132中的每个导电路径可以以任何合适的方式来 制造。在一个实施例中,经由制造者140的制造包括穿过芯材料120 钻出相应的孔,并且将相应的导电路径插入到电感器器件110中包括 的每个导电路径的对应空隙中。

[0080]

导电路径131和132可以被制造为任何合适的形状,诸如杆状、 圆柱状、柱状、曲线状、环形、裂环状等。

[0081]

在一个实施例中,导电路径中的每个导电路径是诸如轴向(诸如 沿着y轴)延伸穿过芯材料120的非绕组电路路径。

[0082]

相应间隙141和142中的每个间隙可以以任何合适的方式来制 造。在一个实施例中,制造包括去除(诸如,钻孔、蚀刻等)芯材料 120的一部分来产生相应的空隙。例如,芯材料120中的每个间隙(部 分、区域等)可以被制造为空隙(诸如填充有气体、液体、固体、真 空等的气隙)。备选地,芯材料120由第一可导磁材料制成,并且一 个或多个间隙中的每个间隙由第二可导磁材料制成。

[0083]

在一个实施例中,间隙141和142中的每个间隙的磁导率基本上 小于芯材料120的磁导率。

[0084]

注意,间隙的形状可以根据实施例而变化。芯材料120中的每个 间隙至少从近端111延伸到远端112并且可能更远。

[0085]

在一个实施例中,间隙141和142中的每个间隙表示芯材料120 的切片。间隙的厚度可以是固定值。附加地或备选地,每个间隙的厚 度可以根据与其所属的对应导电路径的距离而变化。

[0086]

在电流从近端111流经导电路径131到达远端112或者从远端112流经导电路径131到达近端111期间,可导磁的芯材料120限制 由流经相应导电路径131的电流生成的对应第一磁通量。

[0087]

在电流从近端111流经导电路径132到达远端112或者从远端 112流经导电路径131到达近端111期间,可导磁的芯材料120限制 由流经相应导电路径132的电流生成的对应第一磁通量。

[0088]

如前所述,制造者140可以被配置为将每个间隙制造为具有与芯 材料120的磁导率不同的磁导率。

[0089]

在一个实施例中,制造者140将第一间隙141生产为在第一方向 (诸如向左)上,从第一导电路径131径向向外延伸;制造者140将 第二间隙142生产为在与第一方向相对的第二方向(诸如向右)上, 从第二导电路径132径向向外延伸。

[0090]

间隙(磁导率与芯材料120不同的芯材料120的一个或多个区域 或体积)的存在控制了相应电感路径(第一导电路径和第二导电路径) 的参数,诸如每个电感路径的电感、与每个电感路径相关联的饱和阈 值、第一电感路径与第二电感路径之间的磁耦合等。

[0091]

在导电路径131与导电路径132之间的区域161中(诸如p2和 p6之间的任何位置),发生通量抵消,从而可以减小电感器路径(也 被称为导电路径)的尺寸。由于经由芯材料120中存在间隙而实现的 芯材料120的相应角部处的低通量密度,可以保持器件的相同面积并 且引入负载电流的再调整路径。

[0092]

如本文所述,在电流流过相应导电路径的情况下,每个间隙用于 控制芯材料120中的磁通量。在一个实施例中,间隙141和142的存 在阻碍磁通量流过芯材料120。间隙的存在和如本文所述的正确放置 致使:i)减小与相应导电路径相关联的电感,ii)增加与相应导电路 径相关联的磁通量饱和水平,以及iii)减少第一导电路径131与第二 导电路径132之间的磁耦合。

[0093]

因此,如本文所述的制造者140将电感器器件110生产为包括一 个或多个间隙(诸如第一间隙和第二间隙)来控制与导电路径(又被 称为电感路径)相关联的相应参数(诸如,电感、饱和阈值、磁耦合 等)。

[0094]

图2b是根据本文实施例的电感器器件的示例截面侧视图。

[0095]

如该示例侧视实施例所示,在x轴的p4与p5之间,导电路径131 与导电路径132之间的区域161不存在间隙。间隙141相对于x轴存 在于p1与p3之间。p6与p8之间存在间隙142。导电路径131存在 于p3与p4之间。导电路径132存在于p5与p6之间。

[0096]

图2c是根据本文实施例的电感器器件的示例侧视图。

[0097]

如该示例侧视实施例中所示,导电路径152的侧视图存在于p1 与p2之间;导电路径153的侧视图存在于p7与p8之间。芯材料120 存在于p2与p7之间的侧视区域261中。

[0098]

如本文进一步讨论的,电感器器件110(诸如导电路径和芯材料 120中的对应间隙)可以被复制并设置在包括多个导电路径对的封装 件中。

[0099]

例如,由于与电感器器件110相关联的简单磁结构(同一芯上的 相之间的耦合因子非常低),电感器器件110的多相实现方式可以利 用单个基元(电感器器件110中的导电路径对131和132)的简单阵 列布置来实现。

[0100]

多相由数量为n_ph=2*(n_x)*〖(n〗_y)(其中n_x和n_y是≥1 的整数)的相组成。

[0101]

如果相应实现方式需要奇数个电感器,则可以在阵列结构中添加 单个电感器,然后:i)在该单个电感器中失去通量抵消优势,从而增 加了尺寸,以及ii)多相由数量为n_ph=2*(n_x)*〖(n〗_y)+1(其 中n_x和n_y是≥1的整数)的相组成。

[0102]

图3是图示了根据本文实施例的电感器器件的属性的示例图。

[0103]

在该示例实施例中,m(导电路径131与导电路径132之间的磁 耦合因子)大于0,从而导致相(导电路径131与导电路径132)之 间的一定量的直接耦合。

[0104]

在一个实施例中,期望m的值保持在阈值以下,因为m的高值 增加了相应电感器中的rms电流。耦合可以被用于增加瞬态响应。

[0105]

在耦合因子的低值(即,〖m_1,2/l〗_ph1或〖m_2,1/l〗_ph2)) 的情况下,电流形状以及因此的rms电流实际上由自电感l_ph1和 l_ph2来限定,其中l_ph1是导电路径131的电感并且l_ph2是导电 路径132的电感。

[0106]

l_ph1和l_ph2的幅度由相应的外支腿间隙141和142的属性(诸 如间隙的面积、体积、长度等)来限定。

[0107]

间隙141和142被设置在导电路径131与导电路径132之间的区 域161之外,以实现图3所示的等效电路。

[0108]

图4是图示了根据本文实施例的电感器器件的焊盘的顶部视图的 示例图。

[0109]

如该示例实施例中所示,制造者140将电感器器件110生产为在 远端112处包括多个导电焊盘(由金属、金属合金等制造),以促进 电感器器件110与相应电路的连接。

[0110]

更具体地,在该示例实施例中,制造者140将导电焊盘410-1(诸 如接地焊盘)耦合/连接到导电路径154的远端112。制造者140将导 电焊盘410-2(诸如接地焊盘)耦合/连接到导电路径152的远端112。 制造者140将导电焊盘420(诸如提供输出电压)耦合/连接到导电路 径131和导电路径132的远端112。

[0111]

图5是图示了根据本文实施例的电感器器件的焊盘的顶部视图的 示例图。

[0112]

为了降低输出电容上的等效esr并且降低输出上的电压纹波,返 回路径可以被实现为将输出电压vout传送回位于邻近的电容器,以 将到接地的ac电流返回路径最小化。

[0113]

如该示例实施例中所示,制造者140将电感器器件110生产为在 远端112处包括多个导电焊盘(由金属、金属合金等制造),以促进 电感器器件110与相应电路的连接。

[0114]

更具体地,在该示例实施例中,制造者140将导电焊盘410-1(诸 如接地焊盘)耦合/连接到导电路径154的远端112。制造者140将导 电焊盘410-2(诸如接地焊盘)耦合/连接到导电路径152的远端112。

[0115]

制造者140将导电焊盘520(诸如提供输出电压)耦合/连接到导 电路径131和导电路径132的远端112。另外,制造者140将导电焊 盘520(诸如借助导电路径131和132而提供输出电压)耦合/连接到 导电路径151和导电路径154的远端112。在一个实施例中,导电路 径151和154然后将输出电压vout从远端112传送到电感器器件110 的近端111。

[0116]

图6是图示了根据本文实施例的电源中的电路部件的连接的示例 图。

[0117]

在该非限制性示例实施例中,电源1200包括控制器1240和多个 相221(ph1)和222(ph2),它们共同生成为负载(load)118供 电的相应的输出电压123(输出电流)。注意,负载118可以是可以 位于独立电路板上的任何合适的电路,诸如cpu(中央处理单元)、 gpu(图形处理单元)和asic(专用集成电路,诸如包括一个或多 个人工智能加速器的专用集成电路)等。

[0118]

另外注意,该示例实施例中的电源1200可以包括任意数量的相。 作为非限制性示例实施例,为了例示,电源1200包括为负载118供 电的两个相。根据需要,相可以被分离,使得为第一负载供电的第一 相221与为第二负载供电的第二相而独立。

[0119]

如操作相221和相222的组合来为相同负载118供电的示例实施 例中所示,相221包括开关qa1(第一高侧开关电路)、开关qb1 (第一低侧开关电路或控制开关电路)和电感

路径1231(诸如导电路 径131)。相222包括开关qa2(高侧开关电路)、开关qb2(低侧 开关电路)和电感路径1232(导电路径132)。

[0120]

此外,在该示例实施例中,电压源120-1向开关qa1(诸如,高 侧开关)和开关qb1(诸如,低侧开关)的串联组合提供电压v1(诸 如输入电压6vdc或任何合适的电压)。

[0121]

在一个实施例中,开关qa1和qb1以及电感路径1231(导电路 径131)的组合根据降压转换器拓扑(诸如每个相彼此异相)操作来 产生输出电压123(又被称为vout)。

[0122]

此外,在该示例实施例中,注意,开关qa1的漏极节点(d)被 连接来接收由电压源120-1提供的输入电压v1。开关qa1的源极节 点(s)被耦合到开关qb1的漏极节点(d)以及电感路径1231的输 入节点。开关qb1的源极节点被耦合到接地参考电压。电感路径1231 的输出节点被耦合到负载118。

[0123]

又另外在该示例实施例中,相222的开关qa2的漏极节点被连 接来接收由电压源120-1提供的输入电压v1。开关qa2的源极节点 (s)被耦合到开关qb2的漏极节点(d)以及电感路径1232的输入 节点。开关qb2的源极节点被耦合到接地。电感路径1232的输出节 点被耦合到负载118。

[0124]

如前所述,相221与222的组合产生为负载118供电的输出电压 123。即,电感路径1231(导电路径131)产生输出电压123;电感路 径1232(导电路径132)产生输出电压123。

[0125]

在操作期间,如图所示,控制器1240产生控制信号105(诸如控 制信号a1和控制信号b1)来控制相应开关qa1和qb1的状态。例 如,控制器1240所产生的控制信号a1驱动并控制开关qa1的栅极 节点;控制器1240所产生的控制信号b1驱动并控制开关qb1的栅 极节点。

[0126]

另外,控制器1240产生控制信号a2和b2来控制开关qa2和 qb2的状态。例如,控制器1240所产生的控制信号a2驱动并控制 开关qa2的栅极节点;控制器1240所产生的控制信号b2驱动并控 制开关qb2的栅极节点。

[0127]

在一个实施例中,控制器1240将相221和222控制为相对于彼 此异相180度。

[0128]

如对于降压转换器已知的,在相221中,在开关qb1被停用(off) 时,将高侧开关qa1激活到on状态将输入电压v1耦合到电感路径 1231的输入,从而导致由电感路径1231提供给负载118的电流量增 加。相反,在开关qa1被停用(off)时将低侧开关qb1激活到on 状态将接地参考电压耦合到电感路径1231的输入,从而导致由电感 路径1231提供给负载118的电流量减少。控制器1240监视输出电压 123的幅度并且将开关qa1和qb1控制为使得输出电压123保持在 期望的电压范围内。

[0129]

在相222中,以类似的方式,在开关qb2被停用(off)的同时 将高侧开关qa2激活到on状态将输入电压v1耦合到电感路径1232 的输入,从而导致由电感路径1232提供到负载118的电流量增加。 相反地,在开关qa2被停用(off)的同时将低侧开关qb2激活到 on状态将接地参考电压耦合到电感路径1232的输入,从而导致由电 感路径1232提供给负载118的电流量增大。如前所述,控制器1240 监视输出电压123的幅度并且将开关qa2和qb2控制为使得输出电 压123保持在期望的电压范围内。

[0130]

因此,根据一个实施例,电感器器件是为相应负载118供电的功 率转换器1200的一部分。

[0131]

图7是图示了根据本文实施例的以竖直电路堆叠被实例化的图6 的多相电源的示

例侧视图。

[0132]

如该示例实施例中所示,电源1200支持竖直功率流。

[0133]

例如,衬底1205和对应的一个或多个电源(诸如v1)向电源堆 叠组装件1300供电,电源堆叠组装件1300进而为动态负载118供电。 借助电源堆叠组装件1300传送的接地参考(gnd)提供了参考电压 和电流借助堆叠而被传送到负载118的返回路径。

[0134]

在一个实施例中,衬底1205是电路板(诸如独立板、母板、注 定要耦合到母板的独立板等)。包括一个或多个电感器器件的电源堆 叠组装件1300被耦合到衬底1205。如前所述,负载118可以是可以 位于独立电路板上的任何合适的电路,诸如cpu、gpu和asic(诸 如包括一个或多个人工智能加速器的asic)。在一个实施例中,堆 叠组装件1300作为模块被嵌入到衬底中。

[0135]

注意,电源堆叠组装件1300中的电感器器件110可以如本文所述以 任何合适的方式被实例化。在该非限制性示例实施例中,电源堆叠组装 件1300包括图1中的电感器器件110或者如本文所述的任何其他附图的 电感器器件。电源堆叠组装件1300可以被配置为包括如本文所述的电感 器器件110中的任何电感器器件。

[0136]

此外,在该示例实施例中,制造者140经由多个部件的堆叠来制 造电源堆叠组装件1300(诸如dc-dc功率转换器165),多个部件 包括第一功率接口1301、开关层1310中的一个或多个开关、连接层 1320、一个或多个电感器组装件(诸如包括电感器器件110)和第二 功率接口1302。

[0137]

制造者140还将第一功率接口1301设置在堆叠(部件的电源组 装件1300)的基部处。电源堆叠组装件1300的基部(诸如功率接口 1301)将电源堆叠组装件1300耦合到衬底1205。

[0138]

在一个实施例中,制造者140将电容器1221和1222设置在包括 功率接口1301的电源堆叠组装件1300的层中。

[0139]

更进一步地,当制造电源堆叠组装件1300时,制造者140将电 源堆叠组装件1300中的诸如开关qa1、qb1、qa2和qb2的多个开 关电耦合到第一功率接口1301。第一功率接口1301以及与衬底1205 的对应连接使得开关qa1、qb1、qa2和qb2能够从衬底1205接收 诸如功率输入的功率,功率输入为诸如输入电压v1和gnd参考电 压。衬底1205上的一个或多个迹线、功率层等将来自电压(或功率) 源的电压提供或传送到电源堆叠组装件1300的功率接口1301。

[0140]

如前所述,控制器1240生成控制信号105来控制电源堆叠组装 件1300中的相应开关qa1、qb1、qa2和qb2。制造者140以任何 合适的方式来提供控制器1240与开关qa1、qb1、qa2和qb2之间 的连接,以传送相应信号105。

[0141]

在开关层1310中的开关顶部处,制造者140还将电源堆叠组装 件1300制造为包括如本文所述的一个或多个电感器器件。另外,经 由连接层1320,制造者140将开关qa1、qb1、qa2和qb2进一步 连接到一个或多个电感器器件110。

[0142]

更具体地,在该示例实施例中,制造者140将开关qb1的源极节 点(s)连接到功率接口1301中的接地参考节点1210-1。注意,接地 参考节点1210-1经由l形接地节点1210-1(其被连接到接地电压参 考)而从衬底1205延伸到动态负载118。制造者140将开关qb1的 漏极节点(d)连接到节点1321(诸如由金属制成),节点1321被 电连接到电感路径1231的第

一端部141(诸如导电路径131的实例)。 因此,经由连接层1320,制造者将开关qb1的漏极节点连接到电感 器器件110的电感路径1231。

[0143]

制造者140将开关qa1的漏极节点(d)连接至第一功率接口 1301的电压源节点1220(其被电连接至输入电压v1)。制造者140 将开关qa1的源极节点(s)连接到节点1321,如前所述,节点1321 被电连接到电感路径1231的第一端部141(导电路径131的实例)。 因此,经由连接层1320和对应节点1321,开关qa1的源极节点被连 接到电感器器件110的电感路径1231。

[0144]

如进一步所示,制造者140将开关qb2的源极节点(s)连接到 功率接口1301中的接地参考节点1210-2。接地参考节点1210-2经由 l形接地参考节点1210-2(其被连接到接地电压参考)而从衬底1205 延伸到动态负载118。制造者140将开关qb2的漏极节点(d)连接 到节点1322(诸如由金属制成),节点1322被电连接到电感路径1232 的第一端部141(诸如导电路径132的实例)。因此,经由连接层1320, 开关qb2的漏极节点被连接到电感器器件110的电感路径1232。

[0145]

注意,虽然节点1210-1和1210-2中的每个节点从电源堆叠组装 件1300的侧视图看起来是l形,但是在一个实施例中,节点1210关 于电源堆叠组装件1300的外表面(以与先前讨论的导电路径133类 似的方式)周向延伸。

[0146]

如进一步所示,制造者140将开关qa2的漏极节点(d)连接到 功率接口1301中的电压源节点1220(其被连接到电压v1)。制造者 140将开关qa2的源极节点(s)连接到节点1322,节点1322被电 连接到电感路径1232的第一轴向端部141(导电路径132的实例)。 因此,经由连接层1320和对应节点1322,开关qa2的源极节点被连 接到电感器器件110的电感路径1232。

[0147]

因此,制造者140将一个或多个开关(诸如,qa1、qb1、qa2 和qb2)设置在电源堆叠组装件1300中的第一功率接口1301和电感 器器件110之间。

[0148]

在一个非限制性示例实施例中,电源堆叠组装件1300中的一个 或多个开关qa1、qb1、qa2和qb2中的每个开关是在第一功率接 口1301与电感器器件110之间设置的竖直场效应晶体管。附加地或 备选地,注意,开关qa1、qb1、qa2和qb2中的一个或多个可以 是任何合适类型的开关,诸如竖直或横向场效应晶体管、双极结型晶 体管等。横向fet也是可能的,但竖直fet是该概念的理想选择, 因为它们具有与顺序系统需求匹配的自然竖直电流性质。

[0149]

如前所述,制造者140将电源堆叠组装件1300制造为包括一个 或多个电感器器件110。在该示例实施例中,制造者将多个电感路径 1231设置在电源堆叠组装件1300中的多个开关qa1、qb1、qa2和 qb2与第二功率接口1302之间。

[0150]

根据进一步的实施例,注意,制造多个电感路径1231和1232包 括:将多个电感路径制造为包括第一电感路径1231和第二电感路径 1232,第一电感路径1231和第二电感路径1232在连接层1320和功 率接口1302之间延伸穿过电感器器件110的芯材料120。在一个实施 例中,制造者140将电感器器件110制造为包括:i)芯材料120,芯 材料是可导磁铁磁材料,ii)从电感器器件110的第一轴向端部141 延伸穿过芯材料120、到达电感器器件110的第二轴向端部142的第 一电感路径1231,iii)从电感器器件110的第一轴向端部141延伸穿 过芯材料120、到达电感器器件110的第二轴向端部142的第二电感 路径1232。

[0151]

更进一步在该示例实施例中,第一电感路径1231被设置在电源 堆叠组装件1300(功率转换器电路)的第一相221(图6)中;第二 电感路径1232被设置在电源堆叠组装件1300(功率转换器电路)的 第二相222(图6)中。在功率转换器(电源堆叠组装件1300)的操 作期间,并联设置的第一相221和第二相222的组合产生输出电压123。根据需要,控制器1240可以被制造到电源堆叠组装件中1300 中或者可以被集成到cpu、gpu或asic中。

[0152]

在一个实施例中,一个或多个电感路径1231和1232中的每个电 感路径是从堆叠中包括多个开关qa1、qb1、qa2和qb2的第一层 (诸如开关层1310)延伸到堆叠中包括第二功率接口1302的第二层 的相应非绕组路径。

[0153]

注意,本文中的进一步实施例包括将电感器器件110中的多个电 感路径并联连接来减小相应电压调节器的有效系统电感。如本文所 述,电感器器件110中的任何数量的电感路径可以被并联连接来提供 期望的整体系统电感。因此,除了控制诸如芯材料120的磁导率的参 数、电感器器件110中的每个非绕组导电路径(诸如直线或直接路径) 的相应长度(在第一端部141与第二端部142之间)之外,本文的实 施例还包括将多个电感路径并联连接来控制由相应电感器器件110提 供的电感幅度。另外注意,并联电感器可以不具有相同的有效电感, 并且可以被用于优化整个系统瞬态或效率性能。本文的实施例包括改 变单独相的电感值的灵活性,使得整体系统电感可以针对不同的输出 负载来优化。例如,高电感可以针对轻负载来实现,低电感针对重负 载和瞬态来实现。

[0154]

如进一步所示,制造者140将电感器器件110设置在电源堆叠组 装件1200中,位于开关层1310中的多个开关(qa1、qb1、qa2和 qb2)与第二功率接口1302之间。

[0155]

更具体地,制造者140将电源组装件1300生产为包括第二功率 接口1302。在一个实施例中,制造者140将电感器器件110的输出轴 向端部和对应的节点连接到第二功率接口1302。第二功率接口1302 可操作为接收由电感器器件110产生的输出电压123并且将其输出到 负载118。制造者140将电感路径1231和电感路径1232两者的输出 节点耦合到输出电压节点1331(诸如金属的材料层)。因此,输出电 压节点1331被电连接到相应电感路径1231和1232的输出。

[0156]

在一个实施例中,动态负载118的一个或多个节点或引脚、焊盘 等被耦合到输出电压节点1331。例如,电源堆叠组装件1200的输出 电压节点1331将电感路径1231和1232中的每个电感路径所产生的 输出电压123传送到负载118的一个或多个节点、引脚、焊盘等。

[0157]

因此,经由在接地电压与输入电压v1之间切换电感路径,电感 路径1231和1232的组合共同产生输出电压123来为负载118供电。

[0158]

如前所述,电源堆叠组装件1300还包括接地节点1210-1和1210-2 (诸如第三导电路径133的实例)。在一个实施例中,电感器器件110 的导电路径133(诸如接地节点1210-1、1210-2等)的实例相对于电 源堆叠组装件1300提供周边电磁屏蔽,从而防止或减少到周围环境 中的对应辐射发射。

[0159]

在又一些实施例中,制造者140将第一功率接口1301制造为包 括第一触点元件,该第一触点元件可操作为将电源堆叠组装件1300 的基部处的第一功率接口1301连接到主机衬底1205。制造者将第二 功率接口1302制造为包括第二触点元件,第二触点元件可操作为将 动态负载118固定到电源堆叠组装件1300。

[0160]

注意,电源堆叠组装件1200被制造为还包括第一电容器1221、 1222等,以在输入

电压节点1220(向电源堆叠组装件1300提供输入 电压v1的第一导电路径)和接地节点1210-1和1210-2(诸如,向电 源堆叠组装件1300提供接地参考电压的第二导电路径)之间提供连 接。

[0161]

制造者140还将输出电压节点1331(诸如另一导电路径)设置在 包括第二功率接口1302的电源堆叠组装件1302的层中。如前所述, 输出电压节点1331(诸如金属层)可操作为将输出电压123传送到动 态负载118。

[0162]

根据进一步的实施例,制造者140将电源堆叠组装件1300制造 为包括在输出电压节点1331与相应接地节点1210之间连接的第二电 容器(1391、1392等)。更具体地,电容器1391被耦合在输出电压 节点1331与接地节点1210-1之间;电容器1392被耦合在输出电压 节点1331与接地节点1210-2之间。

[0163]

如前所述,节点1210可以是围绕电感器器件110和/或电源堆叠 组装件1300的连续周边屏蔽件。

[0164]

本文中另外的实施例包括将动态负载118附贴到第二功率接口 1302。因此,动态负载118被附贴在电源堆叠组装件1300的顶部处。

[0165]

如本文所述的电源堆叠组装件1300(诸如竖直堆叠的部件的组装 件)提供优于常规功率转换器的优点。例如,本文所述的电源堆叠组 装件1300在组装件中提供了部件的新颖连接(诸如经由堆叠),从 而在将功率转换并传送到动态负载118时产生更短的电路路径和更低 的损耗。

[0166]

如先前关于图6所讨论的,在操作期间,电感器器件110和对应 的电感路径1231和1232可操作为基于所接收的功率(由输入电压 v1提供的电流)来产生输出电压123。换言之,电源堆叠组装件1300 以及对应制造的部件的堆叠(诸如第一功率接口1301、一个或多个开 关qa1、qb1、qa2和qb2、电感器器件110、第二功率接口1302) 是功率转换器,功率转换器可操作为将在第一功率接口1301处接收 的输入电压v1(诸如dc电压)转换为从第二功率接口1302输出到 动态负载118的输出电压123(诸如dc电压)。

[0167]

本文中另外的实施例包括系统的制造。例如,本文中的实施例包 括制造者140。制造者140接收衬底1205,诸如电路板;制造者140 将部件的堆叠(诸如电源堆叠组装件1300)的基部(诸如接口1301) 附贴到电路板。如前所述,部件的堆叠(电源堆叠组装件1300)可操 作为生成用于为负载118供电的输出电压123。负载118被附贴到电 路板或者负载118被附贴在电源堆叠组装件1300的顶部处。

[0168]

此外,如前所述,负载118可以是可以位于独立的电路板上的任 何合适的电路,诸如cpu、gpu和asic(诸如包括一个或多个人工 智能加速器的asic)。

[0169]

因此,在一个实施例中,(电路、系统等)制造者140接收衬底 1205(诸如电路板)。如前所述,电路制造者接收电感器器件110(第 一电路部件)。电路制造者将第一电路部件(电感器器件110或承载 电感器器件110的部件)附贴到衬底1205。电路板制造者接收第二电 路部件(诸如负载118)。电路板制造者将第二电路部件(负载118) 附贴到第一电路部件(电感器器件110)。在功率转换器操作期间, 电路板上设置的电源控制器1240控制电流从一个或多个电压源(诸 如提供输入电压v1)传送通过电感器器件110(诸如导电路径131 和132或者任何数量的导电路径),以产生为负载118(第二电路部 件)供电的输出电压123(vout)。

[0170]

注意,在一个实施例中,衬底1205包括可选的衬底部分1205-1 和1205-2,在该情况下,电源组装件1200被嵌入在衬底1205中。即 使被嵌入到由衬底1205、衬底部分1205-1和衬底部分1205-2形成的 腔中,电源组装件1200仍然被附贴到衬底1205。

[0171]

图8是图示了根据本文实施例的电感器器件的截面图(仰视)的 示例图。

[0172]

在该示例实施例中,制造者140(组装者)将电感器器件810(也 被称为电感器组装件)制造为包括导电路径(电感路径)对。

[0173]

例如,在一个实施例中,制造者140以如前所述的方式,在芯材 料120中制造第一对导电路径(诸如第一导电路径131和第二导电路 径132)。如图所示,第二导电路径132(电感器,或者所谓的相ph2) 与第一导电路径131(电感器,或者所谓的相ph1)间隔开。第一对 中的导电路径131和132中的每个导电路径从电感器器件810的近端 111延伸到远端112。

[0174]

间隙(gap)141提供与第一电感路径(导电路径131)相关联 的有益调整;间隙142提供与第二电感路径(导电路径132)相关联 的有益调整。

[0175]

另外,制造者在芯材料120中制造第二对导电路径(导电路径133 和导电路径134)。第二对中的导电路径133和134中的每个导电路 径(类似于先前针对导电路径131和132所讨论的)从近端111延伸 到远端112。第二对导电路径包括第三导电路径133(电感器,相ph3) 和第四导电路径134(电感器,相ph4)。第四导电路径134与第三 导电路径133被间隔开。

[0176]

如进一步所示,制造者将电感器器件810生产为包括针对每个导 电路径的间隙。例如,导电路径131包括间隙141;导电路径132包 括间隙142;导电路径133包括间隙143;导电路径134包括间隙144。

[0177]

电感器器件810在每个导电路径对的周边处还包括任意数量的导 电返回路径。例如,导电路径851、852、855和856关于第一对导电 路径131和132的周边来设置;导电路径852、853、854和855关于 第二对导电路径133和134的周边来设置。导电路径851、852、853、 854、855和856中的每个导电路径以与先前针对电感器器件110所讨 论的类似的方式从电感器器件810的近端111延伸到远端112。

[0178]

图9是图示了根据本文实施例的电感器器件的焊盘的透视图(诸 如俯视图)的示例图。

[0179]

如该示例实施例中所示,参考图8和图9,制造者140将电感器 器件810生产为在近端111处包括多个导电焊盘(由金属、金属合金 等制造),来促进电感器器件110与相应电路的连接。

[0180]

更具体地,在该示例实施例中,制造者140将导电焊盘951(诸 如vout焊盘)耦合/连接到导电路径851的近端111。制造者140将 导电焊盘952(诸如接地焊盘)耦合/连接到导电路径852的近端111。 制造者140将导电焊盘953(诸如vout焊盘)耦合/连接到导电路径 853的近端111。

[0181]

如进一步所示,制造者140将导电焊盘954(诸如接地焊盘)耦 合/连接到导电路径854的近端111。制造者140将导电焊盘955(诸 如vout焊盘)耦合/连接到导电路径855的近端111。制造者140将 导电焊盘956(诸如接地焊盘)耦合/连接到导电路径856的近端111。

[0182]

制造者140将导电路径856的远端112耦合到导电焊盘910-1(接 地);制造者140将导电路径852的远端112耦合到导电焊盘910-2 (接地);制造者140将导电路径854的远端

112耦合到导电焊盘910-3 (接地)。

[0183]

制造者140还将导电路径851的远端112耦合到导电焊盘920 (vout);制造者140将导电路径855的远端112耦合到导电焊盘920 (vout);制造者140将导电路径853的远端112耦合到导电焊盘920 (vout)。

[0184]

图10是图示了根据本文实施例的与电感器器件810中的对应导 电路径(电感器)相关联的属性(诸如与具有n_x=1和n_y=2电路的 单个基元阵列相关联的磁耦合度)的示例图。

[0185]

图11a是图示了根据本文实施例的电感器器件的截面图(仰视) 的示例图。

[0186]

在该示例实施例中,制造者140(组装者)将电感器器件1110(也 被称为电感器组装件)制造为包括导电路径(电感路径)对。

[0187]

例如,在一个实施例中,制造者140将电感器器件1110制造为 包括多对电感路径的序列。

[0188]

例如,制造者140以如前所述的方式在芯材料120中制造第一对 导电路径(诸如第一导电路径131和第二导电路径132)。如图所示, 第二导电路径132(电感器,相ph2)与第一导电路径131(电感器, 相ph1)间隔开。第一对中的导电路径131和132中的每个导电路径 从电感器器件1110的近端111延伸到远端112。间隙141提供与第一 电感路径(导电路径131)相关联的有益调整;间隙142提供与第二 电感路径(导电路径132)相关联的有益调整。

[0189]

另外,制造者在芯材料120中制造第二对导电路径(导电路径133 和导电路径134)。第二对中的导电路径133和134中的每个导电路 径(类似于先前针对导电路径131和132所讨论的)从近端111延伸 到远端112。第二对导电路径包括第三导电路径133(电感器,相ph3) 和第四导电路径134(电感器,相ph4)。第四导电路径134与第三 导电路径133间隔开。制造者将电感器器件1110生产为包括针对每 个导电路径的间隙。间隙143提供与电感路径(导电路径133)相关 联的有益调整;间隙144提供与电感路径(导电路径134)相关联的 有益调整。

[0190]

另外,制造者在芯材料120中制造第三对导电路径(导电路径135 和导电路径136)。第三对中的导电路径135和136中的每个导电路 径(类似于先前针对导电路径131和132所讨论的)至少从近端111 延伸到远端112。第三对导电路径包括导电路径135(电感器,相ph5) 和导电路径136(电感器,相ph6)。导电路径135以与先前讨论的 类似方式与导电路径136间隔开。制造者将电感器器件1110生产为 包括针对每个导电路径的间隙。间隙145提供与电感路径(导电路径 135)相关联的有益调整;间隙146提供与电感路径(导电路径136) 相关联的有益调整。

[0191]

另外,制造者在芯材料120中制造第四对导电路径(导电路径137 和导电路径138)。第三对中的导电路径137和138中的每个导电路 径(类似于先前针对导电路径131和132所讨论的)从近端111延伸 到远端112。第三对导电路径包括导电路径137(电感器,相ph7)和 导电路径138(电感器,相ph8)。导电路径137以与先前讨论的类 似的方式与导电路径138间隔开。制造者将电感器器件1110生产为 包括针对每个导电路径的间隙。间隙147提供与电感路径(导电路径 137)相关联的有益调整;间隙148提供与电感路径(导电路径138) 相关联的有益调整。

[0192]

如进一步所示,电感器器件1110在每对导电路径的周边处包括 任意数量的导电

返回路径。例如,导电路径851、852、855和856关 于第一对导电路径131和132来设置;导电路径852、853、854和855 关于第二对导电路径133和134来设置;导电路径853、857、859和 854关于第三对导电路径135和136来设置;导电路径857、858、860 和859关于第四对导电路径137和138来设置。

[0193]

导电路径851、852、853、854、855、856、857、858、859和860 中的每个导电路径以与先前针对电感器器件110讨论的类似方式从电 感器器件1110的近端111延伸到远端112。

[0194]

图11b是图示了根据本文实施例的电感器器件的焊盘的顶部视 图的示例图。

[0195]

如该示例实施例中所示,制造者140将电感器器件1110生产为 在近端111处包括多个导电焊盘(由金属、金属合金等制造)来促进 电感器器件110与相应电路的连接。

[0196]

更具体地,在该示例实施例中,制造者140将导电焊盘951(诸 如vout焊盘)耦合/连接到导电路径851的近端111。制造者140将 导电焊盘952(诸如接地焊盘)耦合/连接到导电路径852的近端111。 制造者140将导电焊盘953(诸如vout焊盘)耦合/连接到导电路径 853的近端111。

[0197]

如进一步所示,制造者140将导电焊盘954(诸如接地焊盘)耦 合/连接到导电路径854的近端111。制造者140将导电焊盘955(诸 如vout焊盘)耦合/连接到导电路径855的近端111。制造者140将 导电焊盘956(诸如接地焊盘)耦合/连接到导电路径856的近端111。

[0198]

制造者140将导电焊盘957(诸如接地焊盘)耦合/连接到导电路 径857的近端111。制造者140将导电焊盘958(诸如vout焊盘)耦 合/连接到导电路径858的近端111。制造者140将导电焊盘959耦合 /连接到导电路径859的近端111。制造者140将导电焊盘960耦合/ 连接到导电路径860的近端111。

[0199]

制造者140将导电路径856的远端112耦合到导电焊盘910-1(接 地);制造者140将导电路径852的远端112耦合到导电焊盘910-2 (接地);制造者140将导电路径854的远端112耦合到导电焊盘910-3 (接地);制造者140将导电路径857的远端112耦合到导电焊盘910-4 (接地);制造者140将导电路径860的远端112耦合到导电焊盘910-5 (接地)。

[0200]

制造者140还将导电路径851的远端112耦合到导电焊盘920 (vout);制造者140将导电路径855的远端112耦合到导电焊盘920 (vout);制造者140将导电路径853的远端112耦合到导电焊盘920 (vout);制造者140将导电路径859的远端112耦合到导电焊盘920 (vout);制造者140将导电路径858的远端112耦合到导电焊盘920 (vout)。

[0201]

图12a是图示了根据本文实施例的电感器器件的截面图的示例 图。

[0202]

在该示例实施例中,制造者将电感器器件1210制造为包括在芯 材料120中设置的电感器器件810-1和电感器器件810-2的组合。电 感器器件810-1表示图8中电感器器件810的第一实例。电感器器件 810-2表示图8中的电感器器件810的第二实例。

[0203]

再次参考图12a,电感器器件1210包括将与电感器器件1210相 关联的电感器器件810-1和电感器器件810-2分离的间隙1250。

[0204]

在该配置中,相之间的间隙1250(间隔、芯材料120中的空隙) 防止导电路径之间的耦合。在一个实施例中,间隙1250的厚度(诸 如,被填充有空气、气体、液体、具有与芯材料120不同的磁导率的 固体等)大于间隙141、142等的厚度的2倍。

[0205]

图12b是图示了根据本文实施例的电感器器件的焊盘的视图的 示例图。

[0206]

在该示例性实施例中,电感器器件1210包括导电焊盘并且以与 先前在图9中所示

和讨论的方式类似的方式被设置在近端111和远端 112处。

[0207]

图13是图示了根据本文实施例的包括任意数量的相的单个基元 的电感器器件阵列(具有n_x≥1和n_y≥1)的磁耦合属性的示例图。

[0208]

图14a是图示了根据本文实施例的电感器器件的截面图的示例 图。

[0209]

在该示例实施例中,制造者140(组装者)将电感器器件110-14 (又被称为电感器组装件,n_ph=2*(n_x)*〖(n〗_y)+1)制造为包 括导电路径(电感路径)对和单个导电路径。

[0210]

例如,在一个实施例中,制造者140以如前所述的方式在电感器 器件110-14的芯材料120中制造第一对导电路径(诸如第一导电路 径131和第二导电路径132)。如图所示,第二导电路径132(电感 器,相ph2)与第一导电路径131(电感器,相ph1)间隔开。第一对 中的导电路径131和132中的每个导电路径从电感器器件110-14的 近端111延伸到远端112。间隙141提供与第一电感路径(导电路径131)相关联的有益调整;间隙142提供与第一电感路径(导电路径 132)相关联的有益调整。

[0211]

另外,制造者将电感器器件110-14制造为在芯材料120中包括从 近端111到远端112的导电路径1433。以与先前讨论的类似方式,间 隙1443提供与第一电感路径(导电路径1433)相关联的有益调整。

[0212]

如进一步所示,电感器器件110-14在每个导电路径对或每个单个 导电路径的周边处包括任意数量的导电返回路径。

[0213]

例如,导电路径1451、1452、1455和1456关于第一对导电路径 131(电感器,相ph1)和132(电感器,路径ph2)设置;导电路径 1452、1453、1454和1455关于导电路径1433而设置。

[0214]

以与先前讨论的类似方式,导电路径1451、1452、1453、1454、 1455和1456中的每个导电路径以与先前针对电感器器件110讨论的 类似方式从电感器器件110-14的近端111延伸到远端112。

[0215]

图14b是图示了根据本文实施例的图14中的电感器器件的焊盘 的视图的示例图。

[0216]

如该示例实施例中所示,制造者140将电感器器件1410生产为 在近端111处包括多个导电焊盘(由金属、金属合金等制造)来促进 电感器器件110-14与相应电路的连接。

[0217]

如进一步所示,制造者140将导电焊盘1551(诸如vout焊盘) 耦合/连接到导电路径1451的近端111。

[0218]

制造者140将导电焊盘1552(诸如接地焊盘)耦合/连接到导电 路径1452的近端111。

[0219]

制造者140将导电焊盘1553(诸如vout焊盘)耦合/连接到导电 路径1453的近端111。

[0220]

制造者140将导电焊盘1554(诸如接地焊盘)耦合/连接到导电 路径1454的近端111。

[0221]

制造者140将导电焊盘1555(诸如vout焊盘)耦合/连接到导电 路径1455的近端111。

[0222]

制造者140将导电焊盘1556(诸如接地焊盘)耦合/连接到导电 路径1456的近端111。

[0223]

制造者140将导电路径1451的远端112耦合到导电焊盘1420-1 (vout)。

[0224]

制造者140将导电路径1452的远端112耦合到导电焊盘1410-2 (接地)。

[0225]

制造者140将导电路径1453的远端112耦合到导电焊盘1420-1 (vout)。

[0226]

制造者140将导电路径1454的远端112耦合到导电焊盘1410-3 (接地)。

[0227]

制造者140将导电路径1455的远端112耦合到导电焊盘1420-1 (vout)。

[0228]

制造者140将导电路径1456的远端112耦合到导电焊盘1410-1 (接地)。

[0229]

图15是图示了根据本文实施例的图14中描述的电感器器件的磁 耦合属性的示例图。

[0230]

图16是图示了根据本文实施例可操作为执行一个或多个方法的 示例计算机架构的图。

[0231]

如先前所讨论的,如本文所讨论的任何资源(诸如控制器1240、 制造者140等)可以被配置为包括计算机处理器硬件和/或对应的可执 行指令来执行如本文所讨论的不同操作。

[0232]

如图所示,本示例的计算机系统1600包括互连1611,互连1611 将计算机可读存储介质(crsm)1612(诸如非暂态类型的介质(可 以是其中可以存储并检索数字信息的任何合适类型的硬件存储介 质))、处理器1613(计算机处理器硬件)、i/o接口1614和通信 接口1617耦合。

[0233]

(多个)i/o接口1614支持与外部硬件1699(诸如,键盘、显示 屏、储存库等)的连接。

[0234]

计算机可读存储介质1612可以是任何硬件存储设备,诸如存储 器、光学存储装置、硬盘驱动装置、软盘等。在一个实施例中,计算 机可读存储介质1612存储指令和/或数据。

[0235]

如图所示,计算机可读存储介质1612可以利用制造者应用140-1 (例如,包括指令)而被编码为执行如本文所讨论的任何操作。

[0236]

在一个实施例的操作期间,处理器1613经由使用互连1611来访 问计算机可读存储介质1612,以启动、运行、执行、解释或以其他方 式执行计算机可读存储介质1612上存储的制造者应用140-1中的指 令。执行制造者应用140-1产生了制造者过程140-2来执行本文所讨 论的任何操作和/或过程。

[0237]

本领域技术人员将理解,计算机系统1600可以包括其他过程和/ 或软件和硬件部件,诸如控制硬件资源的分配和使用来执行制造者应 用140-1的操作系统。

[0238]

根据不同的实施例,请注意,计算机系统可以驻留在各种类型的 设备中的任何设备中,包括但不限于电源、开关式电容器转换器、功 率转换器、移动计算机、个人计算机系统、无线设备、无线接入点、 基站、电话设备、台式电脑、膝上型电脑、笔记本电脑、上网本电脑、 大型机系统、掌上电脑、工作站、网络计算机、应用服务器、存储设 备、消费电子设备(诸如相机、摄像机)、机顶盒、移动设备、视频 游戏机、手持视频游戏设备、外围设备(诸如交换机)、调制解调器、 路由器、机顶盒、内容管理设备、手持遥控设备、任何类型的计算或 电子设备等。计算机系统1650可以驻留在任何位置处,或者可以被 包括在任何网络环境中的任何合适的资源中来实现如本文所讨论的 功能。

[0239]

如本文所述,由一个或多个资源支持的功能经由图17中的流程 图来讨论。请注意,以下流程图中的步骤可以以任何合适的顺序来执 行。

[0240]

图17是图示了根据本文实施例的示例方法的流程图1700。请注 意,与以上讨论的概念会有一些重叠。

[0241]

在处理操作1710中,制造者(组装者)接收芯材料块120,芯材 料120是可导磁材料。

[0242]

在处理操作1720中,制造者将第一导电路径131设置为从电感 器器件110的近端111穿过芯材料120,到达电感器器件110的远端 112。芯材料120限制由流过第一导电路径131的电流产生的第一磁 通量。

[0243]

在处理操作1730中,制造者将芯材料120制造为包括与第一导 电路径131相关联的间隙141。间隙141(诸如被填充有空气、真空、 其他材料)具有与芯材料不同的磁导率120。

[0244]

再次注意,本文中的技术非常适用于电感器和功率转换器应用。 然而,应当注意,本文中的实施例不限于在这样的应用中使用,并且 本文中讨论的技术也很好地适用于其他应用。

[0245]

虽然已参考其优选实施例具体地示出和描述了本发明,但是本领 域技术人员将理解,在不脱离所附权利要求所限定的本技术的精神和 范围的情况下,可以在形式和细节上做出各种改变。这样的改变旨在 被本技术的范围所覆盖。因此,本技术的实施例的前述描述不旨在限 制。相反,对本发明的任何限制在所附权利要求书中呈现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1