1.本发明涉及半导体技术领域,尤其涉及一种静电防护器件及其制作方法。

背景技术:2.静电放电esd(electro-static discharge)是日常生活中的常见现象,虽不易被人体感知,却会对集成电路产品造成严重威胁。据美国国家半导体公司(national-semiconductor)数据统计表明,现今集成电路失效产品中的38%是由esd/eos(electrostatic-discharge/electrical-over-stress)所引起的。对于高压cmos或高压bcd工艺,其广泛的用于制造电源管理、高压驱动以及汽车电子等领域的集成电路产品中。而这类集成电路产品往往工作在大电流、大电压、强电磁干扰环境下,esd防护器件会出现低鲁棒性、误触发等问题,需要高可靠、高鲁棒性的esd解决防护方案。

3.现有的技术中,由于传统ldmos(如图1结构所示),当esd脉冲来临时,nldmos器件寄生npn管存在开启的非均匀性问题,会导致局部电流聚积,电子电流密度超过漂移区杂质浓度后,电场峰值转移到近漏端,nldmos内部发生内部kirk(基区扩展效应),局部过热失效。为防止kirk效应的产生,如图2所示,通常在传统ldmos器件的漏端插入p+注入区,形成可控硅整流器scr(silicon controlled rectifier,scr)器件结构。ldmos-scr作为esd防护器件,具有出色的鲁棒性和单位面积效率,可以通过较高的hbm测试。但是如图3所示,传统ldmos-scr器件的scr结构触发之后维持电压(vh)很低,如果芯片在测试或者工作的过程中,电源管脚发生一定程度的电压过冲或者电压尖峰毛刺,造成scr器件误触发维持在很低的电压值,造成闩锁效应,烧毁芯片。

4.因此,针对现有静电保护器件中容易误触发闩锁效应的问题,有必要提出进一步地的解决方案。

技术实现要素:5.本发明的目的在于提供一种静电防护器件及其制作方法,能够克服现有技术中,双叉指ldmos-scr器件在发生电压过冲或者电压尖峰毛刺时误触发寄生scr,导致深回滞到很低的维持电压引起闩锁现象,即避免误触发闩锁现象。

6.为实现上述发明目的,本发明提供一种静电防护器件,包括

7.衬底;

8.具有第一导电类型的漂移区,形成于所述衬底上;

9.具有第一导电类型的阱区,形成于所述漂移区上;

10.第一体区和第二体区,分别设于所述阱区的两侧,该第一体区和第二体区具有第二导电类型,且所述阱区与所述第一体区的距离小于所述阱区与所述第二体区的距离;

11.其中

12.所述第一体区中仅形成具有第二导电类型的第一重掺区;

13.所述第二体区中设有第一导电类型的第二重掺区和第二导电类型的第三重掺区;

14.所述阱区中仅设有第二导电类型的第四重掺区。

15.优选的,所述第四重掺区和所述第一重掺区之间构成第一寄生器件,所述第四重掺区和所述第二重掺区之间构成第二寄生器件,且所述第一寄生器件具有比所述第二寄生器件更小的击穿电压。

16.优选的,所述第一导电类型为n型,所述第二导电类型为p型,所述第一寄生器件为pnp三极管,所述第二器件为可控硅整流器件。

17.优选的,所述第一体区和第二体区上设有与各个重掺区欧姆接触的电极引出线,该第一体区和第二体区的所有电极引出线共接在低压端形成所述静电防护器件的阴极,所述阱区上设有与所述第四重掺区欧姆接触的电极引出线,所述阱区上的电极引出线接在高压端形成所述静电防护器件的阳极。

18.优选的,所述阳极上有静电脉冲电压时,所述第一寄生器件中的反向pn结发生击穿使得该第一寄生器件被打开,并在静电电压持续增大时,所述静电防护器件上的电压达到所述第二寄生器件的击穿电压,使得该第二寄生器件被打开,形成该器件对静电电流的最大泄流模式。

19.优选的,所述静电防护器件为ldmos-scr器件,所述第一体区上还设有第一栅极区,该第一栅极区位于所述第一重掺区和所述第四重掺区之间,所述第二体区上还设有第二栅极区,该第二栅极区位于所述第二重掺区和所述第四重掺区之间。

20.优选的,所述第一栅极区和所述第二栅极区分别与所述第四重掺区之间设有隔离,所述第一栅极区和第二栅极区上均设有多晶硅栅,该多晶硅栅往所述隔离上延伸构成场板。

21.优选的,所述漂移区与所述第一体区和第二体区分别构成第一反向pn结和第二反向pn结,且所述第一反向pn结的击穿电压小于所述第二反向pn结的击穿电压。

22.根据本发明的目的还提出了一种如上所述的静电防护器件的制作方法,所述制作方法包括如下步骤:

23.提供一衬底;

24.在所述衬底上生长具有第一导电类型的漂移区;

25.在所述漂移区上进行掺杂,分别形成具有第二导电类型的第一体区和第二体区,以及具有第一导电类型的阱区;

26.在所述第一体区、第二体区以及阱区中进行重掺,形成具有第二导电类型的第一重掺区、第三重掺区和第四重掺区;

27.在所述第二体区中重掺,形成具有第一导电类型的第二重掺区;

28.在所述第一重掺区、第二重掺区、第三重掺区以及第四重掺区上制作电极,并在所述电极上制作电引出线,将所述第一体区和第二体区上的电极接入低压端形成阴极,将所述阱区上的电极接入高压端形成阳极。

29.优选的,所述静电防护器件为ldmos-scr器件,该ldmos-scr器件还包括第一栅极区和第二栅极区,分别形成于所述第一体区和第二体区上,该第一栅极区位于所述第一重掺区和所述第四重掺区之间,所述第二体区上还设有第二栅极区,该第二栅极区位于所述第二重掺区和所述第四重掺区之间,且所述第一栅极区和第二栅极区上的栅极通过电引出线被接在所述阴极上。

30.与现有技术相比,本发明的有益效果是:本发明将传统的双叉指ldmos-scr器件漏端n阱中仅留下p+注入区,去掉左边叉指源端p阱中的n+注入区,左边叉指仅保留寄生pnp三极管,右边叉指保留寄生scr,同时设计相关尺寸使得pnp先于scr触发,结合pnp没有回滞的特性及scr的高鲁棒性,使静电防护器件能够在有效静电防护的同时,避免在发生电压过冲或者电压尖峰毛刺时误触发寄生scr,导致深回滞到很低的维持电压引起闩锁现象,即避免误触发闩锁现象。

附图说明

31.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1为传统的ldmos器件结构示意图。

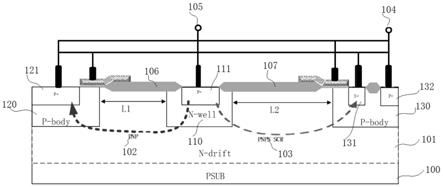

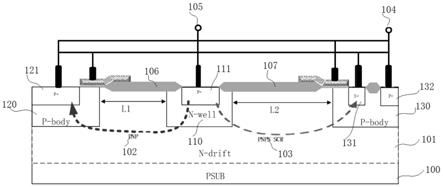

33.图2是一种现有的ldmos-scr器件结构示意图。

34.图3是现有的ldmos-scr的tlp曲线图。

35.图4是本发明的静电防护器件的结构示意图。

36.图5是本发明静电防护器件的tlp曲线图

具体实施方式

37.下面结合各实施方式对本发明进行详细说明,但应当说明的是,这些实施方式并非对本发明的限制,本领域普通技术人员根据这些实施方式所作的功能、方法、或者结构上的等效变换或替代,均属于本发明的保护范围之内。

38.正如背景技术中所述,在传统的ldmos-scr结构中,容易出现闩锁效应使得器件在误触发之后被烧毁。申请人对该现象经过研究后,发现该技术问题的原理如下:对于传统的ldmos-scr结构,其等效电路图如图2所示,包括两个对称分布的mos器件,其中间的n-well构成了漏极区,由于漏极区中包括了一个n型重掺区和两个p型重掺区,使得每个mos器件都产生了寄生的三极管npn和pnp。当正向esd脉冲来临时,正电压使得scr中的n-drift和p-body所形成的pn结发生反偏,随着esd电压逐渐增大,pn结逐渐进入雪崩击穿。pn结雪崩产生的空穴从n阱流入p阱最后被p阱中的p+注入区收集产生电流i

nw

;同样的,产生的电子从p阱流入n阱最后被n阱的n+注入区收集产生电流i

pw

。由于n阱和p阱都存在寄生电阻r

n-well

以及r

p-well

,所以会在n阱及p阱上形成压降。当n阱或者p阱上的压降达到0.7v时,寄生三极管npn或者pnp其中一个就会开启。当一个三极管开启后,其集电极上产生电流所导致的压降又会马上使另一个寄生三极管开启。最终两个三极管形成开路正反馈机制,scr完全开启,形成一条低阻的通路,电压钳位在很低的值,其tlp曲线如图3所示。如果芯片在测试或者工作的过程中,电源管脚发生一定程度的电压过冲或者电压尖峰毛刺,造成scr器件误触发维持在很低的电压值,造成闩锁效应,烧毁芯片。

39.针对上述问题,在本发明中,如图4所示,将传统的双叉指ldmos-scr器件漏端n阱中仅留下p+注入区,同时去掉左边叉指源端p阱中的n+注入区,左边叉指形成寄生pnp三极管,右边叉指形成寄生scr,同时将scr一侧的漂移区l2拉大(l2>l1),使得scr的击穿电压

大于pnp三极管。当esd脉冲来临时,击穿电压较低的pnp三极管先开启,tlp曲线如图5所示,此时对应于vt1的点,由于pnp三极管没有回滞特性,因此器件上的电压会持续升高,当电压升高到scr的击穿电压时,scr路径开启,泄放esd电流。从tlp曲线中可以看到,当芯片管脚发生一定程度的电压过冲或者电压尖峰毛刺时,只要触发pnp之后电流不高于scr的触发电流,就无法继续触发scr路径,从而避免误触发闩锁效应。该器件结合了pnp没有回滞的特性及scr的高鲁棒性,在esd有效防护的同时,可防止管脚过压引起的误触发闩锁效应。

40.下面将通过具体实施例,本本发明的技术方案做详细描述。需要注意的是,由于ldmos器件分为p型管和n型管,两者之间以载流子类型作为区分,虽然在工作特性上有所不同,然而其实现功能的工作原理基本相同,故而在以下所举的实施例中,将以n型沟道的ldmos管作为例子进行说明,此时n型掺杂作为第一导电类型半导体,p型掺杂作为第二导电类型半导体。p型管在本专利的思想基础上做相应调整即可。

41.请参见图4,图4是本发明的一种静电防护器件的结构示意图,如图所示,包括衬底100,该衬底用以提供半导体器件所需的载体,一般的,衬底的导电类型为p型。形成在衬底100上的n型的漂移区101,该漂移区101用以构建器件区,并且提供载流子流动的沟道。在该漂移区101上分别形成n型的阱区110,p型的第一阱区120和第二体区130,第一阱区120和第二体区130分布在阱区110的两侧。其中n型阱区主要用以形成ldmos器件的漏区,p型的第一体区120和第二体区130主要用以形成源区和栅区,这样可以构成一对双向的ldmos器件。

42.与传统的ldmos-scr器件相比,在本发明中,在第一体区120中仅形成具有p型的第一重掺区121,在第二体区130则设置n型的第二重掺区131和p型的第三重掺区132,同时在阱区110中仅设有p型的第四重掺区111。这样的设置方式,改变了传统ldmos-scr器件的对称结构,使得两边的mos器件具有非对称的结构,此时对应于第一体区120所对应的mos器件,其内部只寄生了一个第一寄生器件102,该第一寄生器件102由第四重掺区111经过阱区110、漂移区101之后达到第一体区120内的第一重掺区121,形成的pnp管。而第二体区130对应的mos器件,其内部寄生了一个第二寄生器件103,该第二寄生器件103由第四重掺区111经过阱区110、漂移区101达到第二体区130内的第二重掺区131,形成pnpn的scr结构。无论是第一寄生器件102还是第二寄生器件103,其内部都有一个反接的pn结,当esd电压来临时,都需要击穿该反向pn结,使得器件形成雪崩电流从而导通泄流。

43.另一方面,在本发明中,将阱区110与第一体区120之间的距离设计成小于阱区110与第二体区130之间的距离,这样一来,第一寄生器件102具有比第二寄生器件103更小的击穿电压,从而使得第一寄生器件102的pnp管在esd电压来临时,更快的达到雪崩击穿的电压阈值从而被击穿。请参照图5,图5是本发明的静电防护器件的tlp曲线图,如图5所示,在第一寄生器件102的反向pn结被击穿时,对应于图中vt1的点,由于pnp三极管没有回滞特性,因此器件上的电压会持续升高,当电压升高到第二寄生器件103的击穿电压时,第二寄生器件103中的scr器件开启,泄放esd电流。从tlp曲线中可以看到,当芯片管脚发生一定程度的电压过冲或者电压尖峰毛刺时,只要触发pnp之后电流不高于scr的触发电流,就无法继续触发scr路径,从而避免误触发闩锁效应。

44.进一步的,在第一体区120和第二体区130上设有与各个重掺区欧姆接触的电极引出线,该第一体区120和第二体区130的所有电极引出线共接在低压端形成静电防护器件的阴极104。阱区110上设有与第四重掺区111欧姆接触的电极引出线,该阱区110上的电极引

出线接在高压端形成静电防护器件的阳极105。当阳极105上有静电脉冲电压时,该第一寄生器件102中的反向pn结优选发生击穿使得该第一寄生器件102被打开,并在静电电压持续增大时,该静电防护器件上的电压达到第二寄生器件103的击穿电压,使得该第二寄生器件103被打开,形成该器件对静电电流的最大泄流模式。

45.进一步的,该ldmos-scr器件的两个栅极区分别设置在第一体区120和第二体区130面阱区110一侧的部分表面上,其中第一栅极区122和第二栅极区132分别与第四重掺区111之间设有隔离106、107,这两个隔离106、107分别对应设置在两个mos器件的沟道上,形成该两个隔离的工艺可以为场氧工艺或浅槽隔离工艺。第一栅极区122和第二栅极区132上均设有多晶硅栅,并且该多晶硅栅往所述隔离106、107上延伸构成场板,可以调控沟道中的电流和电压。

46.进一步的,所述漂移区与所述第一体区和第二体区分别构成第一反向pn结和第二反向pn结,即两个耗尽区,且由于这两个耗尽区的长度不一致,从而使得所述第一反向pn结的击穿电压小于所述第二反向pn结的击穿电压。

47.下面就本发明器件的制作方法再做描述。

48.根据上述器件,本发明提出的电防护器件的制作方法,包括如下步骤:

49.提供一衬底;

50.在所述衬底上生长具有第一导电类型的漂移区;

51.在所述漂移区上进行掺杂,分别形成具有第二导电类型的第一体区和第二体区,以及具有第一导电类型的阱区;

52.在所述第一体区、第二体区以及阱区中进行重掺,形成具有第二导电类型的第一重掺区、第三重掺区和第四重掺区;

53.在所述第二体区中重掺,形成具有第一导电类型的第二重掺区;

54.在所述第一重掺区、第二重掺区、第三重掺区以及第四重掺区上制作电极,并在所述电极上制作电引出线,将所述第一体区和第二体区上的电极接入低压端形成阴极,将所述阱区上的电极接入高压端形成阳极。

55.进一步的,所述静电防护器件为ldmos-scr器件,该ldmos-scr器件还包括第一栅极区和第二栅极区,分别形成于所述第一体区和第二体区上,该第一栅极区位于所述第一重掺区和所述第四重掺区之间,所述第二体区上还设有第二栅极区,该第二栅极区位于所述第二重掺区和所述第四重掺区之间,且所述第一栅极区和第二栅极区上的栅极通过电引出线被接在所述阴极上。

56.综上所述,本发明通过将传统的双叉指ldmos-scr器件漏端n阱中仅留下p+注入区,去掉左边叉指源端p阱中的n+注入区,左边叉指仅保留寄生pnp三极管,右边叉指保留寄生scr,同时设计相关尺寸使得pnp先于scr触发,结合pnp没有回滞的特性及scr的高鲁棒性,避免误触发闩锁效应。

57.对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。

58.此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。