共模扼流圈的制作方法

1.该发明涉及共模扼流圈,特别是涉及具备具有被层叠的多个非导电体层的层叠体、和内置于层叠体的第一线圈以及第二线圈的层叠型的共模扼流圈。

背景技术:

2.对于该发明来说感兴趣的技术例如记载于日本特开2006-313946号公报(专利文献1)。专利文献1所记载的技术涉及层叠型的共模扼流圈,该共模扼流圈是超小型的薄膜型的扼流圈,能够进行ghz附近的传输信号的高速传输。更具体而言,在专利文献1记载了当将传输信号(差模信号)的衰减特性为-3db的频率定义为截止频率时,该截止频率为2.4ghz以上的共模扼流圈。

3.专利文献1:日本特开2006-313946号公报

4.由于高速通信技术的发展,需要能够在更高频下,使差模信号透过,并且抑制共模噪声成分的层叠型的共模扼流圈。

技术实现要素:

5.因此,该发明的目的在于提供即使在例如25ghz~30ghz这样的较高的频带,甚至在超过30ghz的极高的频带中,也能够使差模信号透过,并且抑制共模噪声成分的层叠型的共模扼流圈。

6.该发明所涉及的共模扼流圈具备:层叠体,具有被层叠的多个非导电体层,上述非导电体层由非导电体构成;第一线圈以及第二线圈,内置于层叠体;第一端子电极以及第二端子电极,设置于层叠体的外表面,并分别与第一线圈的相互不同的第一端以及第二端电连接;以及第三端子电极以及第四端子电极,设置于层叠体的外表面,并分别与第二线圈的相互不同的第三端以及第四端电连接。

7.上述的层叠体是长方体形状,其具有:上面以及下面,向非导电体层的延伸方向延伸并且相互对置;第一侧面以及第二侧面,将上面以及下面间连结并且相互对置;第一端面以及第二端面,分别将上面以及下面间及第一侧面以及第二侧面间连结并且相互对置,下面是朝向安装基板侧的安装面。

8.第一端子电极具有:第一侧面电极部,设置于第一侧面;和第一下面电极部,与第一侧面电极部相连并设置于下面的一部分。

9.第二端子电极具有:第二侧面电极部,设置于第二侧面;和第二下面电极部,与第二侧面电极部相连并设置于下面的一部分。

10.第三端子电极具有:第三侧面电极部,设置于第一侧面;和第三下面电极部,与第三侧面电极部相连并设置于下面的一部分。

11.第四端子电极具有:第四侧面电极部,设置于第二侧面;和第四下面电极部,与第四侧面电极部相连并设置于下面的一部分。

12.第一线圈具有第一线圈导体,该第一线圈导体沿着非导电体层间的界面配置,第

二线圈具有第二线圈导体,该第二线圈导体沿着与配置了第一线圈导体的非导电体层间的界面不同的非导电体层间的界面配置。

13.在具备这样的构成的共模扼流圈中,为了解决上述的技术课题,在该发明中,第一特征在于当将第一线圈的路径长度设为l1,并将第二线圈的路径长度设为l2时,l1和l2的合计长度为3.4mm以下,并且第二特征在于第一下面电极部、第二下面电极部、第三下面电极部以及第四下面电极部各自的面积为0.034μm2以下。

14.根据该发明,能够降低第一线圈与第二线圈之间的杂散电容、及端子电极与第一线圈以及第二线圈之间的杂散电容,所以能够使共模扼流圈的高频特性提高。

附图说明

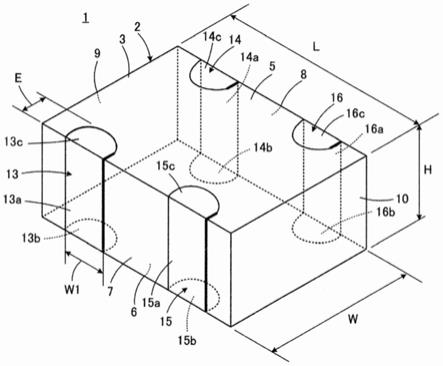

15.图1是表示该发明的一实施方式的共模扼流圈1的外观的立体图。

16.图2是分解表示图1所示的共模扼流圈1的主要部分的俯视图。

17.图3是图1所示的共模扼流圈1的俯视图,是示意性地表示在层叠方向透视内置于层叠体2的第一线圈11以及第二线圈12的图。

18.图4是表示图1所示的共模扼流圈1中的第一线圈11所具备的第一线圈导体17的俯视图,是用于说明线圈导体的匝数的图。

19.图5是表示在为了确认该发明的效果而实施的实验例中制成的共模扼流圈的样品中,代表性地对样品8所涉及的共模扼流圈求出的共模成分的透过特性(scc21透过特性)的图。

20.图6是表示对上述样品8所涉及的共模扼流圈求出的差模成分的透过特性(sdd21透过特性)的图。

21.附图标记说明

[0022]1…

共模扼流圈,2

…

层叠体,3、3a、3b、3c、3d、3e

…

非导电体层,5

…

上面,6

…

下面,7、8

…

侧面,9、10

…

端面,11

…

第一线圈,12

…

第二线圈,13

…

第一端子电极,13a

…

第一侧面电极部,13b

…

第一下面电极部,13c

…

第一上面电极部,14

…

第二端子电极,14a

…

第二侧面电极部,14b

…

第二下面电极部,14c

…

第二上面电极部,15

…

第三端子电极,15a

…

第三侧面电极部,15b

…

第三下面电极部,15c

…

第三上面电极部,16

…

第四端子电极,16a

…

第四侧面电极部,16b

…

第四下面电极部,16c

…

第四上面电极部,17、18

…

线圈导体,19~22

…

引出导体,23~26

…

连接端部,27、28

…

通孔导体,29、30

…

连结部。

具体实施方式

[0023]

参照图1~图4,对该发明的一实施方式的共模扼流圈1进行说明。

[0024]

如图1所示,共模扼流圈1具备具有被层叠的多个非导电体层的层叠体2。在图2图示有多个非导电体层中代表性的非导电体层3a、3b、3c、3d以及3e。以下,除了如图2所示的非导电体层3a、3b、3c、3d以及3e那样相互进行区分的情况之外,在对非导电体层进行一般的说明的情况下,对非导电体层使用“3”的参照附图标记。非导电体层3例如由包含玻璃以及陶瓷的非导电体构成。

[0025]

层叠体2是具有向非导电体层3的延伸方向延伸并且相互对置的上面5以及下面6、连结上面5以及下面6间并且相互对置的第一侧面7以及第二侧面8、分别连结上面5以及下

面6间及第一侧面7以及第二侧面8间并且相互对置的第一端面9以及第二端面10的长方体形状。长方体形状例如也可以是对棱线部分以及角部分赋予了倒圆、倒角的形状。在共模扼流圈1安装于安装基板时,上述下面6成为朝向安装基板侧的安装面。

[0026]

如图2以及图3所示,共模扼流圈1具备内置于层叠体2的第一线圈11以及第二线圈12。另外,如图1所示,共模扼流圈1具备设置于层叠体2的外表面的第一端子电极13、第二端子电极14、第三端子电极15以及第四端子电极16。

[0027]

第一端子电极13具有设置于第一侧面7的第一侧面电极部13a、与第一侧面电极部13a相连并设置于下面6的一部分的第一下面电极部13b、以及与第一侧面电极部13a相连并设置于上面5的一部分的第一上面电极部13c。

[0028]

第二端子电极14具有设置于第二侧面8的第二侧面电极部14a、与第二侧面电极部14a相连并设置于下面6的一部分的第二下面电极部14b、以及与第二侧面电极部14a相连并设置于上面5的一部分的第二上面电极部14c。

[0029]

第三端子电极15具有设置于第一侧面7的第三侧面电极部15a、与第三侧面电极部15a相连并设置于下面6的一部分的第三下面电极部15b、以及与第三侧面电极部15a相连并设置于上面5的一部分的第三上面电极部15c。

[0030]

第四端子电极16具有设置于第二侧面81第四侧面电极部16a、与第四侧面电极部16a相连并设置于下面6的一部分的第四下面电极部16b、以及与第四侧面电极部16a相连并设置于上面5的一部分的第四上面电极部16c。

[0031]

如图2所示,第一端子电极13以及第二端子电极14分别与第一线圈11的相互不同的第一端11a以及第二端11b电连接。第三端子电极15以及第四端子电极16分别与第二线圈12的相互不同的第三端12a以及第四端12b电连接。

[0032]

在以下的说明中,非导电体层3a、3b、3c、3d以及3e按照图2所示的顺序由下向上层叠。

[0033]

参照图2,第一线圈11具有沿着非导电体层3b以及3c间的界面配置的第一线圈导体17。第一线圈11具有分别提供第一端11a以及第二端11b的第一引出导体19以及第二引出导体20。第一引出导体19包含在层叠体2的外表面与第一端子电极13连接的第一连接端部23。第二引出导体20包含在层叠体2的外表面与第二端子电极14连接的第二连接端部24。

[0034]

上述第一连接端部23沿着与配置了第一线圈导体17的非导电体层3b以及3c间的界面不同的非导电体层3a以及3b间的界面配置。另外,第一引出导体19具有:第一通孔导体27,与第一线圈导体17连接并且在厚度方向贯通位于第一线圈导体17与第一连接端部23之间的非导电体层3b;和第一连结部29,沿着配置了第一连接端部23的非导电体层3a以及3b间的界面配置并且将第一通孔导体27与第一连接端部23连接。优选第一连结部29具有直线状地延伸的形状。由此,能够减小起因于第一连结部29的电感,能够使高频特性提高。

[0035]

另一方面,在第二线圈12中,如以下说明的那样,也具备与第一线圈11的情况相同的要素。

[0036]

第二线圈12具有沿着非导电体层3c以及3d间的界面配置的第二线圈导体18。第二线圈12具有分别提供第三端12a以及第四端12b的第三引出导体21以及第四引出导体22。第三引出导体21包含在层叠体2的外表面与第三端子电极15连接的第三连接端部25。第四引出导体22包含在层叠体2的外表面与第四端子电极16连接的第四连接端部26。

[0037]

上述第三连接端部25沿着与配置了第二线圈导体18的非导电体层3c以及3d间的界面不同的非导电体层3d以及3e间的界面配置。另外,第三引出导体21具有:第二通孔导体28,与第二线圈导体18连接并且在厚度方向贯通位于第二线圈导体18与第三连接端部25之间的非导电体层3d;和第二连结部30,沿着配置了第三连接端部25的非导电体层3d以及3e间的界面配置并且将第二通孔导体28与第三连接端部25连接。第二连结部30与上述的第二连结部29相同,优选具有直线状地延伸的形状。由此,能够减小起因于第二连结部30的电感,能够使高频特性提高。

[0038]

共模扼流圈1以使层叠体2的下面6朝向安装基板侧的状态安装。在实施品中,例如层叠体2中的第一端面9与第二端面10对置的长度方向的尺寸l为0.55mm以上并且0.75mm以下,第一侧面7与第二侧面8对置的宽度方向的尺寸w为0.40mm以上并且0.60mm以下,上面5与下面6对置的高度方向的尺寸h为0.20mm以上并且0.40mm以下。

[0039]

根据图2以及图3可知,共模扼流圈1优选第一线圈导体17以及第二线圈导体18各自的匝数为一匝以下。

[0040]

上述的匝数如以下那样定义。第一线圈导体17以及第二线圈导体18分别具有圆弧状地延伸的部分。参照图4,对第一线圈11所具备的第一线圈导体17进行说明。如图4所示,从线圈导体17的始端朝向终端,沿着线圈导体17的外周依次绘制切线t,在该切线t旋转了360度的阶段定义为一匝。在图4所示的线圈导体17中,切线t大约旋转307度,所以能够定义为大约0.85匝。也同样地对第二线圈12所具备的第二线圈导体18定义匝数。

[0041]

第一线圈导体17以及第二线圈导体18的匝数越少,越能够降低在第一线圈11与第二线圈12之间形成的杂散电容,所以能够使共模扼流圈1的高频特性提高。

[0042]

如上述那样,与匝数较少相关,共模扼流圈1的第一特征在于当将第一线圈11的路径长度设为l1,并将第二线圈12的路径长度设为l2时,l1和l2的合计长度为3.4mm以下。通过具备该特征,能够降低在第一线圈11与第二线圈12之间形成的杂散电容,所以共模扼流圈1能够在较高的频带,使差模信号透过,并且抑制共模噪声成分,能够使共模扼流圈1的高频特性提高。

[0043]

在图2中,第一线圈11的路径长度l1是从第一线圈11的第一端11a经由第一引出导体19具备的第一连接端部23、第一连结部29以及第一通孔导体27、第一线圈导体17、以及第二引出导体20所具备的第二连接端部24,并到达第二端11b为止的合计的路径长度,在第一线圈导体17中,沿着宽度方向的大致中央部测定路径长度。

[0044]

同样地,在图2中,第二线圈12的路径长度l2是从第二线圈12的第三端12a经由第三引出导体21所具备的第三连接端部25、第二连结部30以及第二通孔导体28、第二线圈导体18、以及第四引出导体22所具备的第四连接端部26,并到达第四端12b为止的合计的路径长度,在第二线圈导体18中,沿着宽度方向的大致中央部测定路径长度。

[0045]

实际上,在层叠方向对层叠体2进行研磨,使第三连接端部25以及第二连结部30露出,并利用测定显微镜测定第三连接端部25以及第二连结部30各自的路径长度。进一步进行研磨,使第二线圈导体18以及第四连接端部26露出,并利用测定显微镜测定第二线圈导体18以及第四连接端部26各自的路径长度。进一步进行研磨,使第一线圈导体17以及第二连接端部24露出,并利用测定显微镜测定第一线圈导体17以及第二连接端部24各自的路径长度。进一步进行研磨,使第一连接端部23以及第一连结部29露出,并利用测定显微镜测定

第一连接端部23以及第一连结部29各自的路径长度。

[0046]

另一方面,准备其它的层叠体2,在与层叠方向正交的方向对该层叠体2进行研磨,使第一通孔导体27以及第二通孔导体28露出,并利用测定显微镜测定第一通孔导体27以及第二通孔导体28各自的层叠方向上的长度。

[0047]

接下来,将通过以上的测定得到的第三连接端部25、第二连结部30、第二通孔导体28、第二线圈导体18以及第四连接端部26的长度的合计作为第二线圈12的路径长度。同样地,将第一连接端部23、第一连结部29、第一通孔导体27、第一线圈导体17以及第二连接端部24的长度的合计作为第一线圈11的路径长度。

[0048]

如图3所示,优选在层叠体2的层叠方向俯视第一线圈导体17以及第二线圈导体18时,在第一线圈导体17以及第二线圈导体18,除了相互交叉的部分之外,没有相互重合的部分。这有助于降低在第一线圈11与第二线圈12之间形成的杂散电容,作为结果,能够使共模扼流圈1的高频特性提高。

[0049]

另外,根据图3可知,在层叠体2的层叠方向俯视第一线圈导体17以及第二线圈导体18时,第一线圈导体17与第二线圈导体18相互交叉的部位为两个部位。这样,通过使交叉的部位为两个部位以下,能够降低在第一线圈导体17与第二线圈导体18之间形成的杂散电容,有助于高频特性的提高。

[0050]

优选第一线圈导体17与第二线圈导体18之间的距离为6μm以上并且26μm以下。若该距离小于6μm,则有在第一线圈导体17与第二线圈导体18之间形成的杂散电容大至使高频特性降低的程度的担心。另一方面,若该距离超过26μm,则有第一线圈11与第二线圈12的耦合系数降低的担心。

[0051]

此外,虽然在图2中,图示为非导电体层3a、3b、3c、3d以及3e分别为单层,但也可以至少几个非导电体层由多层构成。因此,例如,上述的第一线圈导体17与第二线圈导体18之间的距离的调整既可以通过变更非导电体层3c的单层的厚度来进行,也可以通过变更构成非导电体层3c的层的数目来进行调整。

[0052]

另外,优选第一线圈导体17以及第二线圈导体18各自的线宽度为10μm以上并且24μm以下。若该线宽度小于10μm,则有线圈导体17以及18中的直流电阻较大的担心。另一方面,若该线宽度超过24μm,则有在第一线圈导体17与第二线圈导体18之间形成的杂散电容大至使高频特性降低的程度的担心。

[0053]

作为共模扼流圈1的第二特征,在第一端子电极13、第二端子电极14、第三端子电极15以及第四端子电极16中,第一下面电极部13b、第二下面电极部14b、第三下面电极部15b以及第四下面电极部16b各自的面积为0.034μm2以下,优选第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c各自的面积也为0.034μm2以下。

[0054]

通过具备上述的特征,能够降低端子电极13~16与第一线圈11以及第二线圈12之间的杂散电容,所以能够使共模扼流圈1的高频特性提高。

[0055]

此外,对于第一下面电极部13b、第二下面电极部14b、第三下面电极部15b以及第四下面电极部16b各自的形状、及第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c各自的形状来说,虽然在图1中大致为半圆状,但也可以是例如矩形形状等其它的形状。

[0056]

只要最低限度地满足第一下面电极部13b、第二下面电极部14b、第三下面电极部

15b以及第四下面电极部16b各自的面积为0.034μm2以下这样的条件就能够起到上述的降低杂散电容的效果。对此,也应该考虑存在本来不具备第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c的共模扼流圈。然而,在具备第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c的情况下,通过也使这些上面电极部13c、14c、15c以及16c各自的面积为0.034μm2以下,能够更可靠地并且更显著地起到降低杂散电容的效果。

[0057]

第一下面电极部13b、第二下面电极部14b、第三下面电极部15b以及第四下面电极部16b各自的面积的下限例如为0.004μm2。然而,为了在将共模扼流圈1安装于安装基板时得到足够的固定强度,优选上述面积的下限为0.012μm2。

[0058]

另外,端子电极13~16从上面5形成到下面6,各个端子电极13~16中的设置于第一侧面7或者第二侧面8的第一侧面电极部13a、第二侧面电极部14a、第三侧面电极部15a以及第四侧面电极部16a各自的在第一侧面7或者第二侧面8上的宽度(在图1中,以“w1”表示第一侧面电极部13a的在第一侧面7上的宽度。)优选为0.1mm以上并且0.25mm以下,更优选为0.15mm以上。若该宽度小于0.1mm,则有将共模扼流圈1安装于安装基板时的固定强度不足的担心。另一方面,若该宽度超过0.25mm,则有使共模扼流圈1的高频特性降低的担心。

[0059]

在图1中,对第一端子电极13的第一上面电极部13c,图示与宽度方向正交的方向的尺寸e,优选端子电极13~16中的第一下面电极部13b、第二下面电极部14b、第三下面电极部15b以及第四下面电极部16b、及第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c各自的尺寸e为0.02mm以上并且0.2mm以下,更优选为0.17mm以下。若尺寸e小于0.02mm,则有安装于安装基板时的共模扼流圈1的固定强度降低的担心。另一方面,若尺寸e超过0.2mm,则有使共模扼流圈1的高频特性降低的担心。

[0060]

接下来,对共模扼流圈1的优选的制造方法进行说明。

[0061]

为了制造应该成为非导电体层3的玻璃陶瓷薄片,实施以下的工序。将k2o、b2o3以及sio2、及根据需要的al2o3称量为成为规定的比率,放入白金制的坩埚,并在烧制炉升温至1500~1600℃的温度进行熔融。通过对该熔融物进行快速冷却得到玻璃材料。

[0062]

作为上述的玻璃材料,例如使用至少含有k、b以及si,且将k换算为k2o为0.5~5质量%,将b换算为b2o3为10~25质量%,将si换算为sio2为70~85质量%,将al换算为al2o3为0~5质量%构成的玻璃材料。

[0063]

接下来,通过将上述玻璃材料粉碎为d50(体积基准的累积百分率相当于50%的粒径)为1~3μm左右来得到玻璃粉末。

[0064]

接下来,在上述的玻璃粉末添加d50均为0.5~2.0μm的氧化铝粉末与石英(sio2)粉末,并与psz介质一起放入球磨机,并且,将聚乙烯醇缩丁醛系等有机粘合剂、乙醇、甲苯等有机溶剂、以及增塑剂放入球磨机,并进行混合,从而得到玻璃陶瓷浆料。

[0065]

接下来,通过刮浆法等将上述浆料成形加工为膜厚为20~30μm的片状,并将得到的薄片冲裁为矩形形状,从而得到多个玻璃陶瓷薄片。

[0066]

上述的玻璃陶瓷薄片所包含的无机成分例如包含含有60~66质量%的玻璃材料,含有34~37质量%的石英,且含有0.5~4质量%的氧化铝的电介质玻璃材料。

[0067]

另一方面,准备用于形成第一线圈11以及第二线圈12的将ag作为导电成分的导电性膏体。

[0068]

接下来,例如通过对规定的玻璃陶瓷薄片照射激光,设置用于配置通孔导体27以及28的贯通孔。其后,例如通过丝网印刷对规定的玻璃陶瓷薄片赋予导电性膏体,由此,形成在上述贯通孔填充了导电性膏体的状态的通孔导体27以及28,并且以图案化的状态形成线圈导体17以及18及构成引出导体19~22的连接端部23~26以及连结部29以及30。

[0069]

接下来,将多个玻璃陶瓷薄片层叠为得到图2所示的非导电性体层3a~3e的层叠顺序。此时,根据需要在这些玻璃陶瓷薄片的层叠的上下进一步层叠不设置贯通孔并且不赋予导电性膏体的适当数目的玻璃陶瓷薄片。

[0070]

接下来,在温度60~90℃、压力80~120mpa的条件下对层叠的多个玻璃陶瓷薄片进行热间等静压处理,得到层叠块。

[0071]

接下来,利用切割机等切断层叠块,单片化为能够成为各个共模扼流圈1所具备的层叠体2的尺寸的层叠结构物。

[0072]

接下来,进行了单片化的层叠结构物在烧制炉中,在860~900℃的温度下烧制1~2小时,例如在880℃的温度下烧制1.5小时,得到层叠体2。

[0073]

优选通过将烧制后的层叠体2,或者烧制前的进行了单片化的层叠结构物与介质一起放入旋转桶机,并进行旋转,对棱线部分以及角部分实施倒圆、倒角。

[0074]

接下来,在层叠体2中的引出连接端部23~26的部位涂覆包含ag以及玻璃的导电性膏体。此时,调整为应该成为下面电极部13b、14b、15b以及16b及上面电极部13c、14c、15c以及16c的部分的面积为0.034μm2以下。接着,例如以800~820℃的温度烧焊导电性膏体,由此,形成用于端子电极13~16的基底膜。基底膜的厚度例如大约为5μm。接下来,通过电镀在基底膜上例如依次形成ni膜以及sn膜。这些ni膜以及sn膜的厚度例如分别为大约3μm以及大约3μm。

[0075]

如以上那样,完成图1所示的共模扼流圈1。

[0076]

如上述那样,通过具备当将第一线圈11的路径长度设为l1,并将第二线圈12的路径长度设为l2时,l1和l2的合计长度为3.4mm以下这样的第一特征、以及至少第一下面电极部13b、第二下面电极部14b、第三下面电极部15b以及第四下面电极部16b各自的面积为0.034μm2以下这样的第二特征,共模扼流圈1能够在较高的频带,使差模信号透过,并且抑制共模噪声成分。以下对为了确认该情况而实施的实验例进行说明。

[0077]

[实验例]

[0078]

如表1所示,准备改变了“第一线圈/sg1”、“第二线圈/sg2”、“第一线圈路径长度/l1”、“第二线圈路径长度/l2”以及“下面、上面的电极的面积”的样品1~19所涉及的共模扼流圈。此外,对于各样品的共模扼流圈所具备的层叠体的尺寸来说,长度方向尺寸l为0.65mm,宽度方向尺寸w为0.50mm,高度方向尺寸h为0.30mm。另外,在各样品的共模扼流圈中,使第一线圈导体以及第二线圈导体各自的线宽度为0.018mm。

[0079]

若参照图2进行说明,则在表1中,“第一线圈/sg1”是从第一线圈11中的第一线圈导体17分别到层叠体2的侧面7以及8及端面10的距离,“第二线圈/sg2”是从第二线圈12中的第二线圈导体18分别到侧面7以及8及端面9以及10的距离。在表1中,除了样品2、18之外,在样品1、3~17、19中,使sg1与sg2相互不同,但在这些样品1、3~17、19中,即使在sg1与sg2之差的绝对值最小的样品1、3、17、19中,sg1与sg2之差的绝对值也为0.020mm。另一方面,如上述那样,第一线圈导体17以及第二线圈导体18各自的线宽度为0.018mm。因此,在使sg1与

sg2相互不同的样品1、3~17、19中,如图3所示,在第一线圈导体17与第二线圈导体18之间,除了相互交叉的部分之外,没有相互重合的部分。

[0080]

另外,在表1中,“下面、上面的电极的面积”是图1所示的端子电极13~16中的第一下面电极部13b、第二下面电极部14b、第三下面电极部15b、第四下面电极部16b、第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c各自的面积。在各样品中,第一下面电极部13b、第二下面电极部14b、第三下面电极部15b、第四下面电极部16b、第一上面电极部13c、第二上面电极部14c、第三上面电极部15c以及第四上面电极部16c各自的面积相互相等。

[0081]

【表1】

[0082][0083]

对样品1~19所涉及的共模扼流圈求出共模成分的透过特性(scc21透过特性)以及差模成分的透过特性(sdd21透过特性)。

[0084]

在图5以及图6代表性地分别示出对样品8所涉及的共模扼流圈求出的scc21透过特性以及sdd21透过特性。

[0085]

根据图5以及图6所示的特性图,对样品8求出关于scc21透过特性的峰值位置以及在峰值位置的透过率(最小值)、及关于sdd21透过特性的20ghz、30ghz以及40ghz的各频率下的透过率。另外,通过相同的要领,也对样品1~7以及9~19求出关于scc21透过特性的峰值位置以及在峰值位置的透过率(最小值)、及关于sdd21透过特性的20ghz、30ghz以及40ghz的各频率下的透过率。这些结果如表1所示。

[0086]

另外,在表1示出基于“第一线圈路径长度/l1”以及“第二线圈路径长度/l2”计算出的“线圈路径长度的合计/l1+l2”。

[0087]

参照表1,根据“线圈路径长度的合计l1+l2”为3.4mm以下的样品4~19,在scc21透过特性中,能够使透过特性为最小的频率(峰值位置)在24.6ghz以上。与此相对,在“线圈路径长度的合计l1+l2”超过3.4mm的样品1~3中,scc21透过特性的峰值位置低于24.6ghz,为24.5ghz以下。

[0088]

在上述的“线圈路径长度的合计l1+l2”为3.4mm以下的样品4~19中不满足“下面、上面的电极的面积”为0.034μm2以下的条件的样品13中,scc21透过特性的峰值位置为24.6ghz。

[0089]

与此相对,在“线圈路径长度的合计l1+l2”为3.4mm以下,并且“下面、上面的电极的面积”为0.034μm2以下的样品4~12、14~19中,能够使scc21透过特性的峰值位置为25ghz以上的例如27.9ghz以上。另外,能够使在scc21透过特性的峰值位置的透过率为-24db以下的例如-24.7db以下。

[0090]

接下来,若关注sdd21透过特性,则在满足“线圈路径长度的合计l1+l2”为3.4mm以下,并且“下面、上面的电极的面积”为0.034μm2以下的条件的样品4~12、14~19中,除了样品18之外,能够使20ghz下的透过特性为-0.71db以上,使30ghz下的透过特性为-1.81db以上,并使40ghz下的透过特性为-3.09db以上,可知差模的信号的衰减较小,能够使其有效地透过。

[0091]

此外,样品18由于“第一线圈/sg1”以及“第二线圈/sg2”均为0.105mm,所以存在许多第一线圈导体17与第二线圈导体18相互重合的部分,第一线圈11与第二线圈12之间的杂散电容增大,所以20ghz下的sdd21透过特性为-1.23db,30ghz下的sdd21透过特性为-2.80db,40ghz下的sdd21透过特性为-4.11db,而推测为衰减比较大。

[0092]

以上,与图示的实施方式相关联地对该发明进行了说明,但能够在该发明的范围内,实现其它各种变形例。

[0093]

例如,也可以将第一线圈以及第二线圈的至少一方所具备的一个线圈导体分割为两个部分,分割后的第一部分以及第二部分分别沿着非导电体层间的相互不同的第一界面以及第二界面配置,并通过通孔导体连接第一部分与第二部分。该情况下,作为线圈的路径长度的一部分的线圈导体的路径长度为将线圈导体的第一部分、通孔导体以及线圈导体的第二部分加在一起的状态下的路径长度即可。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1