半导体器件的制作方法

1.本公开涉及半导体器件。

背景技术:

2.作为一种用于增大半导体器件的密度的按比例缩放(scaling)技术,已经提出多栅极晶体管,其中鳍型或纳米线型多沟道有源图案(或硅主体)形成在衬底上并且栅极形成在多沟道有源图案的表面上。

3.由于多栅极晶体管使用三维(3d)沟道,所以能够促进按比例缩放。此外,能够在不增大多栅极晶体管的栅极长度的情况下增强电流控制能力。此外,能够有效地抑制短沟道效应(sce),即沟道区的电位受漏极电压影响的现象。然而,可能难以降低或调制包括p型金属氧化物半导体(pmos)和n型金属氧化物半导体(nmos)两者的多栅极晶体管的阈值电压,因为需要具有适当厚度的适合的p型功函数膜和适合的n型功函数膜,而这些功函数膜的厚度减小已经达到其极限,并且在这些多栅极晶体管的每个中具有有限的空间用于厚金属膜沉积。

技术实现要素:

4.本公开的实施方式提供一种能够降低或调制晶体管的阈值电压的半导体器件。

5.本公开的实施方式还提供一种制造半导体器件的方法,该半导体器件能够降低或调制晶体管的阈值电压。

6.根据本公开的一实施方式,提供一种半导体器件,该半导体器件包括:第一有源图案和第二有源图案,设置在衬底上并彼此相邻;场绝缘膜,设置在衬底上,在第一有源图案和第二有源图案之间,并与第一有源图案和第二有源图案直接接触;与第一有源图案交叉的第一栅极结构,在衬底上;以及与第二有源图案交叉的第二栅极结构,在衬底上,其中第一栅极结构包括在第一有源图案上的第一栅极绝缘膜、在第一栅极绝缘膜上的第一上插入膜以及在第一上插入膜上并与第一上插入膜接触的第一上导电膜,第二栅极结构包括在第二有源图案上的第二栅极绝缘膜、在第二栅极绝缘膜上的第二上插入膜以及在第二上插入膜上并与第二上插入膜接触的第二上导电膜,第一上插入膜和第二上插入膜中的每个包括铝氮化物膜,第一上导电膜和第二上导电膜中的每个包括铝。

7.根据本公开的一实施方式,提供一种半导体器件,该半导体器件包括:第一有源图案和第二有源图案,设置在衬底上并彼此相邻;场绝缘膜,设置在衬底上,在第一有源图案和第二有源图案之间,并与第一有源图案和第二有源图案直接接触;以及与第一有源图案和第二有源图案交叉的栅极结构,在场绝缘膜上,其中栅极结构包括栅极绝缘膜、下导电膜、铝氮化物膜和上导电膜,该栅极绝缘膜设置在第一有源图案和第二有源图案上,该下导电膜设置在栅极绝缘膜的在第一有源图案上的部分上并在场绝缘膜的顶表面上限定台阶,该铝氮化物膜设置在下导电膜上、跨越第一有源图案和第二有源图案,该上导电膜设置在铝氮化物膜上、跨越第一有源图案和第二有源图案并包括铝。

8.根据本公开的一实施方式,提供一种半导体器件,该半导体器件包括:设置在衬底上的第一有源图案,第一有源图案包括第一下图案以及与第一下图案分隔开的第一片状图案;设置在衬底上的第二有源图案,第二有源图案包括与第一下图案相邻的第二下图案以及与第二下图案分隔开的第二片状图案;场绝缘膜,设置在第一有源图案和第二有源图案之间并与第一有源图案和第二有源图案直接接触;以及栅极结构,在场绝缘膜上围绕第一片状图案和第二片状图案,其中栅极结构包括围绕第一片状图案和第二片状图案的栅极绝缘膜、在栅极绝缘膜上的下导电膜、在下导电膜上的铝氮化物膜、以及在铝氮化物膜上的上导电膜,下导电膜围绕第一片状图案并且不沿着第二片状图案的周界形成。

9.根据本公开的一实施方式,提供一种半导体器件,该半导体器件包括设置在衬底的第一区域中的第一有源图案、设置在衬底的第二区域中的第二有源图案、设置在第一有源图案上的第一栅极结构、以及设置在第二有源图案上的第二栅极结构,其中第一栅极结构包括在第一有源图案上的第一栅极绝缘膜以及在第一栅极绝缘膜上并与第一栅极绝缘膜接触的第一铝氮化物膜,第二栅极结构包括在第二有源图案上的第二栅极绝缘膜、以及在第二栅极绝缘膜上并与第二栅极绝缘膜接触的第二铝氮化物膜,第一铝氮化物膜的厚度不同于第二铝氮化物膜的厚度。

10.根据本公开的一实施方式,提供一种半导体器件,该半导体器件包括:设置在衬底上的第一有源图案,第一有源图案包括第一下图案以及与第一下图案分隔开的第一片状图案;设置在衬底上的第二有源图案,第二有源图案包括与第一下图案相邻的第二下图案、以及与第二下图案分隔开的第二片状图案;场绝缘膜,设置在第一下图案和第二下图案之间并与第一下图案和第二下图案直接接触;以及设置在场绝缘膜上的栅极结构,栅极结构围绕第一片状图案和第二片状图案,其中栅极结构包括围绕第一片状图案和第二片状图案的栅极绝缘膜、与栅极绝缘膜接触的插入膜、在插入膜上的下导电膜、以及在下导电膜上的上导电膜,插入膜的厚度在第一片状图案上比在第二片状图案上更大,插入膜包括铝氮化物膜,上导电膜包括铝。

附图说明

11.通过参照附图详细描述本公开的实施方式,本公开的以上和其它的方面以及特征将变得更加明显,附图中:

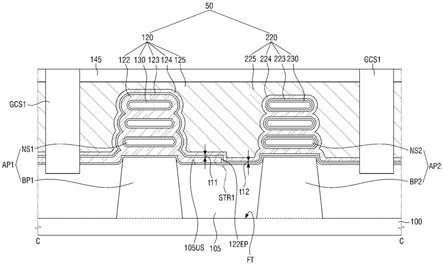

12.图1是根据本公开的一实施方式的半导体器件的布局图;

13.图2a和图2b是沿着图1的线a-a截取的截面图;

14.图3a和图3b是沿着图1的线b-b截取的截面图;

15.图4a和图4b是沿着图1的线c-c截取的截面图;

16.图5是根据本公开的一实施方式的半导体器件的截面图;

17.图6至图8是图5的部分p的放大截面图;

18.图9是根据本公开的一实施方式的半导体器件的截面图;

19.图10是根据本公开的一实施方式的半导体器件的截面图;

20.图11是根据本公开的一实施方式的半导体器件的截面图;

21.图12是根据本公开的一实施方式的半导体器件的截面图;

22.图13是根据本公开的一实施方式的半导体器件的截面图;

23.图14是根据本公开的一实施方式的半导体器件的截面图;

24.图15是根据本公开的一实施方式的半导体器件的截面图;

25.图16是根据本公开的一实施方式的半导体器件的布局图;

26.图17是沿着图16的线d-d截取的截面图;

27.图18是根据本公开的一实施方式的半导体器件的布局图;

28.图19是沿着图18的线e-e截取的截面图;

29.图20和图21是沿着图18的线f-f截取的截面图;以及

30.图22至图24是示出根据本公开的一实施方式的制造半导体器件的方法的截面图。

31.由于图1-图24中的附图旨在用于说明的目的,所以附图中的元件未必按比例绘制。例如,为了清楚的目的,元件中的一些可以被放大或夸大。

具体实施方式

32.在附图中,作为包括鳍型沟道区的鳍型晶体管的鳍式场效应晶体管(finfet)或者包括纳米线或纳米片的晶体管作为根据本公开的一实施方式的示范性半导体器件被示出,但是本公开不限于此。例如,本公开还可以适用于基于二维(2d)材料的场效应晶体管(fet)及其异质结构。

33.根据本公开的一实施方式的半导体器件可以包括隧穿fet(tfet)或三维(3d)晶体管。根据本公开的一实施方式的半导体器件可以包括双极结型晶体管(bjt)或横向扩散金属氧化物半导体(ldmos)晶体管。

34.图1是根据本公开的一实施方式的半导体器件的布局图。图2a和图2b是沿着图1的线a-a截取的截面图。图3a和图3b是沿着图1的线b-b截取的截面图。图4a和图4b是沿着图1的线c-c截取的截面图。

35.除了图2a所示的结构之外,图2b还示出第一源极/漏极接触180,并且除了图3a所示的结构之外,图3b还示出第二源极/漏极接触280。

36.参照图1至图4b,半导体器件可以包括第一有源图案ap1、第二有源图案ap2、第一栅极结构50和第一栅极切割结构gcs1。

37.衬底100可以是体硅(si)衬底或绝缘体上硅(soi)衬底。可选地,衬底100可以是硅(si)衬底或者可以包括另外的材料,诸如例如硅锗(sige)、绝缘体上sige(sgoi)、锑化铟(insb)、铅碲(pbte)化合物、砷化铟(inas)、磷化铟(inp)、砷化镓(gaas)或锑化镓(gasb),但是本公开不限于此。此外,衬底100可以包括一个或更多个半导体层或结构,并可以包括半导体器件的有源或可操作部分。

38.第一有源图案ap1和第二有源图案ap2可以设置在衬底100上。第一有源图案ap1和第二有源图案ap2可以在第二方向d2上延伸,并可以在第一方向d1上彼此相邻。例如,第一有源图案ap1和第二有源图案ap2可以设置为在第一方向d1上彼此间隔开。第一方向d1可以是与第二方向d2交叉的方向。

39.第一有源图案ap1可以是用于形成p型金属氧化物半导体(pmos)晶体管的区域,第二有源图案ap2可以是用于形成n型金属氧化物半导体(nmos)晶体管的区域。换言之,第一有源图案ap1可以设置在pmos区域中,第二有源图案ap2可以设置在nmos区域中。第一有源图案ap1可以包括pmos晶体管的沟道区,第二有源图案ap2可以包括nmos晶体管的沟道区。

40.在本公开的一实施方式中,第一有源图案ap1和第二有源图案ap2可以是包括在逻辑区中的有源区。第一有源图案ap1和第二有源图案ap2可以是包括在单个标准单元中的有源区。

41.在本公开的一实施方式中,第一有源图案ap1和第二有源图案ap2可以是包括在静态随机存取存储器(sram)区域中的有源区。第一有源图案ap1可以是用于形成sram的上拉晶体管的区域,第二有源图案ap2可以是用于形成sram的下拉晶体管或传输晶体管的区域。例如,包括第一有源图案ap1的上拉晶体管可以是pmos晶体管,包括第二有源图案ap2的下拉晶体管可以是nmos晶体管。然而,本公开不限于此。

42.第一有源图案ap1可以包括第一下图案bp1和多个第一片状图案ns1。第二有源图案ap2可以包括第二下图案bp2和多个第二片状图案ns2。

43.第一下图案bp1和第二下图案bp2可以从衬底100突出,并可以在第二方向d2上延伸。例如,第一下图案bp1和第二下图案bp2可以通过部分地去除衬底100的上部来形成,因此可以与衬底100一体地形成,但是本公开不限于此。

44.第一下图案bp1和第二下图案bp2可以在第一方向d1上彼此间隔开,并可以通过在第二方向d2上延伸的鳍沟槽ft分隔开。

45.第一片状图案ns1可以设置在第一下图案bp1上,并可以在第三方向d3上与第一下图案bp1间隔开。

46.第二片状图案ns2可以设置在第二下图案bp2上,并可以在第三方向d3上与第二下图案bp2间隔开。

47.第一片状图案ns1可以在第三方向d3上依次布置,并可以在第三方向d3上彼此间隔开。第二片状图案ns2可以在第三方向d3上依次布置,并可以在第三方向d3上彼此间隔开。这里,第三方向d3可以是与第一方向d1和第二方向d2两者交叉的方向。例如,第三方向d3可以是衬底100的厚度方向。

48.图2a和图2b示出三个第一片状图案ns1布置在第三方向d3上,但是本公开不限于此。例如,第一片状图案ns1的数量可以是2个或多于3个。类似地,图3a和图3b示出三个第二片状图案ns2布置在第三方向d3上,但是本公开不限于此。例如,第二片状图案ns2的数量可以是2个或多于3个。

49.第一下图案bp1和第二下图案bp2可以通过蚀刻衬底100的部分来形成,或者可以包括从衬底100生长的外延层。第一下图案bp1和第二下图案bp2可以包括元素半导体材料,诸如硅(si)或锗(ge)。此外,第一下图案bp1和第二下图案bp2可以包括化合物半导体,诸如例如iv-iv族化合物半导体或iii-v族化合物半导体。

50.iv-iv族化合物半导体可以是例如包含碳(c)、硅(si)、锗(ge)和锡(sn)中的至少两种的二元或三元化合物或通过用iv族元素对该二元或三元化合物掺杂获得的化合物。iv-iv族化合物半导体可以包括例如硅锗(sige)、硅碳化物(sic)或硅锗碳化物(sigec),但是本公开不限于此。

51.iii-v族化合物半导体可以是例如通过使作为iii族元素的铝(al)、镓(ga)和铟(in)中的至少一种和作为v族元素的磷(p)、砷(as)和锑(sb)中的一种结合而获得的二元、三元或四元化合物。iii-v族化合物半导体可以包括例如磷化镓(gap)、砷化镓(gaas)、砷化铟(inas)、磷化铟(inp)、锑化镓(gasb)、锑化铟(insb)或砷化铟镓(ingaas),但是本公开不

限于此。

52.第一片状图案ns1可以包括元素半导体材料(诸如硅(si)或锗(ge))、iv-iv族化合物半导体和/或iii-v族化合物半导体。第二片状图案ns2可以包括元素半导体材料(诸如硅(si)或锗(ge))、iv-iv族化合物半导体和/或iii-v族化合物半导体。

53.在本公开的一实施方式中,第一片状图案ns1和第二片状图案ns2可以包括与衬底100的材料或者第一下图案bp1和第二下图案bp2的材料基本上相同的材料。

54.第一片状图案ns1在第一方向d1上的宽度可以与第一下图案bp1在第一方向d1上的宽度成比例地增大或减小。第二片状图案ns2在第一方向d1上的宽度可以与第二下图案bp2在第一方向d1上的宽度成比例地增大或减小。

55.第一场绝缘膜105可以形成在衬底100上,并可以填充鳍沟槽ft的至少部分。

56.第一场绝缘膜105可以设置在衬底100上、在第一有源图案ap1和第二有源图案ap2之间,并可以与第一有源图案ap1和第二有源图案ap2直接接触。

57.第一场绝缘膜105可以与第一有源图案ap1和第二有源图案ap2直接接触,这意味着在第一有源图案ap1和第二有源图案ap2之间不存在能够用作晶体管的沟道区的其它有源图案。例如,第一有源图案ap1可以用作pmos晶体管的沟道区,第二有源图案ap2可以用作nmos晶体管的沟道区,第二有源图案ap2与第一有源图案ap1相邻而使第一场绝缘膜105插设在它们之间。

58.第一场绝缘膜105可以设置在第一下图案bp1和第二下图案bp2之间,并可以与第一下图案bp1和第二下图案bp2直接接触。

59.在本公开的一实施方式中,第一场绝缘膜105可以覆盖第一下图案bp1的限定鳍沟槽ft的侧壁的部分和/或第二下图案bp2的限定鳍沟槽ft的侧壁的部分。例如,第一下图案bp1的部分和/或第二下图案bp2的部分可以在第三方向d3上突出超过第一场绝缘膜105的顶表面105us。

60.在本公开的一实施方式中,第一场绝缘膜105可以覆盖第一下图案bp1的限定鳍沟槽ft的整个侧壁和第二下图案bp2的限定鳍沟槽ft的整个侧壁。例如,在第三方向d3上,第一下图案bp1和第二下图案bp2可以不突出超过第一场绝缘膜105的顶表面105us。

61.第一片状图案ns1和第二片状图案ns2可以定位得高于第一场绝缘膜105的顶表面105us。

62.第一场绝缘膜105可以包括例如氧化物膜、氮化物膜、氮氧化物膜或其组合。

63.参照图4a,第一场绝缘膜105可以填充鳍沟槽ft的至少部分。参照图4b,第一场绝缘膜105可以包括沿着鳍沟槽ft的侧壁和底表面延伸的场衬层105a以及设置在场衬层105a上的场填充膜105b。

64.第一栅极结构50可以形成在衬底100上,并可以设置在第一场绝缘膜105上。第一栅极结构50可以在第一方向d1上延伸,并可以与第一有源图案ap1、第二有源图案ap2和第一场绝缘膜105交叉。

65.第一栅极结构50可以与第一下图案bp1和第二下图案bp2交叉,并可以围绕每个第一片状图案ns1和每个第二片状图案ns2。

66.第一栅极结构50可以包括第一p型栅极结构120和第一n型栅极结构220。第一p型栅极结构120和第一n型栅极结构220可以彼此直接接触。

67.第一p型栅极结构120可以形成在第一有源图案ap1上,并可以与第一有源图案ap1交叉。第一p型栅极结构120可以包括p型栅电极。

68.第一p型栅极结构120可以与第一下图案bp1交叉,并可以围绕每个第一片状图案ns1。

69.第一n型栅极结构220可以形成在第二有源图案ap2上,并可以与第二有源图案ap2交叉。第一n型栅极结构220可以包括n型栅电极。

70.第一n型栅极结构220可以与第二下图案bp2交叉,并可以围绕每个第二片状图案ns2。

71.第一p型晶体管10p可以被限定在第一p型栅极结构120和第一有源图案ap1彼此交叉的区域中,第一n型晶体管10n可以被限定在第一n型栅极结构220和第二有源图案ap2彼此交叉的区域中。此外,将描述的第一外延图案150可以被包括在第一p型晶体管10p的源极/漏极中,将描述的第二外延图案250可以被包括在第一n型晶体管10n的源极/漏极中。

72.由于第一p型栅极结构120在第一场绝缘膜105之上延伸,所以第一p型栅极结构120不仅与第一有源图案ap1重叠,而且与第一场绝缘膜105的部分重叠。由于第一n型栅极结构220在第一场绝缘膜105之上延伸,所以第一n型栅极结构220不仅与第二有源图案ap2重叠,而且与第一场绝缘膜105的部分重叠。第一p型栅极结构120和第一n型栅极结构220之间的界面可以位于第一场绝缘膜105的顶表面105us上。

73.第一栅极结构50可以包括第一栅极绝缘膜(130和230)、第一下导电膜122、第一上插入膜(123和223)、第一上导电膜(124和224)以及第一填充导电膜(125和225)。

74.第一p型栅极结构120可以包括第(1_1)栅极绝缘膜130、第一下导电膜122、第(1_1)上插入膜123、第(1_1)上导电膜124和第(1_1)填充导电膜125。第一n型栅极结构220可以包括第(1_2)栅极绝缘膜230、第(1_2)上插入膜223、第(1_2)上导电膜224和第(1_2)填充导电膜225。例如,第一下导电膜122可以在第一p型栅极结构120中形成在第(1_1)栅极绝缘膜130上,并且在第一n型栅极结构220中没有下导电膜。

75.第(1_1)栅极绝缘膜130可以设置在第一有源图案ap1上,并可以沿着第一场绝缘膜105的顶表面105us和第一下图案bp1的顶表面延伸。第(1_1)栅极绝缘膜130可以围绕每个第一片状图案ns1,并可以沿着第一片状图案ns1的周界设置。

76.第(1_2)栅极绝缘膜230可以设置在第二有源图案ap2上,并可以沿着第一场绝缘膜105的顶表面105us和第二下图案bp2的顶表面延伸。第(1_2)栅极绝缘膜230可以围绕每个第二片状图案ns2,并可以沿着第二片状图案ns2的周界设置。第(1_1)栅极绝缘膜130和第(1_2)栅极绝缘膜230可以与第一场绝缘膜105的顶表面105us直接接触。第(1_1)栅极绝缘膜130和第(1_2)栅极绝缘膜230可以形成在相同的水平上。这里,表述“在相同的水平上形成两个元件”表示这两个元件通过相同的制造工艺形成,并可以包括相同的材料。第一栅极绝缘膜(130和230)可以跨越第一有源图案ap1和第二有源图案ap2设置。

77.第(1_1)栅极绝缘膜130和第(1_2)栅极绝缘膜230可以包括硅氧化物(sio2)、硅氮氧化物(sion)、硅氮化物(si3n4)或具有比硅氧化物(sio2)的介电常数大的介电常数的高k材料。高k材料可以包括例如硼氮化物(bn)、铪氧化物(hfo2)、铪硅氧化物(hfsio4)、铪锆氧化物(hfzro4)、铪钽氧化物(hf2ta2o9)、铪铝氧化物(hfalo3)、镧氧化物(la2o3)、镧铝氧化物(laalo3)、锆氧化物(zro2)、锆硅氧化物(zrsio4)、钽氧化物(ta2o5)、钛氧化物(tio2)、钡锶

钛氧化物(basrti2o6)、钡钛氧化物(batio3)、锶钛氧化物(srtio3)、钇氧化物(y2o3)、锂氧化物(li2o)、铝氧化物(al2o3)、铅钪钽氧化物(pb(sc,ta)o3)、铅锌铌酸盐(pb(zn

1/3

nb

2/3

)o3)以及其组合中的至少一种。

78.图2a至图4b示出第(1_1)栅极绝缘膜130和第(1_2)栅极绝缘膜230是单层膜,但是本公开不限于此。可选地,如图19所示,第(1_1)栅极绝缘膜130和第(1_2)栅极绝缘膜230中的每个可以包括界面膜(图19的531)和在界面膜上的高k电介质膜(图19的532)。

79.第一下导电膜122可以设置在第一有源图案ap1上。第一下导电膜122可以形成在第(1_1)栅极绝缘膜130上,并可以设置在第一栅极绝缘膜(130和230)的在第一有源图案ap1上的部分上。第一下导电膜122可以围绕每个第一片状图案ns1,并可以沿着第一片状图案ns1的周界设置。第(1_1)栅极绝缘膜130可以插设在第一下导电膜122和每个第一片状图案ns1之间。

80.在本公开的一实施方式中,第一下导电膜122可以大体填充在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间。例如,当在第三方向d3上具有两个相邻的第一片状图案ns1(例如第(1_1)片状图案ns1和第(1_2)片状图案ns1)时,第一下导电膜122可以大体填充从第(1_1)片状图案ns1的顶表面到第(1_2)片状图案ns1的底表面的空间。例如,第一下导电膜122可以与在第(1_1)片状图案ns1的顶表面之上的第(1_1)栅极绝缘膜130直接接触并与在第(1_2)片状图案ns1的底表面之下的第(1_1)栅极绝缘膜130直接接触。

81.在本公开的一实施方式中,第一下导电膜122可以不完全填充在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间。

82.第一下导电膜122不设置在第二有源图案ap2上,并且不延伸到第二有源图案ap2。第一下导电膜122不形成在第(1_2)栅极绝缘膜230上,并且不设置在第一栅极绝缘膜(130和230)的在第二有源图案ap2上的部分上。第一下导电膜122不围绕每个第二片状图案ns2,并且不沿着第二片状图案ns2的周界形成。

83.第一下导电膜122可以包括在第一有源图案ap1和第二有源图案ap2之间设置在第一场绝缘膜105的顶表面105us上的端部122ep。例如,第一下导电膜122可以在第一有源图案ap1和第二有源图案ap2之间在第一场绝缘膜105的顶表面105us上限定第一台阶str1。第一台阶str1可以具有由第一下导电膜122的端部122ep形成的台阶形状。第一下导电膜122的端部122ep可以在第一方向d1上在第一有源图案ap1和第二有源图案ap2之间设置在第一场绝缘膜105的中心附近,但是本公开不限于此。例如,取决于电路设计和/或制造工艺,第一下导电膜122的端部122ep可以在与到第二下图案bp2相比更靠近第一下图案bp1的位置,或者在与到第一下图案bp1相比更靠近第二下图案bp2的位置。

84.第一p型栅极结构120包括第一下导电膜122,但是第一n型栅极结构220可以不包括第一下导电膜122。当第一p型栅极结构120和第一n型栅极结构220彼此直接接触时,第一p型栅极结构120和第一n型栅极结构220可以通过第一下导电膜122彼此区分开。例如,由于第一下导电膜122被包括在第一p型栅极结构120中但没有被包括在第一n型栅极结构220中,所以第一下导电膜122的端部122ep是第一p型栅极结构120的端部。第一p型栅极结构120和第一n型栅极结构220之间的界面可以位于第一下导电膜122的端部122ep处。由第一下导电膜122限定的第一台阶str1可以位于第一p型栅极结构120和第一n型栅极结构220之

间。

85.第一下导电膜122可以是例如用于控制功函数的p型功函数膜。第一下导电膜122可以包括例如钛氮化物(tin)、钽碳化物(tac)、钽氮化物(tan)、钛硅氮化物(tisin)、钽硅氮化物(tasin)和钽碳氮化物(tacn)中的至少一种。例如,第一下导电膜122可以包括钛氮化物(tin)。

86.第(1_1)上插入膜123可以设置在第一有源图案ap1上,并可以形成在第一下导电膜122上。

87.在第一下导电膜122大体填充在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间的情况下,第(1_1)上插入膜123可以沿着第一下导电膜122的外轮廓延伸。第(1_1)上插入膜123可以不形成在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间中,并可以不沿着第一片状图案ns1的周界形成。

88.第(1_2)上插入膜223可以设置在第二有源图案ap2上,并可以与第(1_1)上插入膜123直接接触。第(1_1)上插入膜123和第(1_2)上插入膜223可以形成在相同的水平上。第(1_2)上插入膜223可以形成在第(1_2)栅极绝缘膜230上。第(1_2)上插入膜223可以围绕每个第二片状图案ns2,并可以沿着第二片状图案ns2的周界设置。例如,第(1_2)栅极绝缘膜230可以插设在第(1_2)上插入膜223和每个第二片状图案ns2之间。

89.第一上插入膜(123和223)可以设置在第一下导电膜122上。例如,第一上插入膜(123和223)可以与第一下导电膜122直接接触。第一上插入膜(123和223)可以跨越第一有源图案ap1和第二有源图案ap2设置。

90.由于第一下导电膜122设置在第(1_1)上插入膜123和第(1_1)栅极绝缘膜130之间,所以第(1_1)上插入膜123可以不与第(1_1)栅极绝缘膜130接触。

91.第(1_2)上插入膜223可以与在第二有源图案ap2上的第(1_2)栅极绝缘膜230直接接触,并可以与围绕第二片状图案ns2的第(1_2)栅极绝缘膜230直接接触。

92.第(1_2)上插入膜223可以控制第(1_2)栅极绝缘膜230中的绝缘体中的偶极子,并可以由此控制功函数。例如,第(1_2)上插入膜223可以是n型偶极子层以控制功函数并因此调制nmos晶体管的阈值电压。第(1_1)上插入膜123可以防止将随后描述的第(1_1)上导电膜124扩散到第一下导电膜122中,并可以由此防止可能由第(1_1)上导电膜124引起的功函数的任何变化。例如,第(1_1)上导电膜124可以具有与第一下导电膜122的功函数类型不同的功函数类型。因此,第(1_1)上导电膜124扩散到第一下导电膜122中可能降低第一下导电膜122的功函数,然而,这可以通过插设在它们之间的第(1_1)上插入膜123来防止。

93.第一上插入膜(123和223)可以包括例如基于铝(al)的氮化物。例如,第一上插入膜(123和223)可以包括铝氮化物(aln)。也就是,第(1_1)上插入膜123和第(1_2)上插入膜223可以包括铝氮化物(aln)膜。

94.在本公开的一实施方式中,第(1_1)上插入膜123的厚度t11可以与第(1_2)上插入膜223的厚度t12相同。在本公开的一实施方式中,第(1_1)上插入膜123的厚度t11可以不同于第(1_2)上插入膜223的厚度t12。功函数将被控制的量可以取决于第(1_1)上插入膜123的厚度t11和第(1_2)上插入膜223的厚度t12而变化。

95.第(1_1)上导电膜124可以设置在第一有源图案ap1上。第(1_1)上导电膜124可以形成在第(1_1)上插入膜123上,并可以沿着第(1_1)上插入膜123的轮廓形成。

96.第(1_1)上导电膜124可以不形成在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间中。第(1_1)上导电膜124可以不沿着第一片状图案ns1的周界形成。

97.第(1_2)上导电膜224可以设置在第二有源图案ap2上,并可以与第(1_1)上导电膜124直接接触。第(1_2)上导电膜224可以形成在第(1_2)上插入膜223上。第(1_2)上导电膜224可以围绕每个第二片状图案ns2,并可以沿着第二片状图案ns2的周界设置。

98.在本公开的一实施方式中,第(1_2)上导电膜224可以大体填充在第二下图案bp2和第二片状图案ns2之间以及在第二片状图案ns2之间的空间。例如,当在第三方向d3上存在两个相邻的第二片状图案ns2(例如第(2_1)片状图案ns2和第(2_2)片状图案ns2)时,第(1_2)上导电膜224可以大体填充从第(2_1)片状图案ns2的顶表面到第(2_2)片状图案ns2的底表面的空间。例如,第(1_2)上导电膜224可以与在第(2_1)片状图案ns2的顶表面之上的第(1_2)上插入膜223直接接触,并与在第(2_2)片状图案ns2的底表面下面的第(1_2)上插入膜223直接接触。

99.在本公开的一实施方式中,第(1_2)上导电膜224可以不完全填充在第二下图案bp2和第二片状图案ns2之间以及在第二片状图案ns2之间的空间。

100.第一上导电膜(124和224)可以设置在第一上插入膜(123和223)上,并可以跨越第一有源图案ap1和第二有源图案ap2设置。例如,第(1_1)上导电膜124可以与第(1_1)上插入膜123直接接触,第(1_2)上导电膜224可以与第(1_2)上插入膜223直接接触。

101.第一上导电膜(124和224)可以是例如用于控制功函数的n型功函数膜。例如,第(1_2)上插入膜223(其可以是n型偶极子层)与第(1_2)上导电膜224(其可以是n型功函数膜)一起可以控制功函数,因此可以调制nmos晶体管的阈值电压。第一上导电膜(124和224)可以包括例如铝(al)。第一上导电膜(124和224)可以包括例如钛铝(tial)、钛铝氮化物(tialn)、钛铝碳化物(tialc)、钛铝碳氮化物(tialcn)、钽铝(taal)、钽铝碳化物(taalc)、钽铝氮化物(taaln)和钽铝碳氮化物(taalcn)中的至少一种。第(1_1)上导电膜124和第(1_2)上导电膜224可以形成在相同的水平上。

102.第一填充导电膜(125和225)可以设置在第一上导电膜(124和224)上,并可以跨越第一有源图案ap1和第二有源图案ap2设置。例如,第(1_1)填充导电膜125和第(1_2)填充导电膜225可以分别设置在第(1_1)上导电膜124和第(1_2)上导电膜224上。例如,第一填充导电膜(125和225)可以填充由第一上导电膜(124和224)围绕的空间。第(1_1)填充导电膜125可以设置在第一有源图案ap1上。第(1_2)填充导电膜225可以设置在第二有源图案ap2上。

103.第一填充导电膜(125和225)可以包括例如钨(w)、铝(al)、钴(co)、铜(cu)、钌(ru)、镍(ni)、铂(pt)、镍铂(ni-pt)、钛(ti)和钛氮化物(tin)中的至少一种。第(1_1)填充导电膜125和第(1_2)填充导电膜225可以形成在相同的水平上。

104.在本公开的一实施方式中,在第一上导电膜(124和224)形成为相对厚的情况下,第(1_1)填充导电膜125可以不设置于在第三方向d3上与第一有源图案ap1重叠的区域中。第(1_1)填充导电膜125可以沉积于在第三方向d3上与第一场绝缘膜105重叠的区域中。

105.第一外延图案150可以设置在第一下图案bp1上。第一外延图案150可以设置在第一p型栅极结构120的至少一侧,并可以连接到第一片状图案ns1。

106.第二外延图案250可以设置在第二下图案bp2上。第二外延图案250可以设置在第

一n型栅极结构220的至少一侧,并可以连接到第二片状图案ns2。

107.第一外延图案150可以被包括在使用第一片状图案ns1作为沟道区的第一p型晶体管10p的源极/漏极中。第二外延图案250可以被包括在使用第二片状图案ns2作为沟道区的第一n型晶体管10n的源极/漏极中。第一外延图案150可以电连接到第一片状图案ns1和第一下图案bp1,并可以通过第(1_1)栅极绝缘膜130和将描述的第一栅极间隔物140而与第一p型栅极结构120电绝缘。第二外延图案250可以电连接到第二片状图案ns2和第二下图案bp2,并可以通过第(1_2)栅极绝缘膜230和将描述的第一栅极间隔物140而与第一n型栅极结构220电绝缘。

108.参照图2b,第一源极/漏极接触180可以设置在第一外延图案150上,并可以包括第一接触阻挡膜181和第一接触填充膜182。第一金属硅化物膜185可以进一步设置在第一源极/漏极接触180和第一外延图案150之间以减小接触电阻。

109.参照图3b,第二源极/漏极接触280可以设置在第二外延图案250上,并可以包括第二接触阻挡膜281和第二接触填充膜282。第二金属硅化物膜285可以进一步设置在第二源极/漏极接触280和第二外延图案250之间以减小接触电阻。

110.第一源极/漏极接触180的部分可以被插入在第一外延图案150中。第二源极/漏极接触280的部分可以被插入在第二外延图案250中。第一源极/漏极接触180的底表面可以位于最下面的第一片状图案ns1的顶表面和最上面的第一片状图案ns1的底表面之间。第二源极/漏极接触280的底表面可以位于最下面的第二片状图案ns2的顶表面和最上面的第二片状图案ns2的底表面之间。然而,本公开不限于此。

111.第一接触阻挡膜181和第二接触阻挡膜281可以包括例如钽(ta)、钽氮化物(tan)、钛(ti)、钛氮化物(tin)、钌(ru)、钴(co)、镍(ni)、镍硼化物(nib)、钨(w)、钨氮化物(wn)、钨碳氮化物(wcn)、锆(zr)、锆氮化物(zrn)、钒(v)、钒氮化物(vn)、铌(nb)、铌氮化物(nbn)、铂(pt)、铱(ir)、铑(rh)和二维(2d)材料中的至少一种。2d材料可以是金属材料和/或半导体材料,并可以包括2d同素异形体或2d化合物。例如,2d材料可以包括例如石墨烯、二硫化钼(mos2)、二硒化钼(mose2)、二硒化钨(wse2)和二硫化钨(ws2)中的至少一种,但是本公开不限于此。也就是,2d材料的类型没有被特别限制。第一接触填充膜182和第二接触填充膜282可以包括例如铝(al)、钨(w)、钴(co)、钌(ru)、银(ag)、金(au)、锰(mn)和钼(mo)中的至少一种。

112.第一金属硅化物膜185和第二金属硅化物膜285可以包括金属硅化物。

113.在本公开的一实施方式中,与图2b和图3b所示的不同,第一源极/漏极接触180和第二源极/漏极接触280可以分别不包括第一接触阻挡膜181和第二接触阻挡膜281。

114.在本公开的一实施方式中,与图2b和图3b所示的不同,第一源极/漏极接触180和第二源极/漏极接触280可以不分别插入在第一外延图案150和第二外延图案250中。例如,第一源极/漏极接触180和第二源极/漏极接触280可以分别沉积在第一外延图案150的顶表面和第二外延图案250的顶表面上,而不分别插入到第一外延图案150和第二外延图案250中,并且第一金属硅化物膜185和第二金属硅化物膜285可以分别设置在其界面处。

115.第一栅极间隔物140可以设置在第一栅极结构50的侧壁上。例如,第一栅极间隔物140可以设置在第一p型栅极结构120的侧壁和第一n型栅极结构220的侧壁上。

116.参照图3a和图3b,设置在第二下图案bp2上的第一栅极间隔物140可以包括第一外

间隔物141和第一内间隔物142。第一内间隔物142可以设置于在第三方向d3上彼此相邻的第二片状图案ns2之间以及在最下面的第二片状图案ns2与衬底100之间。参照图2a和图2b,设置在第一下图案bp1上的第一栅极间隔物140可以包括第一外间隔物141,但是可以不包括第一内间隔物142。

117.在本公开的一实施方式中,设置在第一下图案bp1上的第一栅极间隔物140和设置在第二下图案bp2上的第一栅极间隔物140都可以包括第一外间隔物141和第一内间隔物142。在本公开的一实施方式中,设置在第一下图案bp1上的第一栅极间隔物140和设置在第二下图案bp2上的第一栅极间隔物140都可以仅包括第一外间隔物141,但是可以不包括第一内间隔物142。

118.第一外间隔物141和第一内间隔物142可以每个包括例如硅氮化物(si3n4)、硅氮氧化物(sion)、硅氧化物(sio2)、硅氧碳氮化物(siocn)、硅硼氮化物(sibn)、硅氧硼氮化物(siobn)、硅碳氧化物(sioc)以及其组合中的至少一种。在本公开的一实施方式中,第一外间隔物141和第一内间隔物142可以包括相同的材料。可选地,第一外间隔物141和第一内间隔物142可以包括不同的材料。

119.第一栅极覆盖图案145可以设置在第一栅极结构50上以及在第一栅极间隔物140上。第一栅极覆盖图案145的顶表面可以位于与层间绝缘膜190的顶表面相同的平面上。

120.在本公开的一实施方式中,第一栅极覆盖图案145可以设置在第一栅极结构50上并且在第一栅极间隔物140之间。

121.第一栅极覆盖图案145可以包括例如硅氮化物(si3n4)、硅氮氧化物(sion)、硅氧化物(sio2)、硅碳氮化物(sicn)、硅氧碳氮化物(siocn)以及其组合中的至少一种。

122.一对第一栅极切割结构gcs1可以设置在衬底100上,并可以设置在第一场绝缘膜105上。

123.第一栅极切割结构gcs1可以设置为在第一方向d1上彼此间隔开,并可以在第二方向d2上延伸。第一有源图案ap1和第二有源图案ap2可以在第一方向d1上设置在一对相邻的第一栅极切割结构gcs1之间。例如,第一下图案bp1和第二下图案bp2可以在第一方向d1上设置在一对相邻的第一栅极切割结构gcs1之间。该对相邻的第一栅极切割结构gcs1可以在第二方向d2上与第一下图案bp1和第二下图案bp2平行地延伸。

124.第一栅极结构50可以在第一方向d1上设置在该对相邻的第一栅极切割结构gcs1之间。第一栅极切割结构gcs1可以将一对相邻的栅极结构在第一方向d1上分隔开。第一栅极结构50的短侧壁可以面对第一栅极切割结构gcs1的对应侧壁(见图1)。

125.第一栅极绝缘膜(130和230)不沿着每个第一栅极切割结构gcs1的侧壁延伸。

126.在本公开的一实施方式中,第一栅极切割结构gcs1可以沿着标准单元的边界设置。例如,第一栅极切割结构gcs1可以是标准单元分隔结构。在本公开的一实施方式中,第一栅极切割结构gcs1可以设置在sram区域中并可以是栅极分隔结构。

127.第一栅极切割结构gcs1可以包括例如硅氮化物(si3n4)、硅氮氧化物(sion)、硅氧化物(sio2)、硅氧碳氮化物(siocn)、硅硼氮化物(sibn)、硅氧硼氮化物(siobn)、硅碳氧化物(sioc)、铝氧化物(al2o3)以及其组合中的至少一种。第一栅极切割结构gcs1被示出为单层膜,但是本公开不限于此。

128.第一栅极切割结构gcs1的顶表面可以位于与第一栅极覆盖图案145的顶表面的平

面相同的平面上,但是本公开不限于此。

129.第一栅极切割结构gcs1的底表面被示出为比在第一栅极绝缘膜(130和230)与第一场绝缘膜105之间的边界更靠近衬底100,但是本公开不限于此。例如,第一栅极切割结构gcs1可以在第三方向d3上延伸,使得第一栅极切割结构gcs1的底表面可以每个至少到达在第一场绝缘膜105之上的第一栅极绝缘膜(130和230)的顶表面,以将一对相邻的栅极结构在第一方向d1上分隔开。

130.层间绝缘膜190可以设置在第一外延图案150和第二外延图案250上。层间绝缘膜190可以包括例如硅氧化物(sio2)、硅氮化物(si3n4)、硅氮氧化物(sion)、可流动的氧化物(fox)、东燃硅氮烷(tosz)、非掺杂的硅酸盐玻璃(usg)、硼硅酸盐玻璃(bsg)、磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)、等离子体增强原硅酸四乙酯(peteos)、氟化物硅酸盐玻璃(fsg)、掺碳的硅氧化物(cdo)、干凝胶、气凝胶、非晶氟化碳、有机硅酸盐玻璃(osg)、聚对二甲苯、双苯并环丁烯(bcb)、silk、聚酰亚胺、多孔聚合材料和/或其组合,但是本公开不限于此。

131.沿着第一栅极切割结构gcs1在第二方向d2上延伸的导线可以设置在第一栅极切割结构gcs1上。

132.图5是根据本公开的一实施方式的半导体器件的截面图。图6至图8是图5的部分p的放大截面图。为了便于说明,在下文将描述图5至图8的半导体器件,主要集中在与图1至图4b的半导体器件的差异上。

133.参照图5至图8,第一栅极结构50还可以包括第一下插入膜121,该第一下插入膜121设置在第一栅极绝缘膜(130和230)与第一下导电膜122之间。

134.第一下插入膜121可以设置在第一有源图案ap1上。第一下插入膜121可以形成在第(1_1)栅极绝缘膜130上,并可以设置在第一栅极绝缘膜(130和230)的在第一有源图案ap1上的部分上。例如,第一下插入膜121可以与第(1_1)栅极绝缘膜130直接接触。第一p型栅极结构120可以包括第(1_1)栅极绝缘膜130、第一下插入膜121、第一下导电膜122、第(1_1)上插入膜123、第(1_1)上导电膜124和第(1_1)填充导电膜125。

135.第一下插入膜121可以围绕每个第一片状图案ns1,并可以沿着第一片状图案ns1的周界设置。例如,第一下插入膜121可以插置在第(1_1)栅极绝缘膜130和第一下导电膜122之间。

136.第一下插入膜121不形成在第二有源图案ap2上,并且不延伸到第二有源图案ap2。第一下插入膜121不设置在第一栅极绝缘膜(130和230)的在第二有源图案ap2上的部分上。第一下插入膜121不围绕每个第二片状图案ns2,并且不沿着第二片状图案ns2的周界形成。

137.第一下插入膜121可以包括端部121ep,该端部121ep在第一有源图案ap1和第二有源图案ap2之间设置在第一场绝缘膜105的顶表面105us上。

138.参照图6,第一下插入膜121的端部121ep和第一下导电膜122的端部122ep在第一场绝缘膜105的顶表面105us上在第三方向d3上对准。换言之,第一下导电膜122不覆盖第一下插入膜121的端部121ep。

139.在本公开的一实施方式中,参照图7,第一下插入膜121的端部121ep可以比第一下导电膜122的端部122ep更靠近第二有源图案ap2。换言之,第一下插入膜121的端部121ep和第一下导电膜122的端部122ep在第一场绝缘膜105的顶表面105us上不对准。第一下导电膜

122不覆盖第一下插入膜121的端部121ep。

140.在本公开的一实施方式中,参照图8,第一下导电膜122的端部122ep可以比第一下插入膜121的端部121ep更靠近第二有源图案ap2。换言之,第一下插入膜121的端部121ep和第一下导电膜122的端部122ep在第一场绝缘膜105的顶表面105us上不对准。第一下导电膜122覆盖第一下插入膜121的端部121ep。第一下插入膜121的端部121ep和第一下导电膜122的端部122ep中的每个可以在第一方向d1上设置在第一场绝缘膜105的中心附近,但是本公开不限于此。例如,取决于电路设计和/或制造工艺,第一下插入膜121的端部121ep和第一下导电膜122的端部122ep中的每个可以单独地位于与到第二下图案bp2相比更靠近第一下图案bp1的位置或者与到第一下图案bp1相比更靠近第二下图案bp2的位置。

141.第一下插入膜121可以控制第(1_1)栅极绝缘膜130中的绝缘体中的偶极子,并可以由此控制功函数。例如,第一下插入膜121可以是p型偶极子层以控制功函数并因此调制pmos晶体管的阈值电压。例如,第一下插入膜121可以插设在第(1_1)栅极绝缘膜130和第一下导电膜122之间,并且与第一下导电膜122(其可以是p型功函数膜)一起可以控制功函数,因此可以调制pmos晶体管的阈值电压。

142.第一下插入膜121可以包括例如具有约1.5或更高的电负性的金属的氮化物或氧化物。考虑到所讨论的测量以及与特定量的测量相关的误差(即测量系统的限制),如这里所使用的术语“约”包括所陈述的值,并表示在由本领域普通技术人员确定的对于特定值的可接受的偏差范围内。例如,“约”可以表示在一个或更多个标准偏差内,或在所陈述的值的

±

30%、20%、10%、5%内。例如,第一下插入膜121可以包括钼氧化物(moo)、钼氮化物(mon)、铌氧化物(nbo)、铌氮化物(nbn)、镍氧化物(nio)、锡氧化物(sno2)和钛氧化物(tio2)中的至少一种。

143.图9是根据本公开的一实施方式的半导体器件的截面图。为了便于说明,在下文将描述图9的半导体器件,主要集中在与图1至图4b的半导体器件的差异上。

144.参照图9,第一下导电膜(122和222)可以包括围绕每个第一片状图案ns1的第(1_1)下导电膜122和围绕每个第二片状图案ns2的第(1_2)下导电膜222。

145.第一n型栅极结构220可以包括设置在第(1_2)栅极绝缘膜230和第(1_2)上插入膜223之间的第(1_2)下导电膜222。由于第(1_2)上插入膜223形成在第(1_2)下导电膜222上,所以第(1_2)上插入膜223可以不与第(1_2)栅极绝缘膜230接触。

146.在本公开的一实施方式中,第(1_1)下导电膜122的厚度t21可以大于第(1_2)下导电膜222的厚度t22。例如,第(1_2)下导电膜222的厚度t22可以相对薄,因此第(1_2)下导电膜222可以不控制功函数或不对功函数产生显著影响。此外,如果对功函数具有影响,则可以通过其它功函数膜进行补偿。例如,第(1_2)上插入膜223(其可以是n型偶极子层)与第(1_2)上导电膜224(其可以是n型功函数膜)一起可以控制功函数,因此可以调制nmos晶体管的阈值电压。

147.在第一p型栅极结构120和第一n型栅极结构220之间的界面可以是第一下导电膜(122和222)的厚度改变的位置。例如,该界面可以在第(1_1)下导电膜122的厚度t21被改变为第(1_2)下导电膜222的厚度t22的位置。第一下导电膜(122和222)可以在第一下导电膜(122和222)的厚度改变的位置限定第一台阶(图4a的str1)。

148.图10是根据本公开的一实施方式的半导体器件的截面图。图11是根据本公开的一

实施方式的半导体器件的截面图。图12是根据本公开的一实施方式的半导体器件的截面图。为了便于说明,在下文将描述图10至图12的半导体器件,主要集中在与图1至图4b的半导体器件的差异上。

149.参照图10至图12,每个半导体器件还可以包括第二栅极切割结构gcs2,该第二栅极切割结构gcs2在第一方向d1上设置在一对相邻的第一栅极切割结构gcs1之间。

150.第二栅极切割结构gcs2可以在第一有源图案ap1和第二有源图案ap2之间设置在第一场绝缘膜105上。

151.第一栅极结构50可以被第二栅极切割结构gcs2分成第一p型栅极结构120和第一n型栅极结构220。也就是,第二栅极切割结构gcs2可以设置在第一p型栅极结构120和第一n型栅极结构220之间。第二栅极切割结构gcs2的底表面被示出为比在第一栅极绝缘膜(130和230)与第一场绝缘膜105之间的边界更靠近衬底100,但是本公开不限于此。例如,第二栅极切割结构gcs2可以在第三方向d3上延伸,使得第二栅极切割结构gcs2的底表面可以至少到达在第一场绝缘膜105之上的第一栅极绝缘膜(130和230)的顶表面,以将第一p型栅极结构120和第一n型栅极结构220在第一方向d1上分隔开。

152.第二栅极切割结构gcs2可以包括例如硅氮化物(si3n4)、硅氮氧化物(sion)、硅氧化物(sio2)、硅氧碳氮化物(siocn)、硅硼氮化物(sibn)、硅氧硼氮化物(siobn)、硅碳氧化物(sioc)、铝氧化物(al2o3)以及其组合中的至少一种。第二栅极切割结构gcs2被示出为单层膜,但是本公开不限于此。

153.参照图10,第二栅极切割结构gcs2可以设置在与第一下导电膜122的端部(图4a的122ep)重叠的区域中。因此,与图4a的其对应物不同,第一p型栅极结构120不包括由第一下导电膜122形成的第一台阶str1。

154.在本公开的一实施方式中,参照图11,第二栅极切割结构gcs2可以设置在第一场绝缘膜105的其上没有设置第一下导电膜122的部分上。因此,第一p型栅极结构120包括由第一下导电膜122形成的第一台阶str1。此外,第一p型栅极结构120可以包括在第一栅极绝缘膜(130和230)与第一上插入膜(123和223)之间没有插置第一下导电膜122的部分。

155.在本公开的一实施方式中,参照图12,第二栅极切割结构gcs2可以将第一下导电膜122的在第一场绝缘膜105的顶表面105us上的部分分成两个区段。因此,第一n型栅极结构220可以包括与第二栅极切割结构gcs2接触的下导电膜图案122r。

156.图13是根据本公开的一实施方式的半导体器件的截面图。为了便于说明,在下文将描述图13的半导体器件,主要集中在与图1至图4b的半导体器件的差异上。

157.参照图13,第一栅极绝缘膜(130和230)、第一上插入膜(123和223)以及第一上导电膜(124和224)可以沿着每个第一栅极切割结构gcs1的侧壁延伸。

158.第一下导电膜122也可以沿着每个第一栅极切割结构gcs1的侧壁延伸。

159.图14是根据本公开的一实施方式的半导体器件的截面图。为了便于说明,在下文将描述图14的半导体器件,主要集中在与图1至图4b的半导体器件的差异上。

160.参照图14,第一栅极结构50可以包括依次堆叠在第一有源图案ap1和第二有源图案ap2上的第一栅极绝缘膜(130和230)、第一公共插入膜(126和226)、第一下导电膜(122和222)、第一上导电膜(124和224)以及第一填充导电膜(125和225)。

161.第一p型栅极结构120可以包括依次堆叠在第一有源图案ap1上的第(1_1)栅极绝

d截取的截面图。

173.图16的第一区域i中的第一有源图案ap1、第二有源图案ap2和第一栅极结构50可以与图1至图13中的任何一个的其相应的对应物基本上相同。此外,从图16的布局图截取的截面图可以与图4a至图13的截面图中的任何一个基本上相同。因此,在下文将主要参照图17来描述图16和图17的半导体器件,主要集中在图16的第二区域ii上。

174.参照图16和图17,半导体器件可以包括设置在第一区域i中的第一有源图案ap1、第二有源图案ap2和第一栅极结构50以及设置在第二区域ii中的第三有源图案ap3、第四有源图案ap4和第二栅极结构60。

175.衬底100可以包括第一区域i和第二区域ii。在本公开的一实施方式中,第一区域i和第二区域ii可以是逻辑区域。在本公开的一实施方式中,第一区域i和第二区域ii可以是sram区域。在本公开的一实施方式中,第一区域i和第二区域ii中的一个可以是逻辑区域,并且另一个区域可以是sram区域。

176.第三有源图案ap3和第四有源图案ap4可以设置在衬底100上。第三有源图案ap3和第四有源图案ap4可以在第五方向d5上延伸,并可以在第四方向d4上彼此相邻。第五方向d5可以是与第四方向d4交叉的方向。第三有源图案ap3可以是其中形成pmos的区域,第四有源图案ap4可以是其中形成nmos的区域。

177.第三有源图案ap3可以包括第三下图案bp3和多个第三片状图案ns3。第四有源图案ap4可以包括第四下图案bp4和多个第四片状图案ns4。第三下图案bp3可以在第四方向d4上与第四下图案bp4间隔开。第三下图案bp3和第四下图案bp4可以通过在第五方向d5上延伸的鳍沟槽ft而彼此分隔开。

178.第三片状图案ns3可以设置在第三下图案bp3上,并可以在第三方向d3上与第三下图案bp3间隔开。第四片状图案ns4可以设置在第四下图案bp4上,并可以在第三方向d3上与第四下图案bp4间隔开。第三下图案bp3和第四下图案bp4可以通过部分地去除衬底100的上部来形成,因此可以与衬底100一体地形成,但是本公开不限于此。

179.第二场绝缘膜106可以形成在衬底100上。第二场绝缘膜106可以在第三有源图案ap3和第四有源图案ap4之间设置在衬底100上,并可以与第三有源图案ap3和第四有源图案ap4直接接触。第二场绝缘膜106可以设置在第三下图案bp3和第四下图案bp4之间,并可以与第三下图案bp3和第四下图案bp4直接接触。第二场绝缘膜106可以包括例如氧化物膜、氮化物膜、氮氧化物膜或其组合。

180.第二栅极结构60可以形成在衬底100上,并可以设置在第二场绝缘膜106上。第二栅极结构60可以在第四方向d4上延伸,并可以与第三有源图案ap3、第四有源图案ap4和第二场绝缘膜106交叉。

181.第二栅极结构60可以与第三下图案bp3和第四下图案bp4交叉,并可以围绕每个第三片状图案ns3和每个第四片状图案ns4。

182.第二栅极结构60可以包括第二p型栅极结构320和第二n型栅极结构420。

183.第二p型栅极结构320可以形成在第三有源图案ap3上,并可以与第三有源图案ap3交叉。第二p型栅极结构320可以与第三下图案bp3交叉,并可以围绕每个第三片状图案ns3。

184.第二n型栅极结构420可以形成在第四有源图案ap4上,并可以与第四有源图案ap4交叉。第二n型栅极结构420可以与第四下图案bp4交叉,并可以围绕每个第四片状图案ns4。

185.第二p型晶体管20p可以被限定在第二p型栅极结构320和第三有源图案ap3彼此交叉的区域中,第二n型晶体管20n可以被限定在第二n型栅极结构420和第四有源图案ap4彼此交叉的区域中。此外,将描述的第三外延图案550可以被包括在第二p型晶体管20p的源极/漏极中,将描述的第四外延图案650可以被包括在第二n型晶体管20n的源极/漏极中。

186.第二栅极结构60可以包括第二栅极绝缘膜(330和430)、第二下导电膜322、第二上插入膜(323和423)、第二上导电膜(324和424)以及第二填充导电膜(325和425)。

187.第二p型栅极结构320可以包括第(2_1)栅极绝缘膜330、第二下导电膜322、第(2_1)上插入膜323、第(2_1)上导电膜324和第(2_1)填充导电膜325。第二n型栅极结构420可以包括第(2_2)栅极绝缘膜430、第(2_2)上插入膜423、第(2_2)上导电膜424和第(2_2)填充导电膜425。

188.第二p型栅极结构320和第二n型栅极结构420可以分别与图1至图4b的第一p型栅极结构120和第一n型栅极结构220基本上相同,因此将省略其详细描述。

189.第二下导电膜322可以包括端部322ep,该端部322ep在第三有源图案ap3和第四有源图案ap4之间设置在第二场绝缘膜106的顶表面106us上。第二下导电膜322可以在第三有源图案ap3和第四有源图案ap4之间在第二场绝缘膜106的顶表面106us上限定第二台阶str2。第二台阶str2可以具有由第二下导电膜322的端部322ep形成的台阶形状。第二下导电膜322的端部322ep可以在第一方向d1上在第三有源图案ap3和第四有源图案ap4之间设置在第二场绝缘膜106的中心附近,但是本公开不限于此。例如,取决于电路设计和/或制造工艺,第二下导电膜322的端部322ep可以在与到第四下图案bp4相比更靠近第三下图案bp3的位置,或者在与到第三下图案bp3相比更靠近第四下图案bp4的位置。

190.第二台阶str2可以位于第二p型栅极结构320和第二n型栅极结构420之间的界面上。

191.第二上插入膜(323和423)可以设置在第二下导电膜322上。例如,第二上插入膜(323和423)可以与第二下导电膜322直接接触。第二上插入膜(323和423)可以跨越第三有源图案ap3和第四有源图案ap4设置。

192.在本公开的一实施方式中,第(2_1)上插入膜323的厚度t13可以与第(2_2)上插入膜423的厚度t14相同。在本公开的一实施方式中,第(2_1)上插入膜323的厚度t13可以不同于第(2_2)上插入膜423的厚度t14。功函数将被控制的量可以取决于第(2_1)上插入膜323的厚度t13和第(2_2)上插入膜423的厚度t14而变化。

193.参照图4a和图17,第(2_2)上插入膜423的厚度t14可以不同于第(1_2)上插入膜223的厚度t12。

194.第二栅极覆盖图案345可以设置在第二栅极结构60上。

195.在本公开的一实施方式中,从图16的布局图截取的截面图可以与图5至图13的截面图中的一个基本上相同。在本公开的一实施方式中,第一有源图案ap1、第二有源图案ap2、第三有源图案ap3和第四有源图案ap4可以是以上参照图15描述的鳍型图案。

196.图18是根据本公开的一实施方式的半导体器件的布局图。图19是沿着图18的线e-e截取的截面图。图20和图21是沿着图18的线f-f截取的截面图。

197.参照图18至图21,半导体器件可以包括设置在第三区域iii中的第五有源图案ap5和第三栅极结构520以及设置在第四区域iv中的第六有源图案ap6和第四栅极结构620。

198.衬底100可以包括第三区域iii和第四区域iv。例如,第三区域iii可以是逻辑区域或sram区域。第四区域iv可以是输入/输出(i/o)区域。

199.第五有源图案ap5可以设置在衬底100上,并可以在第七方向d7上延伸。第五有源图案ap5可以包括第五下图案bp5和在第三方向d3上与第五下图案bp5间隔开的第五片状图案ns5。第五有源图案ap5可以与图1至图13中的任何一个的第一有源图案ap1或第二有源图案ap2基本上相同。

200.第三栅极结构520可以与第五有源图案ap5交叉,并可以在第六方向d6上延伸。第六方向d6可以是与第七方向d7交叉的方向。第三栅极结构520可以包括依次堆叠在第五有源图案ap5上的第三栅极绝缘膜530、第三上插入膜523、第三上导电膜524和第三上填充膜525。第三栅极绝缘膜530可以包括第三界面膜531和第三高k电介质膜532。第三界面膜531可以包括例如硅氧化物(sio2)膜,但是本公开不限于此。

201.第六有源图案ap6可以设置在衬底100上,并可以在第九方向d9上延伸。第六有源图案ap6可以是以上参照图15描述的鳍型图案。

202.参照图20,在本公开的一实施方式中,第六有源图案ap6可以是形成为单个半导体膜的鳍型图案。参照图21,在本公开的一实施方式中,第六有源图案ap6可以包括第六下图案bp6和半导体堆叠图案scp。半导体堆叠图案scp可以包括交替堆叠的第一半导体图案ssp1和第二半导体图案ssp2。例如,第一半导体图案ssp1可以包括与在第五片状图案ns5的形成期间形成的牺牲半导体图案的半导体材料相同的半导体材料。第二半导体图案ssp2可以包括与第五片状图案ns5的材料相同的材料。第一半导体图案ssp1可以包括相对于衬底100和第二半导体图案ssp2具有蚀刻选择性的材料。在本公开的一实施方式中,第一半导体图案ssp1可以包括sige,第二半导体图案ssp2可以包括si。

203.第四栅极结构620可以与第六有源图案ap6交叉,并可以在第八方向d8上延伸。第八方向d8可以是与第九方向d9交叉的方向。第四栅极结构620可以包括依次堆叠在第六有源图案ap6上的第四栅极绝缘膜630、第四上插入膜623、第四上导电膜624和第四上填充膜625。第四栅极绝缘膜630可以包括第四界面膜631和第四高k电介质膜632。第四界面膜631可以包括例如硅氧化物(sio2)膜,但是本公开不限于此。例如,第四界面膜631的厚度t42可以大于第三界面膜531的厚度t41。

204.第三栅极结构520和第四栅极结构620可以与图3至图4b的第一n型栅极结构220基本上相同,因此将省略其详细描述。

205.在本公开的一实施方式中,第三栅极结构520和第四栅极结构620还可以包括与图4b所示的第一下导电膜122对应的下导电膜和/或与图5所示的第一下插入膜121对应的下插入膜。

206.在本公开的一实施方式中,第四栅极结构620可以不包括包含铝氮化物(aln)膜的第四上插入膜623。

207.第二栅极间隔物540可以设置在第三栅极结构520的侧壁上。例如,第二栅极间隔物540可以包括第二外间隔物541和第二内间隔物542,但是本公开不限于此。

208.第三栅极间隔物640可以设置在第四栅极结构620的侧壁上。

209.第三栅极覆盖图案545可以设置在第三栅极结构520和第二栅极间隔物540上。第四栅极覆盖图案645可以设置在第四栅极结构620和第三栅极间隔物640上。

210.第三外延图案550可以设置在第五下图案bp5上,并可以设置在第三栅极结构520的至少一侧。第四外延图案650可以设置在第六有源图案ap6上,并可以设置在第四栅极结构620的至少一侧。第三外延图案550可以电连接到第五片状图案ns5和第五下图案bp5,并通过第三栅极绝缘膜530和第二栅极间隔物540而与第三栅极结构520电绝缘。第四外延图案650可以电连接到第六有源图案ap6(或第六下图案bp6和半导体堆叠图案scp),并通过第四栅极绝缘膜630和第三栅极间隔物640而与第四栅极结构620电绝缘。

211.图22至图24是示出根据本公开的一实施方式的制造半导体器件的方法的截面图。

212.具体地,图22至图24是沿着图1的线c-c截取的截面图。

213.参照图22,第一有源图案ap1和第二有源图案ap2可以在衬底100上形成为彼此间隔开。

214.第一有源图案ap1可以包括第一下图案bp1和第一片状图案ns1。第二有源图案ap2可以包括第二下图案bp2和第二片状图案ns2。

215.第一场绝缘膜105可以覆盖第一下图案bp1的限定鳍沟槽ft的侧壁的至少部分和第二下图案bp2的限定鳍沟槽ft的侧壁的至少部分。例如,第一下图案bp1的部分和/或第二下图案bp2的部分可以在第三方向d3上突出超过第一场绝缘膜105的顶表面105us。

216.初始栅极绝缘膜130p可以沿着第一场绝缘膜105的顶表面105us、第一下图案bp1的顶表面和第二下图案bp2的顶表面延伸。初始栅极绝缘膜130p可以沿着第一片状图案ns1的周界和沿着第二片状图案ns2的周界形成。

217.初始栅极绝缘膜130p可以对应于图4a的第一栅极绝缘膜(130和230)。

218.参照图23,可以在第一有源图案ap1上形成初始下插入膜121p和初始下导电膜122p。初始下插入膜121p和初始下导电膜122p可以形成在初始栅极绝缘膜130p上。初始下插入膜121p可以围绕每个第一片状图案ns1,并可以沿着第一片状图案ns1的周界设置。初始下导电膜122p可以形成在初始下插入膜121p上,并可以大体填充在第一下图案bp1和第一片状图案ns1之间以及在第一片状图案ns1之间的空间。

219.初始下插入膜121p和初始下导电膜122p可以不形成在第二有源图案ap2上。

220.初始下插入膜121p和初始下导电膜122p可以形成在第一有源图案ap1和第二有源图案ap2上。此后,可以去除初始下插入膜121p和初始下导电膜122p的在第二有源图案ap2上的部分。

221.在本公开的一实施方式中,初始下插入膜121p可以不形成在初始栅极绝缘膜130p和初始下导电膜122p之间。

222.初始下插入膜121p可以对应于图5的第一下插入膜121,初始下导电膜122p可以对应于图5的第一下导电膜122。

223.参照图24,在初始下导电膜122p的形成之后,可以在第一有源图案ap1和第二有源图案ap2上依次形成初始上插入膜123p和初始上导电膜124p。

224.初始上插入膜123p可以对应于图5的第一上插入膜(123和223),初始上导电膜124p可以对应于图5的第一上导电膜(124和224)。

225.此后,可以在初始上导电膜124p上形成初始填充导电膜,并且可以形成图5的第一栅极切割结构gcs1。结果,可以获得图5的第一栅极结构50。

226.总结详细描述,本领域技术人员将理解,在不背离如所附权利要求中限定的本公

开的精神和范围的情况下,可以对这里描述的特定实施方式进行许多变化和修改。因此,本公开的所公开的实施方式仅以一般性和描述性的含义来使用而不是为了限制的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1