一种具有异质结的结势垒肖特基器件的制作方法

1.本发明涉及肖特基器件领域,尤其是一种具有异质结的结势垒肖特基器件。

背景技术:

2.碳化硅(sic)因其宽的带隙、高的雪崩击穿电场、高的导热系数、高的工作温度、高的化学稳定性和耐辐照性而具有优异的电学性能。在高压、高频、大功率、高工作温度等方面具有巨大的应用潜力,目前已发展成为主要的宽带隙半导体材料之一。sic中肖特基势垒接触的首次研究早在20世纪60年代中期就有报道,sic肖特基势垒二极管(sbd)已成为一种很有前景的技术。为了实现p

‑

n结二极管的高阻塞电压与肖特基二极管的低正向压降的结合,baliga提出了sic二极管结构。

3.sic jbs二极管结合了肖特基二极管和pin功率二极管的优点,具有类比于肖特基二极管的低开启电压和高开关速度,以及类比于pin功率二极管的高击穿电压和低反向漏电流。但是,sic jbs二极管在调节正向导通特性和反向击穿特性的平衡时存在矛盾。例如,为了增加sic jbs二极管的正向导通电流,需要增加漂移区的掺杂浓度,但是,随着漂移区浓度的增大,sic jbs二极管的反向击穿电压会减小。所以,sic jbs二极管在增大正向电流的同时严重影响了sic jbs二极管的反向击穿特性。

技术实现要素:

4.本发明人针对上述问题及技术需求,提出了一种具有异质结的结势垒肖特基器件,本发明的技术方案如下:

5.一种具有异质结的结势垒肖特基器件,该结势垒肖特基器件包括从下至上依次层叠的阴极金属层、半导体衬底、半导体外延层以及阳极金属层,半导体衬底和半导体外延层均具有第一掺杂类型;半导体外延层的表面形成有第二掺杂类型的变掺杂区,变掺杂区内部设置有贯穿变掺杂区的表面至底部的具有第二掺杂类型的多晶硅层;多晶硅层及其外部的变掺杂区与半导体外延层的接触界面形成异质结,阳极金属层与半导体外延层的接触界面形成肖特基结。

6.其进一步的技术方案为,多晶硅层位于变掺杂区的中心。

7.其进一步的技术方案为,多晶硅层与变掺杂区在垂直方向上的深度相等,多晶硅层在水平方向上的宽度与多晶硅层外侧的变掺杂区的宽度相等。

8.其进一步的技术方案为,多晶硅层和变掺杂区在垂直方向上的深度均为1μm,多晶硅层在水平方向上的宽度与多晶硅层外侧的变掺杂区的宽度均为0.4μm。

9.其进一步的技术方案为,变掺杂区通过在半导体外延层的表面进行离子注入形成,且变掺杂区的掺杂浓度高于半导体外延层的掺杂浓度。

10.其进一步的技术方案为,半导体外延层的掺杂浓度为5

×

10

15

cm

‑3,变掺杂区的掺杂浓度为1

×

10

19

cm

‑3。

11.其进一步的技术方案为,当结势垒肖特基器件正向偏置时,电流通过异质结和肖

特基结流向半导体外延层形成的漂移区。

12.本发明的有益技术效果是:

13.本技术公开了一种具有异质结的结势垒肖特基器件,当该结势垒肖特基器件正向偏置时,电流通过异质结和肖特基结流向半导体外延层形成的漂移区,由于加入了多晶硅层,流过该区域的电流明显大于常规的sic jbs二极管,因此电流密度相对较大,电阻的相对值也会相对较低。由于半导体外延层整体的掺杂浓度不变,而且相同的变掺杂区同样可以夹断台面,使得肖特基势垒被屏蔽在高电场之外,所以,该结构的反向击穿特性不会受到严重影响,使得该结势垒肖特基器件的正向导通特性和反向击穿特性都较优。

附图说明

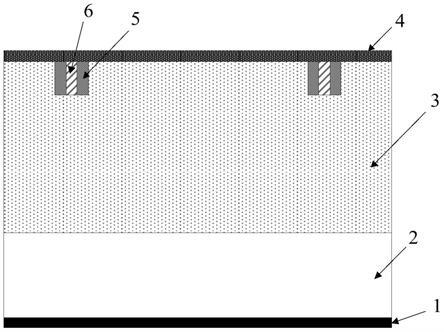

14.图1是本技术公开的具有异质结的结势垒肖特基器件的结构图。

具体实施方式

15.下面结合附图对本发明的具体实施方式做进一步说明。

16.本技术公开了一种具有异质结的结势垒肖特基器件,请参考图1,该结势垒肖特基器件包括从下至上依次层叠的阴极金属层1、半导体衬底2、半导体外延层3以及阳极金属层4,半导体衬底2和半导体外延层3均具有第一掺杂类型。半导体外延层3的表面形成有第二掺杂类型的变掺杂区5,变掺杂区5内部设置有贯穿变掺杂区5的表面至底部的具有第二掺杂类型的多晶硅层6。实际半导体外延层3的表面形成有两侧的两个变掺杂区5,两个变掺杂区5及其内部的多晶硅层6的结构相同。

17.可选的,多晶硅层6位于变掺杂区5的中心。多晶硅层6与变掺杂区5在垂直方向上的深度相等,多晶硅层6在水平方向上的宽度与多晶硅层6外侧的变掺杂区5的宽度相等。垂直方向是指层叠方向,水平方向是指每一层表面方向,多晶硅层6和变掺杂区5在水平方向上的剖面一般为规整结构,则多晶硅层6的宽度即为其径向尺寸,而多晶硅层6外侧的变掺杂区5的宽度即为变掺杂区5的外侧壁至多晶硅层6的外侧壁之间的距离。在一个实施例中,半导体衬底2的厚度为5μm,半导体外延层3的厚度为10μm,多晶硅层6和变掺杂区5在垂直方向上的深度均为1μm,多晶硅层在水平方向上的宽度与多晶硅层外侧的变掺杂区的宽度均为0.4μm。

18.半导体外延层3的掺杂浓度低于半导体衬底2的掺杂浓度,变掺杂区5通过在半导体外延层3的表面进行离子注入形成,且变掺杂区5的掺杂浓度高于半导体外延层3的掺杂浓度。在一个实施例中,变掺杂区5的掺杂浓度与半导体衬底2的掺杂浓度相等,但掺杂不同的离子类型。多晶硅层6通过沟槽刻蚀并沉积形成,多晶硅层6的掺杂浓度高于半导体外延层3的掺杂浓度但低于变掺杂区5的掺杂浓度。在一个实施例中,半导体衬底2的掺杂浓度为1

×

10

19

cm

‑3,半导体外延层3的掺杂浓度为5

×

10

15

cm

‑3,变掺杂区5的掺杂浓度为1

×

10

19

cm

‑3,多晶硅层6的掺杂浓度为5

×

10

18

cm

‑3。

19.在实际应用时,比较典型的,半导体衬底2和半导体外延层3均采用4h

‑

sic制成,且第一掺杂类型为n型,第二掺杂类型为p型,形成n+型4h

‑

sic衬底以及n

‑

型4h

‑

sic外延层。通过在n

‑

型4h

‑

sic外延层中注入p型离子可以得到p+型4h

‑

sic变掺杂区,然后在变掺杂区内制作p型多晶硅层。阴极金属层1采用金属镍,阳极金属层采用金属钛。

20.基于上述结构,多晶硅层6及其外部的变掺杂区5与半导体外延层2的接触界面形成异质结,阳极金属层4与半导体外延层3的接触界面形成肖特基结。异质结的开启电压非常小,当该结势垒肖特基器件正向偏置时,电流通过异质结和肖特基结流向半导体外延层形成的漂移区,由于加入了多晶硅层,流过该区域的电流明显大于常规的sic jbs二极管,因此电流密度相对较大,电阻的相对值也会相对较低。由于半导体外延层整体的掺杂浓度不变,而且相同的变掺杂区同样可以夹断台面,使得肖特基势垒被屏蔽在高电场之外,所以,该结构的反向击穿特性不会受到严重影响。

21.以上所述的仅是本技术的优选实施方式,本发明不限于以上实施例。可以理解,本领域技术人员在不脱离本发明的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1