一种MOS栅控晶闸管及其制造方法

一种mos栅控晶闸管及其制造方法

技术领域

1.本发明属于功率半导体技术领域,特别涉及一种mos栅控晶闸管及其制造方法。

背景技术:

2.功率半导体器件作为开关器件,可以应用于电力电子领域和脉冲功率领域两个方面。当应用于脉冲功率领域时,半导体开关器件常常与电容或电感储能电路相结合,从而产生瞬态电压或电流脉冲。为了满足脉冲功率的应用,开关器件需要具备极高的峰值电流能力和电流上升率(di/dt),同时要具备较高的电压上升率(dv/dt)抗性以保证其工作稳定性。

3.mos场控晶闸管(mos controlled thyristor,简称:mct)兼具mos器件和晶闸管器件的优点,电流密度大,导通功耗低,开启速度快,非常适合应用于脉冲功率领域。但在实际应用时也面临着问题。在利用电容储能方式产生脉冲电流时,储能电容充电速度较快,器件阳极电压上升率(dv/dt)很大。由于器件阳极

‑

栅极间寄生电容的存在,较高的电压变化率会在栅极

‑

阳极之间产生瞬时位移电流,并流过器件栅极通过阴极接地释放,当栅阴极之间寄生电阻不可忽略时,该位移电流会在栅极

‑

阴极间产生电压降,若此电压降超过器件阈值电压,器件将在没有外接栅压的条件下开启,器件误触发,进而影响器件在实际应用过程中的稳定性。

技术实现要素:

4.本发明所要解决的,就是针对上述问题,提出一种高dv/dt抗性的mos栅控晶闸管及其制造方法,以解决常规的mct器件在储能电容充电过程中遇到的误开启问题,从而提高器件和脉冲系统的可靠性。

5.为实现上述目的,本发明采用如下技术方案:

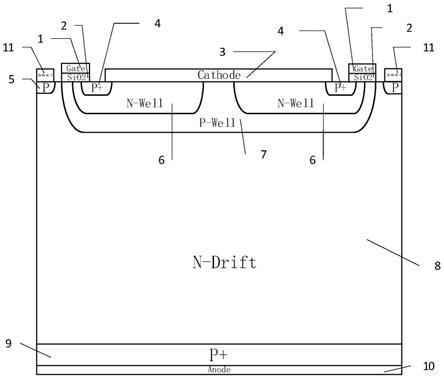

6.一种mos栅控晶闸管,如图2所示,其元胞结构包括从下至上依次层叠设置的阳极金属10、p型阳极区9、n型漂移区8;所述n型漂移区8上层具有以元胞垂直中线呈对称分布的p型阱区7,所述p型阱区7上层具有以元胞垂直中线呈对称分布的2个n型阱区6,所述n型阱区6上层具有p型阴极区4,且p型阴极区4位于n型阱区6远离元胞垂直中线的一侧,所述n型漂移区8上层两端靠近元胞边缘处还具有两个p型掺杂区5;所述元胞p型阱区7上表面两端具有以元胞垂直中线呈对称分布的两个栅氧化层2,所述栅氧化层2上层具有多晶硅栅极区1;所述p型阱区7上表面具有阴极金属区3,所述p型掺杂区5上表面具有第二阴极金属区11。所述p型阱区7和n型阱区6两端的上表面位于多晶硅栅极区1的下方,所述p型阴极区4的一部分位于多晶硅栅极区1下方,另一部分与阴极金属区3上表面接触。

7.具体的,所述第二阴极金属区11与多晶硅栅极1之间留有空隙,所述p型掺杂区5与p型阱区7之间留有空隙,所述第二阴极金属区11与多晶硅栅极1之间空隙要稍大于p型掺杂区5与p型阱区7之间空隙。

8.本发明的技术方案,主要是将传统的栅极结构缩短,从而减小了器件栅极通过栅

氧化层与衬底接触的面积,使栅阳极之间寄生电容明显减小;本发明通过引入第二阴极金属区11缓解了阻断状态下的栅极边缘的电场集中现象,同时通过在第二阴极金属区11下方设置p型掺杂区5,在改进器件dv/dt抗性的同时不牺牲器件的阻断特性。

9.还提供了一种mos栅控晶闸管的制造方法,包括以下步骤:

10.第一步:采用衬底硅片制造结终端,形成n型漂移区8;

11.第二步:采用离子注入和高温扩散推结工艺,在n型漂移区8底部形成p型阳极区9;

12.第三步:在n型漂移区8上表面生长二氧化硅,形成栅氧化层2,在栅氧化层2上表面淀积n型导电多晶硅形成多晶硅栅极区1;

13.第四步:采用离子注入和高温扩散推结工艺,在n型衬底上层形成p型阱区7;

14.第五步:采用离子注入和高温扩散推结工艺,在n型衬底上层两端形成p型掺杂区5,所述p型掺杂区5与p型阱区7不能有交叠部分;

15.第六步:采用离子注入和高温扩散推结工艺;在p型阱区7上层形成n型阱区6,所述n型阱区6关于元胞垂直中线呈对称分布,且两个n型阱区6中间没有交叠;

16.第七步:采用离子注入和高温扩散推结工艺,在两个n型阱区6上层形成p型阴极区4,所述p型阴极区4位于n型阱区6远离元胞垂直中线的一侧,且关于元胞垂直中线呈对称分布;

17.第八步:在n型漂移区8上表面淀积金属层,形成阴极金属区3,第二阴极金属区11,所述阴极金属区3位于元胞中间,两端分别与p型阴极区4上表面部分接触;所述第二阴极金属区11位于元胞两端,且在p型掺杂区5上层,同时沿器件横向方向的宽度不能超过p型掺杂区5沿器件横向方向的宽度。

18.第九步:在p型阳极区9下表面淀积金属层,形成阳极金属层10。

19.本发明的有益效果为,提供了一种具有较低栅阳电容,高dv/dt抗性的mos栅控晶闸管及其制造方法,解决了常规的mos栅控晶闸管在脉冲功率应用时储能电容充电过程中的误开启问题,同时本发明提供的制造方法与传统mct工艺相兼容。

附图说明

20.图1是常规mos栅控晶闸管的结构示意图;

21.图2是实施例中一种mos栅控晶闸管的结构示意图;

22.图3是为本发明提供的一种制作方法的流程示意图;

23.图4是实施例与常规mct器件击穿特性曲线对比示意图;

24.图5是实施例与常规mct器件栅阳极电容仿真实意图

25.图6是mct器件dv/dt抗性仿真电路示意图;

26.图7是dv/dt为37kv/us时实施例与常规mct器件dv/dt抗性仿真结果示意图;

27.图8是dv/dt为56kv/us时实施例与常规mct器件dv/dt抗性仿真结果示意图。

具体实施方式

28.下面结合附图,详细描述本发明的技术方案:

29.图1为常规mos栅控晶闸管的结构示意图,图2为本发明实施例中一种mos栅控晶闸管的结构示意图,两者均利用器件内部晶闸管导通获得高的电流上升率di/dt和峰值电流,

满足脉冲功率应用的条件。但是在实际应用中,由于栅极与阴极间寄生电阻的存在,使得器件栅极电压在高dv/dt和栅阳电容的耦合下升高,超过器件阈值电压从而使器件误开启,最终导致脉冲系统失效。理论分析表明,当栅阳电容减小时,器件通过dv/dt感生出的栅极电压就会减小,从而降低器件误开启的概率。

30.本发明与常规的mos栅控晶闸管相比,由于第二阴极和其下方p型掺杂区的引入,减小了器件栅极通过栅氧化层与衬底接触的面积,使得栅阳寄生电容明显减小。在脉冲功率应用时,储能电容充电过程中,在dv/dt的作用下产生的栅极电流就会减小,从而在栅阴极串联电阻上产生的压降减小,降低了器件栅极电压超过阈值电压造成误开启的可能性。因此本发明在不牺牲器件耐压的情况下,可以有效提高mct器件的dv/dt抗性。

31.图3为本发明提供的一种mos栅控晶闸管制作方法的流程示意图,图4表示的是本发明与常规mct器件击穿特性曲线对比示意图。从图中可以看到,本发明相比传统mct器件耐压不仅没有退化,还稍有增加,这也说明本发明的器件结构上的改变,不会牺牲mct阻断能力。

32.图5为实施例与常规mct器件栅阳极电容仿真实意图。本发明与常规mct器件元胞宽度均为100um,面积均为1cm2。从图中可以看到,当阳极施加20v电压时,传统mct栅阳极电容为32pf,而本发明栅阳极电容仅有4pf,本发明中的mct器件栅阳极寄生电容cga明显小于传统mct器件,降低幅度达87.5%,此结果充分说明了本发明明显减小了mct器件的栅阳极寄生电容cga.

33.图6是mct器件dv/dt抗性仿真电路示意图,选取的栅极

‑

阴极间寄生电阻rgk为100欧姆,充电电路寄生电阻r为5欧姆,充电电路寄生电感为20e

‑

9亨,阳极充电电压u0为2000v,且此电压远小于器件实际耐压,通过改变阳极充电时间来控制外部dv/dt的大小。图7是dv/dt为37kv/us时实施例与常规mct器件dv/dt抗性仿真结果示意图,图8是dv/dt为56kv/us时实施例与常规mct器件dv/dt抗性仿真结果示意图。dv/dt仿真结果表明,传统mct器件在dv/dt为37kv/us时即发生了误触发,而本发明中的mct在dv/dt达到56kv/us时还没有发生误触发现象,本发明中的mct器件相较于传统mct器件dv/dt抗性提高了约51%。因此,通过缩短传统mct结构栅极面积,并引入第二阴极及p型掺杂区,能够减小器件栅极通过栅氧化层与衬底接触的面积,从而减小器件栅极

‑

阳极之间的寄生电容,增强mct器件的dv/dt抗性,有效的解决了常规mos栅控晶闸管在脉冲功率应用时储能电容充电过程中的误开启问题,提升了器件和脉冲电路的稳定性。

34.以图2所示的器件结构示意图为例,其制作方法包括以下步骤:

35.第一步:采用衬底硅片制造结终端,形成n型漂移区8;

36.第二步:采用离子注入和高温扩散推结工艺,在n型漂移区8底部形成p型阳极区9;

37.第三步:在n型漂移区8上表面生长二氧化硅,形成栅氧化层2,在栅氧化层2上表面淀积n型导电多晶硅形成多晶硅栅极区1;

38.第四步:采用离子注入和高温扩散推结工艺,在n型衬底上层形成p型阱区7;

39.第五步:采用离子注入和高温扩散推结工艺,在n型衬底上层两端形成p型掺杂区5,所述p型掺杂区5与p型阱区7不能有交叠部分;

40.第六步:采用离子注入和高温扩散推结工艺;在p型阱区7上层形成n型阱区6,所述n型阱区6关于元胞垂直中线呈对称分布,且两个n型阱区6中间没有交叠;

41.第七步:采用离子注入和高温扩散推结工艺,在两个n型阱区6上层形成p型阴极区4,所述p型阴极区4位于n型阱区6远离元胞垂直中线的一侧,且关于元胞垂直中线呈对称分布;

42.第八步:在n型漂移区8上表面淀积金属层,形成阴极金属区3,第二阴极金属区11,所述阴极金属区3位于元胞中间,两端分别与p型阴极区4上表面部分接触;所述第二阴极金属区11位于元胞两端,且在p型掺杂区5上层,同时沿器件横向方向的宽度不能超过p型掺杂区5沿器件横向方向的宽度。

43.第九步:在p型阳极区9下表面淀积金属层,形成阳极金属层10。

44.应当指出的是,本发明中所提出的一种mos栅控晶闸管的制造方法与传统mos栅控晶闸管工艺能够互相兼容,仅需要额外增加一张掩模版进行p型掺杂区的注入,虽然成本稍有增加,但是能够带来相较于传统mos栅控晶闸管较大dv/dt抗性的提升,极大提高后期在应用过程中的稳定性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1