芯片连接器的制作方法

芯片连接器

【技术领域】

1.本发明涉及一种芯片连接器,尤其涉及一种芯片连接器中的导电端子的改良。

背景技术:

2.随着大数据、云计算、物联网等概念的蓬勃发展,几乎每个新产品都在谈高速传输应用。各应用模块均朝向高速方向发展,以实现前面提到的高速传输应用,用来连接各个模块之间的输入/输出接口当然亦需要高速传输。而作为电脑、服务器等核心部分的中央处理器则朝向更高速、接脚更多的方向发展,用来连接中央处理器与主机板之间的电连接器则不能成为信号传输的瓶颈。在高频信号传输时,信号损失较大,影响高频信号的传输。

3.cn107394448b揭示了一种可传输高频信号且端子具有多条导电路径的电连接器,包括:一绝缘本体,设有多个收容孔;多个端子,分别对应收容于所述收容孔中,每一端子具有:一基部;一弹性臂,自所述基部向上弯折延伸形成,所述弹性臂弯折形成一接触部,用于向上抵接所述对接元件;一第一抵接部,自所述接触部弯折延伸形成,所述第一抵接部包括自所述接触部向下朝远离所述基部弯折倾斜延伸形成的一第一弹性部和自第一弹性部向下靠近所述基部倾斜延伸形成的一第二弹性部;一开槽,贯穿所述接触部、所述第一弹性部和所述第二弹性部;一弯折臂,自所述基部下端弯折延伸形成,所述弯折臂弯折形成一导接部,用于导接所述电子元件,自所述导接部向上弯折延伸形成一第二抵接部,所述第一抵接部抵接所述第二抵接部。其通过开槽贯穿所述第一弹性部、所述第二弹性部和所述接触部,降低所述端子信号传输中的自感现象,避免相邻端子之间的串音,利于提高所述端子高速信号传输。然而,该电连接器结构,无法同时满足良好的机械性能及高频信号传输性能。

4.因此,确有必要对现有的芯片连接器进行改进。

技术实现要素:

5.本发明所要解决的技术问题在于提供一种芯片连接器,其能改善机械性能及电气性能。

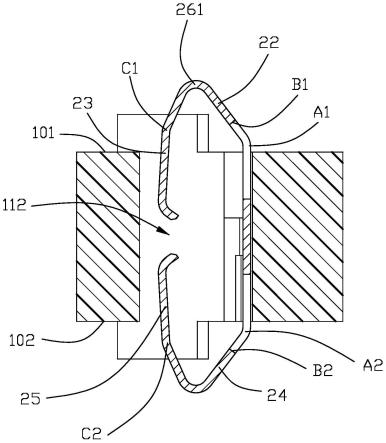

6.为解决上述技术问题,本发明采用以下技术方案:一种芯片连接器,包括本体及呈矩阵排列的若干端子,所述本体设有上表面、下表面及贯穿上下表面的端子孔,所述端子一一收容在对应的端子孔内,所述端子包括固定部、第一弹性部、自第一弹性臂向下弯折的第一抵接部,以及第二弹性部、自第二弹性臂向上弯折的第二抵接部;所述固定部设有固定在所述本体的干涉凸缘,所述第一弹性部具有第一接触部,所述第二弹性部具有第二接触部;所述第一、第二弹性部在受压时,所述第一、第二抵接部彼此电性连接于一起;所述第一弹性部包括自所述固定部向上延伸的第一竖直部、自第一竖直部倾斜延伸出所述本体上表面的第一倾斜部,所述第二弹性部包括自所述固定部向下延伸的第二竖直部、自第二竖直部倾斜延伸出下表面的第二倾斜部,所述端子在未受压的自由状态时,所述第一、第二竖直部彼此共面。

7.与现有技术相比,本发明芯片连接器的第一、第二弹性部分别设置共面的第一、第

二竖直部,可以提高机械性能及电气性能。

【附图说明】

8.图1为本发明芯片连接器的立体图。

9.图2为图1芯片连接器的俯视图,其中一个端子被拆除。

10.图3为图2中沿虚线a-a的剖视图。

11.图4为图3中端子受压后的剖视图。

12.图5为端子的立体图。

13.图6为图5另一角度的立体图。

14.图7为图5的侧视图。

【具体实施方式】

15.以下,将结合图1至图7介绍本发明芯片连接器的具体实施方式。

16.参图1-7所示,本发明为一种芯片连接器100,其收容芯片模组(未图示),用来在芯片模组与电路板(未图示)之间建立电性连接。所述芯片连接器100包括本体10及呈矩阵排列的若干端子20,如图1所示,在具体产品中,根据具体芯片模组的不同,端子数量也将不同,比如服务器中使用的芯片连接器,端子数量已经高达上千个,图1也仅显示其中的一部分。本体10一般由绝缘塑胶制成,其设有上表面101、下表面102及贯穿上下表面的端子孔11,端子20一一收容在对应的端子孔11内。

17.所述端子20包括固定部21、第一弹性部22、自第一弹性部22向下弯折的第一抵接部23,以及第二弹性部24、自第二弹性部向上弯折的第二抵接部25。固定部21的两侧具有固定在本体10的干涉凸缘211,第一弹性部22具有第一接触部261,第二弹性部24具有第二接触部262。第一、第二弹性部22、24在受压时,第一、第二抵接部23、25彼此电性连接于一起,如图4所示。本发明的改良在于,所述第一弹性部22包括自固定部21向上延伸的第一竖直部221、自第一竖直部倾斜延伸出本体上表面101的第一倾斜部222,第二弹性部24包括自固定部21向下延伸的第二竖直部241、自第二竖直部倾斜延伸的第二倾斜部242,端子20在未受压的自由状态时,第一、第二竖直部221、241彼此共面。参图3,可以看出,本发明的端子20上下端均为弹性抵压接触形式,不同于上端弹性抵压而下端焊接的结构,其对端子固定在本体内的强度,端子上下端的弹性抵压的机械性能均有较高要求,本发明的端子20在上下方向相对比较长,使得其保证有一定的弹性强度,同时端子偏瘦长,也可以在端子的高频信号传输中改善阻抗以及相邻端子的串扰。本发明提及的第一、第二并无先后顺序,其用来对相似结构采用相同名称时作区别,本实施例中,面对芯片模组为上,面对电路板的则为下。

18.所述第一接触部261位于第一倾斜部222的最高点处,第一抵接部23包括自第一倾斜部222向下倾斜弯折的第三倾斜部231及自第三倾斜部向下弯折的第一延伸部232,第一延伸部的末端向内弯折有第一抵接端233。第二接触部262位于第二倾斜部242的最低点处,第二抵接部25包括自第二倾斜部242向上倾斜弯折的第四倾斜部251及自第四倾斜部向上弯折的第二延伸部252,第二延伸部的末端向内弯折有第二抵接端253,第一、第二抵接端可彼此机械接触。

19.所述端子孔11包括收容孔112及位于收容孔旁侧的固定缝113,干涉凸缘211则干

涉固定在固定缝112内,第一、第二弹性部22、224自收容孔112向外延伸,第一、第二抵接部23、25自外侧向内延伸入收容孔112。所述固定部21的一侧干涉凸缘221连接有料带连接部27,自上表面向下看(如图2所示),第一、第二倾斜部222、242与料连带连接部27呈45度的夹角。本实施例中,料带连接部27干涉固定在固定缝113内,其对应的干涉凸缘则仅其连接作用。第一、第二弹性部221、241分别开设有沿其延伸方向延伸的纵长槽28。本体的上下表面还凸伸有支撑块12。如图3、4所示,端子孔11的内壁面,尤其是对应固定部21、第一、第二竖直部处的内壁面为竖直面,面对第一、第二抵接部的内壁面114亦为竖直面。

20.如图3所示,在自由状态时,第一、第二延伸部232、252大致平行于第一、第二竖直部221、241,但具体设计时可存在一定的小角度。第一竖直部221与第一倾斜部222的交接点a1高于本体的上表面101,第二竖直部241与第二倾斜部242的交接点a2低于本体的下表面102,端子20在弹力受压时,如图4所示,第一、第二弹性部以固定部21的上下缘为支撑点作弹性位移,产生形变,相对而言,本发明设置第一、第二竖直部,能够加大弹性部的弹性强度。

21.第一弹性部内的纵长槽28的最高点b1与第三倾斜部与第一延伸部的交接点c1处于同一高度,第二弹性部内的纵长槽27的最低点b2与第四倾斜部与第二延伸部的交接点c2处于同一高度。第三倾斜部与第一延伸部的交接点c1位于第一接触部261与第一竖直部221与第一倾斜部222的交接点a1之间,第四倾斜部与第二延伸部的交接点c2位于第一接触部262与第二竖直部241与第二倾斜部242的交接点a2之间。

22.上述实施例仅为本发明的较佳实施方式而已,不应以此限制本发明的范围,即凡是依本发明权利要求书及说明书内容所作的简单的等效变化与修饰,皆应仍属本发明专利涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1