GaN基增强型功率晶体管的制备方法

gan基增强型功率晶体管的制备方法

技术领域

1.本发明涉及一种gan基增强型功率晶体管的制备方法。

背景技术:

2.目前基于p型栅极gan基增强型功率晶体管尽管已经商业化,然而在传统p型栅增强型hemt(high electron mobility transistor,高电子迁移率晶体管)制造工艺中,栅极gan材料区域的p型掺杂不可避免的会引入杂质能级,同时在注入工艺中存在空穴载流子的不充分注入问题,造成了严重的栅极阈值不稳定性,严重影响了p型栅gan基功率晶体管的可靠性,降低了晶体管的功率转换效率。

技术实现要素:

3.针对上述问题,本发明提供一种gan基增强型功率晶体管的制备方法,通过对(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层构成的异质结构全部或部分刻蚀,在栅极区域形成非掺杂(in,ga)n盖帽层,结合盖帽层的反极化效应和薄势垒异质结构al(in,ga)n/(in,ga)n的本征增强型特性实现高阈值gan基增强型hemt,有效避免了传统p型栅极gan盖帽层制造工艺中存在的p型重掺杂和空穴注入不充分问题,显著提高了p型栅增强型hemt的阈值稳定性。下面具体说明本发明的技术方案。

4.一种gan基增强型功率晶体管的制备方法,包括:在衬底上依次制备(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层;刻蚀非栅极区域的非掺杂(in,ga)n盖帽层,使得非栅极区域的al(in,ga)n薄势垒层暴露;在刻蚀完成的非掺杂(in,ga)n盖帽层及暴露出的al(in,ga)n薄势垒层表面沉积钝化层;制作源极和漏极的欧姆接触;制作器件隔离;制作栅极金属。

5.进一步地,本发明的gan基增强型功率晶体管的制备方法,al(in,ga)n薄势垒层厚度小于10nm,al(in,ga)n薄势垒层组分为以下至少一种:aln二元合金,algan、alinn或者ingan三元合金,alingan四元合金。

6.进一步地,本发明的gan基增强型功率晶体管的制备方法,非掺杂(in,ga)n盖帽层厚度大于20nm,其中in组分含量为0~100%。

7.进一步地,本发明的gan基增强型功率晶体管的制备方法,制作源极和漏极的欧姆接触包括:在源极和漏极区域进行源漏开孔,贯穿钝化层及al(in,ga)n薄势垒层,直至到达(in,ga)n缓冲层表面;使用电子束蒸发沉积金属,在源漏开孔处形成欧姆金属;经退火形成源极和漏极的欧姆接触。

8.进一步地,本发明的gan基增强型功率晶体管的制备方法,制作栅极金属包括:在栅极区域开孔贯穿钝化层并沉积金属,得到栅极金属,使栅极金属与非掺杂(in,ga)n盖帽层形成接触,其中,所述接触为欧姆接触或肖特基接触。

9.进一步地,本发明的gan基增强型功率晶体管的制备方法,钝化层采用的材料为sin、aln、sio2中至少一种。

10.进一步地,本发明的gan基增强型功率晶体管的制备方法,栅极金属采用的材料为ni/au、pt/ti/au、al/ni/au、tin群组中的任一种。

11.进一步地,本发明的gan基增强型功率晶体管的制备方法,衬底上依次制备的(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层共同构成(in,ga)n/al(in,ga)n/(in,ga)n异质结构,其中,(in,ga)n/al(in,ga)n/(in,ga)n异质结构的制备方法为:在衬底上采用金属有机物化学气相沉积或分子束外延技术制备。

12.进一步地,本发明的gan基增强型功率晶体管的制备方法,刻蚀非栅极区域的非掺杂(in,ga)n盖帽层所采用的方法为干法刻蚀。

13.进一步地,本发明的gan基增强型功率晶体管的制备方法,钝化层的制备方法为以下之一:化学气相沉积、原子层沉积或等离子体增强化学气相沉积。

14.本发明具有如下有益效果:

15.(1)利用al(in,ga)n薄势垒层/(in,ga)n缓冲层异质结实现栅下二维电子气的本征耗尽。

16.(2)利用非掺杂(in,ga)n盖帽层与al(in,ga)n薄势垒层间的负极化电荷进一步耗尽栅下al(in,ga)n薄势垒层/(in,ga)n缓冲层异质结沟道中的二维电子气,提高增强型hemt的阈值。

17.(3)对衬底上的(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层构成的异质结构进行全部或部分刻蚀,有效避免了传统p型栅极gan盖帽层的p型重掺杂和空穴注入不充分的问题,显著改善了p型栅增强型hemt的阈值稳定性。

附图说明

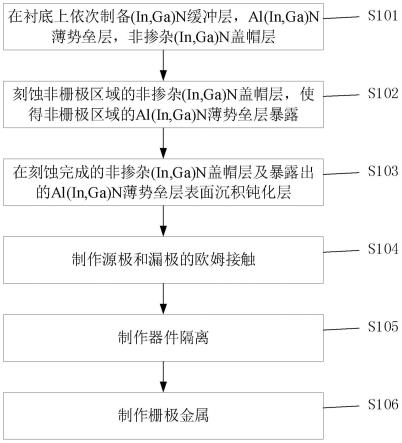

18.图1是本发明的gan基增强型功率晶体管的制备方法流程图;

19.图2是本发明一个实施例的gan基增强型功率晶体管的制备方法步骤示意图;

20.图3是本发明一个实施例制备得到的gan基增强型功率晶体管截面图。

21.图中:

22.201-衬底;202-(in,ga)n缓冲层;203-al(in,ga)n薄势垒层;204-非掺杂(in,ga)n盖帽层;205-钝化层;206-二维电子气;207-欧姆金属;208-器件隔离;209-栅极金属。

具体实施方式

23.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

24.图1是本发明的gan基增强型功率晶体管的制备方法流程图。如图1所示,本发明的方法包括:

25.s101,在衬底上依次制备(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层。

26.此处的(in,ga)n缓冲层是指氮化铟(inn)或氮化镓(gan)缓冲层,用于减小晶体管的漏电,避免在高场下器件的退化;

27.此处的al(in,ga)n薄势垒层是指氮化铝(aln)二元合金,铝镓氮(algan)、铝铟氮(alinn)或者铟镓氮(ingan)三元合金,铝铟镓氮(alingan)四元合金中的一种构成薄势垒

层,用于耗尽沟道的二维电子气,便于形成增强型器件;

28.此处的非掺杂(in,ga)n盖帽层是指非掺杂氮化铟(inn)或氮化镓(gan)盖帽层,用于进一步耗尽沟道的二维电子气,形成阈值更高的增强型器件。

29.在步骤s101,本发明采用金属有机物化学气相沉积(mocvd)或分子束外延技术(mbe)来在衬底上依次制备(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层。

30.其中,al(in,ga)n薄势垒层的厚度小于10nm,组分可以采用aln二元合金,algan、alinn或者ingan三元合金,alingan四元合金。具体地,可以是aln势垒层、algan势垒层、alinn势垒层或alingan势垒层所组成群组中的至少一种。而非掺杂(in,ga)n盖帽层厚度大于20nm,可以是非掺杂的gan,也可以是非掺杂的ingan,其中in组分含量为0~100%。

31.在本发明的技术方案中,al(in,ga)n薄势垒层和(in,ga)n缓冲层形成了al(in,ga)n薄势垒层/(in,ga)n缓冲层异质结构,该异质结构存在自发极化效应和压电极化效应,在(in,ga)n缓冲层靠近界面处,高浓度的电子被束缚在电子势阱中,形成二维电子气沟道。当al(in,ga)n薄势垒层的厚度小于10nm时,栅极区域异质结界面处的导带能级会高于费米能级,可以实现二维电子气的本征耗尽。而非掺杂(in,ga)n盖帽层与al(in,ga)n薄势垒层间也存在自发极化和压电极化效应,当非掺杂(in,ga)n盖帽层厚度大于20nm时,负极化效应更强,产生的负极化电荷更多,因此抬高了al(in,ga)n薄势垒层和(in,ga)n缓冲层界面处的导带能级,使栅下al(in,ga)n薄势垒层/(in,ga)n缓冲层异质结沟道中的二维电子气进一步耗尽,提高增强型hemt的阈值。

32.s102,刻蚀非栅极区域的非掺杂(in,ga)n盖帽层,使得非栅极区域的al(in,ga)n薄势垒层暴露。

33.非栅极区域的非掺杂(in,ga)n盖帽层刻蚀采用的方法为各向异性的干法刻蚀。在传统p型栅极gan盖帽层器件中会对栅极进行p型注入,容易出现界面注入损伤以及注入不均匀等问题,进而影响增强型hemt的阈值稳定性。此处对非栅极区域的非掺杂(in,ga)n盖帽层的干法刻蚀,利用了氟基等离子体对al(in,ga)n薄势垒层的刻蚀自截止特性,可以降低界面的刻蚀损伤,且无需注入掺杂工艺,同时具有各向异性的优点,有效避免了传统p型栅极gan盖帽层的p型重掺杂和空穴注入不充分的问题,显著改善了p型栅增强型hemt的阈值稳定性。

34.s103,在刻蚀完成的非掺杂(in,ga)n盖帽层及暴露出的al(in,ga)n薄势垒层表面沉积钝化层。

35.由于钝化层会诱导产生界面或体固定正电荷,正界面电荷增强了al(in,ga)n薄势垒层和(in,ga)n缓冲层异质结构中的极化电场,从而将异质结界面处(in,ga)n缓冲层的导带拉低到费米能级以下,使得栅极以外区域的二维电子气能够恢复。在本发明的技术方案中,为了诱导产生更多的界面电荷,恢复更多的二维电子气,采用的钝化层为sin、aln或sio2中任一种材料构成的单一介质层,或者为sin、aln、sio2中至少两者叠加而成的复合介质层。钝化层的制备方法为化学气相沉积(lpcvd)、原子层沉积(ald)或等离子体增强化学气相沉积法(pecvd)方法沉积。

36.s104,制作源极和漏极的欧姆接触。

37.在步骤s104,制作源极和漏极的欧姆接触。更具体地,先在源极和漏极区域进行源

漏开孔,贯穿钝化层及al(in,ga)n薄势垒层,直至到达(in,ga)n缓冲层表面,然后,在源漏开孔处使用电子束蒸发沉积金属,经退火后,使源极和漏极形成欧姆接触。

38.s105,制作器件隔离。

39.在步骤s105,制作器件隔离。更具体地,在非器件区域通过高能粒子注入制造高阻态区域,或者采用台面刻蚀,隔断器件与器件之间的电学联系。

40.s106,制作栅极金属。

41.在步骤s106,制作栅极金属。具体为,在栅极区域开孔,贯穿钝化层并沉积金属,得到栅极金属,使栅极金属与非掺杂(in,ga)n盖帽层形成欧姆接触或肖特基接触。其中栅极金属采用的材料可以是ni/au、pt/ti/au、a1/ni/au或tin所组成群组中的任一种。

42.在本发明中,通过对衬底上的(in,ga)n缓冲层,al(in,ga)n薄势垒层,非掺杂(in,ga)n盖帽层构成的异质结构进行全部或部分刻蚀,有效避免了传统p型栅极gan盖帽层的p型重掺杂和空穴注入不充分的问题,显著改善了p型栅增强型hemt的阈值稳定性。在栅极区域保留非掺杂(in,ga)n盖帽层,利用al(in,ga)n薄势垒层和(in,ga)n缓冲层构成异质结构的本征增强和非掺杂(in,ga)n盖帽层的反极化效应实现高阈值gan基增强型hemt,并通过含有界面或体正电荷的钝化层来恢复栅极以外的二维电子气,在得到稳定的增强型功率晶体管的同时,有效提高晶体管的功率转换效率。

43.下面以一个具体的实施例来说明本发明的技术方案。

44.如图2是本发明一个实施例的gan基增强型功率晶体管的制备方法步骤示意图。

45.图2中

①

为衬底201,在本实施例中,采用的衬底201为硅衬底,厚度为1mm。

46.采用化学气相沉积的方法在硅衬底上依次沉积(in,ga)n缓冲层202,al(in,ga)n薄势垒层203,非掺杂(in,ga)n盖帽层204,得到的结构如

②

所不。

47.其中,(in,ga)n缓冲层202采用gan二元合金,沉积厚度为300μm;al(in,ga)n薄势垒层203采用algan三元合金,沉积厚度为5nm;非掺杂(in,ga)n盖帽层204采用非掺杂的gan,沉积厚度为22nm。

48.如

③

所示,在得到的

②

上刻蚀非掺杂(in,ga)n盖帽层204,使得栅极区域以外的非掺杂(in,ga)n盖帽层204都被刻蚀,露出下层的al(in,ga)n薄势垒层203。

49.如

④

所示,在刻蚀完成的

③

表面沉积钝化层205。本实施例中钝化层205为si3n4单一介质层,采用化学气相沉积的方式在

③

表面沉积单种si3n4材料制得。钝化层厚度为20nm。

50.如

⑤

所示,在制得的

④

上制作源极和漏极的欧姆接触。先在源极和漏极区域进行源漏开孔,贯穿钝化层205及al(in,ga)n薄势垒层203,直至到达(in,ga)n缓冲层202表面,然后,在源漏开孔处使用电子束蒸发方式先后沉积ti/al/ni/au金属直至伸出钝化层205表面,经过退火,形成欧姆金属207,使源极和漏极形成欧姆接触。

51.在

⑤

中非器件区域通过高能ar粒子注入,得到如

⑥

中208所示的高阻区域,形成器件隔离208。

52.对栅极区域的钝化层205进行开孔,贯穿钝化层205并沉积ni/au到露出的非掺杂(in,ga)n盖帽层204表面,直至伸出钝化层205表面,得到栅极金属209,使栅极金属209与非掺杂(in,ga)n盖帽层204形成欧姆接触或肖特基接触。最终制得结构如

⑦

所示。

53.至此,本实施例的gan基增强型功率晶体管制备完成。制得的晶体管截面图如图3所示。

54.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1