一种半导体衬底沟槽中外延填充方法及图像传感器与流程

1.本发明涉及半导体技术领域,特别涉及一种半导体衬底沟槽中外延填充方法及图像传感器。

背景技术:

2.对图像传感器的感光区域进行隔离,常见于背照式图像传感器工艺。通常的方法中,先进行衬底晶圆背面减薄工艺,再通过光刻工艺在晶圆表面形成用于图像感光区域隔离的图形,进而通过刻蚀工艺在衬底背面形成深沟槽,继而在深沟槽中填充介质完成图像传感器感光区域的隔离。

3.但是,这种传统方法仍存在以下问题:

①

在研磨衬底晶圆背面减薄过程中,晶圆衬底容易发生扭曲变形,而且光刻本身的对准误差也会使得晶背沟槽图形与像素中心有较大的误差,导致侧向隔离的不均匀性,影响隔离效果;

②

在刻蚀工艺中用到的等离子体会损伤侧壁,而在晶圆背面工艺中,没有办法承受高温工艺,从而难以对侧壁损伤进行修复;

③

相邻的两个像素单元侧向隔离区和对角交叉区域的图形线宽存在差异,会导致在相邻像素侧向区域和对角交叉区域的深度差异,影响隔离和噪点效果。

4.为了改善像素单元之间的隔离效果,可以通过外延生长的方式在深沟槽中形成外延层,以与衬底反型的掺杂外延填充沟槽,形成侧向pn结,可以形成图像传感器的像素单元。但是,由于图像传感器外围的沟槽线宽和方向不一致,在外延的过程中,氯化氢等刻蚀气体的反应、外延生长过程中不同晶面面的融合等因素都会造成外延层基地表面不平滑和晶向的突变,这些突变的表面容易引起晶格位错缺陷。

技术实现要素:

5.本发明的目的在于提供一种半导体衬底沟槽中外延填充方法及图像传感器。

6.具体地,本发明中半导体衬底沟槽中外延填充方法包括:一种半导体衬底沟槽中外延填充方法,包括:在外延过程中进行至少一次氢气环境的高温烘焙工艺,使所述高温烘焙工艺之前形成的外延层表面原子重排,以修复所述外延过程中产生的缺陷。

7.进一步地,所述高温烘焙工艺与所述外延过程在同一反应腔中进行。

8.进一步地,所述至少一次高温烘焙工艺采用温度不低于800℃、气压不低于5torr的氢气环境。

9.进一步地,所述高温烘焙工艺至少持续20秒。

10.本发明还提供给一种图像传感器,在所述图像传感器的形成过程中采用如前述的半导体衬底沟槽中外延填充方法。

11.进一步地,在此种图像传感器中,所述半导体衬底中的沟槽用于形成所述图像传感器像素单元之间的隔离区域。

12.进一步地,所述外延层至少包括与所述半导体衬底掺杂类型相反的子外延层,用

于所述图像传感器像素单元之间的电学隔离。

13.进一步地,所述外延层包括外延本征半导体形成的第一子外延层和外延与所述半导体衬底掺杂类型相反的半导体形成的第二子外延层。

14.进一步地,在所述外延层上部具有外延形成的顶部外延层,所述顶部外延层封闭所述沟槽,使所述沟槽中形成中空间隙。

15.本发明通过上述方案,使得在深沟槽中外延的过程中,增加高温烘焙工艺的步骤,以消除在深沟槽开口处附近具有倾角的位置进行外延时,由于晶向生长差异产生的位错等晶格缺陷。氢气环境下的高温烘焙工艺能够对表面进行高温修复处理,截断前层的位错缺陷影响,让外延生长基底表面晶向过度平滑,有效降低后续的外延生长晶格缺陷,提升外延的质量。

附图说明

16.通过参照附图阅读以下所作的对非限制性实施例的详细描述,本发明的其它特征、目的和优点将会变得更明显。

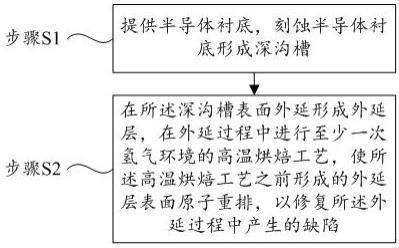

17.图1、图2、图5为本发明一种半导体衬底沟槽中外延填充的结构示意图;图3为外延过程中晶格缺陷示意图;图4为本发明一种图像传感器的形成过程流程图。

18.在图中,贯穿不同的示图,相同或类似的附图标记表示相同或相似的装置(模块)或步骤。

具体实施方式

19.在本发明中提供一种半导体衬底沟槽中外延填充方法,其特征在于,包括:在外延过程中进行至少一次氢气环境的高温烘焙工艺,使所述高温烘焙工艺之前形成的外延层表面原子重排,以修复所述外延过程中产生的缺陷。

20.如图1所示,在半导体器件工艺中,在半导体衬底100中刻蚀形成深沟槽110是常见的工艺流程。在深沟槽110内壁表面外延形成外延层111。但是,在深沟槽110中进行外延生长时,在靠近深沟槽110顶部开口处会逐渐形成具有倾角的斜坡,在这些斜坡上继续外延生长时,由于晶向差异以及沟槽交叉处的线宽更宽等原因(如图2所示,d1《d2),会在外延层111内部产生晶格缺陷,例如位错等(如图3所示)。

21.在本发明中,在形成外延层111的过程中,增加了高温烘焙工艺,在氢气环境中可以使外延层表面的原子重排,消除此时外延层表面的[w用1] 。优选地,在实际应用中高温烘焙工艺可以与外延形成外延层111在同一反应腔内进行。在外延层111达到一定厚度时,暂停外延过程,进行氢气高温烘焙对外延层表面进行修复,之后继续进行外延工艺,形成外延层111。

[0022]

优选地,所述至少一次高温烘焙工艺采用温度不低于800℃、气压不低于5torr的氢气环境,以保证高温烘焙工艺的效果。进一步地,在可选的实施方式中,为了能够更充分地消除外延层的缺陷,所述高温烘焙工艺至少持续20秒。

[0023]

在本发明中,给出一种具体实施方式,本发明中的方案可以用于图像传感器的形成工艺中。如图4所示,该图像传感器的形成过程可以通过以下步骤:

步骤s1:提供半导体衬底100,刻蚀半导体衬底100形成深沟槽110;其中,深沟槽110的线宽可以具有差异,例如在沟槽相交的地方,其对角线宽就会宽于普通的沟槽线宽,在图1中分别标记为110b和110a。

[0024]

步骤s2:在所述深沟槽110表面外延形成外延层111,在外延过程中进行至少一次氢气环境的高温烘焙工艺,使所述高温烘焙工艺之前形成的外延层表面原子重排,以修复所述外延过程中产生的缺陷。

[0025]

优选地,高温烘焙工艺可以与外延形成外延层111在同一反应腔内进行;进一步地,所述至少一次高温烘焙工艺采用温度不低于800℃、气压不低于5torr的氢气环境,以保证高温烘焙工艺的效果。进一步地,在可选的实施方式中,为了能够更充分地消除外延层的缺陷,所述高温烘焙工艺至少持续20秒。

[0026]

在可选的实施方式中,外延层111可以至少包括与半导体衬底100性质相反的子外延层。如图1所示,优选地,由第一子外延层111a和第二子外延层111b组成。其中,第一子外延层111a为本征半导体层,第二子外延层111b的掺杂类型与半导体衬底100相反,即若半导体衬底100为p型掺杂,第二子外延层111b选择n型掺杂;若半导体衬底100为n型掺杂,第二子外延层111b选择p型掺杂。

[0027]

其中第二子外延层111b可以为高浓度掺杂层。

[0028]

在可选的实施方式中,半导体衬底100中的沟槽用于形成所述图像传感器像素单元之间的隔离区域。即如图1中的外延层111,可以在后序工艺步骤中形成像素单元之间的电学隔离。

[0029]

在可选的实施方式中,可在外延层111上通过外延形成顶部外延层112,在深沟槽110a中留有中空间隙113,利用空气的折射率实现像素单元之间的光学隔离,如图5所示。优选地,在形成顶部外延层112前,还可以先在外延层111表面形成介质层114,介质层114的组成成分可以包括但不限于氧化物、氮化物、氮氧化物。

[0030]

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论如何来看,均应将实施例看作是示范性的,而且是非限制性的。此外,明显的,“包括”一词不排除其他元素和步骤,并且措辞“一个”不排除复数。装置权利要求中陈述的多个元件也可以由一个元件来实现。第一、第二等词语用来表示名称,而并不表示任何特定的顺序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1