包括贯通电极的半导体芯片和包括其的半导体封装的制作方法

文档序号:30805786发布日期:2022-07-19 22:57阅读:80来源:国知局

导航: X技术> 最新专利>电气元件制品的制造及其应用技术

1.本专利文献涉及半导体技术,更具体地,涉及一种包括贯通电极的半导体芯片和包括该半导体芯片的半导体封装。

背景技术:

2.电子产品即使其尺寸逐渐变小仍需要大量数据处理。因此,这些电子产品中使用的半导体芯片的尺寸也需要薄且小。此外,已制造了嵌入有多个半导体芯片的半导体封装。

3.多个半导体芯片可在垂直方向上层叠并且可利用穿过半导体芯片的贯通电极彼此电连接。

技术实现要素:

4.在实施方式中,一种半导体芯片可包括:主体部分,该主体部分具有前表面和后表面,该主体部分按照后表面在前表面上方的方式取向;第一贯通电极和第二贯通电极,所述第一贯通电极和所述第二贯通电极穿透主体部分,并且具有突出到主体部分的后表面上方的突起;电源图案,该电源图案形成在主体部分的后表面上方并且与所述突起间隔开;层间绝缘层,该层间绝缘层填充电源图案与所述突起之间的空间;以及第一后连接电极和第二后连接电极,所述第一后连接电极和所述第二后连接电极形成在层间绝缘层上方并且分别连接到第一贯通电极和第二贯通电极,其中,第一后连接电极同时连接到第一贯通电极和电源图案的与第一贯通电极相邻的一部分。

5.在另一实施方式中,一种半导体封装可包括:第一半导体芯片,该第一半导体芯片包括具有前表面和后表面的主体部分、穿透主体部分并且具有突出到主体部分的后表面上方的突起的第一贯通电极和第二贯通电极、形成在主体部分的后表面上方并且与所述突起间隔开的电源图案、填充电源图案与所述突起之间的空间的层间绝缘层、形成在层间绝缘层上方并且分别连接到第一贯通电极和第二贯通电极的第一后连接电极和第二后连接电极以及形成在层间绝缘层和电源图案上方并且填充第一后连接电极与第二后连接电极之间的空间的后绝缘层,主体部分按照后表面在前表面上方的方式取向,其中,第一后连接电极同时连接到第一贯通电极和电源图案的与第一贯通电极相邻的一部分;以及第二半导体芯片,该第二半导体芯片包括分别直接结合到第一后连接电极和第二后连接电极的多个前连接电极以及在填充多个前连接电极之间的空间的同时直接结合到后绝缘层的前绝缘层。

6.在另一实施方式中,一种半导体芯片可包括:主体部分,该主体部分具有前表面和后表面,该主体部分按照后表面在前表面上方的方式取向;第一贯通电极和第二贯通电极,所述第一贯通电极和所述第二贯通电极穿透主体部分;电源图案,该电源图案形成在主体部分的后表面上方并且与第一贯通电极和第二贯通电极间隔开;第一连接图案和第二连接图案,所述第一连接图案和所述第二连接图案形成在主体部分的后表面上方并且分别连接到第一贯通电极和第二贯通电极;层间绝缘层,该层间绝缘层填充电源图案与第一连接图案和第二连接图案之间的空间;以及第一后连接电极和第二后连接电极,所述第一后连接

电极和所述第二后连接电极形成在层间绝缘层上方并且分别连接到第一连接图案和第二连接图案,其中,第一后连接电极同时连接到第一连接图案和电源图案的与第一连接图案相邻的一部分。

7.在另一实施方式中,一种半导体封装可包括:第一半导体芯片,其包括具有前表面和后表面的主体部分、穿透主体部分的第一贯通电极和第二贯通电极、形成在主体部分的后表面上方并且与第一贯通电极和第二贯通电极间隔开的电源图案、形成在主体部分的后表面上方并且分别连接到第一贯通电极和第二贯通电极的第一连接图案和第二连接图案、填充电源图案与第一连接图案和第二连接图案之间的空间的层间绝缘层、形成在层间绝缘层上方并且分别连接到第一连接图案和第二连接图案的第一后连接电极和第二后连接电极以及形成在层间绝缘层和电源图案上方并且填充第一后连接电极与第二后连接电极之间的空间的后绝缘层,主体部分按照后表面在前表面上方的方式取向,其中,第一后连接电极同时连接到第一贯通电极和电源图案的与第一贯通电极相邻的一部分;以及第二半导体芯片,该第二半导体芯片包括分别直接结合到第一后连接电极和第二后连接电极的多个前连接电极以及在填充多个前连接电极之间的空间的同时直接结合到后绝缘层的前绝缘层。

附图说明

8.图1a和图1b是例示了根据本公开的实施方式的半导体芯片的示图。

9.图2是例示了根据本公开的实施方式的层叠的半导体芯片的横截面图。

10.图3a至图3f是例示了根据本公开的实施方式的半导体芯片的制造方法的横截面图。

11.图4a至图4d是例示了根据本公开的另一实施方式的半导体芯片的制造方法的横截面图。

12.图5a和图5b是例示了根据本公开的另一实施方式的半导体芯片的示图。

13.图6a至图6d是例示了根据本公开的另一实施方式的半导体芯片的制造方法的横截面图。

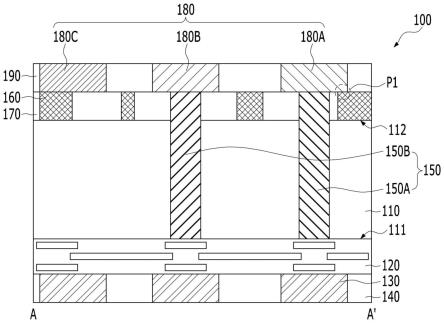

14.图7a至图7c是例示了根据本公开的另一示例性实施方式的半导体芯片的制造方法的横截面图。

15.图8示出例示了采用包括根据实施方式的半导体封装的存储卡的电子系统的框图。

16.图9示出例示了包括根据实施方式的半导体封装的另一电子系统的框图。

具体实施方式

17.以下,将参照附图详细描述本公开的各种实施方式。

18.附图未必按比例绘制。在一些情况下,附图中的至少一些结构的比例可能已被夸大,以便清楚地示出所描述的实施方式的特定特征。在以多层结构呈现具有两个或更多个层的附图或描述中的特定示例时,如所示的这些层的相对定位关系或布置层的顺序反映了所描述或示出的示例的特定实现方式,不同的相对定位关系或布置层的顺序可以是可能的。另外,多层结构的所描述或示出的示例可能没有反映该特定多层结构中所存在的所有层(例如,两个所示层之间可存在一个或更多个附加层)。作为特定示例,当所描述或示出的

多层结构中的第一层被称为在第二层“上”或“上方”或者在基板“上”或“上方”时,第一层可直接形成在第二层或基板上,但也可表示第一层和第二层或基板之间可存在一个或更多个其它中间层的结构。

19.在以下实施方式的描述中,当参数被称为“预定”时,可旨在意指当在处理或算法中使用参数时预先确定参数的值。参数的值可在处理或算法开始时设定,或者可在执行处理或算法的时段期间设定。

20.图1a和图1b是例示了根据本公开的实施方式的半导体芯片的示图。图1a是从上方看时本实施方式的半导体芯片的平面图,图1b是沿着图1a的线a-a’截取的横截面图。在图1a中,为了描述方便,设置在后连接电极下方的贯通电极和电源图案与设置在半导体芯片的最上部的后连接电极一起以虚线示出。

21.参照图1a和图1b,本实施方式的半导体芯片100可包括主体部分110、布线部分120、前连接电极130、前绝缘层140、贯通电极150、电源图案160、层间绝缘层170、后连接电极180和后绝缘层190。

22.主体部分110可由诸如硅或锗的半导体材料形成,并且可具有前表面111、后表面112以及将它们彼此连接的侧表面。主体部分110的前表面111可指设置有布线部分120的有源表面,主体部分110的后表面112可指位于前表面111的相对侧的表面。

23.布线部分120可形成在主体部分110的前表面111下方。布线部分120可包括电连接到贯通电极150的电路/布线结构。为了描述方便,在布线部分120中电路/布线结构被简单地示出为线,但不限于所示的情况。在这种情况下,电路/布线结构可根据半导体芯片100的类型不同地实现。例如,当半导体芯片100包括诸如动态随机存取存储器(dram)和静态随机存取存储器(sram)的易失性存储器或者诸如nand闪存、电阻随机存取存储器(rram)、相变随机存取存储器(pram)、磁阻随机存取存储器(mram)和铁电随机存取存储器(fram)的非易失性存储器时,电路/布线结构可包括具有多个存储器单元的存储器单元阵列。

24.前连接电极130可形成在布线部分120下方。前连接电极130可用于将半导体芯片100电连接到将面向前表面111的另一组件(未示出),例如另一半导体芯片或基板。前连接电极130可包括诸如铜(cu)、镍(ni)、锡(sn)、金(au)、银(ag)或其组合的金属或者该金属的化合物,并且可具有单层结构或多层结构。具体地,当前连接电极130直接结合到另一半导体芯片(未示出)的后连接电极以形成混合结合结构时,前连接电极130可包括可通过高温退火工艺通过金属的相互扩散结合到后连接电极的金属材料。

25.前连接电极130可电连接到布线部分120。此外,前连接电极130可通过布线部分120电连接到贯通电极150。

26.前绝缘层140可形成在布线部分120下方以填充前连接电极130之间的空间。前绝缘层140可包括各种绝缘材料。具体地,当前绝缘层140直接结合到另一半导体芯片(未示出)的后绝缘层以形成混合结合结构时,前绝缘层140可包括可通过绝缘材料之间的共价结合结合到后绝缘层的绝缘材料。例如,前绝缘层140可包括氧化硅或氮化硅。不面向布线部分120的前连接电极130的一个表面和前绝缘层140的一个表面可基本上共面。

27.贯通电极150可具有从主体部分110的前表面111延伸到后表面112并且穿透主体部分110的柱形状。另外,贯通电极150可突出到主体部分110的后表面112上方以进一步穿透形成在主体部分110的后表面112上方的层间绝缘层170。作为示例,贯通电极150可包括

tsv(硅通孔)。贯通电极150可包括各种导电材料。作为示例,贯通电极150可包括诸如铜(cu)、锡(sn)、银(ag)、钨(w)、镍(ni)、钌(ru)、钴(co)或其组合的金属或者该金属的化合物。贯通电极150的一端可连接到布线部分120的电路/布线结构的一部分,贯通电极150的另一端可连接到后连接电极180。在平面图中,各个贯通电极150的宽度由标号w1指示。

28.贯通电极150可包括电连接到电源图案160的第一贯通电极150a以及不电连接到电源图案160的第二贯通电极150b。可通过第一贯通电极150a供应电源(例如,各种电平的电源电压或接地电压)。在这种情况下,施加到第一贯通电极150a的电源可与施加到电源图案160的电源相同。另外,可通过第二贯通电极150b供应各种电平的电源,或者可通过第二贯通电极150b传输驱动半导体芯片100所需的各种信号。在这种情况下,施加到第二贯通电极150b的电源可与施加到第一贯通电极150a和电源图案160的电源不同。例如,施加到第二贯通电极150b的电位值可与施加到第一贯通电极150a和电源图案160的电位值不同。

29.电源图案160可形成在主体部分110的后表面112上方,以在水平方向上与贯通电极150间隔开。电源图案160可通过第一后连接电极180a电连接到第一贯通电极150a并且可与第二贯通电极150b电绝缘。电源图案160可包括各种导电材料。作为示例,电源图案160可包括诸如铜(cu)、镍(ni)、锡(sn)、金(au)、银(ag)或其组合的金属或者该金属的化合物。

30.在本实施方式中,在平面图中,电源图案160可包括沿着一个方向布置的多个线图案160a以及将多个线图案160a的端部彼此连接的延伸图案160b。层间绝缘层170可填充多个线图案160a之间的空间。即,多个线图案160a可与层间绝缘层170交替地布置。在这种情况下,与形成具有平板形状的电源图案的情况相比,形成层间绝缘层170的面积可增加,以使得形成电源图案160的层与形成在其上的层(例如,形成后连接电极180和后绝缘层190的层)之间的粘附性质可改进。然而,本公开不限于此,假设与贯通电极150间隔开,电源图案160可具有各种平面形状。

31.通过电源图案160a,两个或更多个第一贯通电极150a可彼此电连接以形成配电网络(pdn),因此,可通过第一贯通电极150a进行稳定电源供给。

32.层间绝缘层170可形成在主体部分110的后表面112上方以填充贯通电极150与电源图案160之间的空间。层间绝缘层170可包括诸如氧化硅、氮化硅或其组合的各种绝缘材料。另外,层间绝缘层170可具有单层结构或多层结构。不面向主体部分110的后表面112的贯通电极150的一个表面、电源图案160的一个表面和层间绝缘层170的一个表面可形成基本上平坦的表面。

33.后连接电极180可形成在基于贯通电极150的一个表面、电源图案160的一个表面和层间绝缘层170的一个表面形成的平坦表面上方。后连接电极180可用于将半导体芯片100电连接到将面向后表面112的另一组件(未示出),例如另一半导体芯片。后连接电极180可包括诸如铜(cu)、镍(ni)、锡(sn)、金(au)、银(ag)或其组合的金属或者该金属的化合物,并且可具有单层结构或多层结构。后连接电极180可由与前连接电极130相同的材料形成。具体地,当后连接电极180直接结合到另一半导体芯片(未示出)的前连接电极以形成混合结合结构时,后连接电极180可包括可通过高温退火工艺通过金属的相互扩散结合到前连接电极的金属材料。在平面图中,各个后连接电极180的宽度由标号w2指示。

34.后连接电极180可包括连接到第一贯通电极150a的第一后连接电极180a、连接到第二贯通电极150b的第二后连接电极180b以及未连接到贯通电极150的第三后连接电极

180c。

35.第一后连接电极180a可形成为与各个第一贯通电极150a交叠并且连接。第一后连接电极180a可与第一贯通电极150a一一对应。此外,第一后连接电极180a可与电源图案160的与第一贯通电极150a相邻的部分同时交叠并且连接(参见p1)。为此,第一后连接电极180a的宽度w2的值可大于第一贯通电极150a的宽度w1与第一贯通电极150a和与之相邻的电源图案160之间的最小距离d1之和。结果,第一后连接电极180a可将第一贯通电极150a电连接到电源图案160,并且施加到第一贯通电极150a和电源图案160的电源可被供应给第一后连接电极180a。

36.第二后连接电极180b可形成为与各个第二贯通电极150b交叠并且连接。第二后连接电极180b可与第二贯通电极150b一一对应。第二后连接电极180b可能不与第二贯通电极150b周围的电源图案160交叠/连接。为此,电源图案160可被布置为使得第二贯通电极150b和与之相邻的电源图案160之间的最小距离d2大于第一贯通电极150a和与之相邻的电源图案160之间的最小距离d1。即,第二后连接电极180b的宽度w2的值可小于第二贯通电极150b的宽度w1与第二贯通电极150b和与之相邻的电源图案160之间的最小距离d2之和。施加到第二贯通电极150b的电源或信号可被供应或传输给第二后连接电极180b。

37.第三后连接电极180c可形成为与第一后连接电极180a和第二后连接电极180b间隔开,而不与贯通电极150交叠或连接。第三后连接电极180c可以是不用于信号传输或电源供给的虚设物(dummy)。在本实施方式中,第三后连接电极180c可通过与电源图案160交叠并且连接而被施加有与电源图案160相同的电源。然而,如果第三后连接电极180c处于不电连接到除了电源图案160之外的其它布线的浮置状态,则第三后连接电极180c可能不执行信号传输或电源供给的功能。此外,如稍后描述的,即使第三后连接电极180c连接到另一半导体芯片的前连接电极(参见图2中的130),在第三后连接电极180c处于不电连接到除了电源图案160之外的其它布线的浮置状态的情况下,第三后连接电极180c也可能不执行信号传输或电源供给的功能。在另一实施方式中,与例示不同,第三后连接电极180c可能不与电源图案160交叠/连接。即,第三后连接电极180c可形成在不存在电源图案160的区域中,因此可具有电浮置状态。第三后连接电极180c可执行各种功能。作为示例,第三后连接电极180c可起到方便工艺的作用,例如当层叠多个半导体芯片100时在平坦化工艺期间用作停止层。作为另一示例,第三后连接电极180c可起到改进具有多个半导体芯片100的半导体封装中的发热特性的作用。可省略第三后连接电极180c。

38.前连接电极130和后连接电极180可具有相同的布置方式。即,在平面图中,多个前连接电极130和多个后连接电极180可彼此交叠。

39.后绝缘层190可形成在基于贯通电极150的一个表面、电源图案160的一个表面和层间绝缘层170的一个表面形成的平坦表面上方,以填充后连接电极180之间的空间。后绝缘层190可包括各种绝缘材料。后绝缘层190可由与前绝缘层140相同的材料形成。具体地,当后绝缘层190直接结合到另一半导体芯片(未示出)的前绝缘层以形成混合结合结构时,后绝缘层190可包括可通过绝缘材料之间的共价结合来结合到前绝缘层的绝缘材料。例如,后绝缘层190可包括氧化硅或氮化硅。不面向上述平坦表面的后连接电极180的一个表面和后绝缘层190的一个表面可基本上共面。

40.根据上述半导体芯片100,第一后连接电极180a可同时连接到对应的第一贯通电

极150a和与之相邻的电源图案160。此外,第一后连接电极180a可直接接触对应的第一贯通电极150a和与之相邻的电源图案160。因此,由于两个或更多个第一贯通电极150a通过第一后连接电极180a和电源图案160形成pdn,所以可容易地且稳定地供应电源。具体地,当多个半导体芯片100在垂直方向上层叠时,可更高效地执行通过多个半导体芯片100的电源供给。

41.另外,当多个半导体芯片100在垂直方向上层叠时,可提供将垂直方向上相邻的半导体芯片100牢固地结合的混合结合结构。这将在下面参照图2更详细地描述。

42.图2是例示了根据本公开的实施方式的层叠的半导体芯片的横截面图。图2示出两个半导体芯片在垂直方向上层叠的情况。

43.参照图2,第一半导体芯片100可与上述图1a和图1b的半导体芯片100基本上相同。因此,使用与图1a和图1b的标号相同的标号。

44.第二半导体芯片200也可与上述图1a和图1b的半导体芯片100基本上相同。即,第二半导体芯片200可包括:主体部分210,其具有前表面211和后表面212,在实施方式中该主体部分按照后表面212在前表面211上方的方式取向;布线部分220,其设置在主体部分210的前表面211上方;前连接电极230,其设置在布线部分220上方并且通过布线部分220电连接到贯通电极250;前绝缘层240,其设置在布线部分220上方并且填充前连接电极230之间的空间;贯通电极250,其穿透主体部分210并且突出到主体部分210的后表面212上方;电源图案260,其设置在主体部分210的后表面212上方;层间绝缘层270,其设置在主体部分210的后表面212上方并且填充贯通电极250和电源图案260之间的空间;后连接电极280,其设置在层间绝缘层270上方;以及后绝缘层290,其设置在层间绝缘层270上方并且填充后连接电极280之间的空间。贯通电极250可包括电连接到电源图案260的第一贯通电极250a和未电连接到电源图案260的第二贯通电极250b。后连接电极280可包括同时连接到第一贯通电极250a和电源图案260的第一后连接电极280a、连接到第二贯通电极250b而未连接到电源图案260的第二后连接电极280b以及未连接到贯通电极250的第三后连接电极280c。

45.第二半导体芯片200可层叠在第一半导体芯片100上方,并且第二半导体芯片200的前表面211面向第一半导体芯片100的后表面112。在这种情况下,第一半导体芯片100的后连接电极180可直接结合到第二半导体芯片200的前连接电极230,并且第一半导体芯片100的后绝缘层190可直接结合到第二半导体芯片200的前绝缘层240。这可通过在第一半导体芯片100的后连接电极180和后绝缘层190分别与第二半导体芯片200的前连接电极230和前绝缘层240接触的状态下执行高温退火工艺来实现。在高温退火工艺期间,用于形成第一半导体芯片100的后连接电极180和第二半导体芯片200的前连接电极230的金属可通过金属的相互扩散(例如,铜的相互扩散)而彼此结合。此时,用于形成第一半导体芯片100的后绝缘层190和第二半导体芯片200的前绝缘层240的绝缘材料可通过绝缘材料的共价结合(例如,氧化硅或氮化硅之间形成的共价结合)来彼此结合。因此,可执行第一半导体芯片100与第二半导体芯片200之间的混合结合。即,可原位执行金属与金属的结合以及绝缘层与绝缘层的结合。

46.第一半导体芯片100的第一至第三后连接电极180a、180b和180c中的每一个可结合到第二半导体芯片200的对应前连接电极230。在这种情况下,第一至第三后连接电极180a、180b和180c的布置方式可与前连接电极230的布置方式基本上相同。在平面图中,第

一至第三后连接电极180a、180b和180c中的每一个可与对应前连接电极230交叠。可省略第一半导体芯片100的第三后连接电极180c。在这种情况下,也可省略第二半导体芯片200的与第三后连接电极180c对应的前连接电极230。根据实施方式,通过第一贯通电极150a、电源图案160、第一后连接电极180a和连接到第一后连接电极180a的前连接电极230将电源供应给第一半导体芯片100和第二半导体芯片200,并且通过第二贯通电极150b、第二后连接电极180b和连接到第二后连接电极180b的前连接电极230将信号传输至第一半导体芯片100和第二半导体芯片200。根据实施方式,通过第一贯通电极150a、电源图案160、第一后连接电极180a和连接到所述第一后连接电极180a的前连接电极230供应给第一半导体芯片100和第二半导体芯片200的电源不同于通过第二贯通电极150b、第二后连接电极180b和连接到第二后连接电极180b的前连接电极230供应给第一半导体芯片100和第二半导体芯片200的电源。

47.根据上述实施方式,可通过形成混合结合结构来进行第一半导体芯片100与第二半导体芯片200之间的牢固结合。另外,由于在没有连接凸块的情况下实现第一半导体芯片100与第二半导体芯片200之间的电连接,所以它们之间的电源供给路径或信号传输路径可缩短。结果,电源供给延迟或信号传输延迟可减小,从而改进了第一半导体芯片100和第二半导体芯片200的操作特性。另外,由于不需要第一半导体芯片100和第二半导体芯片200之间的用于布置凸块的空间,所以通过利用绝缘材料填充空间而导致的传热效率的降低可减小。

48.此外,通过不在表面上设置电源图案160和260,对混合结合结构的界面结合力的影响可最小化。混合结合结构的界面结合力可被定义为绝缘层和绝缘层之间的共价结合力与金属和金属之间的金属间结合力之和。由于共价结合力比金属间结合力强,所以当绝缘层在结合界面处所占据的面积减小时,总界面结合力也可减小。如果电源图案形成在与后连接电极相同的高度处(即,后绝缘层中),则下半导体芯片的后绝缘层与上半导体芯片的前绝缘层之间的接触面积可减小,因此它们之间的界面结合力可减小。

49.图3a至图3f是例示了根据本公开的实施方式的半导体芯片的制造方法的横截面图。

50.参照图3a,可在载体基板(未示出)上方形成结构,该结构具有:初始主体部分310,其具有前表面311和初始后表面312并且其中形成有初始贯通电极350;布线部分320,其形成在初始主体部分310的前表面311下方;以及前连接电极330和前绝缘层340,其形成在布线部分320下方。初始贯通电极350可包括初始导电柱352以及围绕初始导电柱352的侧表面和上表面的初始间隔物354。下面将更详细地描述形成该结构的方法。

51.首先,可提供具有前表面311和初始后表面312的初始主体部分310。初始后表面312距前表面311的距离可比图1b的后表面112大,因此,初始主体部分310可具有比图1b的主体部分110大的厚度。

52.随后,可蚀刻初始主体部分310以在初始主体部分310中形成孔313。孔313可从初始主体部分310的前表面311朝着初始后表面312形成在预定深度。孔313的深度可小于初始主体部分310的厚度。

53.随后,可沿着孔313的内壁形成初始间隔物354,并且可利用导电材料填充形成有初始间隔物354的孔313以形成初始导电柱352。因此,可形成初始贯通电极350。初始导电柱

352可包括金属或金属化合物,并且初始间隔物354可包括氧化硅、氮化硅、金属氮化物等。

54.随后,可在形成有初始贯通电极350的初始主体部分310的前表面311下方形成布线部分320,并且可在布线部分320下方形成前连接电极330和前绝缘层340。因此,可获得图3a的结构。

55.参照图3b,可去除初始主体部分310的一部分以形成比初始主体部分310薄的主体部分310a。即,可执行减薄工艺。

56.可对初始主体部分310的初始后表面312执行减薄工艺。因此,主体部分310a可具有前表面311和后表面312a。主体部分310a的前表面311与后表面312a之间的距离可小于前表面311与初始后表面312之间的距离。可通过磨削、化学机械抛光(cmp)和/或回蚀来执行减薄工艺。此外,可执行减薄工艺以使得初始贯通电极350的一部分可从主体部分310a的后表面312a突出。初始贯通电极350的从主体部分310a的后表面312a突出的部分将被称为初始贯通电极350的突起(参见p2)。

57.参照图3c,可在主体部分310a的后表面312a和初始贯通电极350的突起上方形成初始第一层间绝缘层372。初始第一层间绝缘层372可沿其下轮廓适形地形成。作为示例,初始第一层间绝缘层372可包括氮化硅。

58.随后,可沿其下轮廓在初始第一层间绝缘层372上方形成初始第二层间绝缘层374和初始第三层间绝缘层376的层叠结构。该层叠结构可具有开口op,开口op提供要形成电源图案的空间。该层叠结构可通过沿其下轮廓在初始第一层间绝缘层372上方沉积用于形成初始第二层间绝缘层374和初始第三层间绝缘层376的绝缘材料层并且通过掩模和蚀刻工艺去除与开口op对应的区域中的绝缘材料层来形成。在该掩模和蚀刻工艺期间,初始第一层间绝缘层372可用作蚀刻停止层。作为示例,初始第二层间绝缘层374和初始第三层间绝缘层376可分别包括氧化硅和氮化硅。

59.参照图3d,可沿其下轮廓在图3c的所得结构上方形成初始含金属薄膜层362。初始含金属薄膜层362可包括金属或金属化合物,并且可具有单层结构或多层结构。初始含金属薄膜层362可通过沉积等形成,并且可形成为具有不完全填充开口op的薄厚度。初始含金属薄膜层362可起到改进稍后描述的含金属层364的性质和/或形成工艺的作用。

60.随后,可在初始含金属薄膜层362上方形成初始含金属层364。初始含金属层364可包括金属或金属化合物,并且可具有单层结构或多层结构。初始含金属层364可通过沉积、电镀等形成,并且可形成为具有充分填充形成有初始含金属薄膜层362的开口op的厚度。

61.参照图3e,可对图3d的所得结构执行平坦化工艺。平坦化工艺可通过化学机械抛光等执行。另外,可执行平坦化工艺以使得除了存在于初始贯通电极350上方的初始第三层间绝缘层376之外,初始第三层间绝缘层376的上表面(参见图3d中的箭头

①

)暴露。

62.作为该工艺的结果,可形成含金属薄膜层362a、含金属层364a、第一层间绝缘层372a、第二层间绝缘层374a、第三层间绝缘层376a以及具有导电柱352a和间隔物354a的贯通电极350a。含金属薄膜层362a、含金属层364a、第一层间绝缘层372a、第二层间绝缘层374a、第三层间绝缘层376a和贯通电极350a可形成平坦表面。下面将更具体地描述含金属薄膜层362a、含金属层364a、第一层间绝缘层372a、第二层间绝缘层374a、第三层间绝缘层376a和贯通电极350a的形状和功能。

63.具有导电柱352a和间隔物354a的贯通电极350a可基本上对应于图1b的贯通电极

150。导电柱352a可用作用于信号传输/电源供给的路径。间隔物354a可围绕导电柱352a的侧壁以将主体部分310a和导电柱352a电绝缘和/或防止从导电柱352a到主体部分310a的金属扩散。

64.含金属薄膜层362a和含金属层364a可对应于图1b的电源图案160。因此,含金属薄膜层362a和含金属层364a将被称为电源图案360。含金属薄膜层362a可沿着上述开口(参见图3c中的op)的侧表面和下表面形成,并且可提供含金属层364a以填充形成有含金属薄膜层362a的开口。因此,含金属层364a的侧表面和下表面可由含金属薄膜层362a围绕。如上所述,含金属薄膜层362a可用于改进含金属层364a的性质和/或形成工艺。作为示例,尽管未示出,含金属薄膜层362a可具有多层结构,该多层结构具有屏障层和设置在屏障层上方的种子层。屏障层可包括诸如钛(ti)、钛钨(tiw)、氮化钛(tin)、镍钒(niv)等的金属或金属化合物,并且种子层可包括诸如铜(cu)等的金属。在这种情况下,屏障层可起到防止可通过第二层间绝缘层374a发生的电源图案360之间的金属扩散的作用,并且种子层可在电镀期间用作种子以用于形成含金属层364a。

65.第二层间绝缘层374a和第三层间绝缘层376a可基本上对应于图1b的层间绝缘层170。第一层间绝缘层372a未示出于图1b中,但是可被添加到图1b的半导体芯片。第一层间绝缘层372a可沿着主体部分310a的后表面312a和贯通电极350a的突起的侧表面形成。第一层间绝缘层372a可起到防止贯通电极350a的突起之间的金属扩散或者防止被外部金属污染的作用。第二层间绝缘层374a和第三层间绝缘层376a可用于将电源图案360彼此绝缘并且提供要形成电源图案360的空间。此外,第三层间绝缘层376a可起到防止可通过第二层间绝缘层374a发生的电源图案360之间的金属扩散的作用。

66.参照图3f,可在图3e的所得结构上方形成后绝缘层390,后绝缘层390具有提供要形成后连接电极的空间的开口392。尽管未示出,可通过在图3e的所得结构上方沉积绝缘材料层并且通过掩模和蚀刻工艺去除要形成后连接电极的区域中的绝缘材料层来形成后绝缘层390。后绝缘层390可包括诸如氧化硅的绝缘材料。

67.随后,可形成填充开口392的后连接电极380。后连接电极380可包括沿着开口392的侧表面和下表面形成的含金属薄膜层382以及填充形成有含金属薄膜层382的开口392的含金属层384。尽管未示出,后连接电极380可通过以下步骤形成:沿着后绝缘层390的上表面和开口392的侧表面和下表面沉积用于形成含金属薄膜层382的薄金属材料层,通过沉积或电镀在薄金属材料层上方沉积厚度足以填充开口392的另一金属材料层,并且执行平坦化工艺,直至后绝缘层390的上表面暴露。

68.因此,可制造与图1b的半导体芯片100基本上相同的半导体芯片。

69.此外,在图3a至图3f的实施方式中,电源图案360和后连接电极380可全部通过对绝缘层进行构图以形成要形成电源图案360和后连接电极380的空间,然后利用形成电源图案360和后连接电极380的导电材料填充该空间来形成。然而,本公开不限于此,可使用通过对导电层进行构图,然后利用绝缘材料填充构图的导电层之间的空间来形成电源图案和/或后连接电极的方法。这将在下面参照图4a至图4d示例性地描述。

70.图4a至图4d是例示了根据本公开的另一实施方式的半导体芯片的制造方法的横截面图。将聚焦于与图3a和图3b的不同来进行描述。

71.参照图4a,可在载体基板(未示出)上方形成结构,该结构具有:主体部分410,其具

有前表面411和后表面412;初始贯通电极450,其穿透主体部分410并且突出到主体部分410的后表面412上方;布线部分420,其形成在主体部分410的前表面411下方;以及前连接电极430和前绝缘层440,其形成在布线部分420下方。初始贯通电极450可包括初始导电柱452以及围绕初始导电柱452的侧表面和上表面的初始间隔物454。

72.随后,可在主体部分410的后表面412上方形成含金属薄膜层462和含金属层464层叠的电源图案460。尽管未示出,电源图案460可通过在主体部分410的后表面412上方沉积用于形成含金属薄膜层462和含金属层464的材料层,并且使用掩模和蚀刻工艺对材料层进行构图来形成。另选地,尽管未示出,电源图案460可通过以下步骤形成:在主体部分410的后表面412上方沉积用于形成含金属薄膜层462的材料层,形成提供要形成含金属层464的空间的光刻胶图案,通过电镀在由光刻胶图案提供的空间中形成含金属层464,去除光刻胶图案,并且去除通过含金属层464暴露的材料层。在这种情况下,与上述实施方式的电源图案(参见图3e中的360)不同,含金属薄膜层462可仅接触含金属层464的下表面。

73.参照图4b,可沿其下轮廓在电源图案460、主体部分410的后表面412和初始贯通电极450的突起上方形成初始第一层间绝缘层472。作为示例,初始第一层间绝缘层472可包括氮化硅。

74.随后,可在初始第一层间绝缘层472上方形成初始第二层间绝缘层474至足以覆盖电源图案460和初始贯通电极450的突起的厚度。作为示例,初始第二层间绝缘层474可包括氧化硅。

75.参照图4c,可对图4b的所得结构执行平坦化工艺。可执行该平坦化工艺,直至电源图案460的上表面暴露。

76.结果,可形成填充电源图案460之间的空间的第一层间绝缘层472a和第二层间绝缘层474a以及具有导电柱452a和间隔物454a的贯通电极450a。第一层间绝缘层472a可沿着主体部分410的后表面412、电源图案460的侧表面和贯通电极450a的突起的侧表面形成。第一层间绝缘层472a可起到防止贯通电极450a的突起与电源图案460之间的金属扩散的作用。

77.参照图4d,可在图4c的所得结构上方形成后连接电极480。后连接电极480可包括含金属薄膜层482和含金属层484的层叠结构。尽管未示出,后连接电极480可通过在图4c的所得结构上方沉积用于形成含金属薄膜层482和含金属层484的材料层,并且通过掩模和蚀刻工艺对材料层进行构图来形成。另选地,尽管未示出,后连接电极480可通过以下步骤形成:在图4c的所得结构上方沉积用于形成含金属薄膜层482的材料层,形成提供要形成含金属层484的空间的光刻胶图案,通过电镀在由光刻胶图案提供的空间中形成含金属层484,去除光刻胶图案,并且去除通过含金属层484暴露的材料层。在这种情况下,与上述实施方式的后连接电极(参见图3f中的380)不同,含金属薄膜层482可仅接触含金属层484的下表面。

78.随后,可形成填充后连接电极480之间的空间的后绝缘层490。尽管未示出,后绝缘层490可通过在图4c的所得结构上方沉积厚度足以覆盖后连接电极480的绝缘材料层,并且执行平坦化工艺直至后连接电极480的上表面暴露来形成。

79.因此,可制造与图1b的半导体芯片100基本上相同的半导体芯片。

80.图5a和图5b是例示了根据本公开的另一实施方式的半导体芯片的示图。图5a是从

上方看时本实施方式的半导体芯片的平面图,图5b是沿着图5a的线b-b’截取的横截面图。在图5a中,为了描述方便,设置在后连接电极下方的贯通电极、连接图案和电源图案与设置在半导体芯片的最上部的后连接电极一起以虚线示出。将聚焦于与上述图1a和图1b的实施方式的不同来进行描述。

81.参照图5a和图5b,本实施方式的半导体芯片500可包括主体部分510、布线部分520、前连接电极530、前绝缘层540、贯通电极550、电源图案560、连接图案565、层间绝缘层570、后连接电极580和后绝缘层590。

82.主体部分510可具有前表面511和后表面512。布线部分520可形成在主体部分510的前表面511下方。前连接电极530和前绝缘层540可形成在布线部分520下方。

83.贯通电极550可具有从主体部分510的前表面511延伸到后表面512以穿透主体部分510的柱形状。贯通电极550的一端可连接到布线部分520,贯通电极550的另一端可连接到连接图案565。在平面图中,各个贯通电极550的宽度由标号w1指示。贯通电极550可包括电连接到电源图案560的第一贯通电极550a以及未电连接到电源图案560的第二贯通电极550b。

84.电源图案560可形成在主体部分510的后表面512上方,以在水平方向上与贯通电极550间隔开。电源图案560可通过第一后连接电极580a电连接到第一贯通电极550a并且可与第二贯通电极550b电绝缘。

85.连接图案565可在垂直方向上形成在与电源图案560相同的高度处。即,连接图案565可形成在主体部分510的后表面512上方。连接图案565可形成为与各个贯通电极550交叠并且连接。连接图案565和贯通电极550可彼此一一对应。连接图案565可包括连接到第一贯通电极550a的第一连接图案565a以及连接到第二贯通电极550b的第二连接图案565b。

86.连接图案565的宽度w3可大于贯通电极550的宽度w1并且可小于后连接电极580的宽度w2。在本实施方式中,第一连接图案565a可和与之相邻的电源图案560间隔开预定最小距离d3,但是本公开不限于此,第一连接图案565a的侧表面和与之相邻的电源图案560的侧表面可彼此接触。另一方面,第二连接图案565b可和与之相邻的电源图案560间隔开。即,第二连接图案565b的侧表面和与之相邻的电源图案560的侧表面可能不接触。连接图案565可由与电源图案560相同的金属或金属化合物形成。

87.层间绝缘层570可形成在主体部分510的后表面512上方以填充电源图案560与连接图案565之间的空间。

88.后连接电极580可包括连接到第一连接图案565a的第一后连接电极580a、连接到第二连接图案565b的第二后连接电极580b以及未连接到连接图案565的第三后连接电极580c。

89.第一后连接电极580a可形成为与各个第一连接图案565a交叠并且连接。因此,第一贯通电极550a可通过第一连接图案565a电连接到第一后连接电极580a。此外,第一后连接电极580a可同时与第一连接图案565a和与之相邻的电源图案560的一部分交叠并且连接。为此,第一后连接电极580a的宽度w2的值可大于第一连接图案565a的宽度w3与第一连接图案565a和与之相邻的电源图案560之间的最小距离d3之和。结果,第一后连接电极580a可将第一连接图案565a电连接到电源图案560。

90.第二后连接电极580b可形成为与各个第二连接图案565b交叠并且连接。因此,第

二贯通电极550b可通过第二连接图案565b电连接到第二后连接电极580b。第二后连接电极580b可通过不与第二连接图案565b周围的电源图案560交叠/连接而与电源图案560电绝缘。

91.第三后连接电极580c可形成为与第一后连接电极580a和第二后连接电极580b间隔开,而不与连接图案565交叠或连接。即,第三后连接电极580c可以是不用于信号传输或电源供给的虚设物。

92.后绝缘层590可形成在基于连接图案565的一个表面、电源图案560的一个表面和层间绝缘层570的一个表面形成的平坦表面上方,以填充后连接电极580之间的空间。

93.即使利用上述的半导体芯片500,也可获得上述实施方式的半导体芯片(参见图1a和图1b中的100)的效果。即,由于第一后连接电极580a同时连接到对应的第一连接图案565a和与之相邻的电源图案560,所以可容易地且稳定地执行通过这些元件的电源供给。

94.另外,当多个半导体芯片500在垂直方向上层叠时,可提供用于将垂直方向上相邻的半导体芯片500牢固地结合的混合结合结构。即,由于电源图案560和连接图案565设置在后连接电极580下方,所以在后连接电极580和后绝缘层590分别结合到另一半导体芯片(未示出)的前连接电极和前绝缘层的情况下,电源图案560和连接图案565不会不利地影响结合。

95.图6a至图6d是例示了根据本公开的另一实施方式的半导体芯片的制造方法的横截面图。

96.参照图6a,可在载体基板(未示出)上方形成结构,该结构具有:主体部分610,其具有前表面611和后表面612;布线部分620,其形成在主体部分610的前表面611下方;前连接电极630和前绝缘层640,其形成在布线部分620下方;以及初始贯通电极650,其穿透主体部分610并且在连接到布线部分620的同时突出到主体部分610的后表面612上方。初始贯通电极650可包括初始导电柱652和初始间隔物654。

97.随后,可沿其下轮廓在主体部分610的后表面612和初始贯通电极650的突起上方形成初始第一层间绝缘层672。作为示例,初始第一层间绝缘层672可包括氮化硅。

98.参照图6b,通过执行平坦化工艺以使得存在于初始主体部分610的后表面612上方的初始第一层间绝缘层672的上表面暴露,可形成具有导电柱652a和间隔物654a的贯通电极650a以及第一层间绝缘层672a。

99.作为该工艺的结果,贯通电极650a可具有穿透主体部分610和第一层间绝缘层672a的柱形状。第一层间绝缘层672a的上表面和贯通电极650a的一个表面可形成平坦表面。

100.随后,可在第一层间绝缘层672a上方形成第二层间绝缘层674和第三层间绝缘层676的层叠结构,其具有提供要形成电源图案和连接图案的空间的开口op。作为示例,第二层间绝缘层674和第三层间绝缘层676可分别包括氧化硅和氮化硅。

101.参照图6c,可形成填充在第二层间绝缘层674和第三层间绝缘层676的开口中的电源图案660和连接图案665。电源图案660可包括含金属薄膜层662和含金属层664,并且含金属薄膜层662可围绕含金属层664的侧表面和下表面。连接图案665可包括含金属薄膜层666和含金属层668,并且含金属薄膜层666可围绕含金属层668的侧表面和下表面。

102.参照图6d,可在图6c的所得结构上方形成后绝缘层690和后连接电极680,后绝缘

层690具有提供用于形成后连接电极680的空间的开口,后连接电极680形成在后绝缘层690的开口中。后连接电极680可包括含金属薄膜层682和含金属层684,并且含金属薄膜层682可围绕含金属层684的侧表面和下表面。

103.因此,可制造与图5b的半导体芯片100基本上相同的半导体芯片。

104.图7a至图7c是例示了根据本公开的另一示例性实施方式的半导体芯片的制造方法的横截面图。

105.参照图7a,可在载体基板(未示出)上方形成结构,该结构具有:主体部分710,其具有前表面711和后表面712;布线部分720,其形成在主体部分710的前表面711下方;前连接电极730和前绝缘层740,其形成在布线部分720下方;第一层间绝缘层772,其形成在主体部分710的后表面712上方;以及贯通电极750,其穿透主体部分710和第一层间绝缘层772。贯通电极750可包括导电柱752和间隔物754。

106.随后,可在主体部分710的后表面712上方形成含金属薄膜层762和含金属层764层叠的电源图案760以及含金属薄膜层766和含金属层768层叠的连接图案765。

107.参照图7b,可形成第二层间绝缘层774和第三层间绝缘层776以填充电源图案760与连接图案765之间的空间。第二层间绝缘层774可包括例如氮化硅,并且可沿着电源图案760的侧表面、连接图案765的侧表面和第一层间绝缘层772的上表面形成。第三层间绝缘层776可包括例如氧化硅,并且可具有由第二层间绝缘层774围绕的侧表面和下表面。

108.参照图7c,可在图7b的所得结构上方形成后连接电极780。后连接电极780可包括含金属薄膜层782和含金属层784的层叠结构。

109.随后,可形成填充后连接电极780之间的空间的后绝缘层790。

110.因此,可制造与图5b的半导体芯片500基本上相同的半导体芯片。

111.根据本公开的上述实施方式,可提供一种能够改进操作特性并方便制造工艺的半导体芯片以及包括其的半导体封装。

112.图8示出例示了包括采用根据实施方式的半导体封装中的至少一个的存储卡7800的电子系统的框图。存储卡7800包括诸如非易失性存储器装置的存储器7810以及存储控制器7820。存储器7810和存储控制器7820可存储数据或读出所存储的数据。存储器7810和存储控制器7820中的至少一个可包括根据所描述的实施方式的半导体封装中的至少一个。

113.存储器7810可包括应用了本公开的实施方式的技术的非易失性存储器装置。存储控制器7820可控制存储器7810,使得响应于来自主机7830的读/写请求,读出所存储的数据或者存储数据。

114.图9示出例示了包括根据所描述的实施方式的半导体封装中的至少一个的电子系统8710的框图。电子系统8710可包括控制器8711、输入/输出装置8712和存储器8713。控制器8711、输入/输出装置8712和存储器8713可通过提供数据移动的路径的总线8715彼此联接。

115.在实施方式中,控制器8711可包括一个或更多个微处理器、数字信号处理器、微控制器和/或能够执行与这些组件相同的功能的逻辑器件。控制器8711或存储器8713可包括根据本公开的实施方式的半导体封装中的一个或更多个。输入/输出装置8712可包括选自键区、键盘、显示装置、触摸屏等中的至少一个。存储器8713是用于存储数据的装置。存储器8713可存储要由控制器8711执行的数据和/或命令等。

116.存储器8713可包括诸如dram的易失性存储器装置和/或诸如闪存的非易失性存储器装置。例如,闪存可被安装到诸如移动终端或台式计算机的信息处理系统。闪存可构成固态盘(ssd)。在这种情况下,电子系统8710可在闪存系统中稳定地存储大量数据。

117.电子系统8710还可包括被配置为向通信网络发送数据以及从通信网络接收数据的接口8714。接口8714可为有线或无线型。例如,接口8714可包括天线或者有线或无线收发器。

118.电子系统8710可被实现为移动系统、个人计算机、工业计算机或者执行各种功能的逻辑系统。例如,移动系统可以是个人数字助理(pda)、便携式计算机、平板计算机、移动电话、智能电话、无线电话、膝上型计算机、存储卡、数字音乐系统和信息发送/接收系统中的任一个。

119.如果电子系统8710表示能够执行无线通信的设备,则电子系统8710可用在使用cdma(码分多址)、gsm(全球移动通信系统)、nadc(北美数字蜂窝)、e-tdma(增强时分多址)、wcdma(宽带码分多址)、cdma2000、lte(长期演进)或wibro(无线宽带互联网)的技术的通信系统中。

120.尽管出于例示性目的描述了各种实施方式,但对于本领域技术人员而言将显而易见的是,在不脱离以下权利要求中限定的本教导的精神和范围的情况下,可进行各种改变和修改。

121.相关申请的交叉引用

122.本技术要求2020年12月30日提交的韩国专利申请no.10-2020-0186907的优先权,其整体通过引用并入本文。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:孙晧荣

- 技术所有人:爱思开海力士有限公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、贺老师:氮化物陶瓷、光功能晶体材料及燃烧合成制备科学及工程应用

- 2、杨老师:工程电磁场与磁技术,无线电能传输技术

- 3、许老师:1.气动光学成像用于精确制导 2.人工智能方法用于数据处理、预测 3.故障诊断和健康管理

- 4、王老师:智能控制理论及应用;机器人控制技术

- 5、李老师:1.自旋电子学 2.铁磁共振、电磁场理论

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....