一种CIS芯片异形栅极结构及制作方法与流程

一种cis芯片异形栅极结构及制作方法

技术领域

1.本发明涉及一种cis(cmos image sensor)芯片工艺与应用仿真,尤其涉及一种cis芯片异形栅极结构及制作方法。

背景技术:

2.大尺寸cmos图像传感器(cis)由于其高灵敏度和曝光时间短,常常用作高速动态捕捉等场景,目前已经广泛应用于广播、体育、机器视觉和科学研究等领域.然而图像滞后问题是高速cis像素设计的挑战之一。为了减少图像延迟,过去的研究主要集中在抑制传输门边缘周围的电势垒或阱。尽管信号电荷从当栅极开启时,ppd中电子全部经传输沟道转移到fd中。但还有另一种可能引起图像延迟的来源。当栅极从开启状态到关闭时,沟道区域的电荷将移动到pd侧或fd的一面。这样的电荷反向到pd将产生图像滞后。

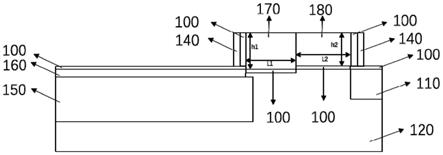

3.如图1

‑

a所示,在cis(cmos image sensor)芯片中连接光电二极管pd(photodiode)和浮动扩散区fd(floating diffusion)的栅极结构,作为pd中光生电子传输到fd的阀门通道,影响芯片各项重要参数如电子转移效率,图像滞后等。

4.综上,传统cis芯片栅极下沟道电势平坦,由于本身结构和工艺等问题可能会存在电势垒和电势阱等问题,降低了光生电荷的转移效率,甚至在靠近扎光二极管ppd(pinned photodiode)侧沟道具有高势垒时,会产生电子回流到ppd中从而会导致图像拖尾。

5.有鉴于此,特提出本发明。

技术实现要素:

6.本发明的目的是提供了一种cis芯片异形栅极结构及制作方法,以解决现有技术中存在的上述技术问题。

7.本发明的目的是通过以下技术方案实现的:

8.本发明的cis芯片异形栅极结构,包括设于衬底上的扎光二极管ppd和浮动扩散区fd,在靠近所述扎光二极管ppd的一侧设有宽度为l1、高度为h1的第一多晶硅栅极,在靠近所述浮动扩散区fd的一侧设有宽度为l2、高度为h2的第二多晶硅栅极;

9.所述第一多晶硅栅极为p型掺杂,所述第二多晶硅栅极为n型掺杂;

10.所述宽度l1与l2相同或不相同,所述高度h1与h2不相同。

11.上述的cis芯片异形栅极结构的制作方法,包括步骤:

12.a、在靠近所述扎光二极管ppd的一侧经过光刻和刻蚀得到沟槽,然后沉积栅极氧化层,再沉积多晶硅,在所述沟槽对应的位置通过光刻和离子注入进行p型掺杂;

13.b、在靠近所述浮动扩散区fd的一侧通过光刻和离子注入进行n型掺杂;

14.c、对于非栅极区域的多晶硅和氧化层,分别通过光刻和刻蚀去掉,再经过化学机械平坦化处理得到多晶硅;

15.d、经过氧化层沉积,氮化硅沉积,再由过刻蚀去掉表面氮化硅和氧化层,留下侧壁氧化硅

‑

氮化硅结构,最终得到所述异形栅极结构。

16.与现有技术相比,本发明所提供的cis芯片异形栅极结构及制作方法,通过光刻和刻蚀工艺形成异形栅极,再通过离子注入在靠近ppd一边p型掺杂,靠近fd一侧进行n型掺杂,得到栅极两侧不同的阈值电压,阶梯状的沟道结构增加了沟道长度,阶梯连接处的电势由高到低分布有效减少栅极关断后沟道电子向ppd回流。

附图说明

17.图1

‑

a为传统栅极结构示意图。

18.图1

‑

b为本发明实施例栅极结构示意图。

19.图2

‑

a,2

‑

b,2

‑

c,2

‑

d分别为按本发明实施例提供工艺步骤得到的截面形貌示意图。

20.图3为本发明实施例在栅极关断时电势分布仿真结果示意图。

21.图4

‑

a为本发明实施例在栅极关断时,在y=0~0.03um范围内等距离切20条水平线示意图。

22.图4

‑

b为本发明实施例20条水平线在x方向上的静电势分布示意图。

23.图5为本发明实施例提供工艺步骤示意图。

24.图中:

25.100 oxide

26.110 fd

27.120 p

‑

sub

28.130 polysilicon

29.140 sin

30.150 ppd

31.160 pinning p+

32.170 p+polysilicon

33.180 n+polysilicon

具体实施方式

34.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述;显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,这并不构成对本发明的限制。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

35.首先对本文中可能使用的术语进行如下说明:

36.术语“和/或”是表示两者任一或两者同时均可实现,例如,x和/或y表示既包括“x”或“y”的情况也包括“x和y”的三种情况。

37.术语“包括”、“包含”、“含有”、“具有”或其它类似语义的描述,应被解释为非排它性的包括。例如:包括某技术特征要素(如原料、组分、成分、载体、剂型、材料、尺寸、零件、部件、机构、装置、步骤、工序、方法、反应条件、加工条件、参数、算法、信号、数据、产品或制品等),应被解释为不仅包括明确列出的某技术特征要素,还可以包括未明确列出的本领域公知的其它技术特征要素。

38.术语“由

……

组成”表示排除任何未明确列出的技术特征要素。若将该术语用于权利要求中,则该术语将使权利要求成为封闭式,使其不包含除明确列出的技术特征要素以外的技术特征要素,但与其相关的常规杂质除外。如果该术语只是出现在权利要求的某子句中,那么其仅限定在该子句中明确列出的要素,其他子句中所记载的要素并不被排除在整体权利要求之外。

39.术语“质量份”是表示多个组分之间的质量比例关系,例如:如果描述了x组分为x质量份、y组分为y质量份,那么表示x组分与y组分的质量比为x:y;1质量份可表示任意的质量,例如:1质量份可以表示为1kg也可表示3.1415926kg等。所有组分的质量份之和并不一定是100份,可以大于100份、小于100份或等于100份。除另有说明外,本文中所述的份、比例和百分比均按质量计。

40.除另有明确的规定或限定外,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如:可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本文中的具体含义。

41.当浓度、温度、压力、尺寸或者其它参数以数值范围形式表示时,该数值范围应被理解为具体公开了该数值范围内任何上限值、下限值、优选值的配对所形成的所有范围,而不论该范围是否被明确记载;例如,如果记载了数值范围“2~8”时,那么该数值范围应被解释为包括“2~7”、“2~6”、“5~7”、“3~4和6~7”、“3~5和7”、“2和5~7”等范围。除另有说明外,本文中记载的数值范围既包括其端值也包括在该数值范围内的所有整数和分数。

42.术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述和简化描述,而不是明示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本文的限制。

43.本发明实施例中未作详细描述的内容属于本领域专业技术人员公知的现有技术。本发明实施例中未注明具体条件者,按照本领域常规条件或制造商建议的条件进行。本发明实施例中所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

44.一种cis芯片异形栅极结构,包括设于衬底上的扎光二极管ppd和浮动扩散区fd,其特征在于,在靠近所述扎光二极管ppd的一侧设有宽度为l1、高度为h1的第一多晶硅栅极,在靠近所述浮动扩散区fd的一侧设有宽度为l2、高度为h2的第二多晶硅栅极;

45.所述第一多晶硅栅极为p型掺杂,所述第二多晶硅栅极为n型掺杂;

46.所述宽度l1与l2相同或不相同,所述高度h1与h2不相同。

47.所述第一多晶硅栅极与第二多晶硅栅极的上表面平齐,所述第二多晶硅栅极的下表面与所述浮动扩散区fd的上表面平齐,所述第一多晶硅栅极的下表面向下深入到沟槽中。

48.上述的cis芯片异形栅极结构的制作方法,如图2a至图2d及图5所示,包括步骤:

49.a、在靠近所述扎光二极管ppd的一侧经过光刻和刻蚀得到沟槽,然后沉积栅极氧化层,再沉积多晶硅,在所述沟槽对应的位置通过光刻和离子注入进行p型掺杂;

50.b、在靠近所述浮动扩散区fd的一侧通过光刻和离子注入进行n型掺杂;

51.c、对于非栅极区域的多晶硅和氧化层,分别通过光刻和刻蚀去掉,再经过化学机械平坦化处理得到多晶硅;

52.d、经过氧化层沉积,氮化硅沉积,再由过刻蚀去掉表面氮化硅和氧化层,留下侧壁氧化硅

‑

氮化硅结构,最终得到所述异形栅极结构。

53.所述步骤a中,所述沟槽深度为0.02um,所述氧化层厚度为71.5a,所述多晶硅厚度为2000a;

54.所述步骤c中,所述化学机械平坦化处理得到的多晶硅厚度为1450a。

55.为了更加清晰地展现出本发明所提供的技术方案及所产生的技术效果,下面以具体实施例对本发明实施例所提供的进行详细描述。

56.实施例1

57.本发明的一个实施例涉及栅极的形成,栅极p+n+掺杂,以及相应仿真栅极沟道电势对比。

58.如图1

‑

b所示,本发明从栅极结构出发,提供一种异形栅极结构,靠近ppd一侧l1宽带内形成第一高度h1的多晶硅栅极,在靠近fd另一侧,形成宽度为l2的第二高度h2多晶硅栅极,通过不同的栅极高度和掺杂得到不同阈值电压,在栅极关断时,有效控制沟道电子向ppd回流,提高成像质量。

59.具体实施例的制作方法,如图2

‑

a至图2

‑

d及图5所示:

60.1.栅极沟槽形成,首先在栅极对应靠近ppd的栅极一半宽度l1位置,经过光刻和刻蚀得到深度为0.02um沟槽,然后沉积栅极氧化层厚度为71.5a,再沉积2000a多晶硅;

61.2.在栅极沟槽位置对应位置通过光刻和离子注入进行p型掺杂,同样在栅极位置另一侧l2宽度范围内通过光刻和离子注入进行n型掺杂;

62.3.栅极形成,对于非栅极区域的多晶硅和氧化层,分别通过光刻和刻蚀去掉,再经过化学机械平坦化(cmp,chemical

‑

mechanical planarization)处理得到厚度为1450a的多晶硅厚度;

63.4.经过氧化层沉积,氮化硅沉积,再由过刻蚀(over etch)去掉表面氮化硅和氧化层,留下侧壁氧化硅

‑

氮化硅结构,最终得到此异形栅极结构。

64.按照半导体物理学中的定义,p型掺杂的多晶硅的费米能级大于n型掺杂,右侧n型掺杂多晶硅功函数差小于左侧p型掺杂,因此栅极左侧阈值电压大于右侧结构,进而能够在传输管沟道形成由小到大的梯度电势分布,减小沟道电子回流,有效抑制图像滞后。如图3所示,为本实施例的栅极关断后的电势分布仿真结果,在关断时左侧深沟道下的电势明显小于右侧沟道电势,具体可见分别在沟道内水平方向取值得到的在的电势分布(图4a至图4b)。

65.如图4a所示在y方向从0.03到0的位置上,也就是左右侧沟道垂直方向等份切20条水平线,图4b显示的是这些水平线在x方向上不同位置的静电势大小,虚线位置是栅极沟槽靠近右侧阶梯位置,由图可以清晰看出,当栅极关断时深沟槽处沟道静电势明显小于右侧正常沟道处静电势。

66.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,

都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。本文背景技术部分公开的信息仅仅旨在加深对本发明的总体背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1