一种基于硅通孔的延迟均衡器件

1.本发明属于三维集成电路技术领域,涉及一种基于硅通孔的延迟均衡器件。

背景技术:

2.目前为止,我们所讨论的网络都具有被用来获得所需的振幅与频率的特征。全通滤波器也是很重要的一类,这类电路网络具有平坦的频率响应,但引入了一个固定的相移与频率,全通滤波器通常被称为延迟均衡器。

3.在延迟器件方面,模拟组延迟均衡器可使用全通滤波器。理想形式的全通网络具有恒定的振幅和特定的组延迟响应,任意的组延迟响应可以使用组延迟均衡器来实现。均衡器可以用于更窄的带宽和更高的选择性滤波器。随着微电子技术的发展,晶体管的特征尺寸逐渐达到物理极限,集成电路的设计、可靠性都受到严重影响,元器件的集成难度加大。对于高阶的延迟网络,将元器件集成时由于复杂的电路网络,面临集成的结构面积大等问题。

4.tsv技术提供了一条新思路,此设计中,将电感器件通过tsv实现,不但在低频时有稳定的延迟性能、低损耗,更有效提高了延迟器件的集成度。

技术实现要素:

5.本发明的目的是提供一种基于硅通孔的延迟均衡器件,该均衡器件不但在低频是有稳定的延迟性能、低损耗,而且结构紧凑,集成度高。

6.本发明所采用的技术方案是,一种基于硅通孔的延迟均衡器件,包括tsv电感l1,tsv电感l1分别连接tsv电感l2、双层交指电容c1、双层交指电容c2;tsv电感l2分别连接双层交指电容c1、双层交指电容c3及tsv电感l3;双层交指电容c3分别与双层交指电容c5及双层交指电容c4连接;双层交指电容c4分别与tsv电感l3、tsv电感l4及双层交指电容c6连接;双层交指电容c6分别与双层交指电容c7及双层交指电容c8连接;双层交指电容c7与tsv电感l4连接;双层交指电容c5与tsv电感l5连接;双层交指电容c8与tsv电感l6连接。

7.本发明的特点还在于:

8.tsv电感l1、tsv电感l2、tsv电感l3、tsv电感l4、tsv电感l5、tsv电感l6均通过若干个tsv呈螺旋状绕制形成,各tsv之间通过rdl层依次首尾相接。

9.tsv电感l1中的各tsv的螺旋绕制方向与tsv电感l2中各tsv的螺旋绕制方向相反。

10.双层交指电容c1、双层交指电容c2、双层交指电容c3、双层交指电容c4、双层交指电容c5、双层交指电容c6、双层交指电容c7、双层交指电容c8的结构相同,均包括:电容极板plate1、电容极板plate2、电容极板plate3、电容极板plate4;

11.电容极板plate1和电容极板plate3构成同一层之间的交指电容;电容极板plate2和电容极板plate4构成同一层之间的交指电容;

12.电容极板plate1和电容极板plate4连接,电容极板plate2和电容极板plate3连接。

13.tsv电感l1的起始端port1与双层交指电容c1中的电容极板plate2连接;

14.tsv电感l1的末端port2分别与tsv电感l2的末端port2、双层交指电容c2中的电容极板plate2连接;

15.tsv电感l2的起始端port1分别与双层交指电容c1中的电容极板plate4、双层交指电容c3中的电容极板plate2、tsv电感l3的起始端port1连接;

16.双层交指电容c3中的电容极板plate4分别与双层交指电容c5中的电容极板plate2、双层交指电容c4中的电容极板plate2;

17.双层交指电容c4中的电容极板plate4分别与tsv电感l3的末端port2、tsv电感l4的起始端port1及双层交指电容c6中的电容极板plate2;

18.双层交指电容c6中的电容极板plate4分别与双层交指电容c7中的电容极板plate2、双层交指电容c8中的电容极板plate2连接;

19.双层交指电容c7中的电容极板plate4与tsv电感l4的末端port2连接;

20.双层交指电容c5中的电容极板plate4与tsv电感l5的起始端port1连接;

21.双层交指电容c8中的电容极板plate4与tsv电感l6的末端port2连接;

22.tsv电感l5的末端port2、tsv电感l6的起始端port1及双层交指电容c2中的电容极板plate4均接地。

23.本发明的有益效果如下:

24.1.电感采用tsv结构,tsv位于硅基衬底中,与现有普遍的硅工艺产品相兼容;

25.2.采用tsv电感器件,电感值可调,器件利用率高;

26.3.电感器件采用tsv技术实现的三维结构,与传统的二维螺旋结构相比,损耗低,占用面积小,集成度高;

27.4.电容器件采用双层交指电容结构,相对于单层结构来说,占用面积小。

附图说明

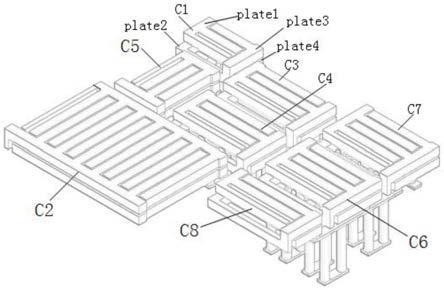

28.图1是本发明一种基于硅通孔的延迟均衡器件的三维结构示意图;

29.图2是本发明一种基于硅通孔的延迟均衡器件中各tsv电感之间的连接结构示意图;

30.图3(a)~(f)是本发明一种基于硅通孔的延迟均衡器件中各tsv电感的绕制俯视图;

31.图4是本发明一种基于硅通孔的延迟均衡器件中单个tsv的结构示意图;

32.图5是本发明一种基于硅通孔的延迟均衡器件中单个双层交指电容的主视图;

33.图6是本发明一种基于硅通孔的延迟均衡器件中单个双层交指电容的三维结构示意图;

34.图7是本发明一种基于硅通孔的延迟均衡器件中单个双层交指电容中电容极板plate2与电容极板plate4之间的结构示意图;

35.图8是本发明一种基于硅通孔的延迟均衡器件的电路图;

36.图9为本发明一种基于硅通孔的延迟均衡器件的结构模型仿真曲线图。

37.图中,1.铜柱,2.二氧化硅层,3.硅基衬底层,4.上层rdl,5.下层rdl,6.互连键,7.互连层。

具体实施方式

38.下面结合附图和具体实施方式对本发明进行详细说明。

39.本发明一种基于硅通孔的延迟均衡器件,为六阶的50ps等延迟线的电路网络结构,根据所需延迟计算电路网络中的相关器件值,并进行结构设计。

40.本发明一种基于硅通孔的延迟均衡器件,整体结构从上到下依次为八个双层交指电容、互连键6、互连层7、互连键6及六个tsv电感;

41.如图1所示,包括八个双层交指电容分别为:双层交指电容c1、双层交指电容c2、双层交指电容c3、双层交指电容c4、双层交指电容c5、双层交指电容c6、双层交指电容c7、双层交指电容c8;

42.六个tsv电感分别为:tsv电感l1、tsv电感l2、tsv电感l3、tsv电感l4、tsv电感l5、tsv电感l6均通过若干个tsv呈螺旋状绕制形成,各tsv之间通过rdl层依次首尾相接。

43.如图2、3所示,具体对六个tsv电感的结构进行说明:图3中port1表示各tsv电感螺旋绕制的起始端;port2表示各tsv电感的螺旋绕制末端。

44.图3(a)为tsv电感l1的绕制结构俯视图,其中tsv电感l1采用6个tsv依次收尾相接呈螺旋状绕制而成;结合图2可知,tsv电感l1中每个tsv的上端连接有上层rdl4,tsv电感l1中的每个tsv的下端连接下层rdl5;tsv电感l1中,下层rdl5长度为64um、上层rdl4的长度从tsv电感l1的起始端port1到tsv电感l1的末端port2依次为32um、61.5um、61.5um、32um。

45.图3(b)为tsv电感l2的绕制结构俯视图;tsv电感l2采用6个tsv依次收尾相接呈螺旋状绕制而成;结合图2可知,tsv电感l2中的每个tsv的上端连接有上层rdl4,每个tsv的下端连接下层rdl5;

46.tsv电感l2和tsv电感l1的尺寸相同,但绕线方式不同;

47.图3(c)为tsv电感l3的绕制俯视图;其中tsv电感l3采用4个tsv依次收尾相接呈螺旋状绕制而成;结合图2可知,tsv电感l3中每个tsv的上端连接有上层rdl4,tsv电感l3中的每个tsv的下端连接下层rdl5;

48.tsv电感l3中,下层rdl5长度为30um、上层rdl4的长度从tsv电感l3的起始端port1到tsv电感l3的末端port2依次为20um、40um、20um;

49.图3(d)为tsv电感l4的绕制俯视图;其中tsv电感l4采用4个tsv依次收尾相接呈螺旋状绕制而成;结合图2所示,tsv电感l4中每个tsv的上端连接有上层rdl4,tsv电感l4中的每个tsv的下端连接下层rdl5;

50.tsv电感l4中,下层rdl5长度为30um、上层rdl4的长度从tsv电感l4的起始端port1到tsv电感l4的末端port2依次为17um、40um、10um;

51.图3(e)为tsv电感l5的绕制俯视图;其中tsv电感l5采用4个tsv依次收尾相接呈螺旋状绕制而成;结合图2所示,tsv电感l5中每个tsv的上端连接有上层rdl4,tsv电感l5中的每个tsv的下端连接下层rdl5;

52.tsv电感l5中,下层rdl5长度为30um、上层rdl4的长度从tsv电感l5的起始端port1到tsv电感l5的末端port2依次为16um、40um、16um;

53.图3(f)为tsv电感l6的绕制俯视图;其中tsv电感l6采用4个tsv依次收尾相接呈螺旋状绕制而成;结合图2所示,tsv电感l6中每个tsv的上端连接有上层rdl4,tsv电感l6中的每个tsv的下端连接下层rdl5;

54.tsv电感l6中,下层rdl5长度为32um、上层rdl4从tsv电感l6的起始端port1到tsv电感l6的末端port2依次为22um、41um、22um。考虑器件之间的相关互连,可以根据所需要的值或结构进行调整。

55.如图4所示,每个tsv(硅通孔)包括铜柱1,铜柱1外依次同轴包裹有二氧化硅层2及硅基衬底层3;铜柱1的直径为10um,铜柱1的高度为96um,在铜柱1的外围有一层0.3um的二氧化硅层2的薄层将铜柱1包裹,在tsv构成的各电感部分中,tsv的横向中心距为20um,rdl宽为10um,厚度为3um。

56.双层交指电容c1、双层交指电容c2、双层交指电容c3、双层交指电容c4、双层交指电容c5、双层交指电容c6、双层交指电容c7、双层交指电容c8的结构均相同,根据电容值不同,8个双层交指电容的尺寸不同;如图5所示,均包括:电容极板plate1、电容极板plate2、电容极板plate3、电容极板plate4;

57.电容极板plate1和电容极板plate3构成同一层之间的交指电容;电容极板plate2和电容极板plate4构成同一层之间的交指电容;

58.电容极板plate1和电容极板plate4连接,电容极板plate2和电容极板plate3连接。

59.各tsv电感与各双层交指电容之间连接时采用互连层7进行连接;

60.各tsv电感与各双层交指电容之间连接时采用从上至下依次为互连键6、互连层7及互连键6的连接方式进行连接。

61.电容极板plate1和电容极板plate2、电容极板plate3和电容极板plate4各自之间构成金属(cu)-氧化物(二氧化硅)-金属(cu)(mim)电容;

62.如图6、7所示,电容极板plate1和电容极板plate4相接(铜块net2的一端和电容极板plate1内侧相接,铜块net2的另一端和铜块net3相接;铜块net5将铜块net3和电容极板plate4内侧相接);

63.电容极板plate2和电容极板plate3相接(通过铜块net4将同一层的和电容极板plate2相接的铜块net1接到上层的电容极板plate3上)。

64.各双层交指电容结构相同,各rdl(铜块net1、铜块net2、铜块net3、铜块net4、铜块net5为将plate金属板相接的rdl)宽10um、高10um、间距2um、上下层间距2um、指到极板距离d为2um。电容介质为二氧化硅。

65.各电容指数、指长aw不同,双层交指电容c3、双层交指电容c4(0.150pf)指长73.5um、指数3;双层交指电容c1(0.071pf)指长40.5um、指数2;双层交指电容c2(0.784pf)指长92.2um、指数13;双层交指电容c5(0.122pf)指长53.8um、指数3;双层交指电容c6、c7(0.190pf)指长69um、指数4;双层交指电容c8(0.0984pf)指长71um、指数2。也可采用单层的交指电容来实现此功能,相对于单层电容来说,双层电容在所占用的面积有很大优势。

66.电容极板plate1、电容极板plate2、电容极板plate3、电容极板plate4材料均为金属cu;指长aw待设计,指到极板的距离d为2um。tsv电感l1的起始端port1与双层交指电容c1中的电容极板plate2连接;

67.tsv电感l1的末端port2分别与tsv电感l2的末端port2、双层交指电容c2中的电容极板plate2连接;

68.tsv电感l2的起始端port1分别与双层交指电容c1中的电容极板plate4、双层交指

电容c3中的电容极板plate2、tsv电感l3的起始端port1连接;

69.双层交指电容c3中的电容极板plate4分别与双层交指电容c5中的电容极板plate2、双层交指电容c4中的电容极板plate2;

70.双层交指电容c4中的电容极板plate4分别与tsv电感l3的末端port2、tsv电感l4的起始端port1及双层交指电容c6中的电容极板plate2;

71.双层交指电容c6中的电容极板plate4分别与双层交指电容c7中的电容极板plate2、双层交指电容c8中的电容极板plate2连接;

72.双层交指电容c7中的电容极板plate4与tsv电感l4的末端port2连接;

73.双层交指电容c5中的电容极板plate4与tsv电感l5的起始端port1连接;

74.双层交指电容c8中的电容极板plate4与tsv电感l6的末端port2连接;

75.tsv电感l5的末端port2、tsv电感l6的起始端port1及双层交指电容c2中的电容极板plate4均接地。

76.图8为本发明一种基于硅通孔的延迟均衡器件的电路结构,图中tsv电感l1和tsv电感l2两者之间存在互感,耦合系数k为0.314。

77.耦合系数的计算公式如下:

[0078][0079]

其中,q为极点;

[0080]

如下表1为本发明一种基于硅通孔的延迟均衡器件的各器件数值;

[0081]

表1

[0082][0083]

图9为本发明一种基于硅通孔的延迟均衡器件的结构模型仿真曲线图;图9中插入损耗s21》-2db,结构传输效率高,低损耗;groupdelay曲线参数在低频3ghz之前延迟变化小于10%,3ghz之后延迟变化小于25%。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1