用于制造晶圆级芯片尺寸封装(WLCSP)的方法与流程

用于制造晶圆级芯片尺寸封装(wlcsp)的方法

1.相关申请的交叉参考

2.本技术要求于2020年10月21日提交的美国专利临时申请第63/094,424号的优先权,其公开内容通过引用并入本文。

技术领域

3.本发明总体上涉及一种用于制造集成电路封装的方法,并且具体地,涉及一种用于制造晶圆级芯片尺寸封装(wlcsp)的方法。

背景技术:

4.参考图1,图1示意性地示出(不一定按比例)晶圆级芯片尺寸封装(wlcsp)10的截面,其包括具有顶表面14、底表面16和厚度18的半导体衬底12。例如,半导体衬底12可包括块体衬底或绝缘体上半导体(soi)衬底。集成电路装置20被设置在半导体衬底12的顶表面14上和顶表面下方(例如,该集成电路装置包括衬底内的掺杂区域、晶体管栅极结构和衬底之上的金属接触件)。在半导体衬底12的顶表面14处,预金属化介电(pmd)层覆盖集成电路装置20。由多个金属化层(如本领域已知的,包括位于绝缘材料内的导线、通孔和接合焊盘26)形成的互连结构22被设置在pmd层之上,并被配置为电互连集成电路装置20。在互连结构22的最上层的顶部上设置具有暴露接合焊盘26的开口的钝化层24。从衬底12的底表面16到具有暴露的接合焊盘26的钝化层的整体结构在本领域称为半导体管芯28。封装10还包括再分布层(rdl),其在本领域也称为中介层,以在管芯28的接合焊盘26与用于封装的凸块下金属化(ubm)焊盘30之间提供电气连接线。再分布层rdl之上的钝化层32包括暴露ubm焊盘30的开口。焊球34被安装至每个ubm焊盘30。一般而言,在常见实施方式中,球34的厚度小于衬底12的厚度18(并且更具体地,衬底12的厚度约为球34的厚度的两倍)。

5.在许多空间敏感应用中,封装集成电路的总厚度尽可能薄是至关重要的。因此,业界正在努力通过减小半导体衬底12的厚度18来减小晶圆级芯片尺寸封装10的总厚度。这如图2所示。例如,在常见实施方式中,球34的厚度大于厚度18。然而,减小衬底12的厚度的一个问题是:在附接焊球的位置处,裂纹40将形成在管芯28中。

6.本领域需要一种工艺或方法,用于制造支持使用减薄的半导体衬底12的晶圆级芯片尺寸封装(wlcsp)。

技术实现要素:

7.在一个实施例中,一种工艺包括:生产前端制程(feol)衬底晶圆,其包括具有第一厚度和背表面的半导体衬底晶圆以及预金属化介电层;在预金属化介电层之上生产后端制程(beol)结构,所述beol结构包括第一钝化层,第一钝化层包括用于接合焊盘的开口;在所述第一钝化层之上形成再分布层,其中再分布层将接合焊盘电连接到凸块下金属化焊盘;形成第二钝化层,第二钝化层包括用于凸块下金属化焊盘的开口,并由此制造生产晶圆;开放从生产晶圆的顶表面向下延伸到仅部分地穿过半导体衬底晶圆的深度的沟槽;在所述凸

块下金属化焊盘处执行凸块化工艺之前,将第一柄状件(handle)附接到生产晶圆的顶表面;在半导体衬底晶圆的背表面处从第一厚度减薄至第二厚度,到达沟槽并形成多个晶圆级芯片尺寸封装;将第二柄状件附接到所述多个晶圆级芯片尺寸封装的底表面;移除所述第一柄状件,以暴露凸块下金属化焊盘;以及执行所述凸块化工艺,以在每个暴露的凸块下金属化焊盘处形成焊球。

8.在一个实施例中,一种工艺包括:开放从生产晶圆的顶表面向下延伸穿过划线区域到达仅部分地穿过半导体衬底的深度的沟槽,所述沟槽界定集成电路位置;在执行凸块化工艺之前,将第一柄状件附接到生产晶圆的顶表面;在半导体衬底的背表面处减薄以到达沟槽并在每个集成电路位置处形成晶圆级芯片尺寸封装;将第二柄状件附接到用于晶圆级芯片尺寸封装的减薄的半导体衬底的底表面;移除所述第一柄状件,以在顶表面处暴露凸块下金属化焊盘;以及执行所述凸块化工艺,以在每个暴露的凸块下金属化焊盘处形成焊球。

附图说明

9.为了更好地理解实施例,现在仅通过示例的方式参考附图,其中:

10.图1和图2示出了晶圆级芯片尺寸封装(wlcsp)的示意性截面;以及

11.图3a至图3h示出了用于制造晶圆级芯片尺寸封装(wlcsp)的方法中的步骤。

具体实施方式

12.现在参考图3a至图3h,示出了用于制造晶圆级芯片尺寸封装(wlcsp)的方法中的步骤。使用截面图示出这些步骤。应注意,尽管以一定程度的精度示出特定结构(如本文所述)之间的比例关系,但不必按比例绘制。对于优选实施方式,图3a至图3h的工艺步骤按顺序示出。

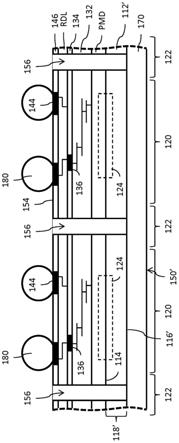

13.图3a示出了具有顶表面114、底表面116和厚度118的半导体衬底晶圆112。晶圆112包括由划线(或切割)区域122界定的多个集成电路位置120。例如,半导体衬底晶圆112可包括块体衬底晶圆或绝缘体上半导体(soi)衬底晶圆。每个集成电路位置120都包括设置在半导体衬底晶圆112的顶表面114上和下的集成电路装置124(例如,该集成电路装置包括衬底内的掺杂区域、晶体管栅极结构和衬底之上的金属接触件)。在半导体衬底112的顶表面114处,预金属化介电(pmd)层覆盖集成电路装置124。用于形成图3a所示结构的工艺在本领域通常被称为前端制程(feol)工艺,其生产对应的feol晶圆130。

14.图3b示出了对feol晶圆130执行的进一步晶圆尺寸处理的结果,其中,在pmd层之上设置由多个金属化层(如本领域已知的,包括位于绝缘材料内的导线、通孔和接合焊盘136)形成的互连结构132。导线和通孔被配置为电互连集成电路装置124。在互连结构132的最上层的顶部上设置具有暴露接合焊盘136的开口的钝化层134。用于在feol晶圆130的顶部上形成图3b所示的附加结构的工艺在本领域通常被称为后端制程(beol)工艺,其生产对应beol晶圆140。

15.图3c示出了对beol晶圆140执行的进一步晶圆尺寸处理的结果,其中使用传统rdl沉积工艺添加再分布层(rdl)(其在本领域也称为中介层),以在接合焊盘136和凸块下金属化(ubm)焊盘144之间提供电连接线。然后,钝化层146沉积在再分布层rdl之上,并被配置为

包括暴露ubm焊盘144的开口。用于在beol晶圆140的顶部上形成图3c所示的附加结构的工艺制造生产晶圆150。

16.然后,对生产晶圆150执行以下步骤。接下来,从生产晶圆150的顶表面154开始,在每个划线(或切割)区域122的位置处在生产晶圆150中切入沟槽156,以便完成晶圆150的部分切割。结果如图3d所示。机械切割工艺可用于形成沟槽156。在该工艺步骤中,具有实现穿透衬底12的精确部分深度的能力的机械切割工具被用于切割。控制切割深度至关重要。沟槽156具有从顶表面154开始、完全延伸穿过钝化层146、再分布层rdl、钝化层134、互连结构132和预金属化介电pmd层的深度。沟槽156进一步仅部分地延伸到半导体衬底晶圆112中到达深度“d”,其至少且更优选地大于晶圆级芯片尺寸封装(wlcsp)的半导体衬底的最终期望厚度,但不大于衬底晶圆112的厚度。

17.将玻璃支撑晶圆160(也称为玻璃柄状件)接合到生产晶圆150的顶表面154。通过层压工艺将具有粘附力的支撑晶圆160接合到表面154。结果如图3e所示。

18.然后,在半导体衬底晶圆112的底表面116处执行衬底背侧减薄,以便将厚度118减小至减薄厚度118’,基本上完成在沟槽156限定的位置对生产晶圆150的切割,并且在每个集成电路位置120处制造晶圆级芯片尺寸封装165。在优选实施方式中,该减薄通过使用砂轮的机械背侧研磨来执行。备选地,可以使用合适的机械/化学工艺。晶圆级芯片尺寸封装165通过其正侧与玻璃支撑晶圆160的附接,在集成电路位置120处彼此保持相对位置。结果如图3f所示。

19.然后,将又一支撑晶圆170(也称为柄状件)接合到晶圆级芯片尺寸封装165的底表面116’。通过层压工艺将具有粘附力的支撑晶圆170接合到表面116’。在一种实施方式中,又一支撑晶圆可由玻璃制成。又一支撑晶圆170的材料至少对焊料的回流(下面将进一步解释)使用的温度(例如,至少200℃)耐热是至关重要的。在背侧接合玻璃支撑晶圆170之后,使用针对每个晶圆级芯片尺寸封装165的清洗工艺,使正侧的玻璃支撑晶圆160与钝化层146的顶表面154断开接合。结果如图3g所示。

20.接下来,针对每个晶圆级芯片尺寸封装165,在顶表面154处(即,在钝化层146的顶表面处)执行凸块化工艺,在每个ubm焊盘144上滴落焊料。在滴落焊料之后,在一定温度(例如,近似200℃)下执行热处理,以便熔化和回流沉积的焊料,然后进行冷却以在每个ubm焊盘144处形成焊球180。结果如图3h所示。应注意,结构146、rdl、134、132、pmd的厚度在尺寸上相对于衬底112’和球180的尺寸被放大。更精确地示出衬底112'和球180之间的一般尺寸关系。

21.然后,将晶圆级芯片尺寸封装165从支撑晶圆170移除。本领域技术人员熟知的无弹射磁带和卷轴(tnr)工艺可用于该移除。该工艺是一种标准的wlcsp工艺,用于拾取从晶圆切割的各个管芯并放入相应载带袋中,然后将载带卷绕到行业标准卷轴中。

22.图3a-图3h所示工艺与半导体衬底晶圆的背面研磨在凸块化工艺之后执行(例如,参见kamphuis的美国专利第9,466,585号和kim的美国专利申请公开第2019/0172814号)的传统工艺相比具有许多优点。这些现有技术工艺涉及衬底开裂的重大风险。然而,在图3a-图3h的工艺中,凸块化工艺有利地发生在半导体衬底晶圆的减薄之后,从而最小化(如果不是消除的话)开裂的风险。此外,图3a-图3h的工艺在执行背面减薄和正面凸块化操作之前执行半导体衬底晶圆的部分切割,以便允许使用直接附接到正面的用于背面研磨的支撑柄

状件,而不介入焊料凸块。

23.尽管已在附图和前述描述中详细说明并描述了本发明,但这些说明和描述被视为说明性或示例性的,而非限制性的;本发明不限于所公开的实施例。本领域技术人员根据对附图、公开和所附权利要求的研究在实践所要求发明的过程中可理解和实现所公开实施例的其他变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1