1.本公开涉及半导体芯片技术领域,尤其涉及一种半导体结构及其制备方法、三维存储器。

背景技术:

2.随着存储单元的特征尺寸接近工艺下限,平面工艺和制造技术变得具有挑战性且成本高昂,这造成2d或者平面nand闪存的存储密度接近上限。

3.为克服2d或者平面nand闪存带来的限制,业界已经研发了具有三维结构的存储器(3d nand),3d nand存储器具有栅极隔槽(gate line slit,简称gls),以在存储器上划分多个存储块。

4.在相关技术中,通过在相邻两个栅极隔槽之间形成顶部选择栅切线(top select gate cut,简称tsg cut),可进一步将存储块划分为多个子存储块,以提高有效沟道孔(channel hole,简称ch)的数量,增加存储器的存储密度。如何在保证器件良率和合理的工艺难度的前提下,在相邻两个栅极隔槽之间形成多条顶部选择栅切线,成为领域内亟待解决的问题。

技术实现要素:

5.本公开的实施例提供一种半导体结构及其制备方法、三维存储器,旨在至少部分解决如何在相邻两个栅极隔槽之间形成多条顶部选择栅切线的问题。

6.为达到上述目的,本公开的实施例采用如下技术方案:

7.一方面,提供一种半导体结构的制备方法。所述制备方法包括:在衬底上形成堆叠结构,所述堆叠结构包括层叠设置的多个膜层对,每个膜层对包括相邻的绝缘层和第一牺牲层;形成多个栅极隔槽和多个选择栅沟槽,相邻两个栅极隔槽之间设置有多个选择栅沟槽,所述栅极隔槽贯穿所述堆叠结构,所述选择栅沟槽贯穿所述堆叠结构中远离所述衬底一侧的至少一个所述绝缘层和至少一个所述第一牺牲层;去除所述第一牺牲层以形成空腔,沉积栅导电材料,以在所述空腔内形成栅导电层;去除所述选择栅沟槽中的栅导电材料;在所述选择栅沟槽内形成顶部选择栅切线。

8.在一些实施例中,所述形成多个栅极隔槽和多个选择栅沟槽,包括:在所述堆叠结构中形成所述多个选择栅沟槽;形成第二牺牲层,所述第二牺牲层填充所述多个选择栅沟槽,并覆盖所述堆叠结构远离所述衬底的表面;在所述堆叠结构中形成所述多个栅极隔槽。

9.在一些实施例中,所述第二牺牲层与所述第一牺牲层的材料相同。

10.在一些实施例中,在所述去除所述选择栅沟槽中的栅导电材料之前,还包括:去除所述栅极隔槽内及所述堆叠结构远离所述衬底的表面上的栅导电材料;形成覆盖所述栅极隔槽内表面的第一保护层。

11.在一些实施例中,所述去除所述栅极隔槽内及所述堆叠结构远离所述衬底的表面上的栅导电材料,包括:去除所述栅极隔槽侧壁和底部、及所述堆叠结构远离所述衬底的表

面上的栅导电材料;去除所述栅导电层的靠近所述栅极隔槽的部分,形成第一凹陷。

12.在一些实施例中,所述形成覆盖所述栅极隔槽内表面的第一保护层,包括:形成第一保护薄膜,所述第一保护薄膜覆盖所述栅极隔槽、所述选择栅沟槽和所述堆叠结构远离所述衬底的表面;去除所述第一保护薄膜中覆盖所述选择栅沟槽和所述堆叠结构远离所述衬底的表面的部分,形成所述第一保护层。

13.在一些实施例中,在沉积栅导电材料的过程中,所述栅导电材料填充所述选择栅沟槽,形成牺牲填充部。在去除所述栅极隔槽内及所述堆叠结构远离所述衬底的表面上的栅导电材料的过程中,所述牺牲填充部远离所述衬底的部分被去除,形成第二凹陷。

14.在一些实施例中,在所述去除所述栅极隔槽内及所述堆叠结构远离所述衬底的表面上的栅导电材料之前,还包括:形成第二保护薄膜,所述第二保护薄膜覆盖所述栅极隔槽、所述选择栅沟槽和所述堆叠结构远离所述衬底的表面上的栅导电材料;去除所述第二保护薄膜中覆盖所述栅极隔槽和所述堆叠结构远离所述衬底的表面上的栅导电材料的部分,形成第二保护层。

15.在一些实施例中,在沉积栅导电材料的过程中,所述栅导电材料覆盖所述选择栅沟槽的内表面,形成牺牲覆盖层,所述选择栅沟槽内具有间隙。在形成第二保护薄膜的过程中,所述第二保护薄膜填充所述间隙。在去除所述栅极隔槽内及所述堆叠结构远离所述衬底的表面上的栅导电材料的过程中,所述牺牲覆盖层远离所述衬底的部分被去除,形成第三凹陷。

16.在一些实施例中,所述去除所述选择栅沟槽中的栅导电材料,包括:去除所述选择栅沟槽内的栅导电材料;去除所述栅导电层的靠近所述选择栅沟槽的部分,使所述栅导电层靠近所述选择栅沟槽的侧面相对于所述绝缘层靠近所述选择栅沟槽的侧面内缩,以形成第四凹陷。

17.在一些实施例中,在所述选择栅沟槽内形成顶部选择栅切线,包括:沉积电介质材料,填充在所述选择栅沟槽内的电介质材料形成所述顶部选择栅切线。其中,在沉积电介质材料的过程中,所述电介质材料还沉积在所述栅极隔槽的内表面。

18.在一些实施例中,在所述选择栅沟槽内形成顶部选择栅切线之后,还包括:在所述栅极隔槽内形成填充图案。

19.在一些实施例中,在衬底上形成堆叠结构之前,还包括:在衬底上形成至少一个停止层。在衬底上形成堆叠结构的步骤,与所述形成多个栅极隔槽和多个选择栅沟槽的步骤之间,还包括:形成多个沟道结构。

20.在一些实施例中,所述沟道结构贯穿所述堆叠结构和所述至少一层停止层,并延伸至所述衬底中,所述沟道结构包括存储功能层和沟道层,所述存储功能层和所述沟道层相邻设置。在所述选择栅沟槽内形成顶部选择栅切线之后,还包括:依次去除所述衬底,及所述沟道结构的存储功能层中延伸至所述衬底中的部分,以暴露所述沟道结构的沟道层;形成源极层,所述源极层覆盖所述沟道层所暴露的部分,以与所述沟道层电连接。

21.在一些实施例中,所述形成源极层,包括:形成掺杂的多晶硅层;对所述多晶硅层进行退火处理,形成所述源极层。

22.在一些实施例中,在所述形成源极层之后,所述制备方法还包括:在所述源极层远离所述堆叠结构的一侧形成层间介质层,所述层间介质层具有至少一个过孔;在所述层间

介质层远离所述堆叠结构的一侧形成金属互连层,所述金属互连层通过所述层间介质层的至少一个过孔与所述源极层电连接。

23.另一方面,提供一种半导体结构。所述半导体结构包括源极层、设置于所述源极层上的堆叠结构,堆叠结构包括层叠设置的多个膜层对,每个膜层对包括相邻的绝缘层和栅导电层。所述堆叠结构设有多个栅极隔槽和多个选择栅沟槽,相邻两个栅极隔槽之间设置有多个选择栅沟槽。所述栅极隔槽贯穿所述堆叠结构,所述选择栅沟槽贯穿所述堆叠结构中远离所述源极层一侧的至少一个所述绝缘层和至少一个所述栅导电层。所述半导体结构还包括设置于所述选择栅沟槽内的顶部选择栅切线。

24.另一方面,提供一种三维存储器。所述三维存储器包括:如上述实施例所述的半导体结构。

25.又一方面,提供一种存储系统。所述存储系统包括控制器及上述实施例所述的存储器,所述控制器耦合至所述存储器,且用于控制所述存储器存储数据。

26.又一方面,提供一种电子设备,包括上述实施例所述的存储系统。

27.在一些实施例中,所述电子设备包括如下至少一种:手机、台式计算机、平板电脑、笔记本电脑、服务器、车载设备、可穿戴设备、移动电源。

28.本公开的一些实施例提供了一种半导体结构的制备方法,在堆叠结构上形成多个栅极隔槽和多个选择栅沟槽,并且相邻两个栅极隔槽之间设置有多个选择栅沟槽。在选择栅沟槽内形成顶部选择栅切线之前,通过栅极隔槽去除第一牺牲层形成空腔,可避免相邻两个顶部选择栅切线之间第一牺牲层,因顶部选择栅切线的阻隔而无法通过栅极隔槽去除的问题,提高了器件良率;并且,在沉积栅导电材料形成栅导电层之前,在堆叠结构上形成多个选择栅沟槽,可避免形成多个选择栅沟槽的过程中,需要刻蚀堆叠结构中的绝缘层和栅导电层,降低了制备工艺的难度。

29.并且,通过选择栅沟槽和栅极隔槽在空腔中沉积栅导电材料,以在空腔内形成栅导电层,从而将多个第一牺牲层替换成多个栅导电层。然后,去除选择栅沟槽中的栅导电材料,在选择栅沟槽内形成顶部选择栅切线,以在相邻两个栅极隔槽之间形成多个顶部选择栅切线。

30.本公开的一些实施例还提供了一种半导体结构,相邻两个栅极隔槽之间设置有多个选择栅沟槽,且选择栅沟槽内设置有顶部选择栅切线,即相邻两个栅极隔槽之间设置有多个顶部选择栅切线,可进一步将存储块划分为多个子存储块,以提高半导体结构的有效沟道孔的数量,从而增加存储器的存储密度。

31.可以理解地,本公开的上述实施例提供的三维存储器、存储系统及电子设备,其所能达到的有益效果可参考上文中半导体结构及其制备方法的有益效果,此处不再赘述。

附图说明

32.为了更清楚地说明本公开中的技术方案,下面将对本公开一些实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例的附图,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。此外,以下描述中的附图可以视作示意图,并非对本公开实施例所涉及的产品的实际尺寸、方法的实际流程、信号的实际时序等的限制。

33.图1a为根据一些实施例的一种三维存储器的立体结构示意图;

34.图1b为图1a中的三维存储器沿剖面线a-a'的剖视图;

35.图2a~图2k为根据一些实施例的半导体结构的一种制备方法的流程图;

36.图2l为根据一些实施例的半导体结构的另一种制备方法的流程图;

37.图3a为根据一些实施例的另一种半导体结构的俯视图;

38.图3b为图3a中的半导体结构沿剖面线b-b'的剖视图;

39.图4a~图4s为根据一些实施例的半导体结构的一种制备方法的各步骤图;

40.图5a~图5f为根据一些实施例的半导体结构的另一种制备方法的各步骤图;

41.图6a~图6c为根据一些实施例的半导体结构的又一种制备方法的各步骤图;

42.图7为根据一些实施例的一种存储系统的结构图;

43.图8为根据一些实施例的另一种存储系统的结构图;

44.图9为根据一些实施例的电子设备的结构图。

具体实施方式

45.下面将结合附图,对本公开一些实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。基于本公开所提供的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本公开保护的范围。

46.在本公开的描述中,需要理解的是,术语“中心”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本公开和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。

47.除非上下文另有要求,否则,在整个说明书和权利要求书中,术语“包括”被解释为开放、包含的意思,即为“包含,但不限于”。在说明书的描述中,术语“一个实施例”、“一些实施例”、“示例性实施例”、“示例性地”或“一些示例”等旨在表明与该实施例或示例相关的特定特征、结构、材料或特性包括在本公开的至少一个实施例或示例中。上述术语的示意性表示不一定是指同一实施例或示例。此外,所述的特定特征、结构、材料或特点可以以任何适当方式包括在任何一个或多个实施例或示例中。

48.以下,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上。

49.在描述一些实施例时,可能使用了“连接”及其衍伸的表达。例如,描述一些实施例时可能使用了术语“电连接”以表明两个或两个以上部件彼此间有直接物理接触或电接触。这里所公开的实施例并不必然限制于本文内容。

[0050]“a、b和c中的至少一个”与“a、b或c中的至少一个”具有相同含义,均包括以下a、b和c的组合:仅a,仅b,仅c,a和b的组合,a和c的组合,b和c的组合,及a、b和c的组合。

[0051]“a和/或b”,包括以下三种组合:仅a,仅b,及a和b的组合。

[0052]

另外,“基于”的使用意味着开放和包容性,因为“基于”一个或多个所述条件或值的过程、步骤、计算或其他动作在实践中可以基于额外条件或超出所述的值。

[0053]

在本公开的内容中,“在

……

上”、“上方”、和“之上”的含义应当以最宽泛的方式解释,使得“在...上”不仅意味着“直接在某物上”,而且还包括其间具有中间特征或层的“在某物上”的含义,并且“上方”或“之上”不仅意味着在某物“上方”或“之上”,还包括其间没有中间特征或层的在某物“上方”或“之上”的含义(即,直接在某物上)。

[0054]

本文参照作为理想化示例性附图的剖视图和/或平面图描述了示例性实施方式。在附图中,为了清楚,放大了层和区域的厚度。因此,可设想到由于例如制造技术和/或公差引起的相对于附图的形状的变动。因此,示例性实施方式不应解释为局限于本文示出的区域的形状,而是包括因例如制造而引起的形状偏差。例如,示为矩形的蚀刻区域通常将具有弯曲的特征。因此,附图中所示的区域本质上是示意性的,且它们的形状并非旨在示出设备的区域的实际形状,并且并非旨在限制示例性实施方式的范围。

[0055]

如本文所使用的,术语“衬底”是指可以在其上添加后续的材料层的材料。衬底本身可以被图案化。被添加在衬底上的材料可以被图案化或者可以保持不被图案化。此外,衬底可以包括诸如硅、锗、砷化镓、磷化铟等的多种半导体材料。替代地,衬底可以由诸如玻璃、塑料或蓝宝石晶圆之类的非导电材料制成。

[0056]

术语“三维存储器”是指,在衬底的主表面上阵列布置,且沿垂直于衬底的方向延伸的存储单元晶体管串(在本文中被称为“存储单元串”,例如nand存储单元串),所形成的半导体器件。如本文所使用的,术语“垂直/垂直地”意味着标称上垂直于衬底的主表面(即横向表面)。

[0057]

请参见图1a和图1b,图1a为本公开一些实施例提供的三维存储器的立体结构示意图,图1b为图1a中三维存储器沿剖面线a-a'的剖面图。

[0058]

如图1a和图1b所示,三维存储器100包括堆叠结构4,堆叠结构4具有台阶形貌,包括多层交替层叠的栅导电层43和绝缘层(图中未示出)。栅导电层43和绝缘层沿第一方向x延展。沿第三方向z,多层栅导电层43中位于最下方的栅导电层43被构造为源端选择栅sgs,多层栅导电层43中位于最上方的栅导电层43被构造为漏端选择栅sgd,多层栅导电层43中位于中间层的栅导电层43被构造为多条字线wl(例如,图1b示出的wl1~wl4),源端选择栅sgs、漏端选择栅sgd和字线wl统称为栅线。

[0059]

需要说明的是,为清楚展示三维存储器100的结构,图1a中仅示出了四条字线wl,三维存储器100中的字线wl的数量可以远多于四条。

[0060]

三维存储器100还包括沿第三方向z贯穿漏端选择栅sgd、各层字线wl、源端选择栅sgs的沟道结构5阵列。如图1b所示,沟道结构5将各层字线wl串接起来,形成存储单元串50。一个存储单元串50相当于多个平面存储单元的存储容量。因此,三维存储器能够提供较大的存储容量。

[0061]

如图1a所示,三维存储器100在x-y平面上包括存储单元串50阵列。

[0062]

继续参见图1a,三维存储器100还包括位于源端选择栅sgs下方的源极层13。在一些示例中,存储单元串50阵列共用源极层13。

[0063]

三维存储器100还包括漏端选择栅触点sgd cnt、源端选择栅触点sgs cnt、源端触点sl cnt、字线触点wl cnt以及位线触点bl cnt。其中,漏端选择栅触点sgd cnt与漏端选择栅sgd电连接;源端选择栅触点sgs cnt与源端选择栅sgs电连接;源端触点sl cnt与源端sl电连接;每个字线触点wl cnt与一条字线wl电连接,由此字线触点wl cnt可以分别于每

个存储单元串50中分别寻址;每个位线触点bl cnt与一个存储单元串50的顶端电连接,由此位线触点bl cnt可以分别独立寻址每个存储单元串50。

[0064]

三维存储器100还包括位线bl,位线bl通过位线触点bl cnt与存储单元串50电连接。

[0065]

在一些示例中,三维存储器100还包括设置于存储单元串50阵列一侧的外围器件,以及设置于存储单元串50阵列与外围器件之间的互联层,通过互联层实现存储单元串50阵列与外围器件的电连接。

[0066]

如图1a所示,为了实现三维存储器100的存储区的分块存储,该三维存储器100中还包括用于将堆叠结构4划分成多个存储块的栅极隔槽8。在一些示例中,栅极隔槽8沿第三方向z贯穿堆叠结构4,且至少沿第一方向x延伸。

[0067]

需要说明的是,上述源极层13在x-y平面中延伸,第一方向x和第二方向y例如是源极层13平面中的两个正交方向:第一方向x例如为字线wl的延伸方向,第二方向y例如为位线bl的延伸方向。第三方向z垂直于源极层13,即垂直于x-y平面。

[0068]

在相关技术中,通过在相邻两个栅极隔槽之间形成顶部选择栅切线,可进一步将存储块划分为多个子存储块,以提高有效沟道孔的数量,增加存储器的存储密度。

[0069]

为了在相邻两个栅极隔槽之间形成多条顶部选择栅切线,并保证器件良率和合理的工艺难度,本发明的发明人在研究中发现,在制备三维存储器的过程中,在堆叠结构上形成多个栅极隔槽,通过栅极隔槽去除堆叠结构中的牺牲层之前,在堆叠结构上形成多个顶部选择栅切线。相邻两个栅极隔槽之间存在多个顶部选择栅切线,则会导致相邻两个顶部选择栅切线之间牺牲层被顶部选择栅切线阻隔,进而无法通过栅极隔槽将相邻两个顶部选择栅切线之间牺牲层去除并替换成栅导电层。

[0070]

而在堆叠结构上形成多个栅极隔槽,通过栅极隔槽去除堆叠结构中的牺牲层并替换成栅导电层之后,在堆叠结构上形成多个选择栅沟槽和多个顶部选择栅切线,在形成多个选择栅沟槽的过程中,需要刻蚀堆叠结构上的氧化层和栅导电层,由于氧化层和栅导电层的材料不同,需要调整刻蚀氧化层和栅导电层的选择比,才可以准确地控制选择栅沟槽的深度,这增加了制备工艺的难度。

[0071]

为解决上述问题,本公开的一些实施例提供了一种半导体结构的制备方法,例如,该制备方法用于制备图3a和图3b中示出的半导体结构200。

[0072]

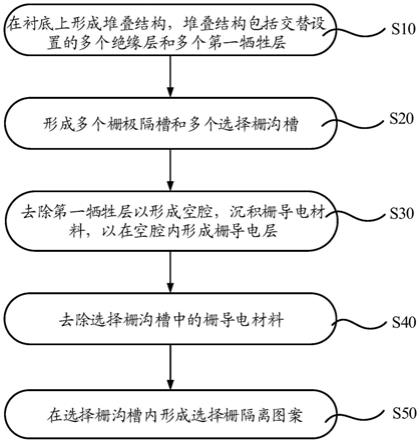

如图2a所示,该制备方法包括如下s10~s50:

[0073]

s10:如图4a所示,在衬底1上形成堆叠结构4,堆叠结构4包括层叠设置的多个膜层对4a,每个膜层对4a包括相邻的绝缘层40和第一牺牲层41。

[0074]

可以理解的是,在衬底1上形成堆叠结构4的过程中,先在衬底1上形成一个绝缘层40,然后在该绝缘层40远离衬底1的一侧形成第一牺牲层41,重复前述的制备步骤,形成交替设置的多个绝缘层40和多个第一牺牲层41,即形成堆叠结构4。每个膜层对4a中的绝缘层40与其他膜层对中的第一牺牲层相邻设置。

[0075]

s20:如图4b和图4d所示,形成多个栅极隔槽8和多个选择栅沟槽6。结合图3a和图3b,相邻两个栅极隔槽8之间设置有多个选择栅沟槽6,并且,每个栅极隔槽8贯穿堆叠结构4,每个选择栅沟槽6贯穿堆叠结构4中远离衬底1一侧的至少一个绝缘层40和至少一个第一牺牲层41。

[0076]

需要说明的是,结合图3a、图3b和图4f,每个栅极隔槽8贯穿堆叠结构4,栅极隔槽8可将栅导电层43(栅导电层43在后续制备步骤中形成)分割成多条栅线,从而在半导体结构200上划分出多个存储块b。

[0077]

同理,每个选择栅沟槽6贯穿堆叠结构4中远离衬底1一侧的至少一个绝缘层40和至少一个第一牺牲层41,即,选择栅沟槽6贯穿位于堆叠结构4顶部的至少一个绝缘层40和至少一个第一牺牲层41,选择栅沟槽6可用于分割堆叠结构4中远离衬底1的至少一个栅导电层43,可进一步将存储块b划分为多个子存储块b1,以提高半导体结构200的有效沟道孔的数量,从而增加半导体结构200的存储密度。

[0078]

示例性地,如图4b所示,每个选择栅沟槽6贯穿堆叠结构4中远离衬底1的两个绝缘层40和两个第一牺牲层41。

[0079]

s30:如图4d、图4e和图4f所示,去除第一牺牲层41以形成空腔42,沉积栅导电材料,以在空腔42内形成栅导电层43。

[0080]

需要说明的是,选择栅沟槽6和栅极隔槽8可暴露多个第一牺牲层41,例如,暴露多个第一牺牲层41的一侧,采用湿法刻蚀工艺,通过栅极隔槽8可以将所有的第一牺牲层41全部刻蚀去除,在第一牺牲层41的设置位置形成空腔42。

[0081]

采用薄膜沉积工艺,通过选择栅沟槽6和栅极隔槽8在空腔42中沉积栅导电材料,以在空腔42内形成栅导电层43。并且,在沉积栅导电材料的过程中,部分栅导电材料会沉积在选择栅沟槽6和栅极隔槽8内,通过后续的制备步骤将沉积在选择栅沟槽6和栅极隔槽8内部分栅导电材料去除。

[0082]

通过上述制备方法,实现了将多个第一牺牲层41替换成多个栅导电层43的目的。

[0083]

s40:如图4i、图4j和图4k所示,去除选择栅沟槽6中的栅导电材料。

[0084]

可以理解的是,通过去除选择栅沟槽6中的栅导电材料,可避免选择栅沟槽6分割栅导电层43所得到的栅线之间电连接的问题。

[0085]

s50:如图4l所示,在选择栅沟槽6内形成顶部选择栅切线60。

[0086]

可以理解的是,形成顶部选择栅切线60的材料为电介质材料,从而通过顶部选择栅切线60阻隔,与选择栅沟槽6相邻的栅导电层43的分割部分,实现栅导电层43的分割部分之间的绝缘。

[0087]

本公开的上述制备方法,在堆叠结构4上形成多个栅极隔槽8和多个选择栅沟槽6,并且,使相邻两个栅极隔槽8之间设置有多个选择栅沟槽6。在选择栅沟槽6内形成顶部选择栅切线60之前,通过栅极隔槽8去除第一牺牲层41形成空腔42,可避免相邻两个顶部选择栅切线60之间第一牺牲层41,因顶部选择栅切线60的阻隔而无法通过栅极隔槽8去除的问题。并且,在沉积栅导电材料形成栅导电层43之前,在堆叠结构4上形成多个选择栅沟槽6,可避免形成多个选择栅沟槽6的过程中,需要刻蚀堆叠结构4中的绝缘层40和栅导电层43,降低了制备工艺的难度。

[0088]

并且,通过选择栅沟槽6和栅极隔槽8在空腔42中沉积栅导电材料,以在空腔42内形成栅导电层43,以将多个第一牺牲层41替换成多个栅导电层43。然后,去除选择栅沟槽6中的栅导电材料,在选择栅沟槽6内形成顶部选择栅切线60,以在相邻两个栅极隔槽8之间形成多个顶部选择栅切线60,可进一步将存储块b划分为多个子存储块b1,以提高半导体结构200的有效沟道孔的数量,从而增加存储器的存储密度。

[0089]

在一些实施例中,如图2b所示,s20:形成多个栅极隔槽8和多个选择栅沟槽6,包括如下s21~s23:

[0090]

s21:如图4b所示,在堆叠结构4中形成多个选择栅沟槽6。

[0091]

s22:如图4c所示,形成第二牺牲层7,第二牺牲层7填充多个选择栅沟槽6,并覆盖堆叠结构4远离衬底1的表面。

[0092]

通过在堆叠结构4上形成第二牺牲层7,可利用第二牺牲层7填平多个选择栅沟槽6以及堆叠结构4远离衬底1的表面,提高堆叠结构4的表面平坦度,从而便于后续的制备步骤的进行,例如,方便了在堆叠结构4中形成多个栅极隔槽8。

[0093]

s23:如图4d所示,在堆叠结构4中形成多个栅极隔槽8。

[0094]

通过第二牺牲层7填充多个选择栅沟槽6,并覆盖堆叠结构4远离衬底1的表面,提高了堆叠结构4的表面平坦度,因此,在堆叠结构4中形成多个栅极隔槽8的过程中,例如,可采用曝光显影工艺,在堆叠结构4的表面形成图案化的光刻胶层,以图案化的光刻胶层为掩膜刻蚀堆叠结构4,形成多个栅极隔槽8,并去除光刻胶层。

[0095]

并且,由于第二牺牲层7填充多个选择栅沟槽6,可避免光刻胶层落入选择栅沟槽6内而难以去除。

[0096]

在一些实施例中,第二牺牲层7与第一牺牲层41的材料相同。

[0097]

示例性地,结合图4d和图4e可知,可采用同一湿法刻蚀工艺,采用同一种刻蚀液,去除第一牺牲层41和第二牺牲层7。

[0098]

示例性地,第二牺牲层7与第一牺牲层41的材料均包括氮化硅。

[0099]

在一些实施例中,如图2c所示,在s40:去除选择栅沟槽6中的栅导电材料之前,制备方法还包括如下s31~s32:

[0100]

s31:如图4f和图4g所示,去除栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料。

[0101]

需要说明的是,根据前文所述,在空腔42中沉积栅导电材料的过程中,栅导电材料沉积在空腔42内形成栅导电层43,并且,部分栅导电材料会沉积在选择栅沟槽6和栅极隔槽8内,在此过程中,还有部分栅导电材料会沉积在堆叠结构4远离衬底1的表面上。

[0102]

通过上述制备方法,去除栅极隔槽8内表面及堆叠结构4远离衬底1的表面上的栅导电材料,可避免沿衬底1的厚度方向z,相邻两个栅导电层43之间通过栅极隔槽8内表面的栅导电材料电连接。

[0103]

示例性地,如图2d所示,s31:去除栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料,包括如下s311~s312:

[0104]

s311:如图4f和图4g所示,去除栅极隔槽8侧壁和底部、及堆叠结构4远离衬底1的表面上的栅导电材料。

[0105]

例如,可采用湿法刻蚀工艺,采用刻蚀液去刻蚀栅极隔槽8侧壁和底部、及堆叠结构4远离衬底1的表面上的栅导电材料。

[0106]

s312:如图4f和图4g所示,去除栅导电层43的靠近栅极隔槽8的部分,使栅导电层43靠近栅极隔槽8的侧面相对于绝缘层40靠近栅极隔槽8的侧面内缩,以形成第一凹陷430。

[0107]

例如,采用湿法刻蚀工艺,采用刻蚀液去刻蚀栅极隔槽8侧壁和底部、及堆叠结构4远离衬底1的表面上的栅导电材料,然后增加湿法刻蚀工艺的时长,采用刻蚀液继续刻蚀栅

导电层43靠近栅极隔槽8的部分,使栅导电层43靠近栅极隔槽8的侧面相对于绝缘层40靠近栅极隔槽8的侧面,朝远离栅极隔槽8的方向u凹陷,以在栅导电层43上形成第一凹陷430。

[0108]

通过上述制备方法,去除栅导电层43的靠近栅极隔槽8的部分,在栅导电层43上形成第一凹陷430,可更充分地去除栅极隔槽8内表面的栅导电材料,从而避免沿第三方向z,相邻两个栅导电层43之间通过栅极隔槽8内表面的栅导电材料电连接。

[0109]

s32:如图4h和图4i所示,形成覆盖栅极隔槽8内表面的第一保护层90,在后续去除选择栅沟槽6中的栅导电材料的过程中,第一保护层90起到保护栅极隔槽8的作用。

[0110]

示例性地,如图2e所示,s32:形成覆盖栅极隔槽8内表面的第一保护层90,包括如下s321~s322:

[0111]

s321:如图4h所示,形成第一保护薄膜9,第一保护薄膜9覆盖栅极隔槽8、选择栅沟槽6和堆叠结构4远离衬底1的表面。

[0112]

例如,可采用薄膜沉积工艺形成第一保护薄膜9,第一保护薄膜9覆盖栅极隔槽8、选择栅沟槽6和堆叠结构4远离衬底1的表面。

[0113]

s322:如图4h和图4i所示,去除第一保护薄膜9中覆盖选择栅沟槽6和堆叠结构4远离衬底1的表面的部分,形成第一保护层90。

[0114]

可以理解的是,参见图4h,第一保护薄膜9的覆盖选择栅沟槽6和堆叠结构4远离衬底1的表面的部分,均位于堆叠结构4的顶部。参见图4i,可采用干法刻蚀工艺,刻蚀第一保护薄膜9的位于堆叠结构4顶部的部分,保留第一保护薄膜9的覆盖栅极隔槽8内表面的部分,即第一保护层90。

[0115]

在一些实施例中,如图4f和图4g所示,根据前文所述,在沉积栅导电材料的过程中,栅导电材料会沉积在选择栅沟槽6、栅极隔槽8及堆叠结构4远离衬底1的表面上,栅导电材料填充选择栅沟槽6,形成牺牲填充部44。

[0116]

需要说明的是,参考图4f和图4g,相较于栅极隔槽8的开口尺寸,选择栅沟槽6的开口尺寸较小,选择栅沟槽6内更易堆积栅导电材料,甚至是填满栅导电材料,形成牺牲填充部44。

[0117]

从而,参考图4f和图4g,在去除栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料的过程中,牺牲填充部44远离衬底1的部分被去除,形成第二凹陷431。

[0118]

示例性地,采用湿法刻蚀工艺,刻蚀液与栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料,以及牺牲填充部44远离衬底1的部分接触,从而将栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料,以及牺牲填充部44远离衬底1的部分刻蚀,在选择栅沟槽6内形成第二凹陷431。

[0119]

进而,如图4h所示,在形成第一保护薄膜9的过程中,第一保护薄膜9会覆盖选择栅沟槽6内的第二凹陷431。如图4i所示,在形成第一保护层90的过程中,去除第一保护薄膜9的覆盖第二凹陷431的部分。

[0120]

示例性地,可采用薄膜沉积工艺形成第一保护薄膜9,第一保护薄膜9覆盖栅极隔槽8和堆叠结构4远离衬底1的表面,以及选择栅沟槽6内的第二凹陷431。

[0121]

示例性地,可采用干法刻蚀工艺,刻蚀第一保护薄膜9的覆盖第二凹陷431和堆叠结构4远离衬底1的表面的部分,保留第一保护薄膜9的覆盖栅极隔槽8内表面的部分(第一保护层90)。

[0122]

在另一些实施例中,如图5a所示,选择栅沟槽6的开口尺寸较大,在沉积栅导电材料的过程中,栅导电材料覆盖选择栅沟槽6的内表面,形成牺牲覆盖层62,且选择栅沟槽6内具有间隙63。

[0123]

可以理解的是,由于选择栅沟槽6的开口尺寸较大,选择栅沟槽6内没有填满栅导电材料,而是在选择栅沟槽6的内表面覆盖一层栅导电材料,形成牺牲覆盖层62,从而在选择栅沟槽6内形成了间隙63。

[0124]

基于此,在一些实施例中,如图2l所示,在s31:去除栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料之前,制备方法还包括如下s301~s302:

[0125]

s301:如图5b所示,形成第二保护薄膜91,第二保护薄膜91覆盖栅极隔槽8、选择栅沟槽6和堆叠结构4远离衬底1的表面上的栅导电材料。

[0126]

示例性地,采用薄膜沉积工艺,在形成第二保护薄膜91的过程中,第二保护薄膜91填充间隙63。例如,薄膜沉积工艺可以包括原子层沉积工艺(atomic layer deposition,简称ald)。

[0127]

s302:如图5b和图5c所示,去除第二保护薄膜91中覆盖栅极隔槽8和堆叠结构4远离衬底1的表面上的栅导电材料的部分,形成第二保护层92。

[0128]

可以理解的是,牺牲覆盖层62为覆盖在选择栅沟槽6内表面的一层栅导电材料,牺牲覆盖层62的厚度较薄。

[0129]

通过第二保护层92填充间隙63,起到保护牺牲覆盖层62的作用,可避免在后续的制备步骤中,在牺牲覆盖层62被刻蚀之后,栅导电层43靠近选择栅沟槽6的部分被刻蚀较多,从而避免对栅导电层43的导电性能产生影响。

[0130]

在一些实施例中,如图5c和图5d所示,在去除栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料的过程中,牺牲覆盖层62远离衬底1的部分被去除,形成第三凹陷620。

[0131]

示例性地,采用湿法刻蚀工艺,刻蚀液与栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料,以及牺牲覆盖层62的顶部接触,从而将栅极隔槽8内及堆叠结构4远离衬底1的表面上的栅导电材料,以及牺牲覆盖层62远离衬底1的部分刻蚀,在选择栅沟槽6内形成第三凹陷620。

[0132]

可以理解的是,通过第二保护层92填充间隙63,减小了牺牲覆盖层62与刻蚀液的接触面积(仅牺牲覆盖层62的顶部与刻蚀液接触),从而避免牺牲覆盖层62被全部刻蚀,避免栅导电层43靠近选择栅沟槽6的部分被刻蚀过多。

[0133]

进而,在一些实施例中,如图5d和图5e所示,在形成第一保护薄膜9的过程中,第一保护薄膜9会覆盖选择栅沟槽6内的第三凹陷620。如图5e和图5f所示,在形成第一保护层90的过程中,去除第一保护薄膜9的覆盖第三凹陷620的部分。

[0134]

示例性地,可采用薄膜沉积工艺形成第一保护薄膜9,第一保护薄膜9覆盖栅极隔槽8和堆叠结构4远离衬底1的表面,以及选择栅沟槽6内的第三凹陷620。

[0135]

示例性地,去除第一保护薄膜9的覆盖第三凹陷620和堆叠结构4远离衬底1的表面的部分,保留第一保护薄膜9的覆盖栅极隔槽8内表面的部分(第一保护层90)。

[0136]

在一些实施例中,如图2f所示,s40:去除选择栅沟槽6中的栅导电材料,包括如下s41~s42:

[0137]

s41:如图4i和图4j所示,去除选择栅沟槽6内的栅导电材料。

[0138]

示例性地,可采用干法刻蚀工艺,对选择栅沟槽6中的栅导电材料进行刻蚀,以去除选择栅沟槽6内的栅导电材料。并且,在第一次刻蚀过程中,第一保护层90可起到保护栅极隔槽8的作用。

[0139]

通过上述制备方法,去除选择栅沟槽6内表面的栅导电材料,可避免沿第三方向z,相邻两个栅导电层43之间通过选择栅沟槽6内表面的栅导电材料电连接。

[0140]

s42:如图4j和图4k所示,去除栅导电层43的靠近选择栅沟槽6的部分,使栅导电层43靠近选择栅沟槽6的侧面相对于绝缘层40靠近选择栅沟槽6的侧面内缩,以形成第四凹陷432。

[0141]

示例性地,采用湿法刻蚀工艺,对栅导电层43的靠近选择栅沟槽6的部分进行刻蚀,使栅导电层43靠近选择栅沟槽6的侧面相对于绝缘层40靠近选择栅沟槽6的侧面,朝远离选择栅沟槽6的方向v凹陷,以在栅导电层43上形成第四凹陷432。

[0142]

通过上述制备方法,在选择栅沟槽6贯穿两个栅导电层43或更多栅导电层43的情况下,去除栅导电层43的靠近选择栅沟槽6的部分,在栅导电层43上形成第四凹陷432,可更充分地去除选择栅沟槽6内表面的栅导电材料,从而避免沿第三方向z,相邻两个栅导电层43之间通过选择栅沟槽6内表面的栅导电材料电连接。

[0143]

在一些实施例中,如图2g所示,s50:在选择栅沟槽6内形成顶部选择栅切线60,包括如下s51:

[0144]

s51:如图4l所示,沉积电介质材料,填充在选择栅沟槽6内的电介质材料形成顶部选择栅切线60。其中,在沉积电介质材料的过程中,电介质材料还沉积在栅极隔槽8内。

[0145]

可以理解的是,相较于栅极隔槽8的开口尺寸,选择栅沟槽6的开口尺寸较小,在沉积电介质材料的量一定的情况下,选择栅沟槽6内更易填满电介质材料。因此,如图4l所示,选择栅沟槽6内填满电介质材料,而栅极隔槽8内没有填满电介质材料,栅极隔槽8内以及堆叠结构4远离衬底1的表面沉积有一层电介质材料。

[0146]

并且,沉积在栅极隔槽8内的电介质材料形成隔离层61,用于保护和隔离其所覆盖的结构,例如,第一保护层90、栅极隔槽8及栅导电层43靠近栅极隔槽8的部分。

[0147]

通过上述制备方法,沉积电介质材料以填充选择栅沟槽6,在选择栅沟槽6内形成顶部选择栅切线60,顶部选择栅切线60可将栅导电层6分割成两部分,且顶部选择栅切线60可阻隔栅导电层6分割的两部分,使栅导电层6分割的两部分之间绝缘。

[0148]

在一些实施例中,如图2h所示,在s50:选择栅沟槽6内形成顶部选择栅切线60之后,制备方法还包括如下s60:

[0149]

s60:如图4m所示,在栅极隔槽8内形成填充图案80。

[0150]

可以理解的是,填充图案80也可将栅导电层6分割成两部分,且填充图案80可阻隔栅导电层6分割的两部分,使栅导电层6分割的两部分之间绝缘。

[0151]

并且,采用填充图案80填满栅极隔槽8,可提高半导体结构200的整体性,进而提高半导体结构200的结构强度。

[0152]

示例性地,可采用薄膜沉积工艺,在堆叠结构4上沉积填充材料,填充材料填充在栅极隔槽8内,且填充材料沉积在堆叠结构4远离衬底1的表面上。然后,去除堆叠结构4远离衬底1的表面上的填充材料,保留栅极隔槽8内的填充材料以形成填充图案80。

[0153]

示例性地,填充材料可包括多晶硅。

[0154]

在一些实施例中,如图2i所示,在s10:在衬底1上形成堆叠结构4之前,制备方法还包括如下s01:

[0155]

s01:如图4a所示,在衬底1上形成至少一个停止层s。

[0156]

可以理解的是,“停止层s”也称为“刻蚀停止层s”,即刻蚀位于停止层s一侧的膜层的过程中,刻蚀终止于停止层s,停止层s不会被刻蚀。本公开的实施例,关于停止层s的具体功能将在后续的相关步骤中进行介绍。

[0157]

示例性地,如图4a所示,s01包括:在衬底1上依次形成第一停止层2和第二停止层3。

[0158]

如图2i所示,在s10与s20之间,制备方法还包括如下s11:

[0159]

s11:如图4a所示,形成多个沟道结构5,沟道结构5贯穿堆叠结构4和至少一层停止层s,并延伸至衬底1中。

[0160]

其中,如图4a所示,沟道结构5包括存储功能层51和沟道层52,两者相邻设置。示例性地,两者依次形成。示例性的,存储功能层51可以为氧化物-氮化物-氧化物叠层(oxide-nitride-oxide,简称ono)。例如,存储功能层51包括设置形成的阻挡层5a、电荷存储层5b和隧穿层5c。

[0161]

如图2i所示,在s50:选择栅沟槽6内形成顶部选择栅切线60之后,制备方法还包括如下s70~s71:

[0162]

s70:如图4n~图4q所示,依次去除衬底1,及沟道结构5的存储功能层51中延伸至衬底1中的部分,以暴露沟道结构5的沟道层52。

[0163]

示例性地,如图4a所示,衬底1包括依次形成的基底10、第三牺牲层11和第四牺牲层12。

[0164]

例如,基底10的材料可包括单晶硅、单晶锗、iii-v族化合物半导体材料、iivi族化合物半导体材料中的至少一个。第三牺牲层11的材料可包括氧化硅。第四牺牲层12的材料可包括多晶硅。

[0165]

如图4m和图4n所示,去除衬底1的基底10,例如,可采用化学机械研磨工艺(chemical mechanical polishing,简称cmp)、干法刻蚀工艺或湿法刻蚀工艺,去除衬底1的基底10。

[0166]

如图4n和图4o所示,去除衬底1的第三牺牲层11,例如,可采用湿法刻蚀工艺,去除衬底1的第三牺牲层11。

[0167]

第四牺牲层12可作为第三牺牲层11的停止层,可以理解的是,上述湿法刻蚀工艺所采用的刻蚀液,可以刻蚀第三牺牲层11,但不可以刻蚀第四牺牲层12,刻蚀终止于第四牺牲层12。

[0168]

如图4o和图4p所示,去除衬底1的第四牺牲层12,例如,可采用湿法刻蚀工艺,去除衬底1的第四牺牲层12。

[0169]

第一停止层2可作为第四牺牲层12的停止层,可以理解的是,上述湿法刻蚀工艺所采用的刻蚀液,可以刻蚀第四牺牲层12,但不可以刻蚀第一停止层2,刻蚀终止于第一停止层2。并且,湿法刻蚀工艺所采用的刻蚀液,也不可以刻蚀存储功能层51的阻挡层5a,即刻蚀还终止于阻挡层5a,从而可暴露沟道结构5延伸至衬底1中的部分。

[0170]

如图4p和图4q所示,去除沟道结构5的存储功能层51中延伸至衬底1中的部分,以暴露沟道结构5的沟道层52。例如,可采用湿法刻蚀工艺,去除沟道结构5的存储功能层51中延伸至衬底1中的部分,以暴露沟道结构5的沟道层52。

[0171]

可以理解的是,在去除沟道结构5的存储功能层51中延伸至衬底1中的部分的过程中,湿法刻蚀工艺所采用的刻蚀液,还刻蚀第一停止层2,但不可以刻蚀第二停止层3,也不可以刻蚀存储功能层51的沟道层52,即刻蚀终止于第二停止层3和沟道层52。

[0172]

s71:如图4r所示,形成源极层13,源极层13覆盖沟道层52所暴露的部分,以与沟道层52电连接。

[0173]

示例性地,可采用薄膜沉积工艺,在第二停止层3远离堆叠结构4的一侧形成源极层13,源极层13覆盖沟道层52所暴露的部分,以与沟道层52电连接。

[0174]

在一些实施例中,如图2j所示,s71:形成源极层13,包括如下s711~s712:

[0175]

s711:形成掺杂的多晶硅层。

[0176]

示例性地,可采用离子注入工艺,对多晶硅层进行掺杂处理,例如,向多晶硅层注入p型或n型掺杂剂,以提高多晶硅层的导电性能。

[0177]

s712:对多晶硅层进行退火处理,形成源极层13。

[0178]

示例性地,可采用激光退火工艺(laser annealing,简称laser ann),对多晶硅层进行退火处理,修复多晶硅层材料的晶格损伤(离子注入工艺所造成的),以及激活注入多晶硅层的掺杂剂。

[0179]

在一些实施例中,如图2k所示,在s71:形成源极层之后,制备方法还包括如下s80~s81:

[0180]

s80:如图4s所示,在源极层13远离堆叠结构4的一侧形成层间介质层14,层间介质层14具有至少一个过孔h。

[0181]

示例性地,可采用薄膜沉积工艺,在源极层13远离堆叠结构4的一侧形成层间介质薄膜。例如,层间介质薄膜的材料可包括氧化硅。

[0182]

采用构图工艺,图案化层间介质薄膜,在层间介质层14中开设至少一个过孔h。

[0183]

s81:如图4s所示,在层间介质层14远离堆叠结构4的一侧形成金属互连层15,金属互连层15通过层间介质层14的至少一个过孔h与源极层13电连接。

[0184]

示例性地,可采用薄膜沉积工艺,在层间介质层14远离堆叠结构4的一侧形成金属互连层15,金属互连层15通过层间介质层14的至少一个过孔h与源极层13电连接。金属互连层15位于过孔h内的部分称为拾取区(pick up area)。

[0185]

通过上述设置方式,可通过源极层13与金属互连层15的电连接,实现源极层13从半导体结构200的背面(底部)引出,简化了半导体结构200的结构设计。

[0186]

在另一些实施例中,如图6a和图6b所示,在去除沟道结构5的存储功能层51中延伸至衬底1中的部分的过程中,还去除了第一保护层90的延伸至衬底1中的部分,以及隔离层61的延伸至衬底1中的部分,以暴露填充图案80。

[0187]

可以理解的是,采用湿法刻蚀工艺,去除沟道结构5的存储功能层51中延伸至衬底1中的部分,湿法刻蚀工艺所采用的刻蚀液,还可以刻蚀第一保护层90的延伸至衬底1中的部分,以及隔离层61的延伸至衬底1中的部分,但不可以刻蚀填充图案80,即刻蚀终止于填充图案80。

[0188]

如图6c所示,形成源极层13,源极层13覆盖沟道层52所暴露的部分,以与沟道层52电连接。并且,源极层13覆盖填充图案80所暴露的部分,以与填充图案80电连接。

[0189]

需要说明的是,本公开的上述实施例中,填充图案80的材料包括导电材料,通过源极层13覆盖填充图案80所暴露的部分,以与填充图案80电连接。

[0190]

通过上述设置方式,可通过源极层13与填充图案80的电连接,实现源极层13从半导体结构200的正面(顶部)引出。

[0191]

本公开所提供的半导体结构的制备方法,首先在衬底1上形成堆叠结构4,堆叠结构4包括交替设置的多个绝缘层40和多个第一牺牲层41。然后,形成贯穿堆叠结构4的多个栅极隔槽8,在相邻两个栅极隔槽8之间形成多个选择栅沟槽6,每个选择栅沟槽6贯穿堆叠结构4中远离衬底1的至少一个绝缘层40和至少一个第一牺牲层41。之后,去除第一牺牲层41以在堆叠结构4中形成空腔42,在空腔42中沉积栅导电材料以形成栅导电层43。最后,去除选择栅沟槽6中的栅导电材料,在选择栅沟槽6内形成顶部选择栅切线60。

[0192]

本公开的上述制备方法,在选择栅沟槽6内形成顶部选择栅切线60之前,通过栅极隔槽8去除第一牺牲层41形成空腔42,可避免在选择栅沟槽6内形成顶部选择栅切线60之后,相邻两个顶部选择栅切线60之间第一牺牲层41,因顶部选择栅切线60的阻隔而无法通过栅极隔槽8去除的问题。

[0193]

并且,在沉积栅导电材料形成栅导电层43之前,在堆叠结构4上形成多个选择栅沟槽6,可避免在沉积栅导电材料形成栅导电层43之后,形成多个选择栅沟槽6的过程中,需要刻蚀堆叠结构4中的绝缘层40和栅导电层43,降低了制备工艺的难度。

[0194]

此外,通过选择栅沟槽6和栅极隔槽8在空腔42中沉积栅导电材料,以在空腔42内形成栅导电层43,以将多个第一牺牲层41替换成多个栅导电层43。然后,去除选择栅沟槽6中的栅导电材料,在选择栅沟槽6内形成顶部选择栅切线60,以在相邻两个栅极隔槽8之间形成多个顶部选择栅切线60,可进一步将存储块b划分为多个子存储块b1,以提高半导体结构200的有效沟道孔的数量,从而增加存储器的存储密度。

[0195]

此外,本公开的一些实施例还提供了一种半导体结构,如图3a和图3b所示,半导体结构200包括源极层13,设置于源极层13上的堆叠结构4,堆叠结构4包括层叠设置的多个膜层对4b,每个膜层对4b包括相邻的绝缘层40和栅导电层43。

[0196]

需要说明的是,上述段落中的“堆叠结构”属于半导体结构200中的结构(产品结构),而在前述半导体结构的制备方法中所提到的“堆叠结构”属于制备过程中的结构,二者的区别在于,制备过程中的堆叠结构包括交替设置的多个绝缘层40和多个第一牺牲层41,而半导体结构200中的堆叠结构包括交替设置的多个绝缘层40和多个栅导电层43。

[0197]

如图3a所示,堆叠结构4设有多个栅极隔槽8和多个选择栅沟槽6,相邻两个栅极隔槽8之间设置有多个选择栅沟槽6。如图3b所示,栅极隔槽8贯穿堆叠结构4,选择栅沟槽6贯穿堆叠结构4中远离源极层13一侧的至少一个绝缘层40和至少一个栅导电层43,即,选择栅沟槽6贯穿位于堆叠结构4顶部的至少一个绝缘层40和至少一个栅导电层43。半导体结构200还包括设置于选择栅沟槽6内的顶部选择栅切线60。

[0198]

本公开的上述半导体结构200,多个栅极隔槽8用于将半导体结构200划分为多个存储块。相邻两个栅极隔槽8之间设置有多个选择栅沟槽6,且选择栅沟槽6内设置有顶部选择栅切线60,即相邻两个栅极隔槽8之间设置有多个顶部选择栅切线60,顶部选择栅切线

60,用于切割栅导电层43,可进一步将存储块划分为多个子存储块,以提高半导体结构的有效沟道孔的数量,从而增加存储器的存储密度。

[0199]

本公开的一些实施例还提供了一种存储系统300,如图7和图8所示,该存储系统300包括控制器301,以及如上述任一实施例中所述的三维存储器100。其中,该控制器301可以耦合至三维存储器100,且用于控制三维存储器100存储数据。

[0200]

示例性地,上述存储系统300可以集成到各种类型的存储设备中,例如,包括在相同封装(例如,通用闪存存储(universal flash storage,简称ufs)封装或嵌入式多媒体卡(embedded multi media card,简称emmc)封装)中。也就是说,存储系统300可以应用于并且封装到不同类型的电子产品中,例如,移动电话、计算机(包括但不限于台式计算机、膝上型计算机、平板计算机、车辆计算机等)、电视机、机顶盒、游戏控制台、打印机、定位设备、车载设备、可穿戴电子设备、智能传感器、虚拟现实(virtual reality,简称vr)设备、增强现实(augmented reality,简称ar)设备或者其中具有储存器的任何其他合适的电子设备。

[0201]

示例性地,如图7所示,存储系统300可以包括:控制器301和一个三维存储器100。该存储系统300可以集成到存储器卡中。

[0202]

其中,存储器卡包括pc卡(pcmcia,个人计算机存储器卡国际协会)、紧凑型闪存(compact flash,简称cf)卡、智能媒体(smart media,简称sm)卡、存储器棒、多媒体卡(multimedia card,简称mmc)、安全数码(secure digital memory card,简称sd)卡、ufs中的任一种。

[0203]

示例性地,如图8所示,存储系统300可以包括:控制器301和多个三维存储器100。该存储系统300可以集成到固态硬盘(solid state drives,简称ssd)中。

[0204]

在一些实施例中,在存储系统300中,例如,控制器301可以被配置为,用于在低占空比环境中操作,例如,sd卡、cf卡、通用串行总线(universal serial bus,简称usb)闪存驱动器、或用于个人计算器、数字相机、移动电话等电子设备中使用的其他介质。

[0205]

又例如,控制器301被配置为,用于在高占空比环境ssd或emmc中操作,ssd或emmc用于智能电话、平板计算机、膝上型计算机等移动设备的数据储存器以及企业存储阵列。

[0206]

在一些实施例中,控制器301可以被配置为,管理存储在三维存储器100中的数据,并且与外部设备(例如主机)通信。在一些实施例中,控制器301还可以被配置为,控制三维存储器100的操作,例如,读取、擦除和编程操作。在一些实施例中,控制器301还可以被配置为,管理关于存储在或要存储在三维存储器100中的数据的各种功能,包括坏块管理、垃圾收集、逻辑到物理地址转换、损耗均衡中的至少一种。在一些实施例中,控制器301还被配置为,处理关于从三维存储器100读取的或者被写入到三维存储器100的数据的纠错码。

[0207]

当然,控制器301还可以执行任何其他合适的功能,例如,格式化三维存储器100。例如,控制器301可以通过各种接口协议中的至少一种与外部设备(例如,主机)通信。

[0208]

需要说明的是,接口协议包括usb协议、mmc协议、外围部件互连(pci)协议、pci高速(pci-e)协议、高级技术附件(ata)协议、串行ata协议、并行ata协议、小型计算机小型接口(scsi)协议、增强型小型磁盘接口(esdi)协议、集成驱动电子设备(ide)协议、firewire协议中的至少一种。

[0209]

本公开的上述实施例中,存储系统300包括上述任一实施例中提供的半导体结构200或三维存储器100,提高了存储系统300的存储容量。

[0210]

本公开的一些实施例还提供了一种电子设备,如图9所示,该电子设备400包括如上述实施例中所述的存储系统300。

[0211]

本公开的上述实施例中,电子设备400包括上述实施例中提供的存储系统300,可提高电子设备400的存储容量。

[0212]

示例性地,上述电子设备400包括如下至少一种:手机、台式计算机、平板电脑、笔记本电脑、服务器、车载设备、可穿戴设备、移动电源。

[0213]

以上所述仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:吴林春;张坤;周文犀

- 技术所有人:长江存储科技有限责任公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、贺老师:氮化物陶瓷、光功能晶体材料及燃烧合成制备科学及工程应用

- 2、杨老师:工程电磁场与磁技术,无线电能传输技术

- 3、许老师:1.气动光学成像用于精确制导 2.人工智能方法用于数据处理、预测 3.故障诊断和健康管理

- 4、王老师:智能控制理论及应用;机器人控制技术

- 5、李老师:1.自旋电子学 2.铁磁共振、电磁场理论

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....