1.本发明涉及半导体放电加工技术领域,具体涉及一种提高半导体材料放电加工效率的进电端表面预处理方法。

背景技术:2.半导体材料因其具有独特的物理化学性质,广泛地应用在国防、通讯、电子、航空航天、高能物理、光学等领域,且随着科技的发展,其需求量越来越大。

3.由于半导体具有高脆性、高硬度和低断裂韧性的特点,常用的内圆切割和砂线切割等以依靠机械磨削作用去除材料的传统的加工方法极易导致硅晶体崩碎、断裂,可加工性较差。尤其涉及到一些特殊零件的加工,例如我国大科学装置中单色器所需的硅片,为了避免加工中出现晶格畸变现象的产生,需要无应力加工,此外还需要满足大尺寸、高晶向精度的加工要求,传统的加工方法无法满足要求。电火花线切割是一种非接触、无宏观切削力的加工方法,并且不受材料硬度和脆性等物理特性的影响,同时,电火花线切割机床可以满足大尺寸以及高晶向精度的加工需求,因此该方法特别适合加工硅晶体。

4.但电火花线切割方法加工效率低,因此严重影响了该方法在半导体加工行业中的发展。在电火花放电加工中,半导体需要与导电的金属基体(导线或工作台)接触,从而形成放电加工回路。半导体的放电加工不同于金属放电加工,受半导体特殊性质的影响,与其的接触界面会形成接触势垒,一处是电极丝与半导体之间的放电端势垒,另一处是进电金属与半导体之间的进电端势垒。两处势垒的存在影响了进电的效果,增加了回路的电阻率,限制了电流的提升,也增加了脉冲电源的负载,需要更高的脉冲电源开路电压,这些因素使得半导体放电加工效率低。如果降低半导体与金属之间的接触势垒,甚至消除了势垒形成欧姆接触的界面,放电加工回路的电阻率可以显著改善,从而提高放电加工的效率。

5.目前,在半导体放电加工领域,减小接触势垒的方法大多是在真空的条件下,利用蒸发、扩散和离子溅射等工艺在半导体表层沉积金属。这些工件预处理方法虽有一定的成效,但大对设备要求高,过程复杂,处理时间长,生产成本高,不利于在半导体放电加工领域的普及。

技术实现要素:6.本发明的目的是提供一种提高半导体材料放电加工效率的进电端表面预处理方法,能有效解决现有减小接触势垒方法对设备要求高、过程复杂、处理时间长以及生产成本高的问题。

7.为解决上述技术问题,本发明采用了以下技术方案:

8.一种提高半导体材料放电加工效率的进电端表面预处理方法,包括以下步骤:先在半导体进电端表面制备一层导电涂层,再对导电涂层部分进行激光辐照、形成蚀除坑,最后在原导电涂层上再涂覆一层导电涂层。

9.其中,激光辐照采用的激光类型为脉冲激光,且是按照点状排布扫描的。

10.其中,半导体材料可以为硅或锗或其它半导体材料;导电涂层的材料可以为导电金属、导电合金或石墨。

11.另外,导电涂层是通过丝网印刷法涂设的。

12.该提高半导体材料放电加工效率的进电端表面预处理方法具体包括以下步骤:

13.s1、将硅片置于丝印网板下,且二者之间存在间隙,之后将导电材料放置在网纱上,利用刮板将导电材料均匀涂覆在硅片上,形成涂层;

14.s2、将涂有涂层的硅片置于激光机下,脉冲激光照射在涂层表面,涂层表面形成蚀除坑;

15.s3、将步骤s2的硅片再次放置在丝印网板下,再涂覆一层导电材料,填满蚀除坑。

16.其中,放电加工的方法是利用极间脉冲放电的电蚀作用来蚀除材料的加工方法;且放电加工的方法为电火花线切割、电火花成型加工、电火花高速小孔加工、电火花铣削加工或微细电火花加工方法等。

17.上述技术方案中提供的提高半导体材料放电加工效率的进电端表面预处理方法,先在半导体进电端表面制备一层导电涂层,再对涂层部分进行激光辐照,激光辐照可以使照射处温度迅速升高,涂层的部分材料会熔化、气化而蚀除,形成蚀除坑;同时激光束投射到材料表面产生的热效应,在高温熔化、爆炸冲击等因素的综合作用下,涂层的原子会向半导体表层扩散,从而增大半导体表层的掺杂浓度,减小或消除进电端的接触势垒。本发明的提高半导体材料放电加工效率的进电端表面预处理方法,成本低、操作简单且省时省力,可有效提高放电回路的导电性,改善半导体放电加工的可加工性。

附图说明

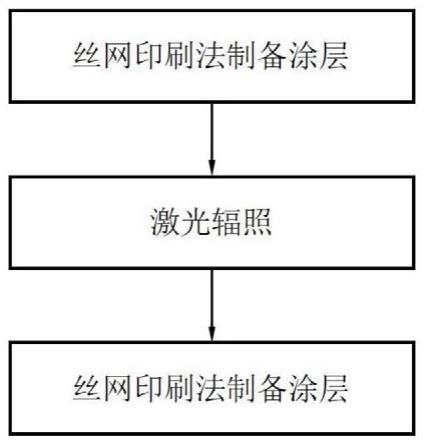

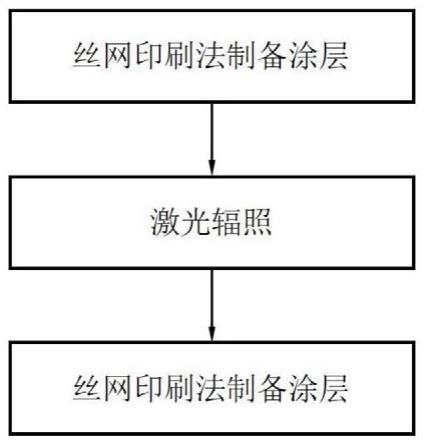

18.图1为本发明提高半导体材料放电加工效率的进电端表面预处理方法的工艺流程图;

19.图2为本实施例丝网印刷法制备涂层示意图;

20.图3为激光辐照法原理的示意图;

21.图4为激光辐照后的样件表面;

22.图5为测得的伏安特性曲线图。

23.图中:1.硅片;2.丝印网板;3.间隙;4.刮板;5.导电材料;6.网纱;7.涂层;8.脉冲激光;9.激光打标机;10.银原子;11.掺杂层。

具体实施方式

24.为了使本发明的目的及优点更加清楚明白,以下结合实施例对本发明进行具体说明。应当理解,以下文字仅仅用以描述本发明的一种或几种具体的实施方式,并不对本发明具体请求的保护范围进行严格限定。

25.本发明采取的技术方案如图1~3所示,一种提高半导体材料放电加工效率的进电端表面预处理方法,具体包括以下步骤:

26.第一步,选取尺寸为30mm*30mm*1mm、电阻率为2.2ω

·

cm的硅片1;

27.第二步,采用丝网印刷法,将硅片1置于丝印网板2下,二者存在间隙3,将导电材料5(本实施例采用银浆)放置在网纱6上,利用刮板4将导电材料5均匀涂覆在硅片1上,形成涂

层7(0.05mm~0.1mm);

28.第三步,测量该硅片1的伏安特性曲线51记录在图5中;

29.第四步,将硅片1至于激光打标机9下,激光打标机产生脉冲激光8按照点状排布扫描方式照射在涂层7的表面,激光辐照过程产生的热效应使得银原子10向硅片1的表层扩散形成掺杂层11;激光辐照后的表面如图4所示,表面存在因激光辐照形成的蚀除坑;

30.第五步,测量该硅片1的伏安特性曲线52记录在图5中;

31.第六步,将硅片1再次放置在丝印网板2下,再涂覆一层导电材料(0.05mm~0.1mm),填满蚀除坑;

32.第七步,测量该硅片1的伏安特性曲线53记录在图5中。

33.比较图5的三条伏安特性曲线,伏安特性曲线52与伏安特性曲线51几乎重合,说明了在激光辐照形成的蚀除坑减小了进电面积、增加了接触势垒的情况下,两条曲线所表现出回路中的电阻率相差不大,说明本发明方法存在有利于减小回路电阻的积极因素。

34.当经过再次涂覆导电材料时,硅片进电端面的进电面积与未经过激光辐照的进电面积相同,此时本发明的有益效果得以体现:伏安特性曲线53的斜率明显大于伏安特性曲线51和51的斜率,即再次涂覆一层导电材料的涂层能够大大增加了回路中的导电性,使得在相同脉冲电压情况下,可以获得更高的加工电流,从而得到更大的加工效率。

35.上面结合实施例和附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,对于本技术领域的普通技术人员来说,在获知本发明中记载内容后,在不脱离本发明原理的前提下,还可以对其作出若干同等变换和替代,这些同等变换和替代也应视为属于本发明的保护范围。