半导体结构及其形成方法、堆叠结构及晶圆堆叠方法与流程

本公开涉及半导体,涉及但不限于一种半导体结构及其形成方法、堆叠结构及晶圆堆叠方法。

背景技术:

1、在高度集成化的半导体发展的趋势下,多晶圆堆叠通常采用混合键合工艺实现晶圆之间的键合。目前,混合键合的铜键合垫使用大马士革工艺制作,为了确保晶圆之间的键合良率及电性连接,需要将待键合表面平坦化到一定程度,同时保证铜键合垫的凹陷或者凸起在10纳米(nm)或者5nm以下,具有极高的工艺难度。

2、相关技术中,晶圆堆叠过程中,铜键合垫在键合时发生热膨胀及扩散形成完整的堆叠结构,然而,如果平坦化制程没有将铜键合垫的凸起或者凹陷控制在10nm或者5nm以下,那么,在晶圆键合过程中堆叠界面之间就会形成空洞,或者,发生晶圆分层,导致键合失效。另外,位于键合垫外围的阻挡层在键合过程中也会发生破裂,增加晶圆堆叠结构漏电的风险,导致键合间距的微缩困难。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其形成方法、堆叠结构及晶圆堆叠方法。

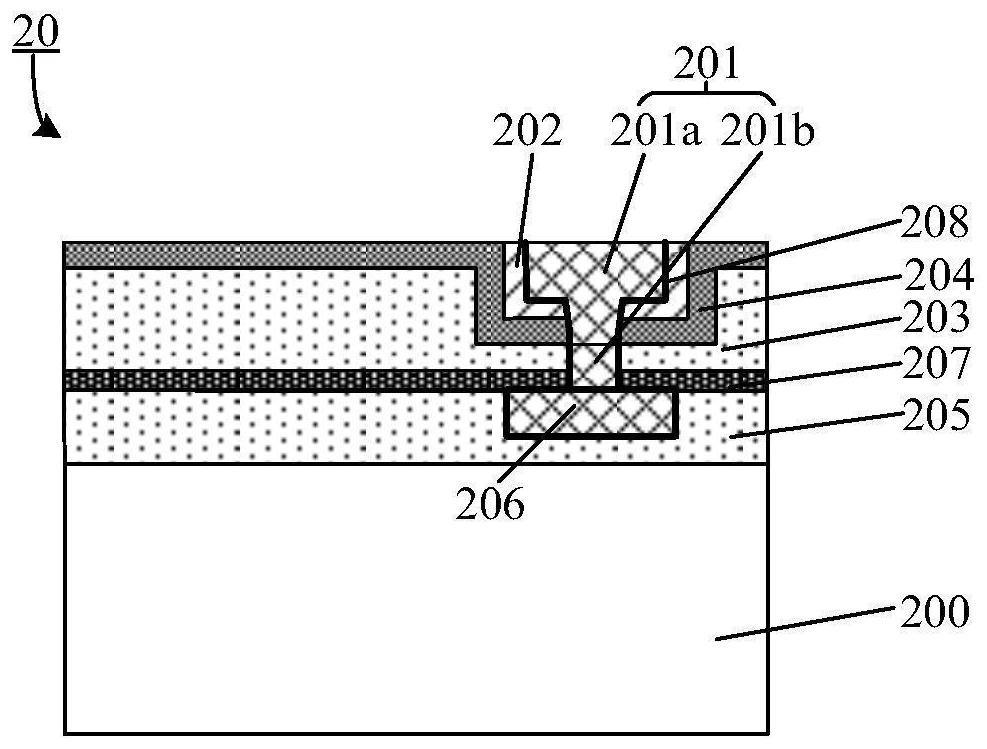

2、第一方面,本公开实施例提供一种半导体结构,包括:顶层金属层和缓冲层;

3、其中,所述顶层金属层位于半导体衬底表面的第一介质层中,且所述顶层金属层贯穿所述第一介质层;

4、所述缓冲层位于所述顶层金属层与所述第一介质层之间。

5、在一些实施例中,所述缓冲层包括缓冲材料;所述缓冲材料包括有机材料、无机材料和复合材料中的至少一种或任一组合。

6、在一些实施例中,所述第一介质层包括相互贯通的第一沟槽和第二沟槽;其中,所述第一沟槽的开口尺寸大于所述第二沟槽的开口尺寸;

7、所述顶层金属层包括位于所述第一沟槽中的第一顶层金属层、和位于所述第二沟槽中的第二顶层金属层。

8、在一些实施例中,所述缓冲层的顶表面与所述第一顶层金属层的顶表面平齐。

9、在一些实施例中,所述半导体结构还包括键合层;所述键合层位于所述缓冲层与所述第一介质层之间,和/或,所述顶层金属层与所述第一介质层之间。

10、在一些实施例中,所述键合层包括键合材料;所述键合材料包括硅氧化物、硅氮化物、硅碳氮化物和硅氮氧化物中的至少一种或任一组合。

11、在一些实施例中,所述缓冲层之间的键合强度大于所述键合层之间的键合强度。

12、在一些实施例中,所述缓冲层的弹性模量小于所述键合层的弹性模量。

13、在一些实施例中,所述半导体结构还包括位于所述半导体衬底表面的第二介质层和位于所述第二介质层中的底层金属层;其中,所述第一介质层位于所述第二介质层之上;

14、所述底层金属层与所述第二顶层金属层连接。

15、在一些实施例中,所述半导体结构还包括位于所述第一介质层和所述第二介质层之间的刻蚀停止层;

16、其中,所述第二沟槽贯穿所述刻蚀停止层。

17、在一些实施例中,所述半导体结构还包括:阻挡层;所述阻挡层位于所述顶层金属层外侧壁及底部。

18、第二方面,本公开实施例提供一种半导体结构的制作方法,所述方法包括:

19、提供半导体衬底,所述半导体衬底的表面形成有第一介质层;所述第一介质层包括第一沟槽,且所述第一沟槽的深度小于所述第一介质层的厚度;

20、在所述第一介质层的表面和所述第一沟槽的内壁形成初始缓冲层;

21、去除所述第一沟槽底部的部分初始缓冲层和部分第一介质层,形成贯穿所述第一介质层的第二沟槽和缓冲层;

22、在所述第一沟槽和所述第二沟槽中填充金属材料,形成顶层金属层。

23、在一些实施例中,在形成所述第一介质层之前,所述方法还包括:

24、在所述半导体衬底的表面形成第二介质层;

25、在所述第二介质层中形成底层金属层;

26、在所述第二介质层和所述底层金属层的表面形成初始刻蚀停止层;所述第二顶层金属层与所述底层金属层连接,所述初始刻蚀停止层位于所述第一介质层和所述第二介质层之间。

27、在一些实施例中,所述方法包括:

28、在形成所述初始缓冲层之前,在所述第一介质层的表面和所述第一沟槽的内部形成初始键合层;

29、去除所述第一沟槽底部的部分初始缓冲层、部分初始键合层、部分第一介质层和部分初始刻蚀停止层,形成贯穿所述第一介质层和所述初始刻蚀层的第二沟槽;

30、剩余的初始缓冲层、剩余的初始键合层和剩余的初始刻蚀停止层分别形成所述缓冲层、键合层和刻蚀停止层。

31、在一些实施例中,所述顶层金属层包括位于所述第一沟槽中的第一顶层金属层、和位于所述第二沟槽中的第二顶层金属层;

32、所述在所述第一沟槽和所述第二沟槽中填充金属材料,形成顶层金属层,包括:

33、在所述第一沟槽中的缓冲层和键合层的内壁、和所述第二沟槽中的第一介质层和刻蚀停止层的内壁依次形成阻挡层和种子层;

34、在所述种子层的表面电镀所述金属材料,形成所述第一顶层金属层和所述第二顶层金属层;

35、对所述第一顶层金属层和所述缓冲层进行平坦化处理,直至暴露出所述键合层的表面。

36、第三方面,本公开实施例提供一种堆叠结构,包括:面对面堆叠的第一晶圆和第二晶圆;所述第一晶圆和所述第二晶圆均至少具有上述半导体结构;

37、其中,所述第一晶圆的顶层金属层与所述第二晶圆的顶层金属层对准、所述第一晶圆的缓冲层与所述第二晶圆的缓冲层对准,且所述第一晶圆的键合层与所述第二晶圆的键合层对准。

38、在一些实施例中,所述缓冲层之间的键合强度大于所述键合层之间的键合强度。

39、在一些实施例中,所述缓冲层的弹性模量小于所述键合层的弹性模量。

40、第四方面,本公开实施例提供一种晶圆堆叠方法,所述方法包括:

41、提供具有上述半导体结构的第一晶圆和第二晶圆;

42、将所述第一晶圆与所述第二晶圆面对面对准,以实现所述第一晶圆与所述第二晶圆的堆叠。

43、在一些实施例中,所述第一晶圆和所述第二晶圆均包括位于第一介质层中的顶层金属层、位于所述顶层金属层与所述第一介质层之间的缓冲层、和位于所述缓冲层与所述第一介质层之间的键合层;其中,所述第一介质层分别位于所述第一晶圆和所述第二晶圆的表面;

44、所述将所述第一晶圆与所述第二晶圆面对面对准,以实现所述第一晶圆与所述第二晶圆的堆叠,包括:

45、将所述第一晶圆的顶层金属层、缓冲层和键合层分别与所述第二晶圆的顶层金属层、缓冲层和键合层进行面对面对准,以实现所述第一晶圆与所述第二晶圆的堆叠。

46、本公开实施例提供的半导体结构及其形成方法、堆叠结构及晶圆堆叠方法,其中,半导体结构包括:顶层金属层和缓冲层;顶层金属层位于半导体衬底表面的第一介质层中,且顶层金属层贯穿第一介质层;缓冲层位于顶层金属层与第一介质层之间。由于本公开实施例提供的半导体结构包括位于顶层金属层和第一介质层之间的缓冲层,缓冲层在半导体结构键合过程中可以有效容纳顶层金属层扩散导致的横向膨胀,如此,可以防止由于顶层金属层横向膨胀受限过多导致纵向膨胀,进而产生的半导体结构之间的分层。

- 还没有人留言评论。精彩留言会获得点赞!