半导体封装结构的制作方法

1.本发明涉及半导体封装技术,尤其涉及一种半导体封装结构。

背景技术:

2.随着对更多功能和更小装置的需求不断增加,垂直堆栈两个或更多个封装的层迭封装(package-on-package,pop)技术变得越来越流行。pop技术减少了不同组件(例如控制器和储存设备)之间的线路长度。这提供了更好的电气性能,因为更短的互连布线会产生更快的信号传播并减少噪声和串扰缺陷。

3.尽管现有的半导体封装结构通常是足够的,但是它们在各个方面都不是令人满意的。例如,满足将不同组件整合到一个封装中的通道要求是一项挑战。因此,需要进一步改进半导体封装结构以提供信道设计的灵活性。

技术实现要素:

4.据一些实施例,提供了一种半导体封装结构。半导体封装结构包括前侧重布线层、堆栈结构、后侧重布线层、第一ip核以及第二ip核。堆栈结构设置在前侧重布线层上方并且包括第一半导体裸晶和第一半导体裸晶上方的第二半导体裸晶。后侧重布线层配置于堆栈结构上方。第一ip核配置于堆栈结构中并通过第一走线通道电性耦合于前侧重布线层。第二ip核配置于堆栈结构中并通过第二走线通道电性耦合后侧重布线层,其中第二走线信道与第一走线信道分离且与前侧重布线层电性绝缘。

5.根据一些实施例,提供了一种半导体布线结构。半导体布线结构包括第一封装结构、第一走线通道以及第二走线通道。第一封装结构具有前侧和后侧,并且包括具有第一ip核和第二ip核的堆栈结构。第一走线通道将第一ip核电性耦合到第一封装结构前侧的第一重布线层。第二走线通道独立地电性耦合第二ip核至第一封装结构后侧上的第二重布线层,其中第二走线信道与第一布线信道分离且与第一重布线层电性绝缘。

6.在阅读了在各个附图和附图中示出的优选实施例的以下详细描述之后,本发明的这些和其他目的对于本领域普通技术人员来说无疑将变得显而易见。

附图说明

7.在附图的图中,通过示例而非限制的方式示出了本发明,在附图中,相似的附图标记指示相似的元件。当结合某实施例描述特定的特征、结构或特性时,应当认为,结合其他实施例来实现这样的特征、结构或特性属于本领域技术人员的知识范围,不论是否没有明确指示。

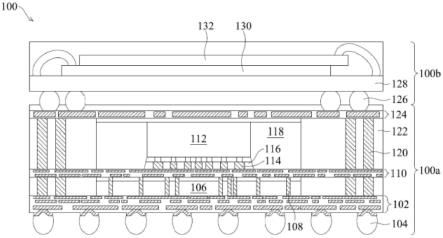

8.图1是根据一些实施例的示例性半导体封装结构的截面图;

9.图2a-2d是根据一些实施例的示例性半导体封装结构中的堆栈结构的截面图;

10.图3是根据一些实施例的示例性半导体封装结构的截面图;

11.图4是根据一些实施例的示例性半导体封装结构的截面图;

12.图5是根据一些实施例的示例性半导体封装结构的截面图;

13.图6是根据一些实施例的示例性半导体封装结构的截面图;以及

14.图7是根据一些实施例的示例性半导体封装结构的截面图。

具体实施方式

15.以下描述是实施本发明的最佳设想模式。该描述是为了说明本发明的一般原理而进行的,不应被理解为限制性的。本发明的范围通过参考所附权利要求来确定。

16.本发明将结合具体实施例并参考某些附图进行描述,但本发明不限于此,仅受权利要求的限制。所描述的附图只是示意性的并且是非限制性的。在附图中,为了说明的目的,一些组件的尺寸可能被夸大而不是按比例绘制。尺寸和相对尺寸不对应于本发明实践中的实际尺寸。

17.根据本公开的一些实施例描述半导体封装结构和半导体布线结构。半导体封装结构为装置(device)和ip核(ip core)(例如内存器件和内存ip核)提供单独的走线通道(routing channel),从而可以提高走线通道设计的灵活性。

18.图1是根据本公开的一些实施例的半导体封装结构100的截面图。额外的特征可以添加到半导体封装结构100。对于不同的实施例,可以替换或消除下面描述的一些特征。为了简化图示,仅示出了半导体封装结构100的一部分。

19.如图1所示,根据一些实施例,半导体封装结构100包括垂直堆栈的第一封装结构100a和第二封装结构100b。第一封装结构100a具有前侧(frontside)及与所述前侧相对的后侧(backside)。第一封装结构100a在其前侧具有第一重布线层102,而在其后侧具有第二重布线层124。因此,第一重布线层102也可称为前侧重布线层102,而第二重布线层124也可称为后侧重布线层124。

20.第一重布线层102包括一个或多个导电层和钝化层,其中一个或多个导电层可以设置在一个或多个钝化层中。导电层可包括金属,例如铜、钛、钨、铝等或其组合。在一些实施例中,钝化层包括聚合物层,例如聚酰亚胺(pi)、聚苯并恶唑(pbo)、苯并环丁烯(bcb)、环氧树脂等或其组合。或者,钝化层可包括介电层,例如氧化硅、氮化硅、氮氧化硅等或其组合。第二重布线层124的材料可以与第一重布线层102的材料类似,在此不再赘述。

21.如图1所示,根据一些实施例,第一重布线层102包括比第二重布线层124更多的导电层和钝化层。第一重布线层102可以比第二重布线层124厚,但本公开不限于此。例如,第二重布线层124可以比第一重布线层102厚或基本等于第一重布线层102。

22.在一些实施例中,第一封装结构100a包括多个导电结构104,位于第一重布线层102下方并电性耦合到第一重布线层102。在一些实施例中,导电结构104包括导电材料,例如金属导电结构104可以包括微凸块、受控塌陷芯片连接(c4)凸块、球栅数组(bga)球等或其组合。

23.在一些实施例中,第一封装结构100a包括堆栈结构,所述堆栈结构包括垂直堆栈在第一重布线层102上方的第一半导体裸晶(die)106和第二半导体裸晶112。根据一些实施例,第一半导体裸晶106和第二半导体裸晶112各自独立地包系统单芯片器件(soc)、逻辑器件、内存器件、射频(rf)器件等或其任何组合。例如,第一半导体裸晶106和第二半导体裸晶112可以各自独立地包括微控制单元(mcu)裸晶、微处理器单元(mpu)裸晶、电源管理集成电

路(pmic)裸晶、全球定位系统(gps)器件、中央处理器(cpu)裸晶、图形处理单元(gpu)裸晶、输入输出(io)裸晶、动态随机存取内存(dram)ip核、静态随机存取内存(sram)、高带宽内存(hbm)等,或它们的任何组合。

24.尽管两个半导体裸晶,第一半导体裸晶106和第二半导体裸晶112,在图1中示出,但也可能有两个以上的半导体裸晶。例如,堆栈结构可以包括垂直堆栈的三个半导体裸晶。或者,堆栈结构可以包括四个半导体裸晶,其中两个半导体裸晶垂直堆栈在一个半导体裸晶上方,并且另一个半导体裸晶布置在该半导体裸晶上方并且与两个半导体裸晶相邻。在一些实施例中,堆栈结构还包括一个或多个被动组件(未示出),例如电阻、电容、电感等或其组合。

25.参照图1,第一半导体裸晶106包括多个通孔108,其电性耦合到第一重布线层102。通孔108可以由诸如金属的导电材料形成。例如,通孔108可以由铜形成。在图1中,通孔108具有实质上垂直的侧壁并从第一半导体裸晶106的顶面延伸至第一半导体裸晶106的底面,但本公开不限于此。第一半导体裸晶106中的通孔108可以具有其他配置和数量。

26.在一些实施例中,第一封装结构100a包括位于第一重布线层102和第二重布线层124之间的第三重布线层110。如图1所示,第三重布线层110可以设置在第一半导体裸晶106的顶面和第二半导体裸晶112的底面之间,并且可以延伸超出第一半导体裸晶106的侧壁和第二半导体裸晶112的侧壁。第三重布线层110可以电性耦合到第一半导体裸晶106、第一半导体裸晶106中的通孔108和第二半导体裸晶112。

27.第三重布线层110的材料可以与第一重布线层102的材料类似,在此不再赘述。如图1所示,第一重布线层102包括比第三重布线层110更多的导电层和钝化层,并且第三重布线层110包括比第二重布线层124更多的导电层和钝化层,但本公开不限于此。例如,第二重布线层124可以包括比第一重布线层102和第三重布线层110更多的导电层和钝化层。

28.通过设置第三重布线层110,可以在第一半导体裸晶106和第二半导体裸晶112之间形成额外的布线通道,这有助于布局规划的灵活性并节省裸晶凸块扇出宽度,如下所述和在图2a-2d所示出的。

29.图2a是根据一些实施例的半导体封装结构100中的堆栈结构200a的截面图。为了简化,仅示出了堆栈结构200a的一部分。在一些实施例中,堆栈结构200a包括第一半导体裸晶106和第二半导体裸晶112。

30.第一半导体裸晶106具有主动表面(active surface)106a和与主动表面106a相对的后侧表面(backside surface)106b。第二半导体裸晶112具有主动表面112a和与主动表面112a相对的后侧表面112b。第一半导体裸晶106和第二半导体裸晶112可以面对面(face to face,ftf)堆栈。即,第二半导体裸晶112的主动表面112a靠近第一半导体裸晶106的主动表面106a。

31.参照图2a,第一知识产权(intellectual property,ip)核101和第二ip核103可以设置在第一半导体裸晶106的主动表面106a上。在一些实施例中,第一ip核101用于控制第二封装结构100b(如图1所示),第二ip核103用于控制与第一重布线层102电性耦合的其他组件。

32.根据一些实施例,由于第三重布线层110设置在第一半导体裸晶106和第二半导体裸晶112之间,因此可以在它们之间形成额外的布线通道。因此,来自第一ip核101的信号和

来自第二ip核103的信号可以通过不同的走线信道,例如分别如路径101p和路径103p所示。具体地,第一ip核101的走线信道(以路径101p表示)可以经过第三重布线层110(如图1所示),第二ip核103的走线信道(以路径103p表示)可以穿过第一半导体裸晶106中的通孔108和第一重布线层102(如图1所示)。

33.即,与第一ip核101的走线通道和第二ip核103的走线通道都经过第一重布线层102相比,在本发明中为第一ip核101和第二ip核103提供了各自的走线通道。如此一来,这些走线通道可以单独优化以满足不同的通道要求。此外,第一ip核101的走线通道不会影响第二ip核103的走线通道,从而增加了通道设计的灵活性。

34.如图2a所示,第一ip核101和第二ip核103是分开并排设置的,但本公开不限于此。例如,根据一些其他实施例,第一ip核101可以被放置在第二ip核103中。或者,第一ip核101和第二ip核103可以设置在第一半导体裸晶102的不同边缘附近。另外,可以有两个以上的ip核。

35.图2b是根据一些实施例的半导体封装结构100中的堆栈结构200b的截面图。为了简化图,仅示出了堆栈结构200b的一部分。堆栈结构200b可以包括与图2a所示的堆栈结构200a相同或相似的组件,并且为了简单起见,将不再详细讨论那些组件。在以下实施例中,第一ip核101设置在第二半导体裸晶112的主动表面112a上,而第二ip核103设置在第一半导体裸晶106的主动表面106a上。

36.如图2b所示,来自第一ip核101的信号和来自第二ip核103的信号可以通过不同的走线信道,例如分别如路径101p和路径103p所示。具体地,第一ip核101的走线信道(以路径101p表示)可以经过第三重布线层110(如图1所示),第二ip核103的走线信道(以路径103p表示)可以穿过第一半导体裸晶106中的通孔108和第一重布线层102(如图1所示)。

37.图2c是根据一些实施例的半导体封装结构100中的堆栈结构200c的截面图。为了简化示意图,仅示出了堆栈结构200c的一部分。堆栈结构200c可以包括与图2a所示的堆栈结构200a相同或相似的组件,并且为了简单起见,将不再详细讨论那些组件。在以下实施例中,第一半导体裸晶106和第二半导体裸晶112可以面对背(face to back,ftb)堆栈。即,第二半导体裸晶112的主动表面112a靠近第一半导体裸晶106的后侧表面106b。

38.如图2c所示,第一ip核101和第二ip核103设置在第一半导体裸晶106的主动表面106a上。来自第一ip核101的信号和来自第二ip核103的信号可以通过不同的走线通道。例如,分别由路径101p和路径103p指示。具体地,第一ip核101的走线信道(以路径101p表示)可以穿过第一半导体裸晶106中的通孔108和第三重布线层110(如图1所示),并且走线通道第二ip核103的(以路径103p表示)可以通过第一重布线层102(如图1所示)。

39.图2d是根据一些实施例的半导体封装结构100中的堆栈结构200d的截面图。为了简化图标,仅示出了堆栈结构200d的一部分。堆栈结构200d可以包括与图2a所示的堆栈结构200a相同或相似的组件并且为了简单起见,将不再详细讨论那些组件。在以下实施例中,第一ip核101设置在第二半导体裸晶112的主动表面112a上,而第二ip核103设置在第一半导体裸晶106的主动表面106a上。

40.如图2d所示,来自第一ip核101的信号和来自第二ip核103的信号可以通过不同的走线信道,例如分别如路径101p和路径103p所示。具体地,第一ip核101的走线信道(以路径101p表示)可以经过第三重布线层110(如图1所示),第二ip核103的走线信道(以路径103p

表示)可以穿过第一重布线层102(如图1所示)。

41.参照图1,根据一些实施例中,在第三重布线层110和第二半导体裸晶112之间形成多个导电结构114。导电结构114可以将第二半导体裸晶112电性耦合到第三重布线层110。取决于走线通道设计和ip核的位置,走线信道还可以包括导电结构114。

42.在一些实施例中,导电结构114包括导电材料,例如金属。导电结构114可包括微凸块、受控塌陷芯片连接(c4)凸块、球栅数组(bga)球等或其组合。

43.在一些实施例中,底部填充材料116形成在第二半导体裸晶112和第三重布线层110之间,并填充导电结构114之间的间隙以提供结构支撑。底部填充材料116可以围绕每个导电结构114。在一些实施例中,底部填充材料116由聚合物形成,例如环氧树脂。在第二半导体裸晶112和第三重布线层110之间形成导电结构114之后,底部填充材料116可以通过毛细管力涂布。然后,可以通过任何合适的固化工艺来固化底部填充材料116。

44.如图1所示,第一封装结构100a包含一模制材料118,环绕第二半导体裸晶112及底部填充材料116,并覆盖部分第三重布线层110的顶面。在一些实施例中,模制材料118邻接第二半导体裸晶112的侧壁和第三重布线层110的顶面。模制材料118可以保护第二半导体裸晶112免受环境影响,从而防止第二半导体裸晶112由于例如应力、化学品和/或湿气所造成的伤害。

45.模制材料118可以包括非导电材料,例如可模制聚合物、环氧树脂、树脂等,或它们的组合。在一些实施例中,模制材料118以液体或半液体形式施加,然后通过任何合适的固化过程固化,例如热固化过程、uv固化过程等,或其组合。模制材料118可以用模具(未示出)成形或模制。

46.然后,可以通过诸如化学机械抛光(cmp)之类的平坦化工艺部分地去除模制材料118,直到暴露第二半导体裸晶112的顶面。在一些实施例中,模制材料118的顶面和第二半导体裸晶112的顶面基本上共面。如图1所示,模制材料118的侧壁可以与第一半导体裸晶106的侧壁共面。

47.在一些实施例中,多个导电柱120形成于邻近堆栈结构(包括第一半导体裸晶106和第二半导体裸晶112)和模制材料118处。导电柱120可以包括金属柱,例如如铜柱。在一些实施例中,导电柱120通过电镀工艺或任何其他合适的工艺形成。如图1所示,导电柱120可以具有基本上垂直的侧壁。

48.如图1所示,导电柱120可以设置在第一重布线层102和第二重布线层124之间,并且可以设置在第三重布线层110的顶表面和底表面上。导电柱120可以电性耦合到第一重布线层102、第二重布线层124和第三重布线层110。

49.导电柱120的位置和数量可以根据第一封装结构100a的走线设计进行调整。例如,在一些其他实施例中,导电柱120设置在第二重布线层124和第三重布线层110之间,而不设置在第一重布线层102和第三重布线层110之间。第二重布线层124通过导电柱120电性耦合到第三重布线层110,并且第三重布线层110通过第一半导体裸晶106中的通孔108电性耦合到第一重布线层102。

50.如图1所示,四个导电柱120设置在堆栈结构的相对侧,但本公开不限于此。例如,在堆栈结构的相对侧上的导电柱120的数量可以不同。或者,导电柱120可设置在堆栈结构的一侧。

51.如图1所示,第一封装结构100a包括围绕堆栈结构(包括第一半导体裸晶106和第二半导体裸晶112)、模制材料118和导电柱120的模制材料122。模制材料122可以填充在导电柱120以及堆栈结构与导电柱120之间的间隙。

52.如图1所示,模制材料122邻接第一半导体裸晶106和模制材料118的侧壁,并覆盖第一重布线层102的顶面、第二重布线层124的底面以及第三重布线层110的顶面和底面。模制材料122可以保护堆栈结构和导电柱120免受环境影响,从而防止堆栈结构和导电柱120由于例如应力、化学物质和/或湿气所造成的伤害。

53.在一些实施例中,模制材料122包括非导电材料,例如可模制聚合物、环氧树脂、树脂等,或它们的组合。在一些实施例中,模制材料122以液体或半液体形式施加,然后通过任何合适的固化过程固化,例如热固化过程、uv固化过程等,或其组合。模制材料122可以用模具(未示出)成形或模制。

54.然后,可以通过诸如化学机械抛光(cmp)的平坦化工艺部分地去除模制材料122,直到暴露导电柱120的顶面。在一些实施例中,模制材料122和导电柱120的顶面基本上共面。如图所示。如图1所示,模制材料122的侧壁可以与第一重布线层102、第二重布线层124和第三重布线层110的侧壁中的至少一个共面。

55.如图1所示,第二重布线层124可以设置在堆栈结构上方,并且覆盖第二半导体裸晶112的顶面、导电柱120的顶面和模制材料122的顶面。

56.如图1所示,根据一些实施例,第二封装结构100b设置在第一封装结构100a上方并且通过多个导电结构126电性耦合到第二重布线层124。在一些实施例中,导电结构126包括导电材料,例如金属。导电结构126可包括微凸块、受控塌陷芯片连接(c4)凸块、球栅数组(bga)球等或其组合。

57.如图1所示,根据一些实施例,第二封装结构100b包括基板128。基板128可以在其中具有布线结构。在一些实施例中,基板128的布线结构包括导电层、导电通孔、导电柱等或其组合。基板128的布线结构可由金属形成,例如铜、钛、钨、铝等或其组合。

58.基板128的布线结构可以设置在金属间介电(inter-metal dielectric,imd)层中。在一些实施例中,imd层可以由有机材料(例如聚合物基材)、非有机材料(例如氮化硅、氧化硅、氮氧化硅等)或它们的组合形成。可以在基板128中和基板128上形成任何期望的半导体组件。然而,为了简化图示,仅示出了平坦基板128。

59.如图1所示,根据一些实施例,第二封装结构100b包括基板128上方的半导体组件130和132。半导体组件130和132可以包括内存裸晶,例如动态随机存取内存(dram)。例如,半导体组件130和132可以是用于移动系统的双倍数据速率(ddr)同步动态随机存取内存(sdram)裸晶。在第二封装结构100b包括内存装置的实施例中,用于第二封装结构100b的ip核(例如第一ip核101)可以被称为内存ip核。

60.半导体组件130和132可以包括相同或不同的器件。在一些实施例中,第二封装结构100b还包括一个或多个被动组件(未示出),例如电阻、电容、电感等或其组合。

61.堆栈结构中的第一ip核101(如图2a-2d所示)可以通过第一布线通道电性耦合到第二封装结构100b,第一布线通道包括第三重布线层110、导电柱120和第二重布线层124。堆栈结构中的第二ip核103(如图2a-2d所示)可以通过包括第一重布线层110的第二布线通道电性耦合到导电结构104。在实施例中,根据ip核的位置,如上所述,第一布线通道或第二

布线通道还可以包括第一半导体裸晶106中的通孔108和/或导电结构114。

62.换句话说,ip核和第二封装结构100b之间的走线通道可以与其他走线通道分离,例如另一个ip核和导电结构104之间的走线通道。具体地,根据一些实施例ip核和第二封装结构100b之间的走线通道与第一重布线层110电性绝缘。因此,可以分别优化不同的走线信道,增加信道设计的灵活性。

63.图3是根据本公开的一些实施例的半导体封装结构300的截面图。需要说明的是,半导体封装结构300可以包括与图1所示的半导体封装结构100相同或相似的组件。为了简单起见,这些组件将不再详细讨论。在以下实施例中,布线通道包括在第一半导体裸晶106上方以及与第二半导体裸晶112相邻的导电柱134。

64.根据一些实施例,导电柱134电性耦合到第二重布线层124、第一半导体裸晶106和第一半导体裸晶106中的通孔108。在用于第二封装结构100b的ip核形成在第一半导体裸晶106的底部的实施例中,ip核和第二封装结构100b之间的布线通道可以包括第一半导体裸晶106中的通孔108、导电柱134以及第二重布线层124。在用于第二封装结构100b的ip核形成在第一半导体裸晶106的顶部的实施例中,ip核和第二封装结构100b之间的布线通道包括导电柱134和第二重布线层124。

65.导电柱134可以包括金属柱,例如铜柱。在一些实施例中,导电柱134通过电镀工艺或任何其他合适的工艺形成。导电柱134可以具有基本上垂直的侧壁。如图3所示,导电柱134可以被模制材料118所围绕。导电柱134可以具有基本上垂直的侧壁并且可以从模制材料118的底面延伸到模制材料118的顶面。

66.导电柱134的位置和数量可以根据第一封装结构100a的布线设计进行调整。例如,多于一个导电柱134可以设置在第一半导体裸晶106上方,并且可以设置为邻近第二半导体裸晶112的一侧或相对侧。此外,半导体封装结构300还可以包括一个或多个重布线层,例如图1中的第三重布线层110。

67.图4是根据本公开的一些实施例的半导体封装结构400的截面图。需要说明的是,半导体封装结构400可以包括与图1所示的半导体封装结构100相同或相似的组件。为了简单起见,这些组件将不再详细讨论。在以下实施例中,布线通道包括第二半导体裸晶112中的通孔136。

68.通孔136可以电性耦合到第二重布线层124、导电结构114、第一半导体裸晶106和第一半导体裸晶106中的通孔108。在用于第二封装结构100b的ip核形成于第一半导体裸晶106的底部的实施例中,ip核与第二封装结构100b之间的走线通道可包括第一半导体裸晶106中的通孔108、导电结构114、通孔136,以及第二重布线层124。在用于第二封装结构100b的ip核形成在第一半导体裸晶106的顶部上的实施例中,ip核和第二封装结构100b之间的走线信道可以包括导电结构114、通孔136和第二重布线层124。

69.在用于第二封装结构100b的ip核形成在第二半导体裸晶112的底部的实施例中,ip核和第二封装结构100b之间的布线通道可以包括通孔136和第二重布线层124。在用于第二封装结构100b的ip核形成在第二半导体裸晶112的顶部的实施例中,ip核和第二封装结构100b之间的走线通道可以包括第二重布线层124,并且可以忽略通孔136。

70.在这些实施例中,第二重布线层124和ip核之间的走线通道不延伸到第一半导体裸晶106和第二半导体裸晶112之外。特别地,第二重布线层124和ip核之间的走线通道通过

由第一半导体裸晶106和/或第二半导体裸晶112屏蔽的区域。

71.通孔136可以由任何导电材料形成,例如金属。举例而言,通孔136由铜形成。如图4所示,通孔136可以具有基本上垂直的侧壁并且可以从第二半导体裸晶112的顶面延伸到第二半导体裸晶112的底面,但是本公开不限于此。第二半导体裸晶112中的通孔136可以具有其他配置。

72.通孔136的位置和数量可以根据第一封装结构100a的布线设计进行调整。例如,可以在第二半导体裸晶112中设置多于一个通孔136。或者,半导体封装结构400还可以包括一个或多个重布线层(例如图1中的第三重布线层110)和/或一个或多个导电柱(例如图3中的导电柱134)。

73.图5是根据本公开的一些实施例的半导体封装结构500的截面图。需要说明的是,半导体封装结构500可以包括与图1所示的半导体封装结构100相同或相似的组件。为了简单起见,这些组件将不再详细讨论。在以下实施例中,较大的第一半导体裸晶106设置在较小的第二半导体裸晶112之上。

74.如图5所示,第二半导体裸晶112可以包括多个通孔138,其可以电性耦合到第一重布线层102、导电结构114和第一半导体裸晶106中的通孔108。通孔138可以由任何导电材料形成,例如金属。例如,通孔138可以由铜形成。如图5所示,通孔138可以每个都具有基本上垂直的侧壁并且可以从第二半导体裸晶112的顶面延伸到第二半导体裸晶112的底面。然而,第二半导体裸晶112中的通孔138可以具有其他配置和数量。

75.通孔138可以电性耦合到第一重布线层102、导电结构114、第一半导体裸晶106和第一半导体裸晶106中的通孔108。在用于第二封装结构100b的ip核形成于第二半导体裸晶112底部的实施例中,ip核与第二封装结构100b之间的走线通道可包括第二半导体裸晶112中的通孔138、导电结构114、第一半导体裸晶106中的通孔108以及第二重布线层124。在用于第二封装结构100b的ip核形成于第二半导体裸晶112顶部的实施例中,ip核与第二封装结构100b之间的走线信道可包括导电结构114、第一半导体裸晶106中的通孔108以及第二重布线层124。

76.在用于第二封装结构100b的ip核形成在第一半导体裸晶106的底部的实施例中,ip核和第二封装结构100b之间的布线通道可以包括第一半导体裸晶106中的通孔108和第二重布线层124。在用于第二封装结构100b的ip核形成在第一半导体裸晶106的顶部的实施例中,ip核和第二封装结构100b之间的走线通道可以包括第二重布线层124而通孔108可以省略。

77.在这些实施例中,第二重布线层124和ip核之间的走线通道不延伸到第一半导体裸晶106和第二半导体裸晶112之外。特别地,第二重布线层124和ip核之间的走线通道通过由第一半导体裸晶106和/或第二半导体裸晶112屏蔽的区域。

78.如图5所示,第一封装结构100a可以包括在第一半导体裸晶106下方并且与第二半导体裸晶112相邻的一个或多个导电柱140。导电柱140是可以选择的。导电柱140可以包括金属柱,例如铜柱。在一些实施例中,导电柱140通过电镀工艺或任何其他合适的工艺形成。

79.导电柱140可以电性耦合到第一重布线层102、第一半导体裸晶106和第一半导体裸晶106的通孔108。参照图5,每个导电柱140可以具有基本上垂直的侧壁。导电柱140可以被模制材料118围绕并且从模制材料118的顶面延伸到模制材料118的底面。

80.导电柱140的位置和数量可以根据第一封装结构100a的布线设计进行调整。如图5所示,两个导电柱140设置在邻近第二半导体裸晶112的相对侧,但本公开不限于此。例如,在堆栈结构的相对侧上的导电柱140的数量可以不同。或者,导电柱140可以设置在堆栈结构的一侧。

81.图6是根据本公开的一些实施例的半导体封装结构600的截面图。需要说明的是,半导体封装结构600可以包括与图1所示的半导体封装结构100相同或相似的组件。为了简单起见,这些组件将不再详细讨论。在以下实施例中,堆栈结构包括位于第一半导体裸晶106上方且与第二半导体裸晶112相邻的多个半导体组件142、144、146。

82.半导体组件142、144、146可以包括主动组件。例如,半导体组件142、144、146可以各自独立地包括系统单芯片器件(soc)、逻辑器件、内存器件、射频(rf)器件等,或其任何组合。例如,半导体组件142、144、146可以各自独立地包括微控制单元(mcu)器件、微处理器单元(mpu)器件、电源管理集成电路(pmic)器件、全球定位系统(gps)器件、中央处理单元(cpu)裸晶、图形处理单元(gpu)裸晶、输入输出(io)裸晶、动态随机存取内存(dram)ip核、静态随机存取内存(sram)、高带宽内存(hbm)等,或其任何组合。

83.在一些其他实施例中,半导体组件142、144、146包括被动组件,例如电阻、电容、电感等,或其组合。半导体组件142、144、146可包括相同或不同的装置。

84.半导体组件142、144、146可以电性耦合到第一半导体裸晶106。半导体组件142、144、146中的每一个可以被模制材料118包围和覆盖。应该注意的是,半导体组件142、144、146、第一半导体裸晶106和第二半导体裸晶112的位置和数量仅是示例性的,本公开不限于此。

85.例如,半导体组件142、144、146可以垂直堆栈。或者,堆栈结构可以包括垂直堆栈的两个半导体组件。在其他一些实施例中,堆栈结构可以包括四个半导体组件,其中两个半导体组件垂直堆栈在一个半导体组件上方,另一个半导体组件设置在该半导体组件上方并且与两个半导体组件相邻。

86.根据第一封装结构100a的走线设计,半导体封装结构600还可以包括一个或多个重布线层(例如图1中的第三重布线层110)、一个或多个导电柱(例如图3中的导电柱134)和/或半导体芯片中的一个或多个通孔(例如图4中的通孔136)。

87.图7是根据本公开的一些实施例的半导体封装结构700的截面图。需要说明的是,半导体封装结构700可以包括与图6所示的半导体封装结构600相同或相似的组件。为了简单起见,这些组件将不再详细讨论。在以下实施例中,堆栈结构包括在第一半导体裸晶106下方且与第二半导体裸晶112相邻的多个半导体组件142、144、146。

88.半导体组件142、144、146可以类似于图6中的半导体组件142、144、146,于此不再赘述。半导体组件142、144、146可电性耦合至第一半导体裸晶106。半导体组件142、144、146中的每一者可被模制材料118围绕且覆盖。应注意,本实施例中半导体组件142、144、146、第一半导体裸晶106和第二半导体裸晶112的数量及位置仅是说明性的,本公开不限于此。

89.例如,半导体组件142、144、146可以垂直堆栈。或者,堆栈结构可以包括垂直堆栈的两个半导体组件。在其他一些实施例中,堆栈结构可以包括四个半导体组件,其中两个半导体组件垂直堆栈在一个半导体组件上方,另一个半导体组件设置在该半导体组件上方并且与两个半导体组件相邻。

90.根据第一封装结构100a的走线设计,半导体封装结构700还可以包括一个或多个重布线层(例如图1中的第三重布线层110)、一个或多个导电柱(例如图3中的导电柱134)和/或半导体裸晶中的一个或多个通孔(例如图4中的通孔136)。

91.总之,通过在封装结构中的半导体裸晶中设置一个或多个重布线层、一个或多个导电柱和/或一个或多个通孔,可以实现封装结构中的ip核到另一个封装结构的单独走线信道。因此,可以单独优化走线信道,增加信道设计的灵活性。

92.虽然已经通过示例和优选实施例的方式描述了本发明,但是应当理解,本发明不限于所公开的实施例。相反,它旨在涵盖各种修改和类似的布置(这对于本领域技术人员来说是显而易见的)。因此,所附权利要求的范围应给予最广泛的解释以涵盖所有此类修改和类似布置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1