显示基板及其制备方法、显示装置与流程

1.本公开涉及显示技术领域,特别涉及一种显示基板及其制备方法、显示装置。

背景技术:

2.有机电致发光二极管(organic light-emitting diodes,oled)当有电流通过时,阳极产生的空穴和阴极产生的电子,在发光层复合并释放光,根据激发能量的不同可以发出不同能量的光子,对应不同颜色的光。使用oled器件作为显示材料的有机发光显示面板具有自发光、广视角、高对比度等优点,广泛应用于手机、电视、笔记本电脑等产品智能产品中,又由于其质量轻、厚度薄、具有抗弯折性能的特点,是目前国内外众多学者的研究重点。

技术实现要素:

3.本公开旨在至少解决现有技术中存在的技术问题之一,提出了一种显示基板及其制备方法、显示装置。

4.为实现上述目的,第一方面,本公开实施例提供了一种显示基板,包括:

5.衬底基板;

6.多个第一像素限定部,设置在所述衬底基板上;所述多个第一像素限定部沿第一方向延伸,且在第二方向上间隔设置;

7.多个第二像素限定部,设置在所述多个第一像素限定部背离所述衬底基板的一侧;所述多个第二像素限定部沿所述第二方向延伸,且在所述第一方向上间隔设置;所述多个第二像素限定部与所述多个第一像素限定部交叉设置;

8.多个第三像素限定部,部分所述第一像素限定部上设置有所述第三像素限定部,且相邻的两个所述第三像素限定部在所述衬底基板上的正投影间隔至少一个所述第一像素限定部在所述衬底基板上的正投影;所述多个第三像素限定部沿所述第一方向延伸,且在所述第二方向上间隔设置;其中,

9.所述第一像素限定部在所述衬底基板上的正投影覆盖位于该第一像素限定部之上的所述第三像素限定部在所述衬底基板上的正投影。

10.在一些实施例中,对于所述第一像素限定部在所述衬底基板上的正投影和位于该第一像素限定部之上的所述第三像素限定部在所述衬底基板上的正投影,其在所述第二方向上位于同一侧的边缘之间的宽度大于或等于10μm。

11.在一些实施例中,对于所述第一像素限定部在所述衬底基板上的正投影和位于该第一像素限定部之上的所述第三像素限定部在所述衬底基板上的正投影,其在所述第一方向上的中心线相互重合。

12.在一些实施例中,相邻设置的两个所述第三像素限定部在所述衬底基板上的正投影间隔至少n个所述第一像素限定部在所述衬底基板上的正投影,其中,n为正整数,且n大于或等于14。

13.在一些实施例中,所述显示基板还包括:

14.第一电极层,设置在所述衬底基板上,包括多个第一电极;所述第一像素限定部设置在相邻的两个所述第一电极之间;

15.发光层,设置在所述第一电极层背离所述衬底基板的一侧,包括发光材料;相邻的两个所述第二像素限定部之间设置有同种颜色的所述发光材料,且该发光材料覆盖相邻的两个所述第二像素限定部之间的所述第一像素限定部。

16.在一些实施例中,所述显示基板还包括:

17.第二电极层,设置在所述多个第一像素限定部、所述多个第二像素限定部和所述发光层背离所述衬底基板的一侧;

18.封装层,设置在所述第二电极层背离所述衬底基板的一侧。

19.第二方面,本公开实施例还提供了一种显示装置,包括:如上述实施例中任一所述的显示基板。

20.第三方面,本公开实施例还提供了一种显示基板的制备方法,包括:

21.在衬底基板上形成多个第一像素限定部;其中,所述多个第一像素限定部沿第一方向延伸,且在第二方向上间隔设置;

22.在所述衬底基板上形成多个第二像素限定部;其中,所述多个第二像素限定部沿所述第二方向延伸,且在所述第一方向上间隔设置;所述多个第二像素限定部与所述多个第一像素限定部交叉设置;

23.在部分所述第一像素限定部上形成多个第三像素限定部;其中,相邻的两个所述第三像素限定部在所述衬底基板上的正投影间隔至少一个所述第一像素限定部在所述衬底基板上的正投影;所述多个第三像素限定部沿所述第一方向延伸,且在所述第二方向上间隔设置;所述第一像素限定部在所述衬底基板上的正投影覆盖位于该第一像素限定部之上的所述第三像素限定部在所述衬底基板上的正投影。

24.在一些实施例中,所述方法还包括:

25.在所述衬底基板上形成第一电极层;其中,所述第一电极层包括多个第一电极;所述第一像素限定部设置在相邻的两个所述第一电极之间;

26.在部分所述第一像素限定部上形成多个第三像素限定部之后,还包括:

27.在所述第一电极层背离所述衬底基板的一侧打印发光层;所述发光层包括发光材料;相邻的两个所述第二像素限定部之间设置有同种颜色的所述发光材料,且该发光材料覆盖两个所述第二像素限定部之间的所述第一像素限定部。

28.在一些实施例中,在所述第一电极层背离所述衬底基板的一侧打印发光层之后,还包括:

29.在所述多个第一像素限定部、所述多个第二像素限定部和所述发光层背离所述衬底基板的一侧形成第二电极层,得到发光器件;

30.封装所述发光器件。

附图说明

31.附图用来提供对本公开的进一步理解,并且构成说明书的一部分,与本公开的实施例一起用于解释本公开,并不构成对本公开的限制。通过参考附图对详细示例实施例进行描述,以上和其他特征和优点对本领域技术人员将变得更加显而易见,在附图中:

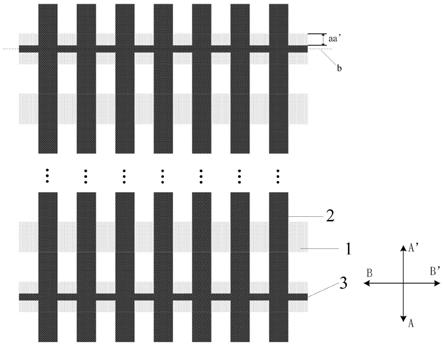

32.图1为本公开实施例提供的一种显示基板的结构示意图;

33.图2为本公开实施例提供的另一种显示基板的结构示意图;

34.图3为本公开实施例提供的一种显示基板的制备方法的流程图;

35.图4为本公开实施例提供的另一种显示基板的制备方法的流程图。

具体实施方式

36.为使本领域的技术人员更好地理解本公开的技术方案,下面结合附图对本公开提供的显示基板及其制备方法、显示装置进行详细描述。

37.在下文中将参考附图更充分地描述示例实施例,但是所述示例实施例可以以不同形式来体现且不应当被解释为限于本文阐述的实施例。反之,提供这些实施例的目的在于使本公开透彻和完整,并将使本领域技术人员充分理解本公开的范围。

38.本文所使用的术语仅用于描述特定实施例,且不意欲限制本公开。如本文所使用的,单数形式“一个”和“该”也意欲包括复数形式,除非上下文另外清楚指出。还将理解的是,当本说明书中使用术语“包括”和/或“由

……

制成”时,指定存在所述特征、整体、步骤、操作、元件和/或组件,但不排除存在或添加一个或多个其他特征、整体、步骤、操作、元件、组件和/或其群组。

39.将理解的是,虽然本文可以使用术语第一、第二等来描述各种元件,但这些元件不应当受限于这些术语。这些术语仅用于区分一个元件和另一元件。因此,在不背离本公开的指教的情况下,下文讨论的第一元件、第一组件或第一模块可称为第二元件、第二组件或第二模块。

40.除非另外限定,否则本文所用的所有术语(包括技术和科学术语)的含义与本领域普通技术人员通常理解的含义相同。还将理解,诸如那些在常用字典中限定的那些术语应当被解释为具有与其在相关技术以及本公开的背景下的含义一致的含义,且将不解释为具有理想化或过度形式上的含义,除非本文明确如此限定。

41.图1为本公开实施例提供的一种显示基板的结构示意图。如图1所示,该显示基板包括:衬底基板(图中未示出)、多个第一像素限定部1、多个第二像素限定部2和多个第三像素限定部3。

42.其中,多个第一像素限定部1设置在衬底基板上,其沿第一方向延伸,且在第二方向上间隔设置,第一方向和第二方向相交,图1中以bb’作为第一方向,以aa’作为第二方向,在一些实施例中,第一方向和第二方向可分别为行方向和列方向。

43.多个第二像素限定部2设置在多个第一像素限定部1背离衬底基板的一侧,其沿第二方向延伸,且在第一方向上间隔设置;第二像素限定部2与第一像素限定部1交叉设置;

44.对于多个第三像素限定部3,部分第一像素限定部1上设置有第三像素限定部3,且相邻的两个第三像素限定部3在衬底基板上的正投影间隔至少一个第一像素限定部1在衬底基板上的正投影;多个第三像素限定部沿第一方向延伸,且在第二方向上间隔设置;其中,第一像素限定部1在衬底基板上的正投影覆盖位于该第一像素限定部1之上的第三像素限定部3在衬底基板上的正投影,即在第二方向上,第三像素限定部3的宽度小于第一像素限定部1的宽度。

45.在一些实施例中,如图1所示,对于第一像素限定部1在衬底基板上的正投影和位

于该第一像素限定部1之上的第三像素限定部3在衬底基板上的正投影,二者在第二方向上位于同一侧的边缘之间的宽度(图中以aa’进行标识)大于或等于10μm;其中,在第三像素限定部3的两侧均预留一定宽度,由此在该预留出的区域中墨水成膜不受影响,继而第三像素限定部3的两侧的成膜状态和成膜均匀性能够得到保证。

46.在一些实施例中,在为第一像素限定部1的边缘和第三像素限定部3的边缘之间预留一定过渡区域的基础上,如图1所示,对于第一像素限定部1在衬底基板上的正投影和位于该第一像素限定部1之上的第三像素限定部3在衬底基板上的正投影,二者在第一方向上的中心线(图中以b进行标识)相互重合,该中心线即平行于该像素限定部在第二方向上的两侧边缘,且过该像素限定部在第二方向上的中间位置的直线。需要说明的是,对于上述的预留宽度至少为10μm,以及将第三像素限定部3设置在对应的第一像素限定部1的中间位置的设置方式,其仅为本公开实施例提供的一种具体化可选实施方式,其他设置方式也同样适用于本公开实施例的技术方案。

47.本公开实施例提供了一种显示基板,其包括设置在衬底基板上的多个第一像素限定部和多个第二像素限定部,多个第一像素限定部沿第一方向延伸,多个第二像素限定部沿第二方向延伸,第二像素限定部与第一像素限定部交叉设置,其对应line bank结构,基于该结构可实现各子像素之间墨水联通,每个子像素之间的墨水体积差异得到均化,可获得较均匀的薄膜,实现均匀发光;并且,该显示基板还包括设置在部分第一像素限定部上的第三像素限定部,该多个第三像素限定部沿第一方向延伸,且相邻的两个第三像素限定部在衬底基板上的正投影间隔至少一个第一像素限定部在衬底基板上的正投影,基于该第三像素限定部可保证在第三像素限定部两侧成膜不受影响,由此可使得联通子像素的边缘封端位置的墨水成膜状态与其他位置的成膜状态一致,避免在边缘封端位置出现发光不均的问题。

48.图2为本公开实施例提供的另一种显示基板的结构示意图。如图2所示,该结构基于图1所示的结构,该显示基板还包括:第一电极层(图中未示出)和发光层4。

49.其中,第一电极层设置在衬底基板上,包括多个第一电极;第一像素限定部1设置在相邻的两个第一电极之间。

50.发光层4设置在第一电极层背离衬底基板的一侧,包括发光材料;相邻的两个第二像素限定部2之间设置有同种颜色的发光材料,且该发光材料覆盖相邻的两个第二像素限定部2之间的第一像素限定部1;图中以红色发光材料r、绿色发光材料g和蓝色发光材料b为例,其分别对应红色子像素、绿色子像素和蓝色子像素;应当理解的是,采用该种颜色的发光材料以及图2中相应的子像素排布方式,其仅为本公开实施例提供的一种具体化可选实施方式,其他颜色的发光材料,如白色发光材料,以及其他像素排布方式,其同样适用于本公开实施例的技术方案。

51.具体地,发光层4在第二方向上联通,也就是说基于喷墨打印制备显示基板时,每一列同色子像素中部分子像素间的墨水是相互联通的,若以在第二方向上并排设置且联通的各子像素为同色的一个像素组,则像素组位于相邻的两个第二像素限定部2之间,覆盖该相邻的两个第二像素限定部2之间的第一像素限定部1,且第三像素限定部3分隔同一列上的各像素组。

52.需要理解的是,为清晰地体现显示基板上述各层的相对位置关系,在图2中以具有

一定透明度的区域表现发光层4覆盖第一像素限定部1的部分,也即两子像素间的联通部分。

53.在一些实施例中,第一像素限定部1和第二像素限定部2均为有机材料,其中第二像素限定部2为疏液性材料,第一像素限定部1采用亲液性材料。

54.在一些实施例中,第一像素限定部1的厚度小于第二像素限定部2的厚度;具体地,第一像素限定部1覆盖各第一电极的边缘,防止产生漏电,并且第一像素限定部1可限定出发光区域;基于厚度较小的第一像素限定部1可实现上述的每一列同色子像素之间相互联通的具体化实施方案。

55.具体地,联通子像素数量与成膜状态是相关联的,成膜状态即子像素的墨水成膜状态,具体可从成膜均匀性的角度进行体现;其中,由于每一列同色子像素之间相互联通,则各子像素之间的墨水体积差异能够得到均化,避免子像素与子像素之间成膜厚度的不均一,从而获得较均匀的薄膜;若以在同一列中联通的各子像素为同色的一个像素组,当联通的子像素的数量,也即像素组内的子像素的数量达到一定数值后,特别地,像素组内的子像素的数量达到15个后,像素组内的子像素的数量继续增加则各子像素的成膜均匀性也几乎不变。与上述理论相对应地,在一些实施例中,相邻设置的两个第三像素限定部3在衬底基板上的正投影间隔至少n个第一像素限定部1在衬底基板上的正投影,其中,n为正整数,且n大于或等于14;也就是说,相邻设置的两个第三像素限定部3之间间隔至少15个位于同一列且同色的子像素。

56.在一些实施例中,该显示基板还包括:第二电极层,设置在多个第一像素限定部1、多个第二像素限定部2和发光层4背离衬底基板的一侧;封装层,设置在第二电极层背离衬底基板的一侧;第一电极层、发光层和第二电极层构成发光器件;在一些实施例中,第一电极层和第一电极可称为阳极,第二电极层可称为阴极;在一些实施例中,该发光器件为oled器件,第一电极层和第二电极层之间出发光层外还包括其他有机功能层,如空穴注入层、空穴传输层、电子注入层和电子传输层等。

57.本公开实施例还提供了一种显示装置,包括:如上述实施例中任一的显示基板。

58.图3为本公开实施例提供的一种显示基板的制备方法的流程图。如图3所示,该方法包括:

59.步骤s1、在衬底基板上形成多个第一像素限定部。

60.其中,多个第一像素限定部沿第一方向延伸,且在第二方向上间隔设置。

61.步骤s2、在衬底基板上形成多个第二像素限定部。

62.其中,多个第二像素限定部沿第二方向延伸,且在第一方向上间隔设置;多个第二像素限定部与多个第一像素限定部交叉设置。

63.步骤s3、在部分第一像素限定部上形成多个第三像素限定部。

64.其中,相邻的两个第三像素限定部在衬底基板上的正投影间隔至少一个第一像素限定部在衬底基板上的正投影;多个第三像素限定部沿第一方向延伸,且在第二方向上间隔设置;第一像素限定部在衬底基板上的正投影覆盖位于该第一像素限定部之上的第三像素限定部在衬底基板上的正投影。

65.在一些实施例中,相邻设置的两个第三像素限定部3在衬底基板上的正投影间隔至少n个第一像素限定部1在衬底基板上的正投影,其中,n为正整数,且n大于或等于14。

66.在一些实施例中,对于第一像素限定部在衬底基板上的正投影和位于该第一像素限定部之上的第三像素限定部在衬底基板上的正投影,二者在第二方向上位于同一侧的边缘之间的宽度大于或等于10μm。

67.在一些实施例中,对于第一像素限定部在衬底基板上的正投影和位于该第一像素限定部之上的第三像素限定部在衬底基板上的正投影,二者在第一方向上的中心线相互重合。

68.图4为本公开实施例提供的另一种显示基板的制备方法的流程图。具体地,该方法为基于图3所示方法的一种具体化可选实施方式;如图4所示,该方法不仅包括步骤s1至步骤s3,还包括步骤s01,以及在步骤s3之后还包括步骤s4。下面仅对步骤s01和步骤s4进行详细描述。

69.步骤s01、在衬底基板上形成第一电极层。

70.其中,第一电极层包括多个第一电极;第一像素限定部设置在相邻的两个第一电极之间。

71.需要说明的是,本公开实施例对步骤s01和步骤s1至步骤s3的执行顺序不做限定,即步骤s01可在步骤s1至步骤s3之前执行,或者步骤s01在步骤s1至步骤s3之后执行,或者步骤s01与步骤s1至步骤s3穿插执行,其均适用于本公开实施例的技术方案。

72.在步骤s3,在部分第一像素限定部上形成多个第三像素限定部的步骤之后,还包括:

73.步骤s4、在第一电极层背离衬底基板的一侧打印发光层。

74.其中,发光层包括发光材料;相邻的两个第二像素限定部之间设置有同种颜色的发光材料,且该发光材料覆盖两个第二像素限定部之间的第一像素限定部。

75.在一些实施例中,在第一电极层背离衬底基板的一侧打印发光层时,还包括进行空穴注入层、空穴传输层、电子注入层和电子传输层的打印。

76.在一些实施例中,如图4所示,在步骤s4,在第一电极层背离衬底基板的一侧打印发光层的步骤之后,还包括:步骤s5和步骤s6。

77.步骤s5、在多个第一像素限定部、多个第二像素限定部和发光层背离衬底基板的一侧形成第二电极层,得到发光器件。

78.步骤s6、封装发光器件。

79.其中,在上述步骤s1至步骤s4的基础上形成第二电极层得到发光器件,并完成蒸镀封装过程。

80.本领域普通技术人员可以理解,上文中所公开方法中的全部或某些步骤、装置中的功能模块/单元可以被实施为软件、固件、硬件及其适当的组合。在硬件实施方式中,在以上描述中提及的功能模块/单元之间的划分不一定对应于物理组件的划分;例如,一个物理组件可以具有多个功能,或者一个功能或步骤可以由若干物理组件合作执行。某些物理组件或所有物理组件可以被实施为由处理器,如中央处理器、数字信号处理器或微处理器执行的软件,或者被实施为硬件,或者被实施为集成电路,如专用集成电路。这样的软件可以分布在计算机可读介质上,计算机可读介质可以包括计算机存储介质(或非暂时性介质)和通信介质(或暂时性介质)。如本领域普通技术人员公知的,术语计算机存储介质包括在用于存储信息(诸如计算机可读指令、数据结构、程序模块或其他数据)的任何方法或技术中

实施的易失性和非易失性、可移除和不可移除介质。计算机存储介质包括但不限于ram、rom、eeprom、闪存或其他存储器技术、cd-rom、数字多功能盘(dvd)或其他光盘存储、磁盒、磁带、磁盘存储或其他磁存储装置、或者可以用于存储期望的信息并且可以被计算机访问的任何其他的介质。此外,本领域普通技术人员公知的是,通信介质通常包含计算机可读指令、数据结构、程序模块或者诸如载波或其他传输机制之类的调制数据信号中的其他数据,并且可包括任何信息递送介质。

81.本文已经公开了示例实施例,并且虽然采用了具体术语,但它们仅用于并仅应当被解释为一般说明性含义,并且不用于限制的目的。在一些实例中,对本领域技术人员显而易见的是,除非另外明确指出,否则可单独使用与特定实施例相结合描述的特征、特性和/或元素,或可与其他实施例相结合描述的特征、特性和/或元件组合使用。因此,本领域技术人员将理解,在不脱离由所附的权利要求阐明的本公开的范围的情况下,可进行各种形式和细节上的改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1