芯片结构、芯片结构的制作方法、电子设备与流程

1.本技术涉及芯片封装技术领域,尤其涉及一种芯片结构、一种芯片结构的制作方法以及一种包括该芯片结构的电子设备。

背景技术:

2.随着电子技术的发展,集成电路板的组装密度越来越高,微电子器件中的焊点也越来越小,对可靠性要求日益提高。电子封装中广泛采用的晶圆级尺寸封装(wafer levelchip scale package,wlcsp)、倒装芯片尺寸封装(flip chip scale package,fccsp)等封装技术均通过焊点直接实现电子器件与基板或电路板之间的电气连接及机械连接。其中,倒装芯片封装技术是把裸芯片正面朝下通过锡膏将其焊球焊接在电路板上的焊盘上的技术,而随着芯片上集成的信号越来越多,如何提高芯片与电路板之间焊点的可靠性成为本领域技术人员的研究热点。

技术实现要素:

3.本技术提供了一种芯片结构、一种芯片结构的制作方法以及一种包括该芯片结构的电子设备,目的在于提高芯片与电路板之间焊点的可靠性。

4.为了实现上述目的,本技术提供了以下技术方案:

5.第一方面,本技术实施例提供了一种芯片结构,包括:

6.电路板,所述电路板上具有多个焊盘,所述多个焊盘包括多个第一焊盘和至少一个第二焊盘;

7.芯片,所述芯片与所述第一焊盘电连接,所述第二焊盘为冗余焊盘;

8.多个电连接结构,所述多个电连接结构包括多个第一电连接结构和至少一个第二电连接结构,所述第一电连接结构位于所述第一焊盘表面,电连接所述芯片与所述第一焊盘,所述第二电连接结构位于所述第二焊盘表面;

9.封装层,所述封装层填充所述电路板和所述芯片之间的空隙。

10.本技术实施例所提供的芯片结构,通过在所述电路板上增加所述第二焊盘,来增加所述电路板的焊盘密度,以减小所述电路板中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水,形成封装层时,增强所述电路板上相邻焊盘之间的毛细作用,提高所述芯片和所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

11.在一种实现方式中,沿所述电路板至所述芯片方向上,所述第二电连接结构的高度与所述第二焊盘到所述芯片之间的距离的比值的取值范围为0.5~1,包括端点值,以在给所述芯片和所述电路板之间的空隙进行胶水填充,形成封装层时,使得所述第二焊盘所在位置具有较强的毛细作用。

12.在又一种实现方式中,在所述电路板所在的平面内,所述多个焊盘中相邻焊盘之

间的空隙的尺寸不大于400微米,以在给所述芯片和所述电路板之间的空隙进行胶水填充,形成所述封装层时,使得各焊盘所在位置具有较强的毛细作用,提高所述芯片和所述电路板之间空隙的胶水填充效果。

13.在再一种实现方式中,所述多个焊盘在所述电路板上均匀分布,以使得各焊盘所在位置处的毛细作用相同或相近,从而在给所述芯片和所述电路板之间的空隙进行胶水填充时,使得各焊盘所在位置处被胶水润湿的速度相同或相近,进一步降低填胶空洞的出现。

14.第二方面,本技术实施例提供了一种芯片结构的制作方法,包括:

15.在电路板上具有焊盘的一侧表面放置钢网,其中,所述电路板上具有多个焊盘,所述多个焊盘包括多个第一焊盘和至少一个第二焊盘,所述钢网上具有多个开口,所述多个开口包括多个第一开口和至少一个第二开口,所述第一开口与所述第一焊盘一一对应,裸露所述第一焊盘,所述第二开口与所述第二焊盘一一对应,裸露所述第二焊盘;

16.在所述钢网的各开口内印刷锡膏,并取走所述钢网;

17.将芯片放置在所述锡膏远离所述电路板的一侧,所述芯片上具有多个焊球,所述芯片上的焊球与所述第一焊盘一一对应;

18.加热所述锡膏,形成多个电连接结构,所述多个电连接结构包括:多个第一电连接结构和至少一个第二电连接结构,所述第一电连接结构为位于所述第一焊盘表面的锡膏和所述芯片上的焊球加热熔化后形成的结构,所述第二电连接结构为位于所述第二焊盘表面的锡膏加热熔化后形成的结构;

19.在所述芯片和所述电路板之间的空隙点胶,在所述芯片和所述电路板之间形成封装层。

20.本技术实施例所提供的芯片结构的制作方法,通过在所述电路板上增加所述第二焊盘,来增加所述电路板的焊盘密度,以减小所述电路板中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水,形成封装层时,增强所述电路板上相邻焊盘之间的毛细作用,提高所述芯片和所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

21.在一种实现方式中,所述第一开口和所述第二开口的尺寸相同,从而使得沿所述电路板至所述芯片的方向上,位于所述第一焊盘表面的第一电连接结构的高度和位于所述第二焊盘表面的第二电连接结构的高度相同。

22.在另一种实现方式中,所述第二开口的尺寸大于所述第一开口的尺寸,从而使得加热所述锡膏后,沿所述电路板至所述芯片的方向上,位于所述第二焊盘表面的第二电连接结构的高度大于位于所述第一焊盘表面的第一电连接结构的高度,从而进一步减小所述第二电连接结构与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水时,增强位于所述第四区域的相邻焊盘之间的毛细作用,提高所述芯片与所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

23.在又一种实现方式中,所述第二开口的体积为所述第一开口的体积的1-3倍,包括端点值,从而使得位于所述第二开口内的锡膏体积为位于所述第一开口内的锡膏的体积的1-3倍,包括端点值,进而使得所述第二连接结构的高度不小于所述第一连接结构的高度,

且不超过所述第二焊盘与所述芯片之间的空隙的高度。

24.第三方面,本技术实施例提供了一种电子设备,包括:上述任一项所述的芯片结构,以提高所述芯片结构中芯片与电路板之间的焊点的可靠性。

附图说明

25.图1为芯片结构应用的电子设备的一种应用场景示意图;

26.图2为现有芯片结构的结构示意图;

27.图3-图5为现有芯片结构的制作过程中涉及的部分结构的示意图;

28.图6为现有芯片结构中芯片上焊球的布局示意图;

29.图7为与图6的芯片电连接的电路板上的焊盘的布局示意图;

30.图8为现有芯片结构的制作过程中,在芯片和电路板之间的空隙点胶时,胶水的流动方向示意图;

31.图9为现有芯片结构的制作过程中,在芯片和电路板之间的空隙点胶完成后,形成的填胶空洞示意图;

32.图10为本技术一个实施例所提供的芯片结构中,电路板上焊盘的布局示意图;

33.图11与图10所示的电路板焊接的芯片上的焊球布局示意图;

34.图12为本技术一个实施例所提供的芯片结构的结构示意图;

35.图13为本技术一个实施例所提供的芯片结构制作过程中,锡膏熔化前的结构示意图;

36.图14为本技术一个实施例所提供的芯片结构的制作方法的流程图;

37.图15-图22为本技术一个实施例所提供的芯片结构的制作方法中各方法步骤涉及的结构示意图;

38.图23为本技术一个实施例所提供的电子设备的结构示意图。

具体实施方式

39.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。以下实施例中所使用的术语只是为了描述特定实施例的目的,而并非旨在作为对本技术的限制。如在本技术的说明书和所附权利要求书中所使用的那样,单数表达形式“一个”、“一种”、“所述”、“上述”、“该”和“这一”旨在也包括例如“一个或多个”这种表达形式,除非其上下文中明确地有相反指示。还应当理解,在本技术实施例中,“一个或多个”是指一个、两个或两个以上;“和/或”,描述关联对象的关联关系,表示可以存在三种关系;例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a、b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。

40.在本说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本技术的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。

41.本技术实施例涉及的多个,是指大于或等于两个。需要说明的是,在本技术实施例的描述中,“第一”、“第二”等词汇,仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。

42.为了下述各实施例的描述清楚简洁,首先给出相关技术的简要介绍:

43.pcb(printed circuit board),中文名称为印制电路板,又称印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气相互连接的载体。

44.焊盘,表面贴装装配的基本构成单元,用来构成电路板的焊盘图案(land pattern)。

45.芯片,半导体元件产品的统称,在电子学中是一种将电路(主要包括半导体设备,也包括被动组件等)小型化的方式,并时常制造在半导体晶圆表面上。

46.倒装芯片(flip chip)是一种无引脚结构,一般含有电路单元,设计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖),在电气上和机械上连接于电路。

47.焊点,是指芯片上的焊球与位于电路板上的焊盘表面的锡膏熔化形成的电连接结构。

48.图1为芯片结构应用在电子设备中的一种场景示意图,在日常生活或工作中,用户经常使用电子设备进行娱乐、办公或学习等活动,但是,在实际使用过程中,有时会出现芯片结构短路,使得电子设备无法开机的现象。

49.如图2所示,图2示出了一种倒装芯片结构的结构示意图,现有技术中的倒装芯片封装通常是先将芯片02表面的焊球通过锡膏焊接到电路板01的焊盘上,然后利用底部填充(underfill)技术对芯片02和电路板01之间的空隙进行填充,以在芯片02和电路板之间的空隙形成填充胶04,从而实现芯片和电路板之间空隙的封装,并利用填充胶04提高芯片02和电路板01之间的结合力,同时提高芯片02通过锡膏与电路板01上的焊盘焊接形成的焊点的可靠性。

50.具体的,在利用底部填充技术对芯片和电路板之间的空隙进行填充时,是先将芯片02的焊球和电路板01上的焊盘通过锡膏焊接,如图3所示,形成焊点;然后在芯片02和电路板01之间的空隙的一侧点胶水05,如图4所示,利用毛细作用,使得胶水05由在芯片02和电路板01之间的空隙的边缘向在芯片02和电路板01之间的空隙的中心区域方向a流动,如图5所示,直至流动结束,完成芯片02和电路板01之间焊点的封装。其中,电路板与芯片之间的空隙中相邻焊点之间的空隙越小,毛细作用越强,该相邻焊点之间的空隙被胶水填充的越饱满,该焊点的可靠性越强。

51.如图6和图7所示,目前电路板01上的焊盘布局和其焊接的芯片02上的焊球布局相同,且所述电路板01上的焊盘与所述芯片02上的焊球一一对应,而芯片02的上焊球布局与芯片的实际应用场景需求有关,经常存在部分区域的焊球密度较大,部分区域的焊球密度较小的情况,从而使得电路板上的焊盘布局也存在部分区域的焊盘密度较大,部分区域的焊盘密度较小的现象。

52.而电路板上焊盘布局中焊盘密度大的地方,相邻焊盘之间的空隙较小,相应的,后续形成焊点后,相邻焊点之间的毛细作用较强,相邻焊点之间的空隙被胶水填充的较好,焊盘密度小的地方,相邻焊盘之间的空隙较大,相应的,后续形成的相邻焊点之间的毛细作用较弱,相邻焊点之间的空隙被胶水填充越慢,甚至无法润湿。

53.继续如图6所示,芯片上的焊球布局通常边缘密度较大,中心区域密度较小,从而使得在电路板和芯片之间填充胶水时,边缘区域的毛细作用较强,润湿的较快,而中心区域的毛细作用较弱,润湿的较慢,如图8所示,当电路板和芯片之间空隙的四周全部被胶水填满,而中心区域还未被胶水填满时,会使得电路板和芯片之间中心区域的空气无法排布,形成填胶空洞,如图9所示的区域06,影响该区域的焊点的可靠性。

54.而且,在对电路板和芯片组成的芯片结构进行整体环境测试(如双85的环境测试,即温度参数为85,湿度参数为85的环境中测试)时,填胶空洞所在的区域容易出现焊点枝晶,导致相邻焊点短路等情况发生,造成电路板和芯片组成的芯片结构无法正常工作。

55.有鉴于此,本技术实施例提供了一种芯片结构,如图10-图12所示,包括:

56.电路板10,如图10所示,所述电路板10上具有多个焊盘12,具体的,所述电路板10包括第一基板11以及位于所述第一基板11表面的多个焊盘12,如图12所示,所述多个焊盘12包括多个第一焊盘121和至少一个第二焊盘122;

57.芯片20,继续如图12所示,所述芯片20与所述第一焊盘121电连接,所述第二焊盘122为冗余焊盘;

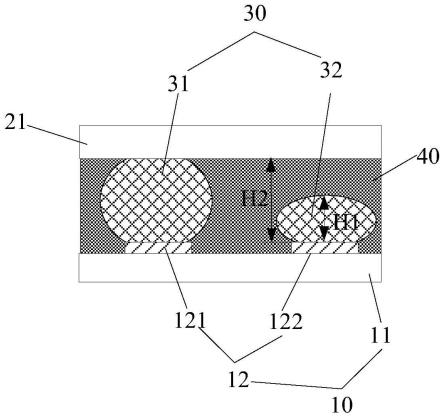

58.多个电连接结构30,所述多个电连接结构30包括多个第一电连接结构31和至少一个第二电连接结构32,所述第一电连接结构31位于所述第一焊盘121表面,电连接所述芯片20与所述第一焊盘121,所述第二电连接结构32位于所述第二焊盘122表面;

59.封装层40,所述封装层40填充所述电路板10和所述芯片20之间的空隙。

60.需要说明的是,所述第一电连接结构31为焊接所述芯片20与所述电路板10的焊点。

61.还需要说明的是,形成多个电连接结构之前,所述芯片20上具有多个焊球22,具体的,如图11和图13所示,所述芯片20包括第二基板21以及位于所述第二基板21表面的多个焊球22,所述第一焊盘121用于和所述芯片20上的焊球22电连接,所述第二焊盘122为冗余焊盘;具体制作时,继续如图13所示,先在所述电路板10上的焊盘12表面形成锡膏,具体为在所述第一焊盘121表面形成第一锡膏33,在第二焊盘122表面形成第二锡膏34;然后将所述芯片20放置在所述锡膏远离所述电路板10一侧表面,其中,所述芯片20上的焊球22位于所述第一锡膏33远离所述电路板10一侧;加热所述锡膏,使得所述锡膏与所述芯片20上的焊球22熔化,形成多个电连接结构30,如图12所示。即在本实施例中,图13为锡膏熔化前,所述芯片结构的结构示意图;图12为锡膏熔化后,所述芯片结构的结构示意图,具体为:锡膏熔化后,位于所述第一焊盘121表面的第一锡膏和所述焊球就会融合成一体结构,形成焊点31,位于所述第二焊盘122表面的第二锡膏变成回流后的锡膏。

62.本技术实施例所提供的芯片结构,通过在所述电路板上增加所述第二焊盘,来增加所述电路板的焊盘密度,以减小所述电路板中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水时,增强所述电路板上相邻焊盘之间的毛细作用,提高所述芯片和所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

63.需要说明的是,在本技术实施例中,所述芯片包括第一区域和第二区域,所述第一区域的焊球密度大于所述第二区域的焊球密度,相应的,所述电路板包括与所述第一区域

对应的第三区域以及与所述第二区域对应的第四区域,所述第三区域的第一焊盘密度大于所述第四区域的第一焊盘密度。

64.还需要说明的是,在本技术实施例中,所述第二焊盘位于所述第四区域,从而通过在所述第四区域增加所述第二焊盘,来增加所述第四区域的焊盘密度,以减小所述第四区域中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水,形成封装层时,增强位于所述第四区域的相邻焊盘之间的毛细作用,提高所述第四区域的胶水填充效果,增加所述电路板的第四区域和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

65.在上述任一实施例的基础上,在本技术的一个实施例中,继续如图12所示,沿所述电路板10至所述芯片20方向上,所述第二电连接结构32的高度h1与所述第二焊盘122到所述芯片20之间的距离h2的比值的取值范围为0.5~1,包括端点值,以在给所述芯片20和所述电路板10之间的空隙进行胶水填充,形成封装层时,使得所述第二焊盘122所在位置具有较强的毛细作用。

66.可选的,在本技术的一个实施例中,沿所述电路板10至所述芯片20的方向上,所述第二电连接结构完全填充所述第二焊盘与所述芯片之间的距离,进一步增强所述第二焊盘位置处的毛细作用,提高所述芯片20与所述电路板10之间的胶水填充效果,增加所述芯片20与所述电路板10之间的结合力,同时,降低填胶空洞出现的概率,解决枝晶问题。

67.在上述任一实施例的基础上,在本技术的一个实施例中,在所述电路板所在的平面内,所述多个焊盘中相邻焊盘之间的空隙的尺寸不大于400微米,以在给所述芯片和所述电路板之间的空隙进行胶水填充,形成所述封装层时,使得各焊盘所在位置具有较强的毛细作用,提高所述芯片和所述电路板之间空隙的胶水填充效果。

68.在上述任一实施例的基础上,在本技术的一个实施例中,所述多个焊盘在所述电路板上均匀分布,以使得各焊盘所在位置处的毛细作用相同或相近,从而在给所述芯片和所述电路板之间的空隙进行胶水填充时,使得各焊盘所在位置处被胶水润湿的速度相同或相近,进一步降低填胶空洞的出现。

69.由上可知,本技术实施例所提供的芯片结构,通过在所述电路板上增加所述第二焊盘,来增加所述电路板的焊盘密度,以减小所述电路板中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水,形成封装层时,增强所述电路板上相邻焊盘之间的毛细作用,提高所述芯片和所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

70.相应的,本技术实施例还提供了一种芯片结构的制作方法,如图14所示,该方法包括:

71.s1:如图15所示,在电路板10上具有焊盘12的一侧表面放置钢网50,所述电路板10上具有多个焊盘12,具体的,所述电路板10包括第一基板11以及位于所述第一基板11表面的多个焊盘12,所述多个焊盘12包括多个第一焊盘121和至少一个第二焊盘122,所述钢网50上具有多个开口,所述多个开口包括多个第一开口51和至少一个第二开口52,所述第一开口51与所述第一焊盘121一一对应,裸露所述第一焊盘121,所述第二开52口与所述第二

焊盘122一一对应,裸露所述第二焊盘122。

72.s2:如图16所示,在所述钢网50的各开口内印刷锡膏,具体为:在第一开口内印刷第一锡膏33,在第二开口内印刷第二锡膏34,并取走所述钢网50,如图17所示,所述第一锡膏33和所述第二锡膏34在同一步工艺中印刷完成;

73.s3:如图18所示,将芯片20放置在所述锡膏远离所述电路板10的一侧,所述芯片20上具有多个焊球22,具体的,所述芯片包括第二基板21以及位于所述第二基板表面的多个焊球22,所述芯片20上的焊球22与所述第一焊盘121一一对应,具体为:所述芯片20上的焊球22位于所述第一锡膏33远离所述电路板10一侧表面;

74.s4:如图19所示,加热所述锡膏,形成多个电连接结构30,所述多个电连接结构30包括:多个第一电连接结构31和至少一个第二电连接结构32,所述第一电连接结构31为位于所述第一焊盘121表面的第一锡膏和所述芯片20上的焊球22加热熔化后形成的焊点,焊接所述电路板10和所述芯片20,所述第二电连接结构32为位于所述第二焊盘122表面的第二锡膏加热熔化后形成的结构;

75.s5:如图20所示,在所述芯片20和所述电路板10之间的空隙点胶水60,在所述芯片20和所述电路板10之间形成封装层40,如图21所示。

76.本技术实施例所提供的芯片结构的制作方法,通过在所述电路板上增加所述第二焊盘,来增加所述电路板的焊盘密度,以减小所述电路板中相邻焊盘之间的间距,并在所述第二焊盘上设置第二电连接结构,以减小所述第二焊盘与所述芯片之间的空隙,进而在所述芯片和所述电路板之间的空隙点胶水,形成封装层时,增强所述电路板上相邻焊盘之间的毛细作用,提高所述芯片和所述电路板之间的胶水填充效果,增加所述电路板和所述芯片之间的结合力,同时,降低填胶空洞出现的概率,解决焊点枝晶的问题。

77.可选的,在上述实施例的基础上,在本技术的一个实施例中,如图15和图16所示,所述第一开口51和所述第二开口52的大小相同,从而使得沿所述电路板10至所述芯片20的方向上,位于所述第一焊盘121表面的第一锡膏33的高度和位于所述第二焊盘122表面的第二锡膏34的高度相同。

78.由于锡膏具有一定的回缩特性,因此,在本技术的另一个实施例中,如图22和图12所示,所述第二开口的尺寸大于所述第一开口的尺寸,从而使得熔化所述锡膏后,沿所述电路板10至所述芯片20的方向上,所述第二电连接结构32的高度h1与所述第二焊盘122到所述芯片20之间的距离h2的比值的取值范围为0.5~1,包括端点值,以在给所述芯片20和所述电路板10之间的空隙进行胶水填充,形成封装层40时,使得所述第二焊盘122所在位置具有较强的毛细作用,提高所述芯片20与所述电路板10之间的胶水填充效果,增加所述芯片20与所述电路板10之间的结合力,同时,降低填胶空洞出现的概率,解决枝晶问题。

79.具体的,在本技术的一个实施例中,所述第二开口的体积为所述第一开口的体积的1-3倍,包括端点值,从而使得位于所述第二开口内的第二锡膏体积为位于所述第一开口内的第一锡膏的体积的1-3倍,包括端点值,进而使得所述第二连接结构的高度不小于所述第二焊盘到所述芯片之间的距离的1/2,且不超过所述第二焊盘与所述芯片之间的空隙的高度。

80.可选的,在本技术的一个实施例中,所述第二开口的体积为所述第一开口的体积的3倍,从而使得位于所述第二开口内的第二锡膏体积为位于所述第一开口内的第一锡膏

的体积的3倍,进而使得沿所述电路板至所述芯片的方向上,所述第二电连接结构完全填充所述第二焊盘与所述芯片之间的距离,进一步增强所述第二焊盘位置处的毛细作用,提高所述芯片20与所述电路板10之间的胶水填充效果,增加所述芯片20与所述电路板10之间的结合力,同时,降低填胶空洞出现的概率,解决枝晶问题。

81.此外,本技术实施例还提供了一种电子设备,该电子设备包括上述任一实施例所提供的芯片结构,以提高所述芯片结构中芯片与电路板之间的焊点的可靠性。具体的,在一些实施例中,电子设备可以是手机、平板电脑、桌面型、膝上型、笔记本电脑、超级移动个人计算机(ultra-mobile personal computer,umpc)、手持计算机、上网本、个人数字助理(personal digital assistant,pda)、可穿戴电子设备、智能手表等设备。

82.可选的,在本技术的一个实施例中,如图23所示,电子设备可以包括处理器110,外部存储器接口120,内部存储器1201,通用串行总线(universal serial bus,usb)接口130,充电管理模块140,电源管理模块141,电池142,天线1,天线2,移动通信模块150,无线通信模块160,音频模块170,扬声器170a,受话器170b,麦克风170c,耳机接口170d,传感器模块180,按键190,马达191,指示器192,摄像头193,显示屏194,以及用户标识模块(subscriber identification module,sim)卡接口195等。其中传感器模块180可以包括压力传感器180a,陀螺仪传感器180b,气压传感器180c,磁传感器180d,加速度传感器180e,距离传感器180f,接近光传感器180g,指纹传感器180h,温度传感器180j,触摸传感器180k,环境光传感器180l,骨传导传感器180m等。

83.需要说明的是,在本技术实施例中,所述处理器等大尺寸芯片与电路板之间的空隙封装后更容易出现填充孔洞现象,因此,在本技术的一个可选实施例中,至少所述处理器与其焊接的电路板所组成的芯片结构采用本技术上述任一实施例所提供的芯片结构。但本技术对此并不做限定,在本技术的其他实施例中,所述电子设备中的任一芯片与其对应的电路板之间都可以采用上述任一实施例所提供的芯片结构,具体视情况而定。

84.可以理解的是,本实施例示意的结构并不构成对电子设备的具体限定。在另一些实施例中,电子设备可以包括比图示更多或更少的部件,或者组合某些部件,或者拆分某些部件,或者不同的部件布置。图示的部件可以以硬件,软件或软件和硬件的组合实现。

85.可选的,在本技术的一个实施例中,电子设备的无线通信功能可以通过天线1,天线2,移动通信模块150,无线通信模块160,调制解调处理器以及基带处理器等实现。

86.天线1和天线2用于发射和接收电磁波信号。电子设备中的每个天线可用于覆盖单个或多个通信频带。不同的天线还可以复用,以提高天线的利用率。例如:可以将天线1复用为无线局域网的分集天线。在另外一些实施例中,天线可以和调谐开关结合使用。

87.移动通信模块150可以提供应用在电子设备上的包括2g/3g/4g/5g等无线通信的解决方案。移动通信模块150可以包括至少一个滤波器,开关,功率放大器,低噪声放大器(low noise amplifier,lna)等。移动通信模块150可以由天线1接收电磁波,并对接收的电磁波进行滤波,放大等处理,传送至调制解调处理器进行解调。移动通信模块150还可以对经调制解调处理器调制后的信号放大,经天线1转为电磁波辐射出去。在一些实施例中,移动通信模块150的至少部分功能模块可以被设置于处理器110中。在一些实施例中,移动通信模块150的至少部分功能模块可以与处理器110的至少部分模块被设置在同一个器件中。

88.调制解调处理器可以包括调制器和解调器。其中,调制器用于将待发送的低频基

带信号调制成中高频信号。解调器用于将接收的电磁波信号解调为低频基带信号。随后解调器将解调得到的低频基带信号传送至基带处理器处理。低频基带信号经基带处理器处理后,被传递给应用处理器。应用处理器通过音频设备(不限于扬声器170a,受话器170b等)输出声音信号,或通过显示屏194显示图像或视频。在一些实施例中,调制解调处理器可以是独立的器件。在另一些实施例中,调制解调处理器可以独立于处理器110,与移动通信模块150或其他功能模块设置在同一个器件中。

89.无线通信模块160可以提供应用在电子设备上的包括无线局域网(wireless local area networks,wlan)(如无线保真(wireless fidelity,wi-fi)网络),蓝牙(bluetooth,bt),全球导航卫星系统(global navigation satellite system,gnss),调频(frequency modulation,fm),近距离无线通信技术(near field communication,nfc),红外技术(infrared,ir)等无线通信的解决方案。无线通信模块160可以是集成至少一个通信处理模块的一个或多个器件。无线通信模块160经由天线2接收电磁波,将电磁波信号调频以及滤波处理,将处理后的信号发送到处理器110。无线通信模块160还可以从处理器110接收待发送的信号,对其进行调频,放大,经天线2转为电磁波辐射出去。

90.在一些实施例中,电子设备的天线1和移动通信模块150耦合,天线2和无线通信模块160耦合,使得电子设备可以通过无线通信技术与网络以及其他设备通信。所述无线通信技术可以包括全球移动通讯系统(global system for mobile communications,gsm),通用分组无线服务(general packet radio service,gprs),码分多址接入(code division multiple access,cdma),宽带码分多址(wideband code division multiple access,wcdma),时分码分多址(time-division code division multiple access,td-scdma),长期演进(long term evolution,lte),bt,gnss,wlan,nfc,fm,和/或ir技术等。所述gnss可以包括全球卫星定位系统(global positioning system,gps),全球导航卫星系统(global navigation satellite system,glonass),北斗卫星导航系统(beidou navigation satellite system,bds),准天顶卫星系统(quasi-zenith satellite system,qzss)和/或星基增强系统(satellite based augmentation systems,sbas)。

91.通过以上的实施方式的描述,所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,仅以上述各功能模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能模块完成,即将装置的内部结构划分成不同的功能模块,以完成以上描述的全部或者部分功能。

92.在本实施例所提供的几个实施例中,应该理解到,所揭露的系统,装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述模块或单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

93.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

94.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何在本技术揭露的技术范围内的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1