一种肖特基接触的沟槽型功率二极管及其制备方法

1.本发明涉及半导体器件领域,尤其涉及一种肖特基接触的沟槽型功率二极管及其制备方法。

背景技术:

2.肖特基势垒二极管(schottky barrier diode,sbd)具有开启电压低、开关速度快等突出有点,是一种重要的功率半导体器件。目前,基于一些耐超高压材质(例如ga2o3)的肖特基势垒二极管器件的性能尚不足以充分发挥其材质的优势,尤其是器件的反向耐压距离其理论极值有较大差距,主要是由于肖特基结界面处的高表面电场导致器件的反向漏电过大造成的。

3.有文献报道了一种沟槽mos型垂直氧化镓肖特基势垒二极管,其工作原理是原理是在利用沟槽mos结构在反偏时的耗尽作用夹断沟槽间的肋条,从而限制反偏肖特基结的漏电,实现低漏电和高耐压。然而,该器件在正向偏置时,沟槽mos结构无法参与导电,必将导致牺牲器件的导通电阻和芯片面积利用率。

4.[1]1230vβ-ga2o

3 trench schottky barrier diodes with an ultra-low leakage current of《1μa/cm

2 wenshen li,zongyang hu,kazuki nomoto,zexuan zhang,jui-yuan hsu,quang tu thieu,kohei sasaki,akito kuramata,debdeep jena,and huili grace xing;

[0005]

[2]first demonstration of ga2o3 trench mos-type schottky barrier diodes kohei sasaki,daiki wakimoto,quang tu thieu,yuki koishikawa,akito kuramata,masataka higashiwaki,member,ieee,and shigenobu yamakoshi;

[0006]

[3]cn1555581a,美商克立股份有限公司;

[0007]

[4]cn113130667a,重庆理工大学。

技术实现要素:

[0008]

本发明目的在于提供一种肖特基接触的沟槽型功率二极管及其制备方法,以解决上述现有技术存在的问题。

[0009]

本发明所述一种肖特基接触的沟槽型功率二极管,包括依次层叠接触的n型漂移层、n型衬底和下电极,所述的n型衬底与下电极为欧姆接触;n型漂移层远离n型衬底的一侧延伸出若干肋条;

[0010]

肋条之间铺设有高势垒层,还设有低势垒层覆盖高势垒层端部和肋条端面;

[0011]

设置上电极填充覆盖低势垒层和高势垒层表面;

[0012]

所述的低势垒层和高势垒层均与n型漂移层为肖特基接触,与上电极为欧姆接触;

[0013]

所述的低势垒层功函数低于5ev,且与n型漂移层形成不低于1.5ev的肖特基势垒;

[0014]

所述的高势垒层功函数不低于5ev,且与n型漂移层形成不低于1.5ev的肖特基势垒。

[0015]

高势垒层和n型漂移层之间还设置绝缘介质层,所述的绝缘介质层至少覆盖肋条下端角部位置。

[0016]

所述高势垒层的材质为金属或合金或金属氧化物。

[0017]

所述低势垒层的材质为金属或合金。

[0018]

所述高势垒层的厚度为10nm至20nm,和/或所述低势垒层的厚度为20nm至100nm。

[0019]

所述的n型衬底为n型氧化镓衬底,和/或所述的n型漂移层为n型氧化镓漂移层。

[0020]

所述肋条的高度为1μm至3μm。

[0021]

所述n型漂移层为单晶结构,掺杂浓度为2

×

10

16

cm-3

至2.8

×

10

18

cm-3

,厚度为5μm至10μm。

[0022]

本发明所述一种肖特基接触的沟槽型功率二极管制备方法,包括以下步骤:

[0023]

在n型衬底上外延生长n型漂移层;

[0024]

在n型衬底下沉积下电极形成欧姆接触;

[0025]

对n型漂移层表面进行选择性刻蚀,得到若干垂直的肋条;

[0026]

在肋条之间的沟槽中沉积高势垒层,且高势垒层与n型漂移层形成肖特基接触;

[0027]

沉积低势垒层用于封闭肋条端面和高势垒层端部,且低势垒层与n型漂移层形成肖特基接触;

[0028]

沉积上电极填充覆盖低势垒层和高势垒层表面,低势垒层和高势垒层均与上电极形成欧姆接触。

[0029]

沉积高势垒层之前,先在沟槽底部沉积绝缘介质层,且绝缘介质层至少覆盖沟肋条下端角部位置。

[0030]

本发明所述一种肖特基接触的沟槽型功率二极管及其制备方法,其优点在于,设置可以与n型漂移层材质形成高势垒肖特基结的高势垒层,高势垒肖特基结在反偏的时候具有相对较小的泄漏电流,其耗尽区的展宽可以夹断沟槽间的肋条,有效阻断低势垒肖特基结的漏电,实现良好的反向耐压特性。当器件正向开启时,位于肋条顶部的低势垒肖特基接触优先开启,确保器件具有低开启电压,随着正向偏压的增加,沟槽中的高势垒肖特基接触开启,确保器件具有低导通电阻。有效解决了原有mos-trench型肖特基势垒二极管正向开启时沟槽mos结构无法参与导电的弊端。

附图说明

[0031]

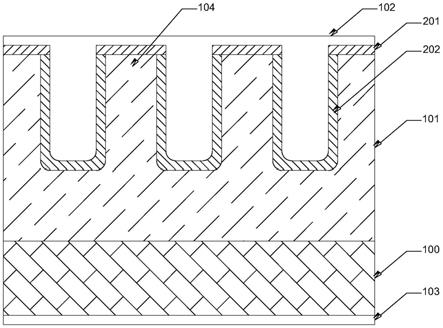

图1是本发明所述沟槽型功率二极管实施例一的结构示意图。

[0032]

图2是对比例一的正向电流密度仿真图。

[0033]

图3是对比例二的正向电流密度仿真图。

[0034]

图4是实施例一的正向电流密度仿真图。

[0035]

图5是两个比例和实施例一的反向电流特性曲线图。

[0036]

图6是对比例一和实施例一的反向电流特性曲线图。

[0037]

图7是对比例一的反向电流密度仿真图。

[0038]

图8是实施例一的反向电流密度仿真图。

[0039]

图9是本发明所述沟槽型功率二极管实施例二的结构示意图。

[0040]

图10是本发明所述沟槽型功率二极管实施例三的结构示意图。

[0041]

附图标记:

[0042]

100-n型衬底、101-n型漂移层、102-上电极、103-下电极、104-肋条;

[0043]

201-低势垒层、202-高势垒层、203-绝缘介质层;

[0044]

301-mos绝缘层。

具体实施方式

[0045]

实施例一

[0046]

如图1所示,本发明所述一种肖特基接触的沟槽型功率二极管包括从上至下依次层叠设置的n型漂移层101、n型衬底100和下电极103。n型漂移层101上端面向上延伸出若干肋条104,肋条104之间形成沟槽。沟槽内铺设有高势垒层202,高势垒层202与n型漂移层101为肖特基接触。在肋条104上再铺设有低势垒层201用于覆盖肋条104上端面和高势垒层202的端部,低势垒层201与n型漂移层101也为肖特基接触。设置上电极102填充覆盖高势垒层202和低势垒层201的表面。

[0047]

在本实施例中,n型漂移层101为氧化镓材质,n型衬底100也为氧化镓材质,但本发明结构还可以用于其他半导体材质的肖特基二极管中。

[0048]

所述高势垒层202的材质为功函数不低于5ev的金属或合金或金属氧化物。目的在于使高势垒层202与n型漂移层101的组成物质形成相对高势垒的肖特基结,所述肖特基结具有不低于1.5ev的肖特基势垒。功函数的具体选择可以根据n型漂移层101材质变化和器件实际需求做合理调整。高势垒层202可以选择的材质包括但不限于:au。

[0049]

所述低势垒层201的材质为功函数低于5ev的金属或合金。目的在于使低势垒层201与n型漂移层101的组成物质形成相对低势垒的肖特基结,所述肖特基结具有不低于1.5ev的肖特基势垒。同理,功函数的具体选择本领域技术人员可以根据本发明构思的指引进行合理选择替换。低势垒层201可以选择的材质包括但不限于:ni、ti、ni/au。

[0050]

关于功函数,可以把5ev作为高功函数和低功函数的界限。同时要加上限定,所指的高功函数金属或金属氧化物必须和半导体形成1.5ev以上的肖特基势垒。因为有一些功函数也大于5ev的金属在和半导体接触时由于费米钉扎效应,最终形成的肖特基势垒还是比较低的,因此本发明特指的是不会发生费米钉扎效应的高功函数金属或金属氧化物。

[0051]

所述高势垒层202的厚度为10nm至20nm,所述低势垒层201的厚度为20nm至100nm。所述肋条104的高度为1μm至3μm。所述n型漂移层101为单晶结构,掺杂浓度为2

×

10

16

cm-3

至2.8

×

10

18

cm-3

,厚度为5μm至10μm。尺寸和掺杂浓度的具体选择,可以根据器件应用场合的不同做适应性调整。

[0052]

制备本实施例所述沟槽型功率二极管的方法步骤如下:

[0053]

在非故意掺杂的n型衬底100上外延生长n型漂移层101;

[0054]

通过物理沉积或化学沉积方法在所述n型衬底100背面沉积下电极103形成欧姆接触;

[0055]

对n型漂移层101进行选择性刻蚀,形成沟道结构,得到若干垂直的肋条104;选择性刻蚀可以通过淹没等方式实现;

[0056]

通过物理沉积或化学沉积方法在沟道中沉积高势垒层202,且高势垒层202与n型漂移层101形成肖特基接触;

[0057]

通过物理或化学沉积方法沉积低势垒层201用于封闭肋条104端面和高势垒层202端部,且低势垒层201与n型漂移层101形成肖特基接触;

[0058]

最后,沉积上电极102填充覆盖低势垒层201和高势垒层202表面,低势垒层201和高势垒层202均与上电极102形成欧姆接触。

[0059]

本实施例中,以au作为高势垒层202、以ni作为低势垒层201。正向电流仿真如图4所示,反向电流仿真如图8所示。

[0060]

对比例一

[0061]

本对比例与实施例一区别主要在于,将实施例一的高势垒层202恢复为现有技术的mos结构,即肋条104外侧是用mos绝缘层进行覆盖。在本对比例中,mos绝缘层的材质为氧化硅。正向电流仿真如图2所示,反向电流仿真如图7所示。

[0062]

对比例二

[0063]

本对比例与实施例一区别主要在于,将实施例一的高势垒层202变为纯低势垒层201的结构,即肋条104外侧是也是用低功函数金属进行覆盖,如同为ni。正向电流仿真如图3所示。反向电流密度不对称,性能远不如实施例一和对比例一,因此不另外做反向电流特性做对比展示。

[0064]

另外再将本实施例和两个对比例的电流特性进行对比,如图5所示,可见纯低功函数金属的结构容易被击穿。而本实施例和对比的mos结构反向击穿相对较难,因此另外做更细化的坐标系进行单独对比,如图6所示。从图6中可见两者都有非常小的反向漏电流,其中有高功函数的器件漏电甚至更小。

[0065]

通过图2至图4的对比可见,在器件的电流密度分布仿真图中,本实施例的电流密度明显小于两个对比例的电流密度,再次印证了本实施例具有更小的反向漏电流,即更优的反向漏电特性。

[0066]

通过图7、图8可以明显看出,有高势垒层202的和具有mos结构的器件,反向偏压下都有耗尽作用,导电沟道都在肋条的中间,比较窄。两种结构的效果类似,但有本实施例的耗尽范围更大,在肋条下方直角位置也有明显的耗尽,而mos结构的耗尽集中在上电极附近导致反向电学特性不如本实施例理想。

[0067]

实施例二

[0068]

如图9所示,相对于实施例一,结构区别主要在于沟槽底部与肋条104转角处设置绝缘介质层203用于缓解电场集中效应:电场在沟槽底部与肋条104的转角处具有最大值,通过引入绝缘介质层,优化了电场的分布,降低了转角处的电场值,从而提高器件的击穿特性。所述的绝缘介质层203位于高势垒层202与n型漂移层101之间,断开该处的电性接触。

[0069]

制备方法也在实施例一的基础上进行调整:在沉积高势垒层202之前,先在沟槽底部沉积绝缘介质层203,且令绝缘介质层203覆盖沟肋条104下端角部位置即可实现。

[0070]

实施例三

[0071]

如图10所示,相对应实施例二,结构区别主要在于绝缘介质层203除了角部位置之外还全部覆盖了沟槽底部。完全断开沟槽下部位置的高势垒层202与n型漂移层101的电性接触。

[0072]

制备方法相对于实施例二,全部在于沉积绝缘介质层203的时候全部覆盖沟槽底部和角部位置即可实现。

[0073]

实施例三与实施例二相比,牺牲了部分导通面积,但制备工艺中少了一步刻蚀,降低了成本,并且两种器件结构中的绝缘介质层都起到了缓解电场集中效应,提高器件击穿特性的效果,其他电学特性也没有明显差异。在实际制备过程中,可根据需要、成本和其他实际情况进行选择。

[0074]

对于本领域的技术人员来说,可根据以上描述的技术方案以及构思,做出其它各种相应的改变以及形变,而所有的这些改变以及形变都应该属于本发明权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1