一种超结功率半导体器件及其制造方法与流程

1.本发明涉及一种功率半导体结构,具体涉及一种超结功率半导体器件及其制造方法。

背景技术:

2.超结金属氧化物半导体场效应晶体管(简称sj mosfet)由n柱与p柱互相间隔设置形成,通常n柱与p柱越窄,n柱与p柱的掺杂浓度就能越大,这样,sj mosfet的特征导通电阻就能越小,但是随着n柱掺杂浓度的增加,sj mosfet的终端的设计就会越来越困难,如果还使用单纯的n柱与p柱互相间隔排列式的终端,sj mosfet的终端击穿电压就会远低于元胞击穿电压。

3.为了获得更小的特征导通电阻,需要设计一种击穿电压较高的sj mosfet终端结构。

技术实现要素:

4.本发明的目的在于针对现有技术的不足,提供了一种超结功率半导体器件及其制造方法。本发明的功率器件包括有源区和包围有源区的第一终端保护区、第二终端保护区和第三终端保护区,第一终端保护区、第二终端保护区和第三终端保护区内的第一阱区、第二阱区与第三阱区能够有效降低器件击穿时的峰值电场,提高终端保护区的击穿电压,能够适用于高掺杂浓度的n型柱与p型柱组成的超结结构,并且在p型柱的宽度出现波动的情况下,器件的击穿点不会出现在终端保护区内,提高了器件的可靠性,能够解决现有技术中存在的sj mosfet终端击穿电压低的问题。

5.为实现以上技术目的,本发明实施例采用的技术方案是:第一方面,本发明实施例提供了一种超结功率半导体器件,其表面设有源极金属与栅极金属,在角落区域内包括有源区和包围所述有源区的第一终端保护区、第二终端保护区和第三终端保护区,所述有源区包括第一导电类型衬底,在所述第一导电类型衬底上方设有第一导电类型外延层,在所述第一导电类型外延层的顶部间隔交替设置有条形的第一导电类型柱与第二导电类型柱,在所述第一导电类型柱的顶部设有第二导电类型体区,在所述第二导电类型体区的表面设有第一导电类型源区,在所述第一导电类型柱的顶部设有沟槽,所述沟槽穿透第一导电类型源区与第二导电类型体区,所述沟槽内设置导电多晶硅,所述导电多晶硅通过栅氧层与第一导电类型源区、第二导电类型体区、第一导电类型柱绝缘,在所述第一导电类型柱与第二导电类型柱的上方设有绝缘介质层,在所述绝缘介质层的上方设有源极金属,在所述绝缘介质层内设置通孔,所述源极金属通过所述通孔与第一导电类型源区、第二导电类型体区、第二导电类型柱欧姆接触;所述有源区内的第二导电类型柱延伸的方向为y方向,与所述第二导电类型柱延伸方向垂直的方向为x方向,所述第一终端保护区内的第一导电类型外延层的顶部设有从有源区内延伸出的第一导电类型柱与第二导电类型柱,在所述第一导电类型外延层的表

面,设有至少一条第二导电类型的第一阱区,所述第一阱区之间互相平行分布且沿着x轴方向延伸;所述第二终端保护区内的第一导电类型外延层的顶部间隔交替设置有条形的第一导电类型柱与条形的第二导电类型柱,所述第一导电类型柱与第二导电类型柱沿着y轴方向延伸,在所述第一导电类型柱和/或第二导电类型柱内设有若干第二导电类型的第二阱区,所述第二阱区之间互相平行分布,且沿着y轴方向延伸;所述第三终端保护区内的第一导电类型外延层的顶部设有从第二终端保护区内延伸出的第一导电类型柱与第二导电类型柱,在所述第三终端保护区内,所述第一终端保护区内的第一阱区在x方向上的延长部分与所述第二终端保护区内的第二阱区在y方向的延长部分相交并重叠,在所述相交重叠的位置设置第二导电类型的第三阱区,所述第三阱区位于所述第一导电类型外延层的顶部。

6.进一步地,所述第一阱区的宽度为0.5-20 μm。

7.进一步地,所述第二阱区的宽度为0.1-5 μm。

8.进一步地,所述第一终端保护区位于所述有源区的y方向上,所述第二终端保护区位于所述有源区的x方向上,所述第一终端保护区和第二终端保护区分别与所述有源区邻接;所述第一终端保护区位于所述第三终端保护区的x方向上,所述第二终端保护区位于所述第三终端保护区的y方向上,所述第三终端保护区与所述第一终端保护区、第二终端保护区邻接。

9.进一步地,所述第一阱区设置在所述第一导电类型柱和/或第二导电类型柱内。

10.进一步地,所述第三阱区设置在所述第一导电类型柱和/或第二导电类型柱的顶部。

11.进一步地,所述功率器件为n型功率器件或p型功率器件,当所述功率器件为n型功率器件时,第一导电类型为n型,第二导电类型为p型;当所述功率器件为p型功率器件时,第一导电类型为p型,第二导电类型为n型。

12.第二方面,本发明实施例提供了一种超结功率半导体器件的制造方法,包括以下步骤:步骤s1、提供第一导电类型衬底,在所述第一导电类型衬底上生长第一导电类型外延层,然后使用第一块光刻板选择性注入第二导电类型杂质,退火后形成第二导电类型体区、第二阱区、第一阱区与第三阱区;步骤s2、使用第二块光刻板选择性刻蚀出深沟槽;步骤s3、淀积第二导电类型单晶硅,所述第二导电类型单晶硅填充满步骤s2形成的深沟槽,形成第二导电类型柱;步骤s4、使用第三块光刻板选择性刻蚀出栅极沟槽后,形成栅氧层、导电多晶硅,然后使用第四块光刻板选择性注入第一导电类型杂质,激活后形成第一导电类型源区;步骤s5、淀积绝缘介质,形成绝缘介质层;步骤s6、使用第五块光刻板选择性刻蚀出通孔,然后淀积金属,使用第六块光刻板选择性刻蚀金属,形成源极金属和栅极金属。

13.第三方面,本发明实施例提供了另一种超结功率半导体器件的制造方法,包括以下步骤:

步骤s1、提供第一导电类型衬底,在所述第一导电类型衬底上生长第一导电类型外延层,使用第一块光刻板选择性刻蚀出深沟槽,然后淀积第二导电类型单晶硅,形成第二导电类型柱;步骤s2、使用第二块光刻板选择性刻蚀出栅极沟槽后,形成栅氧层、导电多晶硅;步骤s3、使用第三块光刻板选择性注入第二导电类型杂质,退火后形成第二导电类型体区、第二阱区、第一阱区与第三阱区;步骤s4、使用第四块光刻板选择性注入第一导电类型杂质,激活后形成第一导电类型源区;步骤s5、淀积绝缘介质,形成绝缘介质层;步骤s6、使用第五块光刻板选择性刻蚀出通孔,然后淀积金属,使用第六块光刻板选择性刻蚀金属,形成源极金属和栅极金属。

14.与现有技术相比,本发明具有以下优点:1、本发明的超结功率半导体器件包括有源区和包围有源区的第一终端保护区、第二终端保护区和第三终端保护区,第一终端保护区、第二终端保护区和第三终端保护区内的第一阱区、第二阱区与第三阱区能够有效降低器件击穿时的峰值电场,提高终端保护区的击穿电压,能够适用于高掺杂浓度的n型柱与p型柱组成的超结结构,并且在p型柱的宽度出现波动的情况下,器件的击穿点不会出现在终端保护区内,提高了器件的可靠性。

15.2、本发明与现有工艺兼容,并且可以应用于超低压的超结半导体器件。

附图说明

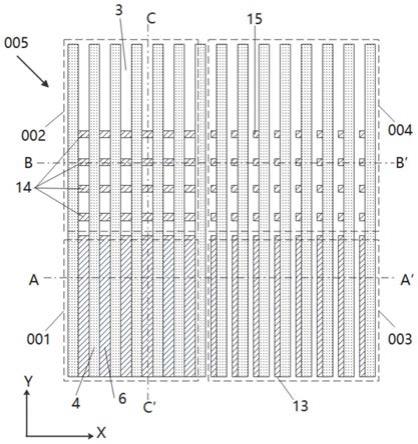

16.图1是本发明实施例提供的超结功率半导体器件的俯视结构示意图。

17.图2是本发明实施例1的功率半导体器件在图1中的角落区域005的俯视结构示意图。

18.图3是本发明实施例2的功率半导体器件在图1中的角落区域005的俯视结构示意图。

19.图4是本发明实施例3的功率半导体器件在图1中的角落区域005的俯视结构示意图。

20.图5是本发明实施例4的功率半导体器件在图1中的角落区域005的俯视结构示意图。

21.图6是本发明设置第三阱区的方法的示意图。

22.图7是沿着图2中的虚线aa’截得的剖面结构示意图。

23.图8是沿着图2中的虚线bb’截得的剖面结构示意图。

24.图9是沿着图2、3、4、5中的虚线cc’截得的剖面结构示意图。

25.图10是沿着图3中的虚线aa’截得的剖面结构示意图。

26.图11是沿着图3中的虚线bb’截得的剖面结构示意图。

27.图12是沿着图4中的虚线aa’截得的剖面结构示意图。

28.图13是沿着图4中的虚线bb’截得的剖面结构示意图。

29.图14是沿着图5中的虚线aa’截得的剖面结构示意图。

30.图15是沿着图5中的虚线bb’截得的剖面结构示意图。

31.图16是形成实施例1功率半导体器件的p型体区、第二阱区的剖面结构示意图。

32.图17是实施例1的功率半导体器件刻蚀深沟槽的剖面结构示意图。

33.图18是实施例1的功率半导体器件形成p型柱的剖面结构示意图。

34.图19是实施例1的功率半导体器件形成栅氧层、导电多晶硅与n型源区的剖面结构示意图。

35.图20是实施例1的功率半导体器件形成绝缘介质层的剖面结构示意图。

36.图21是实施例2的功率半导体器件形成p型柱的剖面结构示意图。

37.图22是实施例2的功率半导体器件形成栅氧层、导电多晶硅的剖面结构示意图。

38.图23是实施例2的功率半导体器件形成p型体区、第二阱区的剖面结构示意图。

39.图24是实施例3的功率半导体器件形成p型体区、第二阱区的剖面结构示意图。

40.图25是实施例3的功率半导体器件刻蚀深沟槽的剖面结构示意图。

41.图26是实施例3的功率半导体器件形成p型柱的剖面结构示意图。

42.附图标记说明:001-有源区;002-第一终端保护区;003-第二终端保护区;004-第三终端保护区;005-角落区域;1-第一导电类型衬底;2-第一导电类型外延层;3-第一导电类型柱;4-第二导电类型柱;5-沟槽;6-第二导电类型体区;7-第一导电类型源区;8-导电多晶硅;9-栅氧层;10-绝缘介质层;11-源极金属;12-通孔;13-第二阱区;14-第一阱区;15-第三阱区;16-栅极金属;17-第一阱区在x方向上的延长部分;18-第二阱区13在y方向的延长部分。

具体实施方式

43.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。其中相同的零部件用相同的附图标记表示。需要说明的是,下面描述中使用的词语“上”和“下”指的是附图中的方向。使用的词语“内”和“外”分别指的是朝向或远离特定部件几何中心的方向。

44.本发明包括以下两种实施例,以n型功率半导体器件为例进行说明。

45.实施例1如图1所示,为本发明实施例提供的超结功率半导体器件的俯视结构示意图,其表面设有源极金属11与栅极金属16,在功率半导体器件的角落区域005内,如图2所示,包括有源区001和包围所述有源区001的第一终端保护区002、第二终端保护区003和第三终端保护区004,如图7所示为沿着图2中的虚线aa’截得的剖面结构示意图,所述有源区001包括n型衬底1,在所述n型衬底1上方设有n型外延层2,在所述n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,在所述n型柱3的顶部设有p型体区6,在所述p型体区6的表面设有n型源区7,在所述n型柱3的顶部设有沟槽5,所述沟槽5穿透n型源区7与p型体区6,所述沟槽5内设置导电多晶硅8,所述导电多晶硅8通过栅氧层9与n型源区7、p型体区6、n型柱3绝缘,在所述n型柱3与p型柱4的上方设有绝缘介质层10,在所述绝缘介质层10的上方设有源极金属11,在所述绝缘介质层10内设置通孔12,所述源极金属11通过所述通孔12与n型源区7、p型体区6、p型柱4欧姆接触;如图2所示,所述有源区001内的p型柱4延伸的方向为y方向,与所述p型柱4延伸方向垂直的方向为x方向,所述第一终端保护区002位于所述有源区001的y方向上,所述第二

终端保护区003位于所述有源区001的x方向上,所述有源区001与所述第一终端保护区002、第二终端保护区003邻接;所述第一终端保护区002位于所述第三终端保护区004的x方向上,所述第二终端保护区003位于所述第三终端保护区004的y方向上,所述第三终端保护区004与所述第一终端保护区002、第二终端保护区003邻接;如图2所示,所述第一终端保护区002内的n型外延层2的顶部设有从有源区001内延伸出的n型柱3与p型柱4,如图9所示为沿着图2中的虚线cc’截得的剖面结构示意图,在所述n型外延层2的表面,设有至少一条p型的第一阱区14,所述第一阱区14之间互相平行分布且沿着x轴方向延伸,所述第一阱区14只设置于n型柱3内;如图2所示,所述第二终端保护区003内的n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,所述n型柱3与p型柱4沿着y轴方向延伸,如图7所示为沿着图2中的虚线aa’截得的剖面结构示意图,在所述p型柱4的顶部靠近有源区001的一侧设有p型的第二阱区13,所述第二阱区13之间互相平行分布,且沿着y轴方向延伸,所述第二阱区13只设置于n型柱3内;如图2所示,所述第三终端保护区004内的n型外延层2的顶部设有从第二终端保护区003内延伸出的n型柱3与p型柱4,如图6所示,为设置第三阱区的方法的示意图,在所述第三终端保护区004内,所述第一终端保护区002内的第一阱区14在x方向上的延长部分17与所述第二终端保护区003内的第二阱区13在y方向的延长部分18相交并重叠,在所述相交重叠的位置设置p型的第三阱区15,如图8所示为沿着图2中的虚线bb’截得的剖面结构示意图,所述第三阱区15位于所述n型柱3的顶部。

46.所述第一阱区14的宽度为0.5 μm。

47.所述第二阱区13的宽度为0.1μm。

48.一种超结功率半导体器件的制造方法,包括以下步骤:步骤s1、如图16所示,提供n型衬底1,在所述n型衬底1上生长n型外延层2,然后使用第一块光刻板选择性注入p型杂质,退火后形成p型体区6和第二阱区13,并采用相同的方法形成第一阱区14与第三阱区15,如图8所示;步骤s2、如图17所示,使用第二块光刻板选择性刻蚀出深沟槽;步骤s3、如图18所示,淀积p型单晶硅,所述p型单晶硅填充满步骤s2形成的深沟槽,形成p型柱4;步骤s4、如图19所示,使用第三块光刻板选择性刻蚀出栅极沟槽5后,形成栅氧层9、导电多晶硅8,然后使用第四块光刻板选择性注入n型杂质,激活后形成n型源区7;步骤s5、如图20所示,淀积绝缘介质,形成绝缘介质层10;步骤s6、如图7所示,使用第五块光刻板选择性刻蚀出通孔12,然后淀积金属,使用第六块光刻板选择性刻蚀金属,形成源极金属11和栅极金属16。

49.实施例2如图1所示,为本发明实施例提供的超结功率半导体器件的俯视结构示意图,其表面设有源极金属11与栅极金属16,在功率半导体器件的角落区域005内,如图3所示,包括有源区001和包围所述有源区001的第一终端保护区002、第二终端保护区003和第三终端保护区004,如图10所示为沿着图2中的虚线aa’截得的剖面结构示意图,所述有源区001包括n型衬底1,在所述n型衬底1上方设有n型外延层2,在所述n型外延层2的顶部间隔设置条形的n

型柱3与条形的p型柱4,在所述n型柱3与p型柱4的顶部设有p型体区6,在所述p型体区6的表面设有n型源区7,在所述n型柱3的顶部设有沟槽5,所述沟槽5穿透n型源区7与p型体区6,所述沟槽5内设置导电多晶硅8,所述导电多晶硅8通过栅氧层9与n型源区7、p型体区6、n型柱3绝缘,在所述n型柱3与p型柱4的上方设有绝缘介质层10,在所述绝缘介质层10的上方设有源极金属11,在所述绝缘介质层10内设置通孔12,所述源极金属11通过所述通孔12与n型源区7、p型体区6欧姆接触;如图3所示,所述有源区001内的p型柱4延伸的方向为y方向,与所述p型柱4延伸方向垂直的方向为x方向,所述第一终端保护区002位于所述有源区001的y方向上,所述第二终端保护区003位于所述有源区001的x方向上,所述有源区001与所述第一终端保护区002、第二终端保护区003邻接;所述第一终端保护区002位于所述第三终端保护区004的x方向上,所述第二终端保护区003位于所述第三终端保护区004的y方向上,所述第三终端保护区004与所述第一终端保护区002、第二终端保护区003邻接;如图3所示,所述第一终端保护区002内的n型外延层2的顶部设有从有源区001内延伸出的n型柱3与p型柱4,如图9所示为沿着图3中的虚线cc’截得的剖面结构示意图,在所述n型外延层2的表面,设有至少一条p型的第一阱区14,所述第一阱区14之间互相平行分布且沿着x轴方向延伸,所述第一阱区14设置于n型柱3与p型柱4内;如图3所示,所述第二终端保护区003内的n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,所述n型柱3与p型柱4沿着y轴方向延伸,如图10所示为沿着图2中的虚线aa’截得的剖面结构示意图,在所述p型柱4的顶部靠近有源区001的一侧设有p型的第二阱区13,所述第二阱区13之间互相平行分布,且沿着y轴方向延伸,所述第二阱区13设置于n型柱3与p型柱4内;如图3所示,所述第三终端保护区004内的n型外延层2的顶部设有从第二终端保护区003内延伸出的n型柱3与p型柱4,在所述第三终端保护区004内,如图6所示,所述第一终端保护区002内的第一阱区14在x方向上的延长部分17与所述第二终端保护区003内的第二阱区13在y方向的延长部分18相交并重叠,在所述相交重叠的位置设置p型的第三阱区15,如图11所示为沿着图3中的虚线bb’截得的剖面结构示意图,所述第三阱区15位于所述n型柱3与p型柱4的顶部。

50.所述第一阱区14的宽度为5 μm。

51.所述第二阱区13的宽度为1 μm。

52.一种超结功率半导体器件的制造方法,包括以下步骤:步骤s1、如图21所示,提供n型衬底1,在所述n型衬底1上生长n型外延层2,使用第一块光刻板选择性刻蚀出深沟槽,然后淀积p型单晶硅,形成p型柱4;步骤s2、如图22所示,使用第二块光刻板选择性刻蚀出栅极沟槽5后,形成栅氧层9、导电多晶硅8;步骤s3、如图23所示,使用第三块光刻板选择性注入p型杂质,退火后形成p型体区6、第二阱区13,并采用相同的方法形成第一阱区14与第三阱区15,如图11所示;步骤s4、使用第四块光刻板选择性注入n型杂质,激活后形成n型源区7;步骤s5、淀积绝缘介质,形成绝缘介质层10;步骤s6、使用第五块光刻板选择性刻蚀出通孔12,然后淀积金属,使用第六块光刻

板选择性刻蚀金属,形成源极金属11和栅极金属16。

53.实施例3如图1所示,为本发明实施例提供的超结功率半导体器件的俯视结构示意图,其表面设有源极金属11与栅极金属16,在功率半导体器件的角落区域005内,如图4所示,包括有源区001和包围所述有源区001的第一终端保护区002、第二终端保护区003和第三终端保护区004,如图12所示为沿着图4中的虚线aa’截得的剖面结构示意图,所述有源区001包括n型衬底1,在所述n型衬底1上方设有n型外延层2,在所述n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,在所述n型柱3的顶部设有p型体区6,在所述p型体区6的表面设有n型源区7,在所述n型柱3的顶部设有沟槽5,所述沟槽5穿透n型源区7与p型体区6,所述沟槽5内设置导电多晶硅8,所述导电多晶硅8通过栅氧层9与n型源区7、p型体区6、n型柱3绝缘,在所述n型柱3与p型柱4的上方设有绝缘介质层10,在所述绝缘介质层10的上方设有源极金属11,在所述绝缘介质层10内设置通孔12,所述源极金属11通过所述通孔12与n型源区7、p型体区6、p型柱4欧姆接触;如图4所示,所述有源区001内的p型柱4延伸的方向为y方向,与所述p型柱4延伸方向垂直的方向为x方向,所述第一终端保护区002位于所述有源区001的y方向上,所述第二终端保护区003位于所述有源区001的x方向上,所述有源区001与所述第一终端保护区002、第二终端保护区003邻接;所述第一终端保护区002位于所述第三终端保护区004的x方向上,所述第二终端保护区003位于所述第三终端保护区004的y方向上,所述第三终端保护区004与所述第一终端保护区002、第二终端保护区003邻接;如图4所示,所述第一终端保护区002内的n型外延层2的顶部设有从有源区001内延伸出的n型柱3与p型柱4,如图9所示为沿着图2中的虚线cc’截得的剖面结构示意图,在所述n型外延层2的表面,设有至少一条p型的第一阱区14,所述第一阱区14之间互相平行分布且沿着x轴方向延伸,所述第一阱区14只设置于n型柱3内;如图4所示,所述第二终端保护区003内的n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,所述n型柱3与p型柱4沿着y轴方向延伸,如图12所示为沿着图4中的虚线aa’截得的剖面结构示意图,在所述p型柱4的顶部的两侧设有p型的第二阱区13,所述第二阱区13之间互相平行分布,且沿着y轴方向延伸,所述第二阱区13只设置于n型柱3内;如图4所示,所述第三终端保护区004内的n型外延层2的顶部设有从第二终端保护区003内延伸出的n型柱3与p型柱4,在所述第三终端保护区004内,如图6所示,所述第一终端保护区002内的第一阱区14在x方向上的延长部分17与所述第二终端保护区003内的第二阱区13在y方向的延长部分18相交并重叠,在所述相交重叠的位置设置p型的第三阱区15,如图13所示为沿着图4中的虚线bb’截得的剖面结构示意图,所述第三阱区15位于所述n型柱3的顶部。

54.所述第一阱区14的宽度为10 μm。

55.所述第二阱区13的宽度为3 μm。

56.一种超结功率半导体器件的制造方法,包括以下步骤:步骤s1、如图24所示,提供n型衬底1,在所述n型衬底1上生长n型外延层2,然后使用第一块光刻板选择性注入p型杂质,退火后形成p型体区6、第二阱区13,并采用相同的方法形成第一阱区14与第三阱区15,如图13所示;

步骤s2、如图25所示,使用第二块光刻板选择性刻蚀出深沟槽;步骤s3、如图26所示,淀积p型单晶硅,所述p型单晶硅填充满步骤s2形成的深沟槽,形成p型柱4;步骤s4、使用第三块光刻板选择性刻蚀出栅极沟槽5后,形成栅氧层9、导电多晶硅8,然后使用第四块光刻板选择性注入n型杂质,激活后形成n型源区7;步骤s5、淀积绝缘介质,形成绝缘介质层10;步骤s6、使用第五块光刻板选择性刻蚀出通孔12,然后淀积金属,使用第六块光刻板选择性刻蚀金属,形成源极金属11和栅极金属16。

57.实施例4如图1所示,为本发明实施例提供的超结功率半导体器件的俯视结构示意图,其表面设有源极金属11与栅极金属16,在功率半导体器件的角落区域005内,如图5所示,包括有源区001和包围所述有源区001的第一终端保护区002、第二终端保护区003和第三终端保护区004,如图14所示为沿着图5中的虚线aa’截得的剖面结构示意图,所述有源区001包括n型衬底1,在所述n型衬底1上方设有n型外延层2,在所述n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,在所述n型柱3与p型柱4的顶部设有p型体区6,在所述p型体区6的表面设有n型源区7,在所述n型柱3的顶部设有沟槽5,所述沟槽5穿透n型源区7与p型体区6,所述沟槽5内设置导电多晶硅8,所述导电多晶硅8通过栅氧层9与n型源区7、p型体区6、n型柱3绝缘,在所述n型柱3与p型柱4的上方设有绝缘介质层10,在所述绝缘介质层10的上方设有源极金属11,在所述绝缘介质层10内设置通孔12,所述源极金属11通过所述通孔12与n型源区7、p型体区6欧姆接触;如图5所示,所述有源区001内的p型柱4延伸的方向为y方向,与所述p型柱4延伸方向垂直的方向为x方向,所述第一终端保护区002位于所述有源区001的y方向上,所述第二终端保护区003位于所述有源区001的x方向上,所述有源区001与所述第一终端保护区002、第二终端保护区003邻接;所述第一终端保护区002位于所述第三终端保护区004的x方向上,所述第二终端保护区003位于所述第三终端保护区004的y方向上,所述第三终端保护区004与所述第一终端保护区002、第二终端保护区003邻接;如图5所示,所述第一终端保护区002内的n型外延层2的顶部设有从有源区001内延伸出的n型柱3与p型柱4,如图9所示为沿着图3中的虚线cc’截得的剖面结构示意图,在所述n型外延层2的表面,设有至少一条p型的第一阱区14,所述第一阱区14之间互相平行分布且沿着x轴方向延伸,所述第一阱区14设置于n型柱3与p型柱4内;如图5所示,所述第二终端保护区003内的n型外延层2的顶部间隔设置条形的n型柱3与条形的p型柱4,所述n型柱3与p型柱4沿着y轴方向延伸,如图14所示为沿着图2中的虚线aa’截得的剖面结构示意图,在所述p型柱4的顶部以及两侧设有p型的第二阱区13,所述第二阱区13之间互相平行分布,且沿着y轴方向延伸,所述第二阱区13设置于n型柱3与p型柱4内;如图5所示,所述第三终端保护区004内的n型外延层2的顶部设有从第二终端保护区003内延伸出的n型柱3与p型柱4,在所述第三终端保护区004内,如图6所示,所述第一终端保护区002内的第一阱区14在x方向上的延长部分17与所述第二终端保护区003内的第二阱区13在y方向的延长部分18相交并重叠,在所述相交重叠的位置设置p型的第三阱区15,

如图15所示为沿着图3中的虚线bb’截得的剖面结构示意图,所述第三阱区15位于所述n型柱3与p型柱4的顶部。

58.所述第一阱区14的宽度为20 μm。

59.所述第二阱区13的宽度为5 μm。

60.一种超结功率半导体器件的制造方法,包括以下步骤:步骤s1、提供n型衬底1,在所述n型衬底1上生长n型外延层2,使用第一块光刻板选择性刻蚀出深沟槽,然后淀积p型单晶硅,形成p型柱4;步骤s2、使用第二块光刻板选择性刻蚀出栅极沟槽5后,形成栅氧层9、导电多晶硅8;步骤s3、使用第三块光刻板选择性注入p型杂质,退火后形成p型体区6、第二阱区13,并采用相同的方法形成第一阱区14与第三阱区15;步骤s4、使用第四块光刻板选择性注入n型杂质,激活后形成n型源区7;步骤s5、淀积绝缘介质,形成绝缘介质层10;步骤s6、使用第五块光刻板选择性刻蚀出通孔12,然后淀积金属,使用第六块光刻板选择性刻蚀金属,形成源极金属11和栅极金属16。

61.所属领域的普通技术人员应当理解:以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的主旨之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1