阵列基板和显示面板的制作方法

1.本技术涉及显示技术领域,具体涉及一种阵列基板和显示面板。

背景技术:

2.目前,因薄膜晶体管(tft)的制程工艺,使得有源层经过蚀刻后,在有源层边缘会形成taper角,即尖角,导致栅极绝缘层沉积后覆盖均匀性不佳,通常在有源层边缘taper角区域栅极绝缘层较有源层主体区域膜层较薄,这使得边缘薄膜晶体管特性提早出现,造成在亚阈区出现驼峰效应,导致器件的性能下降。

技术实现要素:

3.本技术实施例提供一种阵列基板和显示面板,以解决因开启电压不同造成驼峰效应的问题。

4.本技术实施例提供一种阵列基板,包括:

5.衬底;

6.多个晶体管,每一所述晶体管设置于所述衬底上;其中,每一所述晶体管均包括:

7.有源部,所述有源部设置于所述衬底上,所述有源部包括半导体部和与所述半导体部连接且在第一方向上凸出于所述半导体部的至少一个外延尖角部,在所述第一方向上,所述外延尖角部位于所述半导体部的一侧;

8.绝缘部,所述绝缘部设置于所述有源部上,且覆盖所述有源部;

9.第一栅极,所述第一栅极设置于所述绝缘部上,且所述第一栅极位于所述半导体部和所述外延尖角部之上,所述第一栅极沿所述第一方向延伸。

10.可选的,在本技术的一些实施例中,所述阵列基板还包括第二栅极,所述第二栅极与所述第一栅极间隔设置于所述绝缘部上,且所述第二栅极位于所述半导体部和所述外延尖角部之上,所述第二栅极沿着所述第一方向延伸,所述第一栅极与所述第二栅极串联、独立或者并联。

11.可选的,在本技术的一些实施例中,在所述第一方向上,相邻的所述晶体管的所述半导体部通过外延连接部连接,所述第一栅极位于所述半导体部、所述外延尖角部以及所述外延连接部之上,所述阵列基板还包括第二栅极,所述第二栅极与所述第一栅极间隔设置于所述绝缘部上,所述第二栅极位于所述半导体部、所述外延尖角部以及所述外延连接部之上,设置有所述第一栅极的所述半导体部、所述外延尖角部以及所述外延连接部与设置有所述第二栅极的所述半导体部、所述外延尖角部以及所述外延连接部间隔设置。

12.可选的,在本技术的一些实施例中,在所述第一方向上,相邻的所述晶体管的所述半导体部通过外延连接部和所述外延尖角部连接,所述第一栅极位于所述半导体部、所述外延尖角部以及所述外延连接部之上。

13.可选的,在本技术的一些实施例中,在所述第一方向上,所述外延尖角部的长度大于1微米。

14.可选的,在本技术的一些实施例中,所述第一方向与第二方向相交,在所述第二方向上,位于所述外延尖角部上的所述第一栅极在所述衬底上的正投影边缘到所述外延尖角部在所述衬底上的正投影边缘的距离为0-1微米。

15.可选的,在本技术的一些实施例中,所述有源部上设置有通孔,所述通孔位于所述外延尖角部上,所述通孔贯穿所述外延尖角部。

16.可选的,在本技术的一些实施例中,所述半导体部的宽长比的范围为1:1至20:1。

17.可选的,在本技术的一些实施例中,所述阵列基板还包括源极和漏极,所述有源部还包括导体部,所述第一方向与第二方向相交,在所述第二方向上,所述导体部位于所述半导体部的两侧,所述源极设置于一所述导体部上,所述漏极设置于另一所述导体部上。

18.相应的,本技术还提供一种显示面板,所述显示面板包括如上所述的阵列基板。

19.本技术公开了一种阵列基板及显示面板,阵列基板包括衬底和多个晶体管,每一晶体管设置于衬底上;其中,每一晶体管均包括有源部、绝缘部和第一栅极,有源部设置于衬底上,有源部包括半导体部和与半导体部连接且在第一方向上凸出于半导体部的至少一个外延尖角部,在第一方向上,外延尖角部位于半导体部的一侧,绝缘部设置于有源部上,且覆盖有源部,第一栅极设置于绝缘部上,且第一栅极位于半导体部和外延尖角部之上,第一栅极沿第一方向延伸。在本技术中,在第一方向上,通过将有源部的外延尖角部外移,使得外延尖角部不参与半导体部工作的电流减小或得到抑制,避免因开启电压的不同造成驼峰效应,进而提高阵列基板的性能。

附图说明

20.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

21.图1是现有技术提供的阵列基板的平面示意图。

22.图2是图1提供的阵列基板的晶体管沿ab线结构示意图。

23.图3是图1提供的阵列基板中的晶体管的放大平面示意图。

24.图4是图3中的晶体管沿cd线的结构示意图。

25.图5是本技术实施例提供的阵列基板的第一种平面示意图。

26.图6是本技术实施例提供图5中的阵列基板的晶体管的放大平面示意图。

27.图7是本技术提供晶体管的外延尖角部与现有技术中的有源部的边缘区的栅偏压与电流示意图。

28.图8是本技术实施例提供的阵列基板的第二种平面示意图。

29.图9是本技术实施例提供的阵列基板的第三种平面示意图。

具体实施方式

30.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施

例,都属于本技术保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本技术,并不用于限制本技术。在本技术中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。在本技术中,“反应”可以为化学反应或物理反应。

31.请参阅图1-图4。有图1和图2可知,在现有技术中,阵列基板10中的晶体管,在第一方向x上,相邻晶体管的有源部11之间不连接,即同一列且相邻的晶体管的有源部11之间不连接,同一列晶体管共用一栅极12。

32.请参阅图2,每一晶体管还包括衬底13、遮光部14、缓冲部15、栅极绝缘部16、平坦部17、钝化部18、源极19和漏极20,遮光部14设置于衬底13上、缓冲部15设置于衬底13以及遮光部14上,有源部11设置于缓冲部15上,栅极绝缘部16设置于缓冲部15以及有源部11上,栅极12设置于栅极绝缘部上,平坦部17设置于栅极12以及栅极绝缘部上,钝化部18设置于平坦部17上,源极19和漏极20同层设置于钝化部18上,源极19与有源部11的一导体部连接,漏极20与有源部11的另一导体部连接。

33.请参阅图3,阵列基板10的电流由主要漏电流ia和边缘漏电流ic构成,其栅极12电压控制有源部11的沟道区11a的载流子运动,决定阵列基板10器件的开启、工作和关闭状态。请参阅图4,可知有源部11的边缘区11b经过蚀刻后会形成taper角,即尖角,从而导致栅极绝缘部16覆盖均匀性不佳,也就是ⅱ区的栅极绝缘部16膜厚小于ⅰ区的,在同样的栅偏压vg下,两个区域的电场强度不同,ⅱ区的电场强度大于ⅰ区的电场强度,从而导致有源部11的边缘区11b处会先于有源部11的沟道区11a先开启,从而产生了驼峰效应,即因开启电压不同而造成驼峰效应。

34.因此,现有技术的阵列基板10中,因有源部11在蚀刻后,会形成taper角,从而导致栅极12绝缘部覆盖均匀性不佳,使得有源部11的边缘区11b处会先于有源部11的沟道区11a先开启,从而产生了驼峰效应,也即有源部11边缘提前开启,而造成驼峰效应。

35.为了解决上述问题,本技术提供了一种阵列基板及显示面板,可以避免现有技术中的有源部边缘提前开启,而造成驼峰效应的问题。

36.本技术公开了一种阵列基板及显示面板,阵列基板包括衬底和多个晶体管,每一晶体管设置于衬底上;其中,每一晶体管均包括有源部、绝缘部和第一栅极,有源部设置于衬底上,有源部包括半导体部和与半导体部连接且在第一方向上凸出于半导体部的至少一个外延尖角部,在第一方向上,外延尖角部位于半导体部的一侧,绝缘部设置于有源部上,且覆盖有源部,第一栅极设置于绝缘部上,且第一栅极位于半导体部和外延尖角部之上,第一栅极沿第一方向延伸。

37.在本技术中,在第一方向上,通过将有源部的外延尖角部外移,使得外延尖角部不参与半导体部工作的电流减小或得到抑制,避免因开启电压的不同造成驼峰效应,进而提高阵列基板的性能。

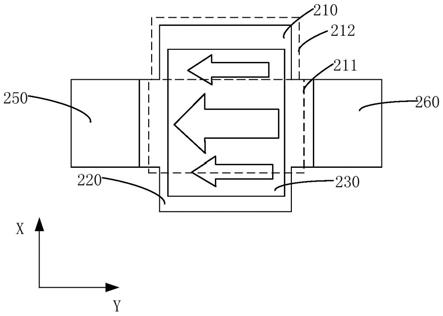

38.请参阅图5和图6,图5本技术实施例提供的阵列基板的第一种平面示意图,图6本技术实施例提供图5中的阵列基板的晶体管的放大平面示意图。本技术提供一种阵列基板30,包括衬底100和多个晶体管200。具体描述如下。

39.每一晶体管200设置于衬底100上,其中,每一晶体管200均包括有源部210、绝缘部

220以及第一栅极230,

40.有源部210设置于衬底100上。有源部210包括一半导体部211和与半导体部211连接且在第一方向x上凸出于半导体部211的一外延尖角部212。在第一方向x上,外延尖角部212位于半导体部211的一侧。

41.在本技术中,在第一方向x上,在与半导体部211连接且在第一方向x上设置有凸出于半导体部211的一外延尖角部212,使得外延尖角部212不参与有源部210的工作的电流减小或得到抑制,且因外延尖角部212凸出于半导体部211,使得后续覆盖的绝缘部220在半导体部211的膜厚均匀,从而使得开启电压一致,也即避免外延尖角部212先于半导体部211开启,从而避免了驼峰效应,从而提高了阵列基板30的性能。

42.请参阅图7,图7是本技术提供晶体管的外延尖角部与现有技术中的有源部的边缘区的栅偏压与电流示意图。对本技术提供的外延尖角部212的电流和现有技术中的有源部11的边缘区11b施加0.1v电压,在vg为0.1-3v时,本技术提供的外延尖角部212的电流小于现有技术中的有源部11的边缘区11b;对本技术提供的外延尖角部212的电流和现有技术中的有源部11的边缘区11b施加10v电压,在vg为0.1-3v时,本技术提供的外延尖角部212的电流小于现有技术中的有源部11的边缘区11b,由此可知,本技术提供的晶体管200使得外延尖角部212不参与有源部210的工作的电流减小或得到抑制,避免了因现有技术中的有源部11的边缘区11b(即尖角)先于有源部11的沟道区11a先开启,而造成驼峰效应,即因开启电压不同而造成驼峰效应。

43.在一实施例中,在第一方向x上,外延尖角部212的长度大于1微米。具体的,在第一方向x上,外延尖角部212的长度可以大于1微米、3微米、5微米、10微米、50微米、80微米或1000微米等。在本技术中,在第一方向x上,将外延尖角部212的长度设置为大于1微米,使得边缘漏电流ic可以忽略不计,避免外延尖角部212先于半导体部211先开启,进而避免出现驼峰效应的问题,进而提高了阵列基板30的性能。

44.在一实施例中,在第一方向x上,多个晶体管200的外延尖角部212可以均位于同一侧或者不同侧,也即外延尖角部212可以均位于半导体部211的同一侧。如,相邻的两个晶体管200的外延尖角部212均位于半导体部211的下方,也即一晶体管200的有源部210的外延尖角部212位于远离另一晶体管200的有源部210的外延尖角部212的一侧;或者,一晶体管200的有源部210的外延尖角部212位于靠近另一晶体管200的有源部210的外延尖角部212的一侧。

45.在一实施例中,有源部210上设置有通孔201,通孔201位于外延尖角部212上,通孔201贯穿外延尖角部212以暴露衬底100。在本技术中,在位于外延尖角部212上设置通孔201,提高了阵列基板30的散热效率,从而可以降低阵列基板30的温度,从而保证阵列基板30的性能。

46.在一实施例中,通孔201的平面形状可以为矩形、椭圆形、四边形、三角形和不规则图形中的一种或几种组合。但不限于此。

47.在一实施例中,在第一方向x上,半导体部211的两侧均设置有外延尖角部212。在本技术中,在第一方向x上,半导体部211的两侧均设置外延尖角部212,进一步使得后续覆盖的绝缘部220在半导体部211的膜厚均匀,从而使得开启电压一致,也即避免外延尖角部212先于半导体部211开启,从而避免了驼峰效应,从而提高了阵列基板30的性能。

48.在一实施例中,有源部210包括两个连接的半导体部211。

49.在一实施例中,有源部210还包括导体部213。在第二方向y上,第一方向x与第二方向y相交,导体部213位于半导体部211的两侧。

50.在一实施例中,半导体部211的宽长比(w/l)的范围为1:1至20:1。具体的,半导体部211的宽长比(w/l)的范围可以为2:1、6:1、8:1、10:1、12:1、18:1或20:1等。在本实施例中,将半导体部211的宽长比(w/l)的范围设置为1:1至20:1,改善阵列基板30的电压负偏的情况,从而提高了阵列基板30的性能。

51.在一实施例中,阵列基板30还包括外延连接部240。在第一方向x上,晶体管200的外延尖角部212与相邻的晶体管200的半导体部211通过外延连接部240连接。

52.绝缘部220设置于有源部210上,且覆盖有源部210。

53.第一栅极230设置于绝缘部220上,且第一栅极230位于半导体部211、外延尖角部212以及外延连接部240之上,第一栅极230沿第一方向x延伸。

54.在一实施例中,在第二方向y上,位于外延尖角部212上的第一栅极230在衬底100上的正投影边缘到外延尖角部212在衬底100上的正投影边缘的距离为0-1微米。具体的,在第二方向y上,位于外延尖角部212上的第一栅极230在衬底100上的正投影边缘到外延尖角部212在衬底100上的正投影边缘的距离可以为0微米、0.3微米、0.5微米、0.8微米或1微米等。当在第二方向y上,位于外延尖角部212上的第一栅极230在衬底100上的正投影边缘到外延尖角部212在衬底100上的正投影边缘的距离可以为0微米时,位于外延尖角部212上的第一栅极230在衬底100上的正投影与外延尖角部212在衬底100上的正投影完全重合。

55.在本技术中,在第二方向y上,位于外延尖角部212上的第一栅极230在衬底100上的正投影边缘到外延尖角部212在衬底100上的正投影边缘的距离设置为0-1微米,进一步避免驼峰效应,从而进一步提高阵列基板30的性能。

56.在一实施例中,在第一方向x上,位于半导体部211上的第一栅极230的宽度与位于外延尖角部212上的第一栅极230的宽度相同。在本技术中,在第一方向x上,将位于半导体部211上的第一栅极230的宽度设置为与位于外延尖角部212上的第一栅极230的宽度相同,从而简化了阵列基板30的制备方法。

57.在一实施例中,晶体管200还包括源极250和漏极260。源极250设置于一导体部213上。漏极260设置于另一导体部213上。

58.需要说明的是,本技术的晶体管200可以为复用晶体管,可以应用于显示面板集成电路设计中。

59.在一实施例中,阵列基板30还包括第二栅极270,第二栅极270与第一栅极230间隔设置于绝缘部220上,且第二栅极270位于半导体部211和外延尖角部212上,第二栅极270沿着第一方向x延伸,第一栅极230与第二栅极270串联、独立或者并联。设置有第一栅极230的半导体部211、外延尖角部212以及外延连接部240与设置有第二栅极270的半导体部211、外延尖角部212以及外延连接部240间隔设置。

60.在本技术中,晶体管200为双栅晶体管200,可以提高器件的迁移率,从而提高阵列基板30的性能。

61.请参阅图8,图8是本技术实施例提供的阵列基板30的第二种平面示意图。需要说明的是,第二种平面示意图与第一种平面示意图的不同之处在于:通孔201位于外延连接部

240上,且部分外延连接部240设置有通孔201。

62.请参阅图9,图9是本技术实施例提供的阵列基板30的第三种平面示意图。需要说明的是,第三种平面示意图与第二种平面示意图的不同之处在于:

63.通孔201均位于外延连接部240。在本技术种,将通孔201均设置于位于外延连接部240上,从而进一步提高膜层的散热效率,从而进一步提高阵列基板30的性能。

64.本技术还提供一种显示面板,显示面板包括本技术所述的阵列基板30。

65.本技术公开了一种阵列基板30及显示面板,阵列基板30包括衬底100和多个晶体管200,每一晶体管200设置于衬底100上;其中,每一晶体管200均包括有源部210、绝缘部220和第一栅极230,有源部210设置于衬底100上,有源部210包括半导体部211和与半导体部211连接且在第一方向x上凸出于半导体部211的至少一个外延尖角部212,在第一方向x上,外延尖角部212位于半导体部211的一侧,绝缘部220设置于有源部210上,且覆盖有源部210,第一栅极230设置于绝缘部220上,且第一栅极230位于半导体部211和外延尖角部212之上,第一栅极230沿第一方向x延伸。在本技术中,在第一方向x上,通过将有源部210的外延尖角部212外移,使得外延尖角部212不参与半导体部211工作的电流减小或得到抑制,避免因开启电压的不同造成驼峰效应,进而提高阵列基板30的性能。

66.以上对本技术实施例所提供的一种阵列基板和显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1