半导体结构及其形成方法、工作方法和可靠性测试方法与流程

本发明涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法、工作方法和可靠性测试方法。

背景技术:

1、在晶圆生产过程中,需要对晶圆的电学性能进行测试,通常在切割道上形成与芯片上相同的器件结构,对切割道区上的器件结构进行测试。

2、由于芯片上器件的多样性,需要针对不同的器件采用不同的测试结构和测试方法进行测试,以保证芯片的电学性能满足要求。

3、因此,需要持续完善测试的全面性。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构及其形成方法、工作方法和可靠性测试方法,以使得半导体结构的测试更为全面。

2、为解决上述技术问题,本发明技术方案提供半导体结构,包括:衬底;位于衬底上的若干匝电感线圈,若干匝所述电感线圈在衬底上的投影图形呈同心环分布,且若干匝所述电感线圈串联;位于衬底上的若干匝检测线圈,若干匝所述检测线圈与电感线圈同心分布,且若干匝所述检测线圈串联,若干匝所述检测线圈分别位于相邻的电感线圈之间,或者,若干匝所述电感线圈分别位于相邻的检测线圈之间。

3、可选的,所述检测线圈的分布方式与所述电感线圈的分布方式相同。

4、可选的,若干匝所述电感线圈位于同一层。

5、可选的,若干匝所述电感线圈沿垂直于衬底表面方向层叠排列;所述半导体结构还包括:若干第一连接层和若干第二连接层,相邻两层电感线圈通过第一连接层电连接,相邻两层检测线圈通过第二连接层电连接。

6、可选的,所述电感线圈在衬底上的投影图形包括椭圆形、矩形或者八边形;所述检测线圈在衬底上的投影图形包括椭圆形、矩形或者八边形。

7、可选的,所述电感线圈的宽度大于检测线圈的宽度。

8、可选的,相邻电感线圈和检测线圈之间的间距为0.11微米~2微米。

9、可选的,所述衬底包括切割道区和芯片区,若干匝电感线圈和若干匝检测线圈位于切割道区或芯片区,或者若干匝电感线圈和若干匝检测线圈同时位于切割道区和芯片区。

10、可选的,还包括:分别与检测线圈两端电连接的第一量测结构和第二量测结构;分别与电感线圈两端电连接的第一给压结构和第二给压结构。

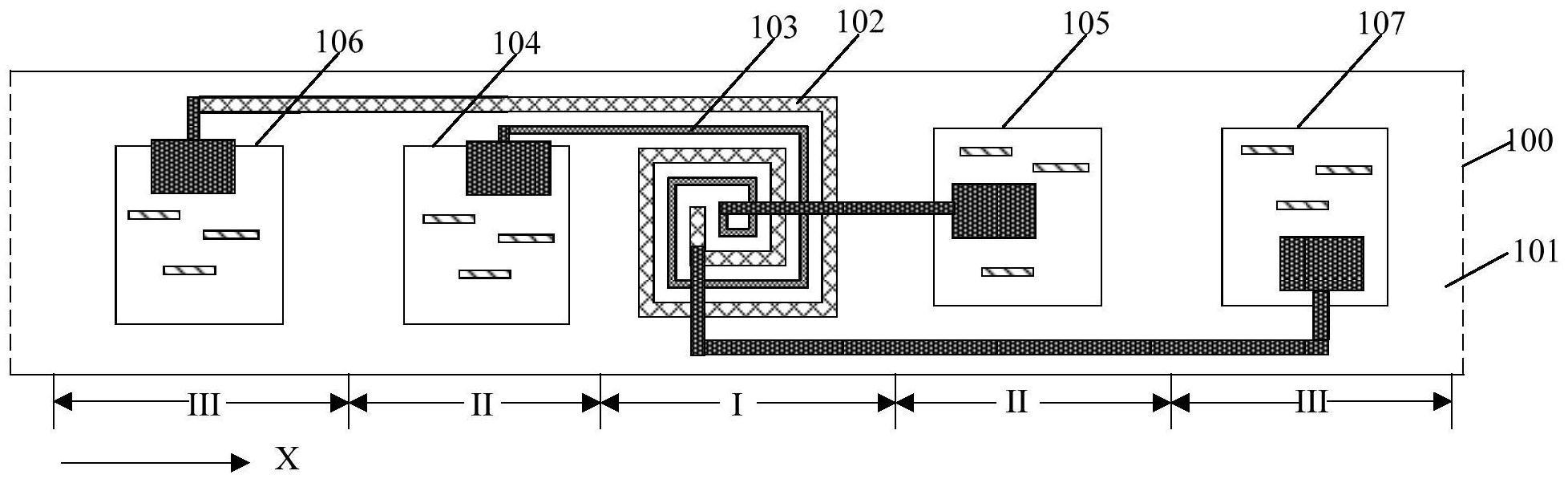

11、可选的,所述切割道区包括器件区、位于器件区两侧的量测区以及位于器件区两侧的给压区,任一所述量测区位于器件区和给压区之间,所述给压区、量测区和器件区沿切割道区延伸方向排列;所述电感线圈和检测线圈位于器件区上,所述第一量测结构和第二量测结构分别位于器件区两侧的量测区上,所述第一给压结构和第二给压结构分别位于器件区两侧的给压区上。

12、相应地,本发明技术方案还提供一种半导体结构的工作方法,包括:提供半导体结构,所述半导体结构包括:衬底;位于衬底上的若干匝电感线圈,若干匝所述电感线圈在衬底上的投影图形呈同心环分布,且若干匝所述电感线圈串联;位于衬底上的若干匝检测线圈,若干匝所述检测线圈与电感线圈同心分布,且若干匝所述检测线圈串联,若干匝所述检测线圈分别位于相邻的电感线圈之间,或者,若干匝所述电感线圈分别位于相邻的检测线圈之间;对电感线圈加载电压;获取检测线圈的电阻。

13、可选的,所述半导体结构还包括:分别与检测线圈两端电连接的第一量测结构和第二量测结构,分别与电感线圈两端电连接的第一给压结构和第二给压结构;通过第一给压结构和第二给压结构对电感线圈加载电压,通过第一量测结构和第二量测结构获取检测线圈的电阻。

14、可选的,获取检测线圈的电阻之后,还包括:根据检测线圈的电阻对所述电感线圈的可靠性状态进行判断;根据检测线圈的电阻对所述电感线圈的可靠性状态进行判断的方法包括:若所述检测线圈的电阻值为无穷大,则所述电感线圈没有发生电迁移效应;若所述检测线圈的电阻值在预设范围内,则所述电感线圈存在电迁移效应。

15、可选的,通过第一给压结构和第二给压结构对电感线圈加载电压的同时,还通过第一量测结构对检测线圈加载电流,通过第二量测结构对检测线圈的电阻进行量测;根据检测线圈的电阻对所述电感线圈的可靠性状态进行判断的方法包括:若所述检测线圈的电阻值在预设范围内,则所述电感线圈没有发生电迁移效应;若所述检测线圈的电阻值小于预设值,则所述电感线圈存在电迁移效应。

16、可选的,所述衬底包括切割道区和芯片区,若干匝电感线圈和若干匝检测线圈位于切割道区或芯片区,或者若干匝电感线圈和若干匝检测线圈同时位于切割道区和芯片区。

17、相应地,本发明技术方案还提供一种半导体结构的可靠性测试方法,包括:提供半导体结构,所述半导体结构包括:衬底;位于衬底上的若干匝电感线圈,若干匝所述电感线圈在衬底上的投影图形呈同心环分布,且若干匝所述电感线圈串联;位于衬底上的若干匝检测线圈,若干匝所述检测线圈与电感线圈同心分布,且若干匝所述检测线圈串联,若干匝所述检测线圈分别位于相邻的电感线圈之间,或者,若干匝所述电感线圈分别位于相邻的检测线圈之间;采用斜坡电流测试对所述半导体结构进行可靠性测试。

18、可选的,所述斜坡电流测试的参数包括:温度为25摄氏度;增加电流至电流密度为15兆安培每平方厘米,每次加大的单位电流为1e-5安培,间隔时间为0.01秒。

19、可选的,所述可靠性测试的时间范围为59分钟至61分钟。

20、相应地,本发明技术方案还提供一种半导体结构的形成方法,包括:提供衬底;在衬底上形成若干匝电感线圈,若干匝所述电感线圈在衬底上的投影图形呈同心环分布,且若干匝所述电感线圈串联;在衬底上形成若干匝检测线圈,若干匝所述检测线圈与电感线圈同心分布,且若干匝所述检测线圈串联,若干匝所述检测线圈分别位于相邻的电感线圈之间,或者,若干匝所述电感线圈分别位于相邻的检测线圈之间。

21、可选的,所述衬底包括切割道区和芯片区,若干匝电感线圈和若干匝检测线圈位于切割道区或芯片区,或者若干匝电感线圈和若干匝检测线圈同时位于切割道区和芯片区。

22、与现有技术相比,本发明的技术方案具有以下有益效果:

23、本发明的技术方案,通过在衬底上设置若干匝检测线圈,若干匝所述检测线圈与电感线圈同心分布,且若干匝所述检测线圈串联,若干匝所述检测线圈分别位于相邻的电感线圈之间,或者,若干匝所述电感线圈分别位于相邻的检测线圈之间。所述检测线圈和电感线圈的设置方式使得在电感线圈发生电迁移时,所述检测线圈能够迅速检测到,从而能够对电感线圈的电迁移可靠性性能进行测试。

24、本发明的可靠性测试方法,通过采用斜坡电流测试对所述半导体结构进行可靠性测试,从而能够缩短测试周期,有利于快速评估多批次产品,提高生产效率;此外,进行可靠性测试的半导体结构为未封装的晶圆产品,能够进一步提高测试效率,简化测试流程。

25、进一步,所述斜坡电流测试的参数包括:温度为25摄氏度;增加电流至电流密度为15兆安培每平方厘米,每次加大的单位电流为1e-5安培,间隔时间为0.01秒。所述工艺参数通过快速增加电流密度,使得半导体结构的电阻变大,从而产生大量的热以使得测试的环境温度达到预设值,使得从而不必采用直接升高环境温度的方式对半导体结构进行加热,以快速达到常规可靠性测试的条件甚至严格于常规可靠性测试的条件,缩短测试周期。

- 还没有人留言评论。精彩留言会获得点赞!