一种新型高维持电压SCR结构

一种新型高维持电压scr结构

技术领域

1.本发明涉及芯片保护技术领域,具体是一种新型高维持电压scr结构。

背景技术:

2.静电放电(esd)是指物体带有不同的静电电荷,在互相靠近或接触时,电荷发生转移的自然现象。静电放电可以分为两个阶段,第一阶段是电荷在物体表面逐渐积累的过程,第二阶段是放电过程。在集成电路产业中,在芯片制造、封装、运输等过程中,芯片内部或外界环境可能会形成一定量的电荷积累。当芯片与外界形成导电通路后,聚集在电路内部或者外界的电荷通过pin引脚流过芯片,虽然总电荷量不多,但由于esd过程时间短,电应力大,会产生高电压大电流,在芯片内的局部空间,短时间内大量焦耳热积累,温度迅速升高造成芯片被烧毁。

3.为了避免芯片在发生静电放电过程中被损坏,需要对芯片添加必要的esd防护。芯片的片上防护一般是在内部核心电路的引脚并联esd防护电路。电路正常工作时,esd防护电路处于关闭状态,当esd事件发生时,由于瞬时的高电压,esd防护电路开启,提供一条导通电阻很低的电流泄放路径,泄放大部分静电电流,同时减少电路承受的esd脉冲电压,从而保护内部核心电路不被损坏。当esd事件结束后,esd防护电路自动关闭,以保证不会影响被保护电路的正常工作。

4.对于片上(on-chip)esd防护,首先要确定该工艺的esd设计窗口;esd设计窗口以被保护电路正常共工作电压vdd和它被保护电路的最小失效电压bv为界限,将电压小于vdd的部分称为被保护电路正常工作区、电压大于bv的部分称为被保护电路失效区、在vdd和bv之间的区域便是esd的设计窗口区域。为了提高ic产品的稳定性,一般在定义esd设计窗口时会留有10%的设计余量。可控硅(scr)因为其鲁棒性高、占用版图面积小、寄生电容低等优点,被广泛应用于集成电路的esd保护器件。

5.然而,现有scr的维持电压过低,在高工作电压下面临闩锁的问题,会影响芯片内部被保护电路的安全与功能,制约其在集成电路的应用。针对以上问题,提出一种新型高维持电压scr结构。

技术实现要素:

6.本发明的目的在于提供一种新型高维持电压scr结构,以解决上述背景技术中提出的问题。

7.为实现上述目的,本发明提供如下技术方案:

8.一种新型高维持电压scr结构,包括p型衬底,所述p型衬底顶部设有一组p型阱区和一组第一n型阱区,所述p型阱区远离第一n型阱区一侧设有第二n型阱区;

9.所述p型阱区一侧设有第一p+重掺杂区域,所述p型阱区另一侧设有第二p+重掺杂区域;

10.所述p型阱区上设有第三p+重掺杂区,所述第三p+重掺杂区两侧均设有浅沟道隔

离,所述第一p+重掺杂区域设置在浅沟道隔离远离第三p+重掺杂区一侧。

11.优选的,所述第一p+重掺杂区域和第三p+重掺杂区通过金属线互连。

12.优选的,所述第一p+重掺杂区域设置在p型阱区与第一n型阱区桥接处,所述第二p+重掺杂区域设置在p型阱区与第二n型阱区桥接处。

13.优选的,所述第一n型阱区上设有第一n+注入区和第一p+注入区,所述第一n+注入区和第一p+注入区之间设有浅沟道隔离,所述第一n+注入区远离第一p+注入区一侧设有浅沟道隔离。

14.优选的,所述第二n型阱区上设有第二n+注入区,所述第二n+注入区两侧均设有浅沟道隔离。

15.优选的,所述第一p+注入区和第一p+重掺杂区域之间的第一n型阱区上设有氧化层,氧化层上为多晶硅栅极。

16.优选的,所述第一n型阱区上设有阳极,所述阳极连接有栅极,所述第二n型阱区处设有阴极。

17.与现有技术相比,本发明的有益效果是:

18.本发明与传统scr相比,针对scr的低维持电压问题,在p型阱区添加了第三p+重掺杂区域,扩展了第二p+重掺杂区域,并在与p型阱相邻处添加了第二n型阱区,在不增加工艺复杂度和失效电流基本不变的情况下,提高scr器件的维持电压,避免闩锁效应的威胁。

附图说明

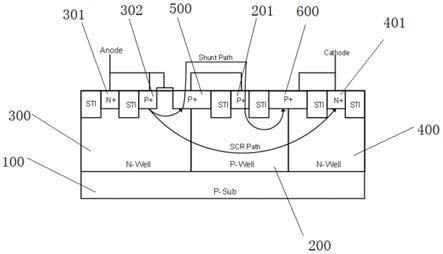

19.图1为本发明的结构示意图。

20.图2为本发明的等效电路图。

21.图中:100

‑‑

p型衬底;

22.200

‑‑

p型阱区、201

‑‑

第三p+重掺杂区;

23.300

‑‑

第一n型阱区、301

‑‑

第一n+注入区、302

‑‑

第一p+注入区;

24.400

‑‑

第二n型阱区、401

‑‑

第二n+注入区;

25.500

‑‑

第一p+重掺杂区域、600

‑‑

第二p+重掺杂区域。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

27.请参阅图1,本发明实施例中,一种新型高维持电压scr结构,包括p型衬底100,所述p型衬底100顶部设有一组p型阱区200和一组第一n型阱区300,所述p型阱区200远离第一n型阱区300一侧设有第二n型阱区400;

28.所述p型阱区200一侧设有第一p+重掺杂区域500,所述p型阱区200另一侧设有第二p+重掺杂区域600;

29.所述p型阱区200上设有第三p+重掺杂区201,所述第三p+重掺杂区201两侧均设有浅沟道隔离,所述第一p+重掺杂区域500设置在浅沟道隔离远离第三p+重掺杂区201一侧。

30.所述第一p+重掺杂区域500和第三p+重掺杂区201通过金属线互连。

31.所述第一p+重掺杂区域500设置在p型阱区200与第一n型阱区300桥接处,所述第二p+重掺杂区域600设置在p型阱区200与第二n型阱区400桥接处。

32.所述第一n型阱区300上设有第一n+注入区301和第一p+注入区302,所述第一n+注入区301和第一p+注入区302之间设有浅沟道隔离,所述第一n+注入区301远离第一p+注入区302一侧设有浅沟道隔离。

33.所述第二n型阱区400上设有第二n+注入区401,所述第二n+注入区401两侧均设有浅沟道隔离。

34.所述第一p+注入区302和第一p+重掺杂区域500之间的第一n型阱区300上设有氧化层,氧化层上为多晶硅栅极。

35.所述第一n型阱区300上设有阳极,所述阳极连接有栅极,所述第二n型阱区400处设有阴极。

36.新型高维持电压scr结构的等效电路图如图2所示,主要由两个寄生的pnp晶体管(q

pnp

和q1)、一个寄生的npn晶体管(q

npn

)、n型/p型阱区电阻(r

nw

/r

pw1

)以及等效电阻(r

pw2

)组成。

37.其工作原理如下:

38.scr的工作条件为:

39.β

pnp

×

β

npn

≥1

40.式中,β

pnp

和β

npn

分别是pnp和npn晶体管的共发射极直流短路电流放大倍数。

41.减小寄生晶体管的电流放大倍数可以弱化正反馈效应,从而提高维持电压。

42.以pnp晶体管为例,电流放大倍数β可以表示为:

[0043][0044]

其中α为共基极直流短路电流放大倍数,表达式如下:

[0045]

α=β

*

·

γ

[0046]

β*为基区输运系数,γ为发射极注入效率。γ表达式如下:

[0047][0048]jne

为基区注入发射区的电子形成的电子扩散电流,j

ne

为发射区注入基区的空穴形成的空穴扩散电流。

[0049]

由上述公式可知,发射极注入效率(γ)与电路增益(β)成正比,因此,减少发射区注入基区的少子电流(j

ne

),可以减小发射极注入效率(γ),弱化正反馈效应,提高维持电压。

[0050]

当给本发明新型高维持电压scr的阳极(anode)施加一个正脉冲时,嵌入的第一p+重掺杂区域500会在第一n型阱区300和p型阱区200的交界处产生一个附加电场,击穿首先发生在此处;

[0051]

雪崩击穿产生的空穴电流流向阴极(cathode),在p型阱区200的电阻(r

pw1

)上产生

压降,最终使得寄生npn管(q

npn

)开启;同时雪崩击穿产生的电子电流流向阳极(anode),在n型阱区电阻(r

nw

)上产生压降,最终使得寄生pnp管(q

pnp

)开启;此后寄生pnp管(q

pnp

)的集电极电流为寄生npn管(q

npn

)提供基极电流,同时寄生npn管(q

npn

)的集电极电流为寄生pnp管(q

pnp

)提供基极电流,两管形成电流正反馈机制,scr路径导通。随着esd电流的继续增加,q1(p+阳极/n阱/p+桥)将开启,电流通过导线流向p型阱区200的p+,经过等效电阻(r

pw2

)流向阴极p+;

[0052]

本发明的新型高维持电压scr有两条泄放电流路径:一条为主scr路径,另一条为寄生pnp/电阻(q1/r)分流路径;寄生pnp/电阻(q1/r

pw2

)形成的分流路径将分流流过主scr路径的发射极结的电流,降低了寄生晶体管的增益,从而削弱了正反馈效应,提高了维持电压。

[0053]

需要注意的是,本技术中p型阱区200的p+即第三p+重掺杂区201,阴极p+即第二p+重掺杂区域600,q1即第一p+注入区302、第一n型阱区300、第一p+重掺杂区域500形成的pnp。

[0054]

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1