一种选通器、存储器及其制备方法与流程

1.本发明涉及半导体技术领域,尤其涉及一种选通器、存储器及其制备方法。

背景技术:

2.选通器是一种重要的数字电路结构,也是现场可编程门阵列(fpga)、存储器(memory)等众多器件的重要组成单元,直接影响器件的速度、功耗等性能。应用选通器的三维(3d)存储器是现代信息技术中用于保存信息的记忆设备,在超高集成密度方面极具前景。然而三维存储器中的泄漏通路却降低了其性能,增加了整体的功耗,并且限制着三维存储器的规模。随着存储密度的逐渐增大,如何优化和改善选通器,以及应用选通器的三维存储器性能成为本领域的重要研究方向。

技术实现要素:

3.有鉴于此,本发明实施例为解决背景技术中存在的至少一个问题而提供一种选通器、存储器及其制备方法。

4.为达到上述目的,本发明的技术方案是这样实现的:

5.本发明实施例提供了一种选通器,所述选通器包括:选通层,所述选通层的材料包括二维bi2o2x材料,其中x选自s、se、te中的至少一种。

6.上述方案中,所述选通层的材料包括二维bi2o2se材料。

7.上述方案中,所述选通层的阈值电压小于4v。

8.上述方案中,所述选通层的厚度小于10nm。

9.本发明实施例还提供了一种存储器,所述存储器包括上述方案所述的选通器。

10.上述方案中,所述存储器包括:

11.沿第一方向延伸的第一导电线;

12.堆叠在所述第一导电线上且沿第一方向延伸的选通层,所述选通层为层状的所述选通器;

13.沿第二方向延伸的第二导电线,所述第一方向与所述第二方向相交;

14.位于所述选通层与所述第二导电线之间,且沿第三方向延伸的存储单元,所述第三方向垂直于所述第一方向与所述第二方向。

15.本发明实施例还提供了一种选通器的制备方法,包括:

16.形成选通层,所述选通层包括二维bi2o2x材料,所述x选自s、se、te中的至少一种。

17.上述方案中,所述选通层的材料包括二维bi2o2se材料。

18.上述方案中,所述选通层的阈值电压小于4v。

19.上述方案中,所述选通层的厚度小于10nm。

20.本发明实施例还提供了一种存储器的制备方法,包括:

21.形成第一导电线材料层,所述第一导电线材料层用于形成沿第一方向延伸的第一导电线;

22.在所述第一导电线材料层上形成沿第三方向叠置的选通材料层和存储单元材料层,所述选通材料层包括二维bi2o2x材料,所述x选自s、se、te中的至少一种,所述选通材料层和存储单元材料层用于形成选通层和存储单元;

23.形成位于所述存储单元上的沿第二方向延伸的第二导电线;其中,

24.所述第一方向与所述第二方向相交,所述第三方向垂直于所述第一方向与所述第二方向。

25.上述方案中,所述选通材料层和存储单元材料层用于形成选通层和存储单元,包括:

26.所述选通材料层和存储单元材料层用于形成选通层和多个存储单元,所述多个存储单元位于同一所述选通层上。

27.本发明实施例采用二维bi2o2x材料作为选通层,利用其平面外方向的单极性阻变行为实现选通层的功能,可以实现很好的双向导通特性。由于二维材料的特性,可以很好地降低器件深宽比,因而有利于器件的高密度。另外二维的bi2o2x材料自身具有绝缘特性,在关态时具有较低的漏电流。同时,可通过调节材料中的氧空位以及x空位控制器件性能,该选通层有更好的调控自由度。

28.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

29.图1为相关技术中存储器的结构示意图;

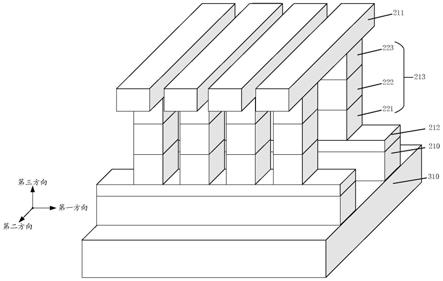

30.图2为本发明一实施例提供的存储器的结构示意图;

31.图3为二维bi2o2x材料的导通原理示意图;

32.图4为本发明另一实施例提供的存储器的结构示意图;

33.图5为本发明实施例提供的存储器的制备方法的流程示意图;

34.图6a至图6f为本发明一实施例提供的存储器在制备过程中的结构示意图。

35.附图标记:

36.110-位线;111-字线;112-选通层;113-存储单元;

37.210-第一导电线;210

’‑

第一导电线材料层;211-第二导电线;211

’‑

第二导电线材料层;212-选通层;212

’‑

选通材料层;213-存储单元;213

’‑

存储单元材料层;213

”‑

存储单元结构体;221-第一电极层;221

’‑

第一电极材料层;222-存储层;222

’‑

存储材料层;223-第二电极层;223

’‑

第二电极材料层;

38.衬底-310;二维bi2o2x材料-311;山丘状结构-312。

具体实施方式

39.下面将参照附图更详细地描述本发明公开的示例性实施方式。虽然附图中显示了本发明的示例性实施方式,然而应当理解,可以以各种形式实现本发明,而不应被这里阐述的具体实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本发明,并且能够将本发明公开的范围完整的传达给本领域的技术人员。

40.在下文的描述中,给出了大量具体的细节以便提供对本发明更为彻底的理解。然

而,对于本领域技术人员而言显而易见的是,本发明可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本发明发生混淆,对于本领域公知的一些技术特征未进行描述;即,这里不描述实际实施例的全部特征,不详细描述公知的功能和结构。

41.在附图中,为了清楚,层、区、元件的尺寸以及其相对尺寸可能被夸大。自始至终相同附图标记表示相同的元件。

42.应当明白,当元件或层被称为“在

……

上”、“与

……

相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在

……

上”、“与

……

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本发明教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。而当讨论的第二元件、部件、区、层或部分时,并不表明本发明必然存在第一元件、部件、区、层或部分。

43.空间关系术语例如“在

……

下”、“在

……

下面”、“下面的”、“在

……

之下”、“在

……

之上”、“上面的”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在

……

下面”和“在

……

下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

44.在此使用的术语的目的仅在于描述具体实施例并且不作为本发明的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

45.在下文的描述中使用的,术语“三维存储器”是指具有如下存储单元的半导体器件:所述存储单元垂直布置在横向取向的衬底上,以使得所述存储单元的数量在垂直方向上相对于衬底提高。如本文使用的,术语“垂直/垂直地”表示标称地垂直于衬底的横向表面。

46.如图1所示,相关技术中,三维存储器主要为三维交叉点(cross-point)架构,该架构下选通层112和存储单元113位于彼此垂直相交的位线(bl)110和字线(wl)111的交叉点处。对于基于cross-point结构的相变存储器、阻变存储器、磁随机存储器来说,交叉阵列中的漏电流问题是实现高密度集成的主要障碍,研制具有高疲劳特性、高均一性的通用选通层对于实现上述存储器的高密度三维交叉阵列集成具有重要意义。对于先进的选通层材料来说,不仅需要其具有很好的开关比,即大的开态电阻,满足大的操作电流的需求,以及低的关态电阻,满足小的漏电需求,还要求选通层材料具有很好的疲劳特性,即重复开关的次数要匹配存储材料的疲劳特性,否则将会使得存储的信息丢失以及器件失效。另外对于先

进工艺节点的不断演进,也要求我们的选通层要做到尽可能的厚度薄且尺寸小。除此之外,对于选通层的要求就是其开关速度要尽可能的快,否则将会影响到对器件的操作速度。

47.目前的1s1r(一选一电阻)的相变存储器或者阻变存储器都是采用双向阈值开关(ots,ovonic threshold switching)作为选通层单元,但是ots选通层单元存在着厚度高、漏电流大、阈值电压高等缺点。

48.基于此,本发明实施例提供了一种选通器,如图2所示,所述选通器包括:选通层212,所述选通层212的材料包括二维bi2o2x材料,其中x选自s、se、te中的至少一种。

49.本发明实施例还提供了一种存储器,包括上述方案所述的选通器,如图2所示,所述存储器包括:沿第一方向延伸的第一导电线210;堆叠在所述第一导电线210上且沿第一方向延伸的选通层212,所述选通层212为层状的所述选通器;沿第二方向延伸的第二导电线211,所述第一方向与所述第二方向相交;位于所述选通层212与所述第二导电线211之间,且沿第三方向延伸的存储单元213,所述第三方向垂直于所述第一方向与所述第二方向。

50.在实际操作中,所述第一导电线210和第二导电线211可以分别作为字线和位线使用。例如,当所述第一导电线210为字线时,所述第二导电线211为位线,当所述第一导电线210为位线时,所述第二导电线211为字线。所述第一导电线210和第二导电线211可以由图案化工艺之后形成的20nm/20nm等幅线宽(line/space,l/s)导电线构成。所述第一导电线和所述第二导电线的材料可以包括导电材料,所述导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。一些具体实施例中,所述第一导电线和所述第二导电线的材料为钨。

51.在一些实施例中,所述第一方向与所述第二方向可以相互垂直。

52.本发明实施例采用二维bi2o2x材料作为选通层,利用其平面外方向的单极性阻变行为实现选通层的功能,可以实现很好的双向导通特性。由于二维材料的特性,可以很好地降低器件深宽比,因而有利于器件的高密度。另外二维的bi2o2x材料自身具有绝缘特性,在关态时具有较低的漏电流。同时,可通过调节材料中的氧空位以及x空位控制器件性能,该选通层有更好的调控自由度。

53.在一些实施例中,所述选通层的材料包括二维bi2o2se材料。

54.附图3为二维bi2o2x材料的导通原理示意图,如附图3所示,衬底310的表面沉积二维bi2o2x材料311,衬底的材料例如可以为sio2/si,在二维bi2o2x材料311局部区域形成一个垂直方向的电场。纳米尺度下二维bi2o2x材料311具有独特的平面外方向电学性质,即在垂直方向的电场作用下,二维bi2o2x材料311表面会形成沿电场方向的纳米尺度的山丘状结构312,这些独特的纳米尺度原子结构的变化会使得该区域的电子的能带结构发生巨大的弯曲,从而实现了纳米导电通道,使得原本绝缘的二维bi2o2x材料311在面外沿着电场方向的局部区域导通,从而实现了很好的阻变行为。随着电场的撤去,这些形成的山丘状结构312会迅速恢复,从而恢复到初始态。二维bi2o2x材料311的这一导通行为与电场方向无关,类似于ots器件,可以实现很好的双向导通特性。并且相比于ots,由于二维材料自身的特点,其可以做到几个原子层的厚度,因此对于器件来说,可以很好地降低其深宽比,因而有利于器件的高密度。另外二维bi2o2x材料311材料自身具有绝缘特性,当电场强度高于某一阈值的时候,即形成了山丘状的原子结构的时候,才会形成导通通路。因此在关态的时候,这种材

料的选通层将具有更低的漏电流。仅仅通过原子层级别的调控,就可以实现对器件性能的有效调控。除了电子参与导电外,氧空位以及x(s、se或te)空位在电场作用的移动以及焦耳热的产生之间的动态平衡,共同贡献了开态下选通层的导通过程,因此这种选通层具有更好的调控自由度。

55.在一些实施例中,所述选通层的阈值电压小于4v,示例性的,例如3.5v、2.5v、1.5v。目前的ots选通层依据电子在charge trap(电荷陷阱)间的跃迁实现开态电流,但是由于载流子单一并且trap(陷阱)密度的限制,使得一般开态电流过低,从而难以提高较高的驱动电流。对于目前的ots选通层其阈值电压较高,通常都高于4v,因此对外围电路的选择和设计也带来的很大的麻烦,除此之外,高的开启电压也带来了巨大的浪涌电流的影响,从而使得我们对器件的操作变得不可控。本方案采用二维的bi2o2x材料作为选通层,可以在较低的阈值电压实现稳定的开/关性能,增加了器件的设计自由度。

56.在一些实施例中,所述选通层的厚度小于10nm,示例性的,例如7nm、4nm、2nm。常规的ots选通层需要保证一定的厚度情况下,才能达到漏电低的需求,否则器件的漏电将会增大,从而不仅带来误操作的问题,还使得器件的功耗大幅度增加。同时,因为深宽比的限制,使得基于ots选通层的1s1r的存储器的尺寸将很难继续降低,否则将给工艺带来巨大的挑战。本方案采用二维的bi2o2x材料作为选通层,由于二维材料自身的特点,其可以做到几个原子层的厚度,因此对于器件来说,可以很好地降低其深宽比,因而有利于器件的高密度。同时可以仅仅通过原子层级别的调控,就可以实现对器件性能的有效调控。

57.在一些实施例中,所述bi2o2x材料包括氧空位和x(x选自s、se、te中的至少一种)空位。示例性的,所述氧空位的浓度大于0.02小于0.2,所述x空位的浓度大于0.01小于0.1。氧空位和x空位的浓度太高,过高的缺陷会导致二维bi2o2x材料的性能下降,氧空位和x空位的浓度太低则不利于改善二维bi2o2x材料平面外方向电学性质。原本绝缘的二维bi2o2x材料在面外沿着电场方向的局部区域导通,除了电子参与导电外,氧空位以及se空位在电场作用的移动以及焦耳热的产生之间的动态平衡,共同贡献了开态下选通层的导通过程,因此这种选通层具有更好的调控自由度。在实际操作中,可以通过氧空位和x空位来调节选通层阈值电压,开关比,电导率等参数。

58.在一些实施例中,如附图2所示,所述存储单元213包括沿第三方向依次堆叠分布的第一电极221、存储层222和第二电极223,其中,所述存储层222包括相变存储材料或阻变存储材料。所述第一电极221与所述第二电极的材料包括金属材料或含碳材料,所述金属材料包括但不限于钨或钛,所述含碳材料包括但不限于无定型碳、碳纳米管或石墨烯等。在一些实施例中,所述第一电极221与所述第二电极的厚度可以为10-50nm,示例性的,例如12nm、18nm等。所述第一电极221与所述第二电极223分别与所述选通层212与所述第二导电线211连接,选通层212根据第一导电线210和第二导电线211上的电压信号,驱动存储层完成数据存储或擦除。所述相变存储材料包括基于硫属元素化物的合金(硫属元素化物玻璃),例如gst(ge-sb-te)合金,或者包括任何其他适当的相变材料。所述阻变存储材料包括但不限于hfox、alox以及taox等,或者包括任何其他适当的阻变材料。

59.在一些实施例中,如附图4所示,所述存储器包括:多个存储单元213,所述多个存储单元213位于同一所述选通层212上。传统的ots选通层是与存储单元一一对应,每一选通层驱动一个存储单元的数据存储或擦除。在制备ots选通层时,需要先形成ots选通材料层,

再额外通过刻蚀工艺,形成单一的ots选通层,一方面刻蚀工艺增加成本且会对器件带来污染或其他损伤,另一方面相邻的ots选通层距离过近会造成不必要的串扰。本公开实施例采用二维的bi2o2x材料作为选通层,利用其平面外方向的单极性阻变行为实现选通层的功能,可以一步形成选通层,不需要额外刻蚀工艺;且具有独特的平面外方向电学性质,即可在局部存在垂直电场的区域实现导通,其他区域仍然保持绝缘状态,一个二维的bi2o2x选通层平面可以在竖直方向上驱动多个存储单元,增加了器件的集成度。

60.在一些实施例中,所述存储器还包括:隔离结构(图中未示出),所述隔离结构位于相邻的存储单元之间,用于电隔离相邻的所述存储单元。所述隔离结构包括但不限于氧化硅,氮氧化硅,氮化硅中一种或者其组合。

61.本公开实施例还提供了一种选通器的制备方法,所述制备方法包括:形成选通层,所述选通层包括二维bi2o2x材料,所述x选自s、se、te中的至少一种。所述选通层的形成方法包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

62.本公开实施例还提供了一种存储器的制备方法,图5为本发明实施例提供的存储器的制备方法的流程示意图。如图5所示,所述方法包括:

63.步骤501、形成第一导电线材料层,所述第一导电线材料层用于形成沿第一方向延伸的第一导电线;

64.步骤502、在所述第一导电线材料层上形成沿第三方向叠置的选通材料层和存储单元材料层,所述选通材料层包括二维bi2o2x材料,所述x选自s、se、te中的至少一种,所述选通材料层和存储单元材料层用于形成选通层和存储单元;

65.步骤503、形成位于所述存储单元上的沿第二方向延伸的第二导电线;其中,所述第一方向与所述第二方向相交,所述第三方向垂直于所述第一方向与所述第二方向。

66.在一些实施例中,所述选通层包括二维bi2o2se材料。

67.下面,结合图6a至6f中存储器在制备过程中的结构示意图,对本发明实施例提供的存储器及其制备方法再作进一步详细的说明。

68.所述方法开始于步骤501,如图6a所示,形成第一导电线材料层210’,所述第一导电线材料层210’用于形成沿第一方向延伸的第一导电线210。

69.在实际操作中,可以首先提供衬底310,衬底位于工艺执行面的下方,从而为工艺的进行提供支撑作用。这里,所述衬底可以为半导体衬底,并且可以包括至少一个单质半导体材料(例如为硅(si)衬底、锗(ge)衬底)、至少一个iii-v化合物半导体材料、至少一个ii-vi化合物半导体材料、至少一个有机半导体材料或者在本领域已知的其他半导体材料。

70.而后在所述衬底310上形成第一导电线材料层210’,所述第一导电线的材料可以包括导电材料,所述导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。

71.接下来,执行步骤502,参见附图6b-6d,在所述第一导电线材料层210’上形成沿第三方向叠置的选通材料层212’和存储单元材料层213’,所述选通材料层212’包括二维bi2o2x材料,所述x选自s、se、te中的至少一种,例如包括但不限于二维bi2o2se材料,所述选通材料层212’和存储单元材料层213’用于形成选通层212和存储单元213。

72.具体的,首先,参见附图6b,在所述第一导电线材料层210’上形成选通材料层

212’,在实际操作中,选通材料层212’的形成工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

73.在一些实施例中,形成选通材料层之后,还包括:将所述选通材料层在真空或还原性气氛下退火。所述还原性气氛例如可以为h2。通过采用真空或还原性气氛下退火,提高二维bi2o2x材料的氧空位和x(x选自s、se、te中的至少一种)空位浓度。原本绝缘的二维bi2o2x材料在面外沿着电场方向的局部区域导通,除了电子参与导电外,氧空位以及x空位在电场作用的移动以及焦耳热的产生之间的动态平衡,共同贡献了开态下选通层的导通过程,因此这种选通层具有更好的调控自由度。在实际操作中,可以通过氧空位和x空位来调节选通层阈值电压,开关比,电导率等参数。具体的,所述氧空位的浓度大于0.02小于0.2,所述x空位的浓度大于0.01小于0.1。氧空位和x空位的浓度太高,过高的缺陷会导致二维bi2o2x材料的性能下降,氧空位和x空位的浓度的浓度太低则不利于改善二维bi2o2x材料平面外方向电学性质。

74.接着,参见附图6c,在选通材料层212’上形成存储单元材料层213’。在一些实施例中,所述存储单元材料层213’包括沿第三方向依次堆叠分布的第一电极材料层221’、存储材料层222’和第二电极材料层223’,其中,所述存储材料层222’包括相变存储材料或阻变存储材料。所述第一电极材料层221’、存储材料层222’和第二电极材料层223’分别用于形成所述第一电极层221、存储层222和第二电极层223。

75.所述第一电极材料层221’与所述第二电极材料层223’的材料包括金属材料或含碳材料,所述金属材料包括但不限于钨或钛,所述含碳材料包括但不限于无定型碳、碳纳米管或石墨烯等。在一些实施例中,所述第一电极材料层221’与所述第二电极材料层223’的厚度可以为10-50nm,示例性的,例如12nm、18nm等。

76.所述相变存储材料包括基于硫属元素化物的合金(硫属元素化物玻璃),例如gst(ge-sb-te)合金,或者包括任何其他适当的相变材料。所述阻变存储材料包括但不限于hfox、alox以及taox等,或者包括任何其他适当的阻变材料。

77.所述第一电极221与所述第二电极223分别与所述选通层212与所述第二导电线211连接,选通层根据第一导电线210和第二导电线211上的电压信号,驱动存储层完成数据存储或擦除。

78.接下来,如附图6d所示,沿第一方向刻蚀所述存储单元材料层213’、所述选通材料层212’和所述第一电极材料层210’,所述第一电极材料层210’成为沿第一方向延伸的第一导电线211,所述选通材料层212’成为选通层212,所述存储单元材料层213’成为存储单元结构体213”。

79.最后,执行步骤503,如附图6e和附图6f所示,形成位于所述存储单元213上的沿第二方向延伸的第二导电线211;其中,所述第一方向与所述第二方向相交,所述第三方向垂直于所述第一方向与所述第二方向。

80.具体的,首先,如附图6e所示,在所述存储单元结构体213”上形成沿第二方向延伸的第二导电线材料层211’。

81.所述第二导电线材料层211’的材料可以包括导电材料,所述导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。

82.接着,沿第二方向刻蚀所述第二导电线材料层211’和所述存储单元结构体213”,

所述第二导电线材料层211’成为沿第二方向延伸的第二导电线211,所述存储单元结构体213”成为存储单元213。具体的,第一电极材料层221’、存储材料层222’和第二电极材料层223’分别成为第一电极层221、存储层222和第二电极层223。

83.在实际操作中,在形成第二导电线材料层211’之前,还可以采用填充材料填充所述存储单元结构体213”之间的空隙。

84.在一些实施例中,如附图6f所示,所述选通材料层212’和存储单元材料层213’用于形成选通层212和存储单元213,包括:所述选通材料层212’和存储单元材料层213’用于形成选通层212和多个存储单元213,所述多个存储单元213位于同一所述选通层212上。在实际操作中,如附图6e和6f所示,在所述存储单元结构体213”上形成沿第二方向延伸的第二导电线材料层211’,沿第二方向刻蚀所述第二导电线材料层211’和所述存储单元结构体213”。此时刻蚀工艺不需要贯穿选通层212,例如可以以选通层212的表面作为刻蚀停止层或刻蚀阻挡层。传统的ots选通层是与存储单元一一对应,每一选通层驱动一个存储单元的数据存储或擦除。在制备ots选通层时,需要先形成ots选通材料层,再额外通过刻蚀工艺,形成单一的ots选通层,一方面刻蚀工艺增加成本且会对器件带来污染或其他损伤,另一方面相邻的ots选通层距离过近会造成不必要的串扰。通过采用二维的bi2o2se材料作为选通层,利用其平面外方向的单极性阻变行为实现选通层的功能,可以一步形成选通层,不需要额外刻蚀工艺;且具有独特的平面外方向电学性质,即可在局部存在垂直电场的区域实现导通,其他区域仍然保持绝缘状态,一个二维的bi2o2se选通层平面可以在竖直方向上驱动多个存储单元,增加了器件的集成度。

85.在一些实施例中,所述方法还包括:形成隔离结构(图中未示出),所述隔离结构位于相邻的存储单元213之间,用于电隔离相邻的所述存储单元213。所述隔离结构包括但不限于氧化硅,氮氧化硅,氮化硅中一种或者其组合。

86.在一些实施例中,所述选通层的阈值电压小于4v,示例性的,例如3.5v、2.5v、1.5v。目前的ots选通层依据电子在charge trap(电荷陷阱)间的跃迁实现开态电流,但是由于载流子单一并且trap(陷阱)密度的限制,使得一般开态电流过低,从而难以提高较高的驱动电流。对于目前的ots选通层其阈值电压较高,通常都高于4v,因此对外围电路的选择和设计也带来的很大的麻烦,除此之外,高的开启电压也带来了巨大的浪涌电流的影响,从而使得我们对器件的操作变得不可控。本方案采用二维的bi2o2x材料作为选通层,可以在较低的阈值电压实现稳定的开/关性能,增加了器件的设计自由度。

87.在一些实施例中,所述选通层的厚度小于10nm,示例性的,例如7nm、4nm、2nm。常规的ots选通层需要保证一定的厚度情况下,才能达到漏电低的需求,否则器件的漏电将会增大,从而不仅带来误操作的问题,还使得器件的功耗大幅度增加。同时,因为深宽比的限制,使得基于ots选通层的1s1r的存储器的尺寸将很难继续降低,否则将给工艺带来巨大的挑战。本方案采用二维的bi2o2x材料作为选通层,由于二维材料自身的特点,其可以做到几个原子层的厚度,因此对于器件来说,可以很好地降低其深宽比,因而有利于器件的高密度。同时可以仅仅通过原子层级别的调控,就可以实现对器件性能的有效调控。

88.综上所述,本发明实施例采用二维bi2o2x材料作为选通层,利用其平面外方向的单极性阻变行为实现选通层的功能,可以实现很好的双向导通特性。由于二维材料的特性,可以很好地降低器件深宽比,因而有利于器件的高密度。另外二维的bi2o2x材料自身具有绝缘

特性,在关态时具有较低的漏电流。同时,可通过调节材料中的氧空位以及x空位控制器件性能,该选通层有更好的调控自由度。

89.需要说明的是,本发明提供的选通器、选通器的制备方法、应用该选通器的存储器和存储器的制备方法属于同一构思;本公开实施例提供的选通器及选通器的制备方法和存储器及存储器的制备方法可以应用于任何包括该结构的集成电路中。各实施例所记载的技术方案中各技术特征之间,在不冲突的情况下,可以任意组合。本领域技术人员能够对上述形成方法步骤顺序进行变换而并不离开本公开的保护范围,本公开实施例中的各步骤在不冲突的情况下,部分步骤可以同时执行,也可以调用先后顺序执行。

90.以上所述,仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1