LED外延结构及其制备方法、LED芯片及其制备方法与流程

led外延结构及其制备方法、led芯片及其制备方法

技术领域

1.本发明涉及半导体技术领域,特别涉及一种led外延结构及其制备方法、led芯片及其制备方法。

背景技术:

2.发光二极管(led,light emitting diode)是一种半导体固体发光器件,其利用半导体pn结作为发光材料,可以直接将电转换为光。由于其具有结构简单、重量轻、无污染等优点,已广泛应用于汽车照明、装饰照明、军用照明、通信、打印等多个领域,被称为环保、节能的绿色照明光源,蕴藏了巨大的商机。

3.以砷化镓(gaas)为代表的

ⅲ‑ⅴ

族化合物半导体由于具有发光效率高、电子饱和漂移速度高、化学性质稳定等特点,在高亮发光二极管、激光器等光电子领域有着巨大的应用潜力,因此被广泛应用于发光二极管的外延生长。

4.合理的调控led外延生长对提高led发光效率起着重要的作用。关于发光效率的提升,改善方法很多,例如:生长gap材料作为窗口层,以提高电流扩展能力。但是,由于gap和衬底之间的晶格存在失配,在生长时会产生缺陷影响结晶质量。具体的,当外延层与衬底之间存在着大的晶格失配,衬底的表面的自由能小于外延层的表面与界面能之和的时候,衬底与外延层之间的键能不是很高,在衬底的表面不能形成浸润层,进而造成了三维岛的形成,继续生长后三维岛不断的扩大变为柱状岛,最后形成表面粗糙的连续膜。这些问题严重制约着led芯片性能的提升。

技术实现要素:

5.鉴于上述问题,本发明的目的在于提供一种led外延结构及其制备方法、led芯片及其制备方法,在p型过渡层与p型窗口层之间引入中间层,实现p型过渡层与p型窗口层之间的晶格常数逐渐改变,以减少突变式结构生长过程中的缺陷,改善晶体质量。

6.本发明的第一方面提供一种led外延结构,包括:

7.衬底;

8.位于所述衬底上的n型半导体层;

9.位于所述n型半导体层上的多量子阱层;以及

10.位于所述多量子阱层上的p型半导体层;

11.其中,所述p型半导体层从下到上依次包括p型过渡层、p型窗口层以及位于二者之间的中间层,所述中间层的晶格常数与所述p型窗口层和所述p型过渡层的晶格常数相匹配。

12.优选地,所述中间层为多层ga组分渐变的ga

x

in

1-x

p层,且0.5≤x≤1。

13.优选地,多层所述中间层的厚度从所述p型过渡层到所述p型窗口层的方向递减。

14.优选地,从所述p型过渡层到所述p型窗口层的方向上,多层所述中间层中每层的ga组分x渐变增加。

15.优选地,从所述p型过渡层到所述p型窗口层的方向,所述中间层依次包括第一中间层、第二中间层、第三中间层、第四中间层以及第五中间层。

16.优选地,所述第一中间层中ga的组分为x=0.5;

17.所述第二中间层中ga的组分为x=0.65;

18.所述第三中间层中ga的组分为x=0.75;

19.所述第四中间层中ga的组分为x=0.85;

20.所述第五中间层中ga的组分为x=0.95。

21.优选地,所述第一中间层的厚度为30~40nm;

22.所述第二中间层的厚度为20~30nm;

23.所述第三中间层的厚度为10~20nm;

24.所述第四中间层的厚度为10~20nm;

25.所述第五中间层的厚度为10~15nm。

26.优选地,所述p型窗口层为层叠结构,包括层叠的第一p型窗口结构层以及位于所述第一p型窗口结构层上的第二p型窗口结构层,其中,所述第一p型窗口结构层经过退火处理。

27.优选地,生长所述第一p型窗口结构层以及所述第二p型窗口结构层的v族源与ⅲ族源的摩尔量之比不同。

28.优选地,生长所述第一p型窗口结构层的v族源与ⅲ族源的摩尔量之比为40~50。

29.优选地,生长所述第二p型窗口结构层的v族源与ⅲ族源的摩尔量之比为50~80。

30.优选地,生长所述第一p型窗口结构层以及所述第二p型窗口结构层的温度不同。

31.优选地,生长所述第一p型窗口结构层的温度为500~600℃。

32.优选地,生长所述第二p型窗口结构层的温度为800~850℃。

33.优选地,所述第一p型窗口结构层的厚度为20~50nm。

34.优选地,所述第一p型窗口结构层的退火温度为950~1000℃。

35.优选地,所述p型半导体层还包括:

36.p型波导层,位于所述多量子阱层上;

37.p型限制层,位于所述p型波导层上;

38.所述p型过渡层、所述中间层和所述p型窗口层位于所述p型限制层上;

39.p型欧姆接触层,位于所述p型窗口层上;

40.所述n型半导体层包括:

41.n型欧姆接触层,位于所述衬底上;

42.n型缓冲层,位于所述n型欧姆接触层上;

43.n型窗口层,位于所述n型缓冲上;

44.n型限制层,位于所述n型窗口层上;以及

45.n型波导层,位于所述n型限制层上。

46.优选地,所述外延结构还包括缓冲层以及腐蚀截止层,所述缓冲层和所述腐蚀截止层位于所述衬底与所述n型半导体层之间。

47.本方面的第二方面提供一种led外延结构的制备方法,包括:

48.在衬底上依次形成n型半导体层、多量子阱层以及p型半导体层;

49.其中,形成所述p型半导体层的方法包括:依次形成p型过渡层、中间层以及p型窗口层;

50.所述中间层的晶格常数与所述p型窗口层和所述p型过渡层的晶格常数相匹配。

51.优选地,所述中间层为多层ga组分渐变的ga

x

in

1-x

p层,且0.5≤x≤1。

52.优选地,多层所述中间层的厚度从所述p型过渡层到所述p型窗口层的方向递减。

53.优选地,从所述p型过渡层到所述p型窗口层的方向上,多层所述中间层中每层的ga组分x渐变增加。

54.优选地,从所述p型过渡层到所述p型窗口层的方向,所述中间层依次包括第一中间层、第二中间层、第三中间层、第四中间层以及第五中间层。

55.优选地,所述第一中间层中ga的组分为x=0.5;

56.所述第二中间层中ga的组分为x=0.65;

57.所述第三中间层中ga的组分为x=0.75;

58.所述第四中间层中ga的组分为x=0.85;

59.所述第五中间层中ga的组分为x=0.95。

60.优选地,所述第一中间层的厚度为30~40nm;

61.所述第二中间层的厚度为20~30nm;

62.所述第三中间层的厚度为10~20nm;

63.所述第四中间层的厚度为10~20nm;

64.所述第五中间层的厚度为10~15nm。

65.优选地,所述p型窗口层为层叠结构,形成所述p型窗口层方法包括:

66.形成第一p型窗口结构层;

67.对所述第一p型窗口结构层进行退火,以减少所述第一p型窗口结构层中的缺陷;

68.在经过退火的所述第一p型窗口结构层上形成第二p型窗口结构层,以得到所述p型窗口层。

69.优选地,生长所述第一p型窗口结构层以及所述第二p型窗口结构层的v族源与ⅲ族源的摩尔量之比不同。

70.优选地,形成所述第一p型窗口结构层的v族源和与ⅲ族源的摩尔量之比40~50。

71.优选地,形成所述第二p型窗口结构层的v族源和与ⅲ族源的摩尔量之比50~80。

72.优选地,生长所述第一p型窗口结构层以及所述第二p型窗口结构层的温度不同。

73.优选地,形成所述第一p型窗口结构层的温度为500~600℃。

74.优选地,形成所述第二p型窗口结构层的温度为800~850℃。

75.优选地,所述第一p型窗口结构层的厚度为20~50nm。

76.优选地,所述第一p型窗口结构层在氢气中的退火温度为950~1000℃。

77.优选地,所述第一p型窗口结构层在氢气中的退火时,关闭形成所述第一p型窗口结构层的气源。

78.优选地,形成所述p型半导体层的方法包括:依次在所述多量子阱层上形成p型波导层,p型限制层,所述p型过渡层,所述中间层,所述p型窗口层以及p型欧姆接触层;

79.形成所述n型半导体层的方法包括:在所述衬底上依次形成n型欧姆接触层,n型缓冲层,n型窗口层,n型限制层以及n型波导层。

80.优选地,在形成所述n型半导体层之前还包括:在所述衬底上形成缓冲层以及腐蚀截止层。

81.本发明的第三方面提供一种led芯片,包括:

82.上述的led外延结构;

83.与n型半导体层电连接的第二电极;以及

84.与p型半导体层电连接的第一电极。

85.优选地,所述led芯片为正装led芯片、倒装led芯片、垂直led芯片中的一种。

86.本发明的第四方面提供一种led芯片的制备方法,包括:

87.采用上述方法形成led外延结构;

88.形成与所述n型半导体层电连接的第二电极;以及

89.形成与所述p型半导体层电连接的第一电极。

90.优选地,所述led芯片为正装led芯片、倒装led芯片、垂直led芯片中的一种。

91.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,在p型过渡层与p型窗口层之间引入中间层,中间层为多层渐变式结构,实现p型过渡层与p型窗口层之间的晶格常数逐渐改变,以减少突变式结构生长过程中的缺陷,改善晶体质量;提高高温条件下生长p型窗口层薄膜的结晶质量并且改善均匀性,进而提高整个led外延层的晶体质量;同时,晶体缺陷的减少使得载流子辐射性复合几率增加而提高了亮度,最终提高led芯片的发光效率。

92.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,从所述p型过渡层到所述p型窗口层的方向上,所述中间层中ga的组分逐渐提高,in的组分逐渐降低,使所述中间层的晶格常数逐渐从大到小过渡到与p型窗口层接近的晶格常数,以实现从所述p型过渡层到所述p型窗口层的过渡。

93.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,靠近所述p型过渡层的中间层的厚度较厚,可以有效调节外延层的晶格常数,避免晶格失配的产生;靠近所述p型窗口层的中间层的厚度较薄,有利于外延层的晶格向所述p型窗口层过渡。

94.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,所述p型窗口层为层叠结构,且经过高温氢气退火处理,其中每层的生长条件不同,通过改变p型窗口层的生长条件以及高温氢气退火两步法来优化p型窗口层的生长方式。

95.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,第一p型窗口结构层的厚度较薄,经由高温氢气退火处理,所述第一p型窗口结构层中含有缺陷的部分减少,晶格质量较高的部分得以保存,进而为第二p型窗口结构层的生长提供良好的基础。

96.本发明实施例提供的led外延结构及其制备方法、led芯片及其制备方法中,第一p型窗口结构层以及第二p型窗口结构层的v/iii比(v族源与ⅲ族源的摩尔量之比)不同,经由改变生长所述第一p型窗口结构层以及第二p型窗口结构层的v/iii比(v族源与ⅲ族源的摩尔量之比)和温度,使晶体的横向以及纵向生长速度发生改变,进而使得晶体的生长方式由岛状生长转变为层状生长,以最终获得完整光滑的表面。

附图说明

97.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

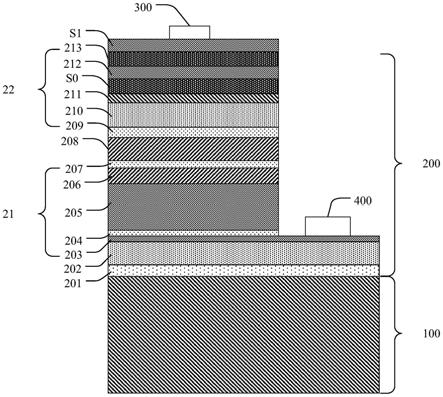

98.图1示出了本发明第一实施例的led芯片的截面图;

99.图2示出了本发明第一实施例的led芯片的制备方法流程图;

100.图3示出了本发明第一实施例的led芯片制备过程的结构示意图;

101.图4示出了本发明第一实施例的中间层的结构示意图;

102.图5示出了本发明第二实施例的led芯片的示意图;

103.图6示出了本发明第二实施例的led芯片的p型窗口层制备方法的流程图;

104.图7示出了本发明第二实施例的led芯片的p型窗口层的制备过程示意图;

105.图8示出了本发明第三实施例的led芯片的示意图;

106.图9示出了本发明第四实施例的led芯片的示意图。

具体实施方式

107.以下将参照附图更详细地描述本发明的各种实施例。在各个附图中,相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。

108.以下将参照附图更详细地描述本发明。在各个附图中,相同的元件采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在一幅图中描述经过数个步骤后获得的半导体结构。

109.应当理解,在描述器件的结构时,当将一层、一个区域称为位于另一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或区域。并且,如果将器件翻转,该一层、一个区域将位于另一层、另一区域“下面”或“下方”。

110.如果为了描述直接位于另一层、另一区域上面的情形,本文将采用“直接在

……

上面”或“在

……

上面并与之邻接”的表述方式。

111.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

112.图1示出了本发明第一实施例的led芯片的截面图;本实施例中,所述led芯片为正装led芯片,如图1所示,所述led芯片包括:衬底100、位于所述衬底100上的外延层200、第一电极300以及第二电极400。

113.所述外延层200沿垂直于所述衬底100的方向从下至上依次包括缓冲层201、腐蚀截止层202、n型半导体层21、多量子阱层208以及p型半导体层22。

114.其中,所述n型半导体层21沿垂直于所述衬底100的方向从下至上依次包括n型欧姆接触层203,n型缓冲层204,n型窗口层205,n型限制层206以及n型波导层207;p型半导体层22沿垂直于所述衬底100的方向从下至上依次包括p型波导层209,p型限制层210,p型过渡层211,中间层s0,p型窗口层212以及p型欧姆接触层213。

115.所述led芯片还包括透明导电层s1,所述透明导电层s1位于所述p型欧姆接触层213上,所述第一电极300通过所述透明导电层s1与p型欧姆接触层213连接,所述第二电极400位于所述n型欧姆接触层203暴露的区域。

116.本实施例中,所述衬底100为

ⅲ‑ⅴ

族化合物中的一种,例如为gaas,但不限于此。

所述缓冲层201的材料例如为掺杂si的gaas,但不限于此;所述腐蚀截止层202的材料例如为掺杂si的掺杂gainp,但不限于此。所述n型欧姆接触层203的材料例如为掺杂si的gaas,但不限于此;所述n型缓冲层204的材料例如为掺杂si的gainp,但不限于此;所述n型窗口层205的材料例如为掺杂si的(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,但不限于此;所述n型限制层206的材料例如为掺杂si的alinp,但不限于此;n型波导层207的材料例如为非掺(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,但不限于此;多量子阱层208的材料例如为gainp/(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,但不限于此;p型波导层209的材料例如为非掺(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,但不限于此;p型限制层210的材料例如为掺杂mg的alinp,但不限于此;所述p型过渡层211的材料例如为掺杂mg的(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,但不限于此;所述p型窗口层212的材料例如为掺杂mg的gap,但不限于此;所述p型欧姆接触层213的材料例如为掺杂c的gap,但不限于此。

117.所述透明导电层s1由透明导电性氧化物形成,其材质包括铟in、sn、al、zn及镓ga等的元素的氧化物中的任一种形成。

118.所述中间层s0为多层渐变的ga

x

in

1-x

p层,且ga组分为0.5≤x≤1,以实现从所述p型过渡层211到所述p型窗口层212的过渡。

119.所述中间层s0的ga组分和厚度渐变,具体的,从所述p型过渡层211到所述p型窗口层212的方向上,每层的ga组分x渐变增加,即每一中间层s0中ga的组分逐渐提高,in的组分逐渐降低,使ga

x

in

1-x

p的晶格常数逐渐从大到小过渡到与p型窗口层212的gap接近的晶格常数,以实现从所述p型过渡层211的algainp到所述p型窗口层212的gap的过渡。并且,从所述p型过渡层211到所述p型窗口层212的方向上,每一中间层s0的厚度逐渐降低,靠近所述p型过渡层211的中间层s0的厚度较厚,可以有效调节外延层200的晶格常数,避免晶格失配的产生;靠近所述p型窗口层212的中间层s0的厚度较薄,有利于外延层200的晶格向所述p型窗口层212过渡。

120.本发明实施例提供的led外延结构及led芯片中,在p型过渡层与p型窗口层之间引入中间层,中间层为多层渐变式结构,实现p型过渡层与p型窗口层之间的晶格常数逐渐改变,以减少突变式结构生长过程中的缺陷,改善晶体质量;同时,晶体缺陷的减少使得载流子辐射性复合几率增加而提高了亮度,最终提高led芯片的发光效率。

121.需要说明的是,以上对外延层中各结构层的材料和组分的描述仅仅是为了说明的目的,而并非为了限制本发明的范围,本领域技术人员可以做出的修改和替代应该属于本发明的范围之内。

122.图2示出本发明第一实施例的led芯片的制备方法流程图。本发明实施例的制备方法用于制备图1所示的led芯片。

123.图3a-图3c示出本发明第一实施例的led芯片制备过程的结构示意图。以下将结合图3a-图3c对本发明第一实施例的led芯片的制备方法进行说明。

124.如图3a所示,步骤s10中,在衬底上依次形成缓冲层、腐蚀截止层、n型半导体层、多量子阱层以及p型半导体层。步骤s10也称为外延层200的制备。例如采用金属有机物化学气相沉积、激光辅助分子束外延、激光溅射或氢化物气相外延等外延生长工艺在衬底100的表面形成外延层200,优选地,采用金属有机物化学气相沉积形成外延层200。

125.其中,所述n型半导体层21沿垂直于所述衬底100的方向从下至上依次包括n型欧

姆接触层203,n型缓冲层204,n型窗口层205,n型限制层206以及n型波导层207;p型半导体层22沿垂直于所述衬底100的方向从下至上依次包括p型波导层209,p型限制层210,p型过渡层211,中间层s0,p型窗口层212,以及p型欧姆接触层213。

126.在一个具体的实施例中,所述衬底100的材料为gaas。所述缓冲层201的材料为gaas,生长温度为700℃~750℃(例如为700℃),厚度为200nm~300nm(例如为200nm)。所述腐蚀截止层202的材料为gainp,生长温度为700℃~750℃(例如为700℃),厚度为10nm~20nm(例如为20nm)。

127.所述n型欧姆接触层203的材料为gaas,生长温度为700℃~750℃(例如为700℃),厚度为5nm~10nm(例如为10nm);所述n型缓冲层204的材料为gainp,生长温度为700℃~750℃(例如为700℃),厚度为15nm~25nm(例如为15nm);所述n型窗口层205的材料为(al

0.7

ga

0.3

)

0.5

in

0.5

p,生长温度为770℃,厚度为1500~2000nm(例如为2000nm);所述n型限制层206的材料为alinp,生长温度是770℃,厚度为1200nm~1500nm(例如为1500nm);所述n型波导层207的材料为非掺(al

0.65

ga

0.35

)

0.5

in

0.5

p,生长温度是770℃,厚度为60nm~80nm(例如为80nm)。

128.所述多量子阱层208包括6~12(例如12)个周期的多量子阱,所述多量子阱层208的材料为gainp/(al

x

ga

1-x

)

0.5

in

0.5

p,且al组分为0.5≤x≤1,生长温度为710℃。

129.所述p型波导层209的材料为非掺(al

0.65

ga

0.35

)

0.5

in

0.5

p,生长温度是770℃,厚度为60nm~80nm(例如为80nm);所述p型限制层210的材料为掺杂mg的alinp,生长温度是770℃,厚度为1200nm~1500nm(例如为1500nm);所述p型过渡层211的材料为掺杂mg的algainp,生长温度是770℃,厚度为5nm~10nm(例如为10nm);所述p型窗口层212的材料为掺杂mg的gap;所述p型欧姆接触层213的材料为高掺c的gap,生长温度为710℃,厚度为150nm。

130.其中,所述中间层s0的材料为ga

x

in

1-x

p,且ga组分为0.5≤x≤1,中间层s0的制备方法为:在所述p型过渡层211上生长ga

x

in

1-x

p层,在生长的过程中,不断提高ga组分并降低in组分,使ga

x

in

1-x

p的晶格逐渐从大到小过渡到与gap接近的晶格常数,进而实现从algalnp过渡到gap。

131.图4示出了本发明第一实施例的中间层的结构示意图。如图4所示,在一个具体的实施例中,所述中间层s0包括依次形成于所述p型过渡层211上的第一中间层s01、第二中间层s02、第三中间层s03、第四中间层s04以及第五中间层s05。其中,第一中间层s01中,ga

x

in

1-x

p中ga的组分为x=0.5,且第一中间层s01的厚度为30~40nm(例如为40nm);第二中间层s02中,ga

x

in

1-x

p中ga的组分为x=0.65,且第二中间层s02的厚度为20~30nm(例如为30nm);第三中间层s03中,ga

x

in

1-x

p中ga的组分为x=0.75,且第三中间层s03的厚度为10~20nm(例如为20nm);第四中间层s04中,ga

x

in

1-x

p中ga的组分为x=0.85,且第四中间层s04的厚度为10~20nm(例如为15nm);第五中间层s05中,ga

x

in

1-x

p中ga的组分为x=0.95,且第五中间层s05的厚度为10~15nm(例如为10nm)。

132.需要说明的是以上对中间层s0的层数、中间层的组分以及厚度的描述仅仅是为了说明的目的,而并非为了限制本发明的范围,本领域技术人员可以做出的修改和替代应该属于本发明的范围之内。

133.参照图3b,s20中,在p型半导体层上形成透明导电层s1,即在所述p型半导体层22的p型接触层213上形成透明导电层s1,用于所述p型接触层213与所述第一电极300的连接。

134.透明导电层s1由透明导电性氧化物形成,其材质包括铟in、sn、al、zn及镓ga等的元素的氧化物中的任一种形成。

135.如图3c所示,步骤s30中,对从所述透明导电层s1到所述n型欧姆接触层203的表面进行刻蚀,使n型欧姆接触层203的表面暴露。

136.如图1所述,步骤s40中,在所述透明导电层s1上形成第一电极,在所述n型欧姆接触层203暴露的至少一个区域形成第二电极。

137.图5示出了本发明第二实施例的led芯片的示意图,与第一实施例不同的是,本实施例中,所述p型窗口层212为层叠结构,包括层叠的第一p型窗口结构层2121以及第二p型窗口结构层2122;生长所述第一p型窗口结构层2121以及第二p型窗口结构层2122的v族源与ⅲ族源的摩尔量之比和温度不同,以使得所述第一p型窗口结构层2121和所述第二p型窗口结构层2122在横向以及纵向的生长速度不同。通过调整生长所述第一p型窗口结构层2121以及第二p型窗口结构层2122的v族源与ⅲ族源的摩尔量之比和温度,使得gap的生长方式将由岛状生长转变为层状生长,大大改善gap的晶体质量。

138.进一步地,所述第一p型窗口结构层2121经过退火处理,以提高所述第一p型窗口结构层2121的晶体质量。本发明实施例提供的led芯片中,第一p型窗口结构层2121的厚度为20~50nm,较薄的第一p型窗口结构层2121经由高温氢气退火处理,含有缺陷的晶体会减少,晶体质量较高的部分得以保存,进而为第二p型窗口结构层2122的生长提供良好的基础。

139.图6示出本发明第二实施例的led芯片的p型窗口层制备方法的流程图,如图6所示,所述p型窗口层的制备方法包括:

140.s110:形成第一p型窗口结构层;

141.s120:第一p型窗口结构层在h2的气氛中进行退火;

142.s130:在第一p型窗口结构层上形成第二p型窗口结构层。

143.为了改善所述p型窗口层212的生长质量,所述掺杂mg的p型窗口层212的生长方式为两段式生长。

144.图7a-图7c示出本发明第二实施例的led芯片的p型窗口层的制备过程示意图,为了更加清楚地展现p型窗口层的制备过程,该附图中省略了一部分结构层。以下将结合图7a-图7c对本发明第二实施例的led芯片的p型窗口层的制备方法进行说明。

145.参照图7a,步骤s110中,在500~600℃的条件下低温生长一层较薄(厚度例如为20~50nm)的第一p型窗口结构层2121,v/iii比(v族源与ⅲ族源的摩尔量之比)为40~50。本实施例中,v族源与ⅲ族源例如为磷烷和三甲基镓。

146.参照图7b,步骤s120中,所述第一p型窗口结构层2121在h2的气氛中进行退火。具体地,将温度升高至950~1000℃,关闭v族源与ⅲ族源(磷烷和三甲基镓),在h2的气氛中进行退火。此时较薄的第一p型窗口结构层2121中含有缺陷的部分减少,留下晶体质量较高的部分。

147.参照图7c,步骤s130中,将温度控制在800~850℃,v/iii比(v族源与ⅲ族源的摩尔量之比)为50~80,进行高温高速生长,改变晶体的横向和纵向生长速度,使gap的生长方式由岛状生长转变为层状生长,形成p型窗口层212,提高了高温条件下生长gap薄膜的结晶质量并且改善均匀性,大大改善gap的晶体质量,进而提高整个led外延层的结构质量。

148.gap材料的生长温度窗口狭窄,不同的生长温度对其成核影响很大,温度较高时晶体质量较好,表面更接近镜面;温度较低时由动力学控制温度的变化对晶体的生长有很大的影响。为解决应力问题,通过高温退火和生长温度来控制应力的释放,将第一p型窗口结构层2121的生长温度降低,释放应力,然后升温退火、结晶,然后再次升温生长第二p型窗口结构层2122以获得良好的晶体质量。本技术中的退火温度更加易于控制应力释放和控制表面平滑,同时使晶体的质量也能有相应的提高。

149.进一步的,由于

ⅴ

族元素的挥发性比ⅲ族元素的挥发性强,因此外延生长过程通常在高v/iii比的条件下进行,以保证生长表面处于富

ⅴ

族元素的环境,这样才能得到良好形貌的外延层。但是,v/iii增加到一定程度,随着成核岛密度的增加,晶体中的杂质以及缺陷有增加趋势,大大降低了晶体的结晶质量。另外,在v/iii比太小时,成核岛的密度较低,岛与岛合并较快,此时原子没有足够的时间通过吸附和解吸附来调整晶格的排布,初始条件下岛之间容易出现大的倾斜及扭转,螺位错及刃位错均较多。因此,选择合适的

ⅴ

/ⅲ比有助于减少晶体中的杂质和缺陷,同时有效抑制气相寄生反应,对于晶体质量有很大改善,本技术中的

ⅴ

/ⅲ比,可以减少晶体中杂质和缺陷,同时有效抑制气相寄生反应,对于晶体质量有很大改善。

150.本发明第二实施例提供的led外延结构及led芯片中,所述p型窗口层为层叠结构,且经过高温氢气退火处理,其中每层的生长条件不同,通过改变p型窗口层的生长条件以及高温氢气退火两步法来优化p型窗口层的生长方式。

151.本发明第二实施例提供的led外延结构及led芯片中,第一p型窗口结构层的厚度较薄,经由高温氢气退火处理,所述第一p型窗口结构层中含有缺陷的部分减少,晶格质量较高的部分得以保存,进而为第二p型窗口结构层的生长提供良好的基础。

152.本发明第二实施例提供的led芯片中第一p型窗口结构层以及第二p型窗口结构层的

ⅴ

/ⅲ比(v族源与ⅲ族源的摩尔量之比)不同,经由改变生长所述第一p型窗口结构层以及第二p型窗口结构层的

ⅴ

/ⅲ比(v族源与ⅲ族源的摩尔量之比)和温度,使晶体的横向以及纵向生长速度发生改变,进而使得晶体的生长方式由岛状生长转变为层状生长,以最终获得完整光滑的表面。

153.以上实施例均以正装led芯片为例来进行说明,在其他的实施例中,所述led芯片还可以为倒装led芯片以及垂直led芯片,图8示出了本发明第三实施例的led芯片的示意图;图9示出了本发明第四实施例的led芯片的示意图。

154.图8中的led芯片为垂直led芯片,图9中的led芯片为倒装led芯片,其中,倒装led芯片与正装led芯片的电极结构相同,所述第二电极400位于所述n型欧姆接触层203暴露的区域。形成所述第二电极400的过程需要对从所述透明导电层s1到所述n型欧姆接触层203的表面进行刻蚀,使n型欧姆接触层203的表面暴露。

155.当所述led芯片为垂直led芯片时,需要剥离生长衬底,以暴露所述n型半导体层,并在n型半导体层上键合上键合衬底100,作为第二电极(n电极)。

156.可以理解的是,凡是应用本发明实施例的led外延结构的led芯片都在本发明实施例所保护的范围内。

157.依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明

书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1