一种PD-SOI集成电路工艺下的新型ESD防护装置的制作方法

一种pd-soi集成电路工艺下的新型esd防护装置

技术领域

1.本发明涉及半导体技术领域中的集成电路esd防护可靠性的设计,具体为针对一种pd-soi集成电路工艺下的新型esd防护装置。

背景技术:

2.随着集成电路功耗、性能的不断发展,soi(silicon on insolution)技术具有极低的寄生电容,同时提供动态电压调节功能,在低压低功耗、存储器、射频、大规模soc和抗辐照等应用上具有明显优势,在物联网、消费电子、移动互联网和航天等领域具有巨大的实际应用价值。在日益进步soi技术应用过程中,静电可靠性问题是一个巨大的挑战。相较于体硅技术,soi结构在散热困难和热分布不平均方面存在明显的劣势。同时由于采用了全耗尽硅膜、高k金属栅等复杂结构,导致在soi中传统esd防护手段效果快速恶劣,esd防护能力大幅度下滑,静电设计复杂性大大增加。

3.pd-soi(partially depleted soi)相对于(fully depleted soi)fd-soi工艺具有更厚的硅膜,具有有效的源漏注入底面,可以形成可控硅或者类可控硅的单元结构作为esd防护装置。可控硅具有良好的泄放电流能力,但是其也有如下缺陷:其一,维持电压过小,一旦受到esd冲击轻则esd防护装置开启便无法关闭,重则闩锁烧毁;其二,开启电压大,一旦esd防护装置的开启电压超过了被保护单元的损伤电压,被保护单元将在esd防护装置开启之前已经烧毁。在28nm以下的先进制程中,限制开启电压和维持电压的esd设计窗口已经被极大地缩小,传统的方法越来越难以满足先进制程下esd防护的需求。

技术实现要素:

4.针对背景技术中提到的问题,本发明的目的是提供一种pd-soi集成电路工艺下的新型esd防护装置,在pd-soi集成电路工艺下通过适当掺杂和结构设计形成侧边附加结构,该侧边附加结构在与径向垂直的侧向方向上,从而为传统的pnpn可控硅结构提供了额外的嵌入式寄生机构,构成新型esd防护装置。

5.本发明的上述技术目的是通过以下技术方案得以实现的:一种pd-soi集成电路工艺下的新型esd防护装置,包含半导体基底一、半导体基底二、绝缘体介质一、绝缘体介质二、绝缘体上半导体基质一、绝缘体上半导体基质二、绝缘体上半导体基质上的多晶硅一和多晶硅二;所述多晶硅一根据方向不同分为径向多晶硅和侧边多晶硅,径向多晶硅和侧边多晶硅电连接,侧边多晶硅在一侧收窄,宽处与窄处有倒角;所述半导体基底一和半导体基底二可以为硅基底;绝缘体介质一和绝缘体介质二可以为sio2绝缘体,绝缘体上半导体基质一、绝缘体上半导体基质二为有源区,厚度与被保护电路的标准器件硅膜厚度,

6.通过参杂可形成第一半导体类型,所述第一半导体类型可以为绝缘体上半导体基质一、绝缘体上半导体基质二的底掺杂,或为扩散形成的阱区掺;

7.通过参杂可形成第二半导体类型,所述第二半导体类型可以为阱区掺杂;第一半导体类型重掺杂一、第一半导体类型重掺杂二和第一半导体类型重掺杂三与第二半导体类

型重掺杂一、第二半导体类型重参杂二的掺杂浓度远高于第一半导体类型中掺杂和第二半导体类型中掺杂,与金属或者金属硅化物引出形成无肖特基势垒的欧姆接触,同时亦为寄生esd泄放机构的电极。

8.作为优选,所述第一半导体类型重掺杂一、第一半导体类型重掺杂二和第一半导体类型重掺杂三与第二半导体类型重掺杂一、第二半导体类型重参杂二可为多晶硅一的自对准形成。

9.作为优选,所述第一半导体类型重掺杂一、第一半导体类型重掺杂二和第一半导体类型重掺杂三与第二半导体类型重掺杂一、第二半导体类型重参杂二可由多晶硅一图形转移构成;并通过倒角的图形转移,形成第一半导体类型重掺杂三的宽处与窄处的倒角。

10.作为优选,主方向上第一半导体类型重掺杂一、第二半导体类型的掺杂和第一半导体类型中的掺杂构成寄生pnp-bjt一,主方向上第二半导体类型的掺杂、第一半导体类型的掺杂、第一半导体类型重掺杂二构成寄生npn-bjt。

11.作为优选,侧方向上第一半导体类型重掺杂一、第二半导体类型的掺杂、第一半导体类型重掺杂三构成寄生pnp-bjt二;由第一半导体类型重掺杂一和第二半导体类型重掺杂一引出形成阳极电极,第二半导体类型重掺杂一至第一半导体类型重掺杂一的内阻构成寄生电阻一,第二半导体类型重掺杂一至第一半导体类型重掺杂三的内阻构成寄生电阻二。

12.作为优选,第一半导体类型重掺杂二、第二半导体类型重参杂二、第二半导体类型重参杂二引出形成阴极电极,第二半导体类型重参杂二至第一半导体类型重掺杂二的内阻构成寄生电阻二。

13.作为优选,寄生pnp-bjt一、寄生npn-bjt、寄生pnp-bjt二相互嵌套形成pnpn可控硅型esd防护装置。

14.作为优选,寄生pnp-bjt二为侧向方向上形成的寄生器件,电流方向与寄生pnp-bjt一和寄生npn-bjt不一致。

15.综上所述,本发明主要具有以下有益效果:

16.在pd-soi集成电路工艺下通过适当掺杂和结构设计形成侧边附加结构,该侧边附加结构在与径向垂直的侧向方向上,从而为传统的pnpn可控硅结构提供了额外的嵌入式寄生机构,构成新型esd防护装置。

17.一方面,该新型esd防护装置在与径向垂直的侧向方向上具有侧边附加结构,泄放静电电荷的流经面积更大,烧毁电流更高,具备更良好的esd防护能力;

18.另一方面,当该新型esd防护装置的pnpn结构进入回穿状态时,该新型esd防护装置的侧边附加结构抽取了部分本应进入pnp发射机的载流子,减弱了pnpn结构的回穿效应,能克服可控硅性esd防护器件维持电压过小的问题;其三,该新型esd防护装置的开启决定于径向垂直的侧向方向上侧边附加结构的击穿,使得整个esd防护装置的开启电压由阱区间的缓变结雪崩击穿转变为侧边附加结构的隧穿击穿,不仅使得整个esd防护装置的触发电压有效降低,也更加可控,更加能够满足深纳微米制程下日益缩小的esd防护窗口要求。

附图说明

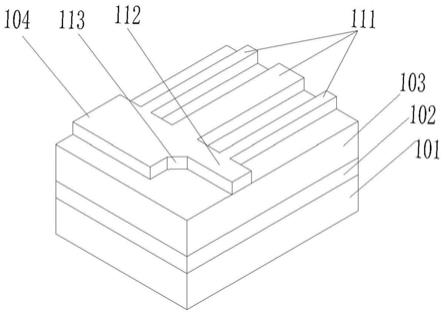

19.图1是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置立体结构

示意图;

20.图2是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的俯视图、前视图、左视图、右视图结构示意图;

21.图3是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的有源区掺杂的俯视图、前视图、后视图、左视图、右视图示意图;

22.图4是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的电学等效电路示意图;

23.图5是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的静电电荷泄放曲线示意图;

24.图6是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的制备掩膜版示意图;

25.图7是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元立体结构示意图;

26.图8是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的俯视图、前视图/后视图、左视图/右视图结构示意图;

27.图9是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的有源区掺杂的俯视图示意图;

28.图10是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的的制备掩膜版示意图。

29.附图说明:101、半导体基底一;201、半导体基底二;102、绝缘体介质一;202、绝缘体介质二;103、绝缘体上半导体基质一;203、绝缘体上半导体基质二;104、多晶硅一;204、多晶硅二;111、径向多晶硅;112、侧边多晶硅;113、倒角;301、第一半导体类型;302、第二半导体类型;3031、第一半导体类型重掺杂一;3032、第一半导体类型重掺杂二;3033、第一半导体类型重掺杂三;3041、第二半导体类型重掺杂一;3042、第二半导体类型重参杂二;401、寄生pnp-bjt一;402、寄生电阻一;403、寄生npn-bjt;404、寄生电阻二;405、寄生pnp-bjt二;406、寄生电阻二;501、零点;502、触发点一;503、维持点;504、热烧毁点一;505、触发点二;506、维持点;507、热烧毁点二;701、半导体基底三;801、半导体基底四;702、绝缘体介质三;802、绝缘体介质四;703、绝缘体上半导体基质三;803、绝缘体上半导体基质四;704、多晶硅三;804、多晶硅四;711、径向多晶硅二;712、侧边多晶硅二;713、倒角二;901、第一半导体类型中掺杂;902、第二半导体类型中掺杂;9031、第一半导体类型重掺杂四;9032、第一半导体类型重掺杂五;9033、第一半导体类型重掺杂六;9041、第二半导体类型重掺杂三;9042、第二半导体类型重掺杂四。

具体实施方式

30.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

31.图1是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置立体结构

示意图;图2是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的俯视图、前视图、左视图、右视图结构示意图,用来用以方便、清晰地说明图1的结构细节。

32.实施例结构上包含半导体基底一101、半导体基底二201,绝缘体介质一102、绝缘体介质二202,绝缘体上半导体基质一103、绝缘体上半导体基质二203,绝缘体上半导体基质上的多晶硅一104、多晶硅二204。如图1所示,多晶硅一104根据方向不同分为径向多晶硅111和侧边多晶硅112,径向多晶硅111和侧边多晶硅112电学上相连接,为但不限于为一次性一体制备。侧边多晶硅112在如图所示的右侧收窄,建议性地宽处与窄处有倒角113。本实施例以兼容标准硅基pd-soi集成电路工艺为目的,为标准硅基工艺,因而实施例中的半导体基底一101、半导体基底二201为但不限于硅基底,掺杂浓度根据标准硅基pd-soi集成电路的沟道底背掺杂浓度决定。绝缘体介质一102、绝缘体介质二202为但不限于sio2绝缘体,由但不限于由注氧隔离(simox)、键合法、smartcurt方法制备。绝缘体上半导体基质一103、绝缘体上半导体基质二203为本装置的主要有源区,为但不限于为标准硅基pd-soi集成电路工艺的硅膜层,厚度与被保护电路的标准器件硅膜厚度,由标准硅基pd-soi集成电路工艺决定。

33.图3是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的有源区掺杂的俯视图、前视图、后视图、左视图、右视图示意图。

34.除了结构上的设计,本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的特征还包括合适的掺杂来形成所述功能。如上所述,绝缘体上半导体基质一103、绝缘体上半导体基质二203为本装置的主要有源区,因此本实施例仅在多晶硅一104、多晶硅二204中表现掺杂示意。

35.第一半导体类型301中掺杂为但不限于为绝缘体上半导体基质一103、绝缘体上半导体基质二203的底掺杂,或为扩散形成的阱区掺杂;第二半导体类型302中掺杂为但不限于为扩散形成的阱区掺杂。第一半导体类型重掺杂一3031、第一半导体类型重掺杂二3032、第一半导体类型重掺杂三3033与第二半导体类型重掺杂一3041、第二半导体类型重参杂二3042的掺杂浓度远高于第一半导体类型重掺杂一3031和第一半导体类型重掺杂二3032,与金属或者金属硅化物引出形成无肖特基势垒的欧姆接触,同时亦为寄生esd泄放机构的电极。第一半导体类型重掺杂一3031、第一半导体类型重掺杂二3032、第一半导体类型重掺杂三3033与第二半导体类型重掺杂一3041、第二半导体类型重参杂二3042的图形为但不限于为多晶硅一104的自对准形成,多晶硅一104的自对准技术有助于减少泄放通路表面的表面损伤,避免大电流下电流在缺陷处集中进而提前烧毁的作用。通过多晶硅一104的图形转移,形成如图所示的第一半导体类型重掺杂一3031、第一半导体类型重掺杂二3032、第一半导体类型重掺杂三3033与第二半导体类型重掺杂一3041、第二半导体类型重参杂二3042;通过多晶硅倒角113的图形转移,形成如俯视图中所示的下侧第一半导体类型重掺杂三3033宽处与窄处的倒角。建议性地形成的倒角能够避免锐角形状早高电压下形成的电场集中,进而避免不可控的高场强造成的意外击穿。

36.图4是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的电学等效电路示意图。

37.参考图3后视图,主方向上第一半导体类型重掺杂一3031、第二半导体类型302的掺杂和第一半导体类型301中的掺杂构成寄生pnp-bjt一401,主方向上第二半导体类型302

的掺杂、第一半导体类型301的掺杂、第一半导体类型重掺杂二3032构成寄生npn-bjt403。侧方向上第一半导体类型重掺杂一3031、第二半导体类型302的掺杂、第一半导体类型重掺杂三3033构成寄生pnp-bjt二405;由第一半导体类型重掺杂一3031和第二半导体类型重掺杂一3041引出形成阳极电极,第二半导体类型重掺杂一3041至第一半导体类型重掺杂一3031的内阻构成寄生电阻一402,第二半导体类型重掺杂一3041至第一半导体类型重掺杂三3033的内阻构成寄生电阻二406。第一半导体类型重掺杂二3032、第二半导体类型重参杂二3042、第二半导体类型重参杂二3042引出形成阴极电极,第二半导体类型重参杂二3042至第一半导体类型重掺杂二3032的内阻构成寄生电阻二404。寄生pnp-bjt一401、寄生npn-bjt403、寄生pnp-bjt二405相互嵌套形成pnpn可控硅型esd防护装置。寄生pnp-bjt二405为侧向方向上形成的寄生器件,电流方向与寄生pnp-bjt一401和寄生npn-bjt403不一致。

38.图5是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的静电电荷泄放曲线示意图。

39.传统的可控硅型esd防护装置其静电电荷泄放曲线如图由零点501开始,随着电压增加,第一半导体类型和第二半导体类型阱区之间的缓变结反向偏压增加,直到在触发点一502发生雪崩击穿,进入回穿区域;当pnp和npnbjt闩锁稳定时,达到回穿区域的维持点503,达到次状态的最小电压及维持电压;随着电压升高继续泄放电荷,直到局部电流密度达到一定程度,热量集聚导致温度急剧上升,发生不可逆的热烧毁,达到热烧毁点一504。传统的可控硅型esd防护装置维持电压过小、开启电压大,难以满足pd-soi工艺先进制程下esd防护的需求。

40.本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置其静电电荷泄放曲线亦如图由零点501开始,随着电压增加,第一半导体类型和第二半导体类型阱区之间的缓变结反向偏压增加的同时,第一半导体类型重掺杂一3031与第一半导体类型重掺杂三3033之间的电压也增加。阱区之间的雪崩击穿和第一半导体类型重掺杂一3031与第一半导体类型重掺杂三3033的隧穿击穿中,一旦其中之一发生即可进入回穿区域。控制合适的侧边多晶硅112宽度,即控制了第一半导体类型重掺杂一3031与第一半导体类型重掺杂三3033之间的距离,进而控制了第一半导体类型重掺杂一3031与第一半导体类型重掺杂三3033的隧穿击穿电压,由此达到有效控制且降低esd防护装置开启电压的功能。一般情况下,第一半导体类型重掺杂一3031与第一半导体类型重掺杂三3033的隧穿击穿明显小于阱区之间的雪崩击穿,因而本专利所公开的装置在较低的触发点二505即可触发。

41.当pnp和npnbjt闩锁稳定时,达到回穿区域的维持点506。当该新型esd防护装置的寄生pnp-bjt一401、寄生npn-bjt403、寄生pnp-bjt二405所形成的pnpn结构进入回穿状态时,侧边附加结构寄生pnp-bjt二405抽取了部分本应进入寄生pnp-bjt一401的载流子,减弱了pnpn结构的回穿效应,由此达到有效提高esd防护装置维持电压的功能,其维持点506高于传统可控硅型esd防护装置的维持点503。

42.随着电压升高继续泄放电荷,局部电流密度也进一步提高。本专利所公开的装置除了主方向的电流,还由于侧边结构寄生pnp-bjt二405的存在,侧方向也分流了部分电流,泄放静电电荷的流经面积更大。因此,达到相同的局部电流密度而发生不可逆的热烧毁时,能泄放的总电流更大,其热烧毁点二507高于传统可控硅型esd防护装置的热烧毁点一504。

43.图6是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的制备掩

膜版示意图。

44.制备本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置并不需要额外的成本,工艺流程上与标准pd-soi工艺相同,仅仅在图形设计上与标准pd-soi电路有所区别。在本实施例默认绝缘体上半导体基质一103、绝缘体上半导体基质二203底掺杂形成第一类型半导体阱区情况下,第二类型半导体的阱区由如图6a所示掩膜版形成。本实施例不排除在绝缘体上半导体基质一103、绝缘体上半导体基质二203底掺杂形成第一类型半导体阱区情况,以额外的掩膜版形成第二类型半导体阱区。绝缘体上半导体基质上的多晶硅一104、多晶硅二204如图6b所示掩膜版形成,用以利用多晶硅一104、多晶硅二204的自对准注入形成多种重掺杂。第一半导体类型重掺杂一3031、第一半导体类型重掺杂二3032、第一半导体类型重掺杂三3033通过如图6c所示掩膜版经过一次注入退火形成,该掩膜版的图案比可以当不强制比图6b更宽,以实现多晶硅一104、多晶硅二204的自对准。第二半导体类型重掺杂一3041、第二半导体类型重参杂二3042通过如图6d所示掩膜版经过一次注入退火形成,该掩膜版的图案比可以但不强制比图6b更宽,以实现多晶硅一104、多晶硅二204的自对准。

45.图7是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元立体结构示意图。该防护单元由图1所示的基本结构对称组成,具有良好的对称性,是本发明所公开装置应用时的建议组成形式。图8是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的俯视图、前视图/后视图、左视图/右视图示意图,用来用以方便、清晰地说明图1的结构细节。

46.实施例结构上包含半导体基底三701、半导体基底四801,绝缘体介质三702、绝缘体介质四802,绝缘体上半导体基质三703、绝缘体上半导体基质四803,绝缘体上半导体基质上的多晶硅三704、多晶硅四804。如图1所示,多晶硅三704根据方向不同分为径向多晶硅二711和侧边多晶硅二712,径向多晶硅二711和侧边多晶硅二712电学上相连接,为但不限于为一次性一体制备。侧边多晶硅二712在如图所示的右侧收窄,建议性地宽处与窄处有倒角二713。本实施例以兼容标准硅基pd-soi集成电路工艺为目的,为标准硅基工艺,因而实施例中的半导体基底三701、半导体基底四801为但不限于硅基底,掺杂浓度根据标准硅基pd-soi集成电路的沟道底背掺杂浓度决定。绝缘体介质三702、绝缘体介质四802为但不限于sio2绝缘体,由但不限于由注氧隔离(simox)、键合法、smartcurt方法制备。绝缘体上半导体基质上的多晶硅三704、多晶硅四804为本装置的主要有源区,为但不限于为标准硅基pd-soi集成电路工艺的硅膜层,厚度与被保护电路的标准器件硅膜厚度,由标准硅基pd-soi集成电路工艺决定。

47.图9是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的有源区掺杂的俯视图示意图;

48.除了结构上的设计,本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置的特征还包括合适的掺杂来形成所述功能。如上所述,绝缘体上半导体基质三703、绝缘体上半导体基质四803为本装置的主要有源区,因此本实施例仅在多晶硅三704、多晶硅四804中表现掺杂示意。

49.第一半导体类型中掺杂901为但不限于为绝缘体上半导体基质三703、绝缘体上半导体基质四803的底掺杂,或为扩散形成的阱区掺杂;第二半导体类型中掺杂902为但不限

于为扩散形成的阱区掺杂。第一半导体类型重掺杂四9031、第一半导体类型重掺杂五9032、第一半导体类型重掺杂六9033与第二半导体类型重掺杂三9041、第二半导体类型重掺杂四9042的掺杂浓度远高于第一半导体类型中掺杂901和第二半导体类型中掺杂902,与金属或者金属硅化物引出形成无肖特基势垒的欧姆接触,同时亦为寄生esd泄放机构的电极。第一半导体类型重掺杂四9031、第一半导体类型重掺杂五9032、第一半导体类型重掺杂六9033与第二半导体类型重掺杂三9041、第二半导体类型重掺杂四9042的图形为但不限于为多晶硅三704的自对准形成,多晶硅三704的自对准技术有助于减少泄放通路表面的表面损伤,避免大电流下电流在缺陷处集中进而提前烧毁的作用。通过多晶硅三704的图形转移,形成如图所示的第一半导体类型重掺杂四9031、第一半导体类型重掺杂五9032、第一半导体类型重掺杂六9033与第二半导体类型重掺杂三9041、第二半导体类型重掺杂四9042;通过多晶硅倒角113的图形转移,形成如俯视图中所示的下侧第一半导体类型重掺杂六9033宽处与窄处的倒角。建议性地形成的倒角能够避免锐角形状早高电压下形成的电场集中,进而避免不可控的高场强造成的意外击穿。

50.图10是本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置应用时组成的防护单元的的制备掩膜版示意图;

51.制备本发明实施例提供的pd-soi集成电路工艺下的新型esd防护装置并不需要额外的成本,工艺流程上与标准pd-soi工艺相同,仅仅在图形设计上与标准pd-soi电路有所区别。在本实施例默认绝缘体上半导体基质三703、绝缘体上半导体基质四803底掺杂形成第一类型半导体阱区情况下,第二类型半导体的阱区由如图6a所示掩膜版形成。本实施例不排除在绝缘体上半导体基质三703、绝缘体上半导体基质四803底掺杂形成第一类型半导体阱区情况,以额外的掩膜版形成第二类型半导体阱区。绝缘体上半导体基质上的多晶硅三704、多晶硅四804如图6b所示掩膜版形成,用以利用多晶硅三704、多晶硅四804的自对准注入形成多种重掺杂。第一半导体类型重掺杂四9031、第一半导体类型重掺杂五9032、第一半导体类型重掺杂六9033通过如图6c所示掩膜版经过一次注入退火形成,该掩膜版的图案比可以当不强制比图6b更宽,以实现多晶硅三704、多晶硅四804的自对准。第二半导体类型重掺杂三9041、第一半导体类型重掺杂五9032通过如图6d所示掩膜版经过一次注入退火形成,该掩膜版的图案比可以但不强制比图6b更宽,以实现多晶硅三704、多晶硅四804的自对准。

52.需要强调的是,借鉴本发明公开细节,利用相反类型用来泄放静电负电荷的方法,亦在本发明的保护范围之内。

53.描述本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1