功率芯片快速测试基板的制作方法

1.本发明涉及半导体功率器件技术领域,尤指一种功率芯片快速测试基板。

背景技术:

2.现有的像igbt、mosfet这一类的功率器件产品,常规情况下在晶圆生产完成后,需要对晶圆上的晶粒(芯片)进行封装,封装后进行参数性能的测试评估。

3.但是,由于芯片封装需要一定的周期,且封装形式也会对可封装的芯片尺寸有所限制,导致功率芯片的测试效率较低,通用性较差。因此,需要一种通用性更强,测试效率更高的功率芯片快速测试基板。

技术实现要素:

4.本发明的目的是提供一种功率芯片快速测试基板,以解决现有技术中功率芯片测试效率较低,通用性较差的问题。

5.本发明提供的技术方案如下:

6.本发明提供一种功率芯片快速测试基板,包括:

7.绝缘基板,所述绝缘基板的表面设置有若干个金属区域,且各个所述金属区域彼此隔离;

8.一个所述金属区域上设置有焊接区,用于焊接待测芯片,且所述待测芯片通过打线的方式与其余的所述金属区域电性连接。

9.对于igbt、mosfet这一类的功率器件产品,常规情况下在晶圆生产完成后,需要对晶圆上的晶粒(芯片)进行封装,封装后进行参数性能的测试评估。但是,由于芯片封装需要一定的周期,且封装形式也会对可封装的芯片尺寸有所限制,导致功率芯片的测试效率较低,通用性较差。本方案通过设置绝缘基板,并在绝缘基板上开设若干个金属区域,各个金属区域彼此隔离,其中一个金属区域用于焊接待测芯片,其余的金属区域通过打线的方式与待测芯片电性连接,使得测试前不需要对功率芯片进行封装,测试效率更高,且能够满足不同类型、不通尺寸的芯片需求,通用性更强。

10.在一些实施方式中,用于焊接所述待测芯片的所述金属区域的侧方设置有引出部,所述引出部用作第一电极。

11.具体的,常用的igbt与mos通常是有三个电极,frd是有两个电极,在引出待测芯片的电极时,可以直接在焊接待测芯片的金属区域的侧方设置一个引出部用作第一电极。

12.在一些实施方式中,所述金属区域的个数为三个,一个用于焊接所述待测芯片,其余两个分别作为第二电极和第三电极。

13.为了保证基板的通用性,可以设置金属区域的个数为三个,当待测芯片为igbt与mos时,一个用于焊接待测芯片,其余两个分别作为第二电极和第三电极;而当待测芯片为frd时,则一个用于焊接待测芯片,一个作为第二电极,另一个空置不用,从而保证基板能够适用各种类型的功率芯片的测试。

14.在一些实施方式中,所述待测芯片的栅极与所述第二电极电性连接,所述待测芯片的源极与所述第三电极电性连接。

15.在一些实施方式中,所述第三电极的尺寸大于所述第二电极的尺寸。

16.为了保证待测芯片的源极能够与第三电极之间打出更多的引线,可以设置第三电极的尺寸大于第二电极的尺寸。

17.在一些实施方式中,所述第一电极、所述第二电极和所述第三电极均焊接有引脚,所述引脚伸出所述绝缘基板,用于连接测试机台。

18.具体的,在进行测试时,可以有多种连接方式,如可以在第一电极、第二电极和第三电极上均焊接有引脚,引脚伸出绝缘基板,从而可以通过引脚插接的方式连接测试机台。

19.在一些实施方式中,所述第一电极、所述第二电极和所述第三电极均连接有引线夹,所述引线夹用于连接测试机台。

20.在进行测试时,也可以通过引线夹连接测试机台与第一电极、第二电极和第三电极,以便进行待测芯片的测试。

21.在一些实施方式中,所述第二电极和所述第三电极分别位于所述第一电极的两侧。

22.在一些实施方式中,所述绝缘基板为陶瓷板。

23.根据本发明提供的一种功率芯片快速测试基板,通过设置绝缘基板,并在绝缘基板上开设若干个金属区域,各个金属区域彼此隔离,其中一个金属区域用于焊接待测芯片,其余的金属区域通过打线的方式与待测芯片电性连接,使得测试前不需要对功率芯片进行封装,测试效率更高,且能够满足不同类型、不通尺寸的芯片需求,通用性更强。

附图说明

24.下面将以明确易懂的方式,结合附图说明优选实施方式,对本方案的上述特性、技术特征、优点及其实现方式予以进一步说明。

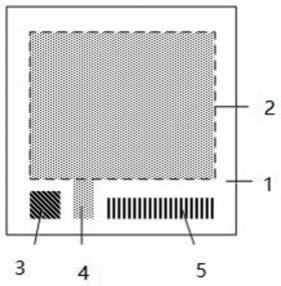

25.图1是本发明实施例的一种测试基板结构示意图;

26.图2是本发明实施例的另一种测试基板结构示意图;

27.图3是本发明实施例的一种测试基板打线结构示意图;

28.图4是本发明实施例的另一种测试基板打线结构示意图。

29.图中标号:1-绝缘基板;2-金属区域;3-第二电极;4-第一电极;5-第三电极;6-待测芯片。

具体实施方式

30.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,并获得其他的实施方式。

31.为使图面简洁,各图中只示意性地表示出了与本发明相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

32.在一个实施例中,参考说明书附图图1和图2,本发明提供一种功率芯片快速测试基板,包括绝缘基板1,绝缘基板1的表面设置有若干个金属区域2,且各个金属区域2彼此隔离。

33.在本实施例中,绝缘基板1为陶瓷板,起到绝缘的作用,在其它实施例中,还可以根据实际需求选择其它类型的绝缘材料,在此不作限制。

34.在本实施例中,金属区域2优选覆铜材料,金属铜导电性较好,在其它实施例中,还可以根据选择其它类型的导电材料,在此也不作限制。

35.一个金属区域2上设置有焊接区,用于焊接待测芯片6,且待测芯片6通过打线的方式与其余的金属区域2电性连接。

36.用于焊接待测芯片6的金属区域2尺寸较大,以满足不同大小的待测芯片6的测试,无需针对不同尺寸的待测芯片6制作不同的绝缘基板1。在将待测芯片6焊接在焊接区时,有多种方式,如可以采用刷锡膏或焊锡片的方式,由于焊锡片更便于裁剪成不同尺寸,可以与不同尺寸的芯片匹配,优先推荐焊锡片,焊锡片裁剪成比芯片略大一圈的尺寸,将待测芯片6叠放在焊锡片上,将覆盖了焊锡片和待测芯片6的绝缘基板1置于加热台上加热几分钟(加热温度需要超过选取的焊锡片的熔点,一般200℃-350℃),焊锡融化后,将加热台关闭,自然环境中冷区,冷却后即完成了待测芯片6与绝缘基板1的快速烧结焊接;此步骤也可变成将焊锡片放置在绝缘基板1需要焊接芯片的位置上,将绝缘基板1置于加热台上加热几分钟(加热温度需要超过选取的焊锡片的熔点,一般200℃-350℃),焊锡融化后,用镊子将需要评估的待测芯片6轻轻的放在融化的焊锡上,将加热台关闭,自然环境中冷区,冷却后即完成了待测芯片6与绝缘基板1的快速烧结焊接。

37.对于igbt、mosfet这一类的功率器件产品,常规情况下在晶圆生产完成后,需要对晶圆上的晶粒(芯片)进行封装,封装后进行参数性能的测试评估。但是,由于芯片封装需要一定的周期,且封装形式也会对可封装的芯片尺寸有所限制,导致功率芯片的测试效率较低,通用性较差。

38.本方案通过设置绝缘基板1,并在绝缘基板1上开设若干个金属区域2,各个金属区域2彼此隔离,其中一个金属区域2用于焊接待测芯片6,其余的金属区域2通过打线的方式与待测芯片6电性连接,使得测试前不需要对功率芯片进行封装,测试效率更高,大大缩短功率芯片评估验证周期(当天可获得测试评估结果),且能够满足不同类型、不通尺寸的芯片需求,通用性更强。

39.在一个实施例中,用于焊接待测芯片6的金属区域2的侧方设置有引出部,引出部用作第一电极4。

40.具体的,常用的igbt与mos通常是有三个电极,frd是有两个电极,在引出待测芯片6的电极时,可以直接在焊接待测芯片6的金属区域2的侧方设置一个引出部用作第一电极4。

41.在一个实施例中,金属区域2的个数为三个,一个用于焊接待测芯片6,其余两个分别作为第二电极3和第三电极5。

42.为了保证基板的通用性,可以设置金属区域2的个数为三个,当待测芯片6为igbt与mos时,一个用于焊接待测芯片6,其余两个分别作为第二电极3和第三电极5;而当待测芯

片6为frd时,则一个用于焊接待测芯片6,一个作为第二电极3,另一个空置不用,从而保证基板能够适用各种类型的功率芯片的测试。

43.优选的,在设置绝缘基板1的布局时,第二电极3和第三电极5分别位于第一电极4的两侧。

44.在一个实施例中,待测芯片6的栅极与第二电极3电性连接,待测芯片6的源极与第三电极5电性连接。

45.优选的,第三电极5的尺寸大于第二电极3的尺寸。

46.具体的,为了保证待测芯片6的源极能够与第三电极5之间打出更多的引线,可以设置第三电极5的尺寸大于第二电极3的尺寸。

47.在一个实施例中,参考说明书附图图2和图4,第一电极4、第二电极3和第三电极5均焊接有引脚,引脚伸出绝缘基板1,用于连接测试机台。

48.具体的,在进行测试时,可以有多种连接方式,如可以在第一电极4、第二电极3和第三电极5上均焊接有引脚,引脚伸出绝缘基板1,从而可以通过引脚插接的方式连接测试机台。引脚部分间距可参考测试机台对应电极的间距。

49.在一个实施例中,参考说明书附图图3,第一电极4、第二电极3和第三电极5均连接有引线夹(引线夹用于直接夹住各个电极,图中并未画出),引线夹用于连接测试机台。

50.在进行测试时,也可以通过引线夹连接测试机台与第一电极4、第二电极3和第三电极5,以便进行待测芯片6的测试。

51.另外,本发明还提供一种测试系统,包括上述的功率芯片快速测试基板,还包括:测试机台,测试机台与待测芯片6电性连接。

52.测试机台与待测芯片6的连接方式可以为引脚连接,通过在第一电极4、第二电极3和第三电极5上焊接引脚,引脚伸出绝缘基板1,从而可以通过引脚插接的方式实现测试机台的待测芯片6的连接;另外,也可以通过引线夹连接测试机台和第一电极4、第二电极3、第三电极5,在此不做限制。

53.通过将上述的测试基板直接与测试机台连接,能够实现待测芯片6的测试,如静态测试、动态测试、耐量测试等,且该测试方式率更高,能够满足不同类型、不通尺寸的芯片需求,通用性更强。

54.应当说明的是,上述实施例均可根据需要自由组合。以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1