一种系统级芯片及其制作方法与流程

1.本发明涉及半导体技术领域,更为具体地说,涉及一种系统级芯片及其制作方法。

背景技术:

2.rf(radio frequency,射频)-soi(silicon on insulator,绝缘体上硅)已经牢牢把控4g手机射频开关市场;rf-soi技术目前已经成为4g手机开关类rf应用的主流技术,其市占率已经超过95%。fd-soi是全耗尽型绝缘衬底上硅技术,同传统基于体硅或者fin-fet相比具有灵活可调的背偏压可以极大得提高芯片性能,其在体硅中引入了超薄的埋氧层作为绝缘层,具有功耗低、速度快、抗辐射、可靠性高的特点,具备高性能运算能力。现有技术中,rf-soi和fd-soi采用完全不同电阻率的衬底,相关芯片结构无法实现兼容。

技术实现要素:

3.有鉴于此,本发明提供了一种系统级芯片及其制作方法,有效解决现有技术存在的技术问题,在系统级芯片中实现了逻辑控制芯片结构和射频芯片结构的兼容。

4.为实现上述目的,本发明提供的技术方案如下:

5.一种系统级芯片的制作方法,包括:

6.提供单晶硅衬底;

7.在所述单晶硅衬底上形成埋氧层,所述埋氧层划分为逻辑区域和射频区域;

8.在所述埋氧层背离所述单晶硅衬底一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘;

9.去除所述单晶硅衬底对应所述射频区域的部分形成镂空区;

10.在所述埋氧层朝向所述单晶硅衬底一侧,形成位于所述镂空区处的多晶硅衬底;

11.在所述单晶硅衬底及所述多晶硅衬底背离所述芯片结构一侧形成封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

12.可选的,在形成所述芯片结构后且形成所述镂空区前,还包括:

13.在所述芯片结构背离所述单晶硅衬底一侧形成键合支撑基板。

14.可选的,所述第一连线焊盘和所述第二连线焊盘为钨金属焊盘。

15.相应的,本发明还提供了一种系统级芯片的制作方法,包括:

16.提供多晶硅衬底;

17.在所述多晶硅衬底上形成埋氧层,所述埋氧层划分为逻辑区域和射频区域;

18.在所述埋氧层背离所述多晶硅衬底一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘;

19.去除所述多晶硅衬底对应所述逻辑区域的部分形成镂空区;

20.在所述埋氧层朝向所述多晶硅衬底一侧,形成位于所述镂空区处的单晶硅衬底;

21.在所述单晶硅衬底及所述多晶硅衬底背离所述芯片结构一侧形成封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

22.可选的,在形成所述芯片结构后且形成所述镂空区前,还包括:

23.在所述芯片结构背离所述多晶硅衬底一侧形成键合支撑基板。

24.可选的,所述第一连线焊盘和所述第二连线焊盘为钨金属焊盘。

25.相应的,本发明还提供了一种系统级芯片,包括:

26.衬底基板,所述衬底基板划分为多晶硅衬底和单晶硅衬底;

27.位于所述衬底基板一侧表面的埋氧层,所述埋氧层划分为对应所述多晶硅衬底的射频区域和对应所述单晶硅衬底的逻辑区域;

28.位于所述埋氧层背离所述衬底基板一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘;

29.以及,位于所述衬底基板背离所述芯片结构一侧的封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

30.可选的,所述系统级芯片还包括位于所述芯片结构背离所述衬底基板一侧的键合支撑基板。

31.可选的,所述第一连线焊盘和所述第二连线焊盘为钨金属焊盘。

32.相较于现有技术,本发明提供的技术方案至少具有以下优点:

33.本发明提供了一种系统级芯片及其制作方法,包括:衬底基板,所述衬底基板划分为多晶硅衬底和单晶硅衬底;位于所述衬底基板一侧表面的埋氧层,所述埋氧层划分为对应所述多晶硅衬底的射频区域和对应所述单晶硅衬底的逻辑区域;位于所述埋氧层背离所述衬底基板一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘;以及,位于所述衬底基板背离所述芯片结构一侧的封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

34.由上述内容可知,本发明提供的技术方案,通过衬底基板的多晶硅衬底实现高阻率衬底,及通过衬底基板的单晶硅衬底实现低阻率衬底;进而能够通过高阻率的多晶硅衬底支持射频芯片结构的功能,及通过低阻率的单晶硅衬底支持逻辑控制芯片结构的功能,达到在系统级芯片中实现逻辑控制芯片结构和射频芯片结构兼容的目的。

附图说明

35.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

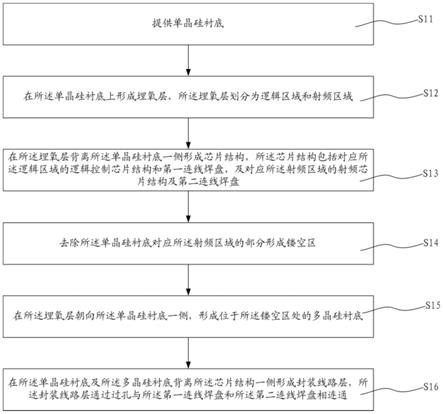

36.图1为本发明实施例一提供的一种系统级芯片的制作方法的流程图;

37.图2a-图2f为图1中各步骤相应的结构示意图;

38.图3为本发明实施例二提供的一种系统级芯片的制作方法的流程图。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

40.正如背景技术所述,rf(radio frequency,射频)-soi(silicon on insulator,绝缘体上硅)已经牢牢把控4g手机射频开关市场;rf-soi技术目前已经成为4g手机开关类rf应用的主流技术,其市占率已经超过95%。fd-soi是全耗尽型绝缘衬底上硅技术,同传统基于体硅或者fin-fet相比具有灵活可调的背偏压可以极大得提高芯片性能,其在体硅中引入了超薄的埋氧层作为绝缘层,具有功耗低、速度快、抗辐射、可靠性高的特点,具备高性能运算能力。现有技术中,rf-soi和fd-soi采用完全不同电阻率的衬底,相关芯片结构无法实现兼容。

41.基于此,本发明实施例提供了一种系统级芯片及其制作方法,有效解决现有技术存在的技术问题,在系统级芯片中实现了逻辑控制芯片结构和射频芯片结构的兼容。

42.为实现上述目的,本发明实施例提供的技术方案如下,具体结合图1至图3对本发明实施例提供的技术方案进行详细的描述。

43.实施例一

44.参考图1所示,为本发明实施例一提供的一种系统级芯片的制作方法的流程图,其中,制作方法包括:

45.s11、提供单晶硅衬底。

46.s12、在所述单晶硅衬底上形成埋氧层,所述埋氧层划分为逻辑区域和射频区域。

47.s13、在所述埋氧层背离所述单晶硅衬底一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘。

48.s14、去除所述单晶硅衬底对应所述射频区域的部分形成镂空区。

49.s15、在所述埋氧层朝向所述单晶硅衬底一侧,形成位于所述镂空区处的多晶硅衬底。

50.s16、在所述单晶硅衬底及所述多晶硅衬底背离所述芯片结构一侧形成封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

51.可以理解的,本发明实施例提供的技术方案,通过衬底基板的多晶硅衬底实现高阻率衬底,及通过衬底基板的单晶硅衬底实现低阻率衬底;进而能够通过高阻率的多晶硅衬底支持射频芯片结构的功能,及通过低阻率的单晶硅衬底支持逻辑控制芯片结构的功能,达到在系统级芯片中实现逻辑控制芯片结构和射频芯片结构兼容的目的。

52.具体结合图2a至图2f对本发明实施例提供的制作方法进行更详细的描述,图2a-图2f为图1中各步骤相应的结构示意图。

53.如图2a所示,对应步骤s11,提供单晶硅衬底110。

54.如图2b所示,对应步骤s12,在所述单晶硅衬底110上形成埋氧层120,所述埋氧层120划分为逻辑区域121和射频区域122。

55.如图2c所示,对应步骤s13,在所述埋氧层120背离所述单晶硅衬底110一侧形成芯

片结构,所述芯片结构包括对应所述逻辑区域121的逻辑控制芯片结构1311和第一连线焊盘1312,及对应所述射频区域122的射频芯片结构1321及第二连线焊盘1322。

56.如图2d所示,对应步骤s14,去除所述单晶硅衬底110对应所述射频区域122的部分形成镂空区。

57.在本发明一实施例中,本发明可以采用光刻及刻蚀工艺去除单晶硅衬底对应射频区域的部分。其中,在形成镂空区前,可以将单晶硅衬底减薄至微米量级。

58.如图2e所示,对应步骤s15,在所述埋氧层120朝向所述单晶硅衬底110一侧,形成位于所述镂空区处的多晶硅衬底140。

59.在本发明一实施例中,本发明提供的多晶硅衬底的电阻率大于单晶硅衬底的电阻率,故而多晶硅衬底可以支持优化射频芯片结构的性能,即实现rf-soi衬底相关技术;单晶硅衬底能够支持优化逻辑控制芯片结构的性能,即实现fd-soi衬底相关技术,进而实现rf-soi相关技术和fd-soi相关技术的兼容。

60.如图2f所示,对应步骤s16,在所述单晶硅衬底110及所述多晶硅衬底140背离所述芯片结构一侧形成封装线路层150,所述封装线路层150通过过孔与所述第一连线焊盘1312和所述第二连线焊盘1322相连通。

61.进一步的,本发明实施例在形成所述芯片结构后且形成所述镂空区前,还包括:在所述芯片结构背离所述单晶硅衬底一侧形成键合支撑基板。

62.可以理解的,在芯片结构背离单晶硅衬底一侧形成键合支撑基板,能够在后续制作过程中为结构提供支撑结构,减小后续结构制备时出现碎片的几率。

63.在本发明一实施例中,本发明提供的所述第一连线焊盘和所述第二连线焊盘为钨金属焊盘,对此本发明不做具体限制。

64.实施例二

65.本发明实施例二提供了一种系统级芯片的制作方法。参考图3所示,为本发明实施例二提供的一种系统级芯片的制作方法的流程图,其中,制作方法包括:

66.s21、提供多晶硅衬底。

67.s22、在所述多晶硅衬底上形成埋氧层,所述埋氧层划分为逻辑区域和射频区域。

68.s23、在所述埋氧层背离所述多晶硅衬底一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘。

69.s24、去除所述多晶硅衬底对应所述逻辑区域的部分形成镂空区。

70.s25、在所述埋氧层朝向所述多晶硅衬底一侧,形成位于所述镂空区处的单晶硅衬底。

71.s26、在所述单晶硅衬底及所述多晶硅衬底背离所述芯片结构一侧形成封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

72.进一步的,本发明实施例在形成所述芯片结构后且形成所述镂空区前,还包括:在所述芯片结构背离所述多晶硅衬底一侧形成键合支撑基板。

73.可以理解的,在芯片结构背离多晶硅衬底一侧形成键合支撑基板,能够在后续制作过程中为结构提供支撑结构,减小后续结构制备时出现碎片的几率。

74.在本发明一实施例中,本发明提供的所述第一连线焊盘和所述第二连线焊盘为钨

金属焊盘,对此本发明不做具体限制。

75.实施例三

76.本发明实施例三提供了一种系统级芯片,其中系统级芯片包括:

77.衬底基板,所述衬底基板划分为多晶硅衬底和单晶硅衬底。

78.位于所述衬底基板一侧表面的埋氧层,所述埋氧层划分为对应所述多晶硅衬底的射频区域和对应所述单晶硅衬底的逻辑区域。

79.位于所述埋氧层背离所述衬底基板一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘。

80.以及,位于所述衬底基板背离所述芯片结构一侧的封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

81.进一步的,本发明实施例提供的所述系统级芯片还包括位于所述芯片结构背离所述衬底基板一侧的键合支撑基板。

82.可以理解的,在芯片结构背离衬底基板一侧形成键合支撑基板,能够在后续制作过程中为结构提供支撑结构,减小后续结构制备时出现碎片的几率。

83.在本发明一实施例中,本发明提供的所述第一连线焊盘和所述第二连线焊盘为钨金属焊盘,对此本发明不做具体限制。

84.本发明实施例提供了一种系统级芯片及其制作方法,包括:衬底基板,所述衬底基板划分为多晶硅衬底和单晶硅衬底;位于所述衬底基板一侧表面的埋氧层,所述埋氧层划分为对应所述多晶硅衬底的射频区域和对应所述单晶硅衬底的逻辑区域;位于所述埋氧层背离所述衬底基板一侧形成芯片结构,所述芯片结构包括对应所述逻辑区域的逻辑控制芯片结构和第一连线焊盘,及对应所述射频区域的射频芯片结构及第二连线焊盘;以及,位于所述衬底基板背离所述芯片结构一侧的封装线路层,所述封装线路层通过过孔与所述第一连线焊盘和所述第二连线焊盘相连通。

85.由上述内容可知,本发明实施例提供的技术方案,通过衬底基板的多晶硅衬底实现高阻率衬底,及通过衬底基板的单晶硅衬底实现低阻率衬底;进而能够通过高阻率的多晶硅衬底支持射频芯片结构的功能,及通过低阻率的单晶硅衬底支持逻辑控制芯片结构的功能,达到在系统级芯片中实现逻辑控制芯片结构和射频芯片结构兼容的目的。

86.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1