新型3D芯片封装结构

新型3d芯片封装结构

技术领域

1.本实用新型涉及一种芯片封装结构,特别涉及一种新型3d芯片封装结构,属于电子封装技术领域。

背景技术:

2.目前的3d封装主要有两种方式,一种是引线键合,特点是先将两个或者多个芯片垂直叠在一起,一般下面的芯片尺寸大,上面的芯片尺寸小,然后焊接线从侧面引出,实现小尺寸芯片和大尺寸芯片电互联,然而这种连接方式获得的封装结构的封装尺寸较大;另一种是tsv工艺(硅通孔),特点是先将两个或者多个芯片垂直叠在一起,然后在芯片上从上到下垂直刻蚀出一个通道,然后再生长金属线实现上下芯片的电互连,然而这种工艺需要进行刻蚀和生长,工艺比较复杂,不合适大规模推广应用。

技术实现要素:

3.本实用新型的主要目的在于提供一种新型3d芯片封装结构,以克服现有技术中的不足。

4.为实现前述实用新型目的,本实用新型采用的技术方案包括:

5.本实用新型实施例提供了一种新型3d芯片封装结构,包括:第一芯片、第二芯片、封装结构和电连接线,所述第一芯片和第二芯片分别设置在所述封装结构的两侧,所述电连接线穿过所述封装结构并分别与所述第一芯片、第二芯片电性连接。

6.与现有技术相比,本实用新型的优点包括:本实用新型实施例提供的一种新型3d芯片封装结构为垂直互连结构,该新型3d芯片封装结构的结构简单且制作工艺简单,并且,该新型3d芯片封装结构不需进行刻蚀和材料的生长,易于推广应用。

附图说明

7.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

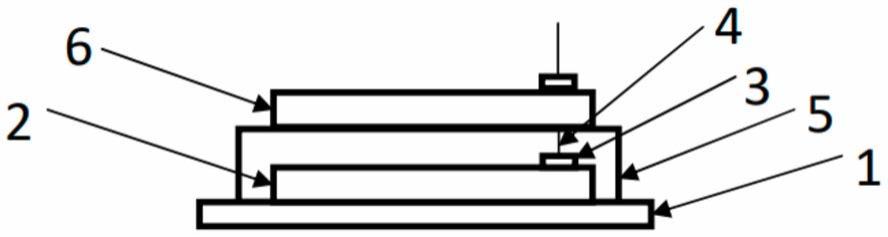

8.图1是本实用新型一典型实施案例中提供的一种新型3d芯片封装结构的结构示意图。

具体实施方式

9.鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本实用新型的技术方案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

10.本实用新型实施例提供了一种新型3d芯片封装结构,包括:第一芯片、第二芯片、封装结构和电连接线,所述第一芯片和第二芯片分别设置在所述封装结构的两侧,所述电

连接线穿过所述封装结构并分别与所述第一芯片、第二芯片电性连接。

11.进一步的,所述第一芯片的表面设置有焊盘,所述电连接线垂直设置在所述第一芯片上并与所述第一芯片的焊盘电性连接。

12.进一步的,所述第二芯片沿厚度方向叠设在所述第一芯片的上方。

13.进一步的,所述电连接线沿厚度方向垂直贯穿所述封装结构并分别与所述第一芯片、第二芯片电性连接。

14.进一步的,所述电连接线分别与所述第一芯片、第二芯片垂直连接。

15.进一步的,至少所述第一芯片被封装在所述封装结构内部。

16.进一步的,所述第一芯片和封装结构固定设置在pcb基板上,所述第二芯片固定设置在所述封装结构上,其中,所述第一芯片被封装在所述封装结构和pcb基板之间。

17.在一些较为具体的实施方案中,所述新型3d芯片封装结构包括:依次叠层设置在多个第一芯片和多个电连接线,多个所述第一芯片分别被封装于多个封装结构内,所述电连接线垂直设置在所述第一芯片的表面,且所述电连接线沿厚度方向垂直贯穿所述封装结构并分别与所述第一芯片、第二芯片电性连接,或者,所述电连接线沿厚度方向垂直贯穿所述封装结构并分别与相邻两个所述第一芯片电性连接。

18.进一步的,所述第一芯片和第二芯片的尺寸和形状相同。

19.进一步的,所述电连接线包括金线。

20.如下将结合附图对该技术方案、其实施过程及原理等作进一步的解释说明,除非特别说明的之外,本实用新型实施例中所采用的电连接线、封装结构等均可以采用本领域技术人员已知的材料和工艺制作获得。

21.请参阅图1,一种新型3d芯片封装结构,包括第一芯片2、第二芯片6、封装结构(例如可以是模压塑封结构)5和电连接线4,所述第一芯片2和封装结构5固定设置在pcb基板1上,所述第二芯片6固定设置在所述封装结构5上并沿厚度方向垂直叠设在所述第一芯片2的上方,其中,所述第一芯片2被封装在所述封装结构5和pcb基板1之间,所述电连接线4穿过所述封装结构5并分别与所述第一芯片、第二芯片电性连接。

22.具体的,所述第一芯片2的表面设置有焊盘(pad)3,所述电连接线4垂直设置在所述第一芯片2上并与所述第一芯片的焊盘3电性连接。

23.具体的,所述电连接线4沿厚度方向垂直贯穿所述封装结构5并分别与所述第一芯片2、第二芯片6电性连接,其中,所述电连接线4分别与所述第一芯片2、第二芯片6垂直连接。

24.在一些较为具体的实施方案中,所述新型3d芯片封装结构包括:依次叠层设置的多个第一芯片2和多个电连接线4,多个所述第一芯片2分别被封装于多个封装结构5内,所述电连接线4垂直设置在所述第一芯片2的表面,且所述电连接线4沿厚度方向垂直贯穿所述封装结构5并分别与所述第一芯片2、第二芯片6电性连接,或者,所述电连接线4沿厚度方向垂直贯穿所述封装结构5并分别与相邻两个所述第一芯片2电性连接,其中,所述第一芯片和第二芯片的尺寸和形状相同,所述电连接线包括金线等。

25.具体的,所述第二芯片6背对第一芯片的表面也设置有第二焊盘,所述第二焊盘上电性连接有第二电连接线,所述第二电连接线与所述第二芯片垂直设置。

26.具体的,本实用新型实施例提供的一种新型3d芯片封装结构,通过从第一芯片上

的pad垂直引出电连接线,然后塑酯模压形成封装结构,然后再将第二芯片对准叠在封装结构上,并通过电连接线实现第一芯片和第二芯片的电互联。

27.具体的,实用新型实施例提供的一种新型3d芯片封装结构可以通过如下工艺制作获得:

28.首先采用die bond设备将第一芯片固定在pcb基板上;

29.采用wire bond设备在第一芯片的pad上垂直竖立一根电连接线,然后采用模压机对第一芯片进行塑封而形成封装结构,电连接线与封装结构垂直设置且所述电连接线的部分自封装结构背对第一芯片的表面露出;

30.采用die bond设备将第二芯片粘贴到塑封后的第一芯片上,并使第二芯片与所述电连接线电连接,从而实现两个芯片的电互联,多个芯片的电互联依次类推。

31.本实用新型实施例提供的一种新型3d芯片封装结构为垂直互连结构,该新型3d芯片封装结构的结构简单且制作工艺简单,并且,该新型3d芯片封装结构不需进行刻蚀和材料的生长,易于推广应用;较之现有技术中采用引线键合所需的封装尺寸更加小,相比tsv工艺需要刻蚀和金属生长,本实用新型提供的一种新型3d芯片封装结构的加工工艺更加简单快捷。

32.应当理解,上述实施例仅为说明本实用新型的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本实用新型的内容并据以实施,并不能以此限制本实用新型的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1