混成式电感装置的制作方法

1.本实用新型是有关于一种电感器,尤其是一种混成式电感装置。

背景技术:

2.现今电子设备蓬勃发展,而电子设备一般都需要外接电源从而运作。然而,电子设备与电源之间的电力传输经常会产生电磁干扰(例如,杂讯)。因此,为了滤除电磁干扰,一般会于电子设备与电源之间设置一电子滤波器(例如,电源滤波器(line filter))。在电源滤波器中,用以滤除电磁干扰的元件主要为共模电感以及差模电感,而另外用以提供其他功能(例如,限流或降低衰减的频率响应等)的主要元件可为无感电阻。

3.由于电源滤波器的发展朝向小型化及高频化,若每使用一共模电感及一差模电感时即需分别提供一磁芯,则会占用电源滤波器的内部空间,而使电源滤波器无法满足小型化的产品需求。此外,若使用不同磁芯的共模电感与差模电感,由于线圈绕组的电压压降问题,会致使无法由共模电感与差模电感来形成无感电阻至电源滤波器中。

技术实现要素:

4.鉴于上述,本实用新型提供一种混成式电感装置。依据一些实施例,通过于单一磁芯绕制多个线圈绕组,以使单一铁芯即可形成共模电感、差模电感及无感电阻,而可降低电源滤波器的电路大小,并降低所占用的电源滤波器的内部空间,以满足电源滤波器小型化的产品需求。依据一些实施例,由于混成式电感装置具有简单的线圈绕组架构,因而能透过绕线机(coil winding machine)自动绕线来实现,而无需手动绕线,致使提升产品生产效率。

5.依据一些实施例,混成式电感装置包含磁芯、第一绕组以及第二绕组。磁芯定义有第一绕组区及第二绕组区。第一绕组区与第二绕组区位于磁芯的不同位置,且彼此分隔。第一绕组包含第一线圈及第二线圈。第一线圈具有多个第一线圈匝、自磁芯的顶面延伸的第一起始端及自磁芯的底面延伸的第一结束端。第一线圈匝绕制于第一绕组区。第二线圈具有多个第二线圈匝、自磁芯的顶面延伸的第二起始端及自磁芯的底面延伸的第二结束端。第二线圈匝绕制于第一绕组区。第一线圈匝与第二线圈匝于第一绕组区具有同一绕制方向。第一线圈匝分别平行第二线圈匝。第一起始端相邻于第二起始端,第一结束端相邻于第二结束端。第二绕组包含第三线圈及第四线圈。第三线圈具有多个第三线圈匝、自磁芯的顶面延伸的第三起始端及自磁芯的底面延伸的第三结束端。第三线圈匝绕制于第二绕组区。第四线圈具有多个第四线圈匝、自磁芯的顶面延伸的第四起始端及自磁芯的底面延伸的第四结束端。第四线圈匝绕制于第二绕组区。第三线圈匝与第四线圈匝于第二绕组区具有同一绕制方向。第三线圈匝分别平行第四线圈匝。第三起始端相邻于第四起始端,第三结束端相邻于第四结束端。第一起始端及第二起始端相邻于第三结束端及第四结束端,第一结束端及第二结束端相邻于第三起始端及第四起始端。

6.依据一些实施例,所述多个第一线圈匝与所述多个第二线圈匝彼此间隔排列,所

述多个第三线圈匝与所述多个第四线圈匝彼此间隔排列。

7.依据一些实施例,所述多个第一线圈匝与所述多个第二线圈匝重叠,所述多个第三线圈匝与所述多个第四线圈匝重叠。

8.依据一些实施例,所述多个第一线圈匝及所述多个第二线圈匝沿着一第一方向缠绕于该第一绕组区,所述多个第三线圈匝及所述多个第四线圈匝沿着一第二方向缠绕于该第二绕组区,其中该第一方向与该第二方向互为相反方向。

9.依据一些实施例,在一电流分别经由该第一线圈的该第一结束端及该第三线圈的该第三结束端流至该第一线圈的该第一起始端及该第三线圈的该第三起始端时,该第一线圈与该第三线圈形成一共模电感。

10.依据一些实施例,在一电流分别经由该第二线圈的该第二起始端及该第四线圈的该第四起始端流至该第二线圈的该第二结束端及该第四线圈的该第四结束端时,该第二线圈与该第四线圈形成一共模电感。

11.依据一些实施例,在一电流分别经由该第一线圈的该第一结束端及该第四线圈的该第四结束端流至该第一线圈的该第一起始端及该第四线圈的该第四起始端时,该第一线圈与该第四线圈透过该电流产生同一磁场方向而形成一差模电感。

12.依据一些实施例,在一电流分别经由该第二线圈的该第二结束端及该第三线圈的该第三结束端流至该第二线圈的该第二起始端及该第三线圈的该第三起始端时,该第二线圈与该第三线圈透过该电流产生同一磁场方向而形成一差模电感。

13.依据一些实施例,该第一起始端与该第二起始端相互耦接,在一电流经由该第一结束端流至该第二结束端时,该第一线圈与该第二线圈形成一无感电阻。

14.依据一些实施例,该第三起始端与该第四起始端相互耦接,在一电流经由该第三结束端流至该第四结束端时,该第三线圈与该第四线圈形成一无感电阻。

15.综上所述,依据一些实施例,通过于单一磁芯绕制多个绕组,且每个绕组具有多个线圈,同一绕组的每个线圈具有同一绕制方向,且同一绕组的每个线圈的线圈匝相互平行(例如第一线圈的线圈匝与第二线圈的线圈匝相互平行),以使在电流产生时,根据不同的线圈组合而形成共模电感、差模电感或无感电阻,而可降低电源滤波器的电路大小,并降低所占用的电源滤波器的内部空间,以满足电源滤波器小型化的产品需求。依据一些实施例,通过多个同一绕制方向的线圈形成绕组,而使此绕组得以透过绕线机自动绕线来实现(即可避免费时的手动绕线),致使提升产品生产效率。

附图说明

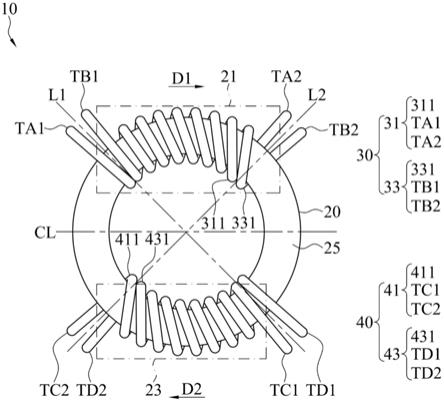

16.图1是本案一些实施例的混成式电感装置的示意图;

17.图2是本案一些实施例的混成式电感装置的示意图;

18.图3是本案一些实施例的部分结构的剖面示意图;

19.图4是本案一些实施例的混成式电感装置的等效电路示意图;

20.图5是本案一些实施例的混成式电感装置的共模信号抑制应用电路;

21.图6是本案一些实施例的混成式电感装置的差模信号抑制应用电路;

22.图7是本案一些实施例的混成式电感装置的无感电阻应用电路。

23.【符号说明】

24.10:混成式电感装置

25.20:磁芯

26.21:第一绕组区

27.23:第二绕组区

28.25:间隙

29.cl:中心轴

30.30:第一绕组

31.31:第一线圈

32.311:第一线圈匝

33.ta1:第一起始端

34.ta2:第一结束端

35.33:第二线圈

36.331:第二线圈匝

37.tb1:第二起始端

38.tb2:第二结束端

39.35:部分结构

40.40:第二绕组

41.41:第三线圈

42.411:第三线圈匝

43.tc1:第三起始端

44.tc2:第三结束端

45.43:第四线圈

46.431:第四线圈匝

47.td1:第四起始端

48.td2:第四结束端

49.l1:第一轴线

50.l2:第二轴线

51.200:电源

52.201:正电端

53.v+:正电源信号

54.203:负电端

55.v

‑

:负电源信号

56.300:外接电路

57.301:第一输入端

58.303:第二输入端

59.c:杂散电容

60.gnd:参考地信号

61.a1~a4:电流方向

62.d1:第一方向

63.d2:第二方向

具体实施方式

64.关于本文中所使用的“第一”及“第二”等术语,其是用以区别所指的元件,而非用以排序或限定所指元件的差异性,且亦非用以限制本实用新型的范围。并且,所使用的“耦接”、“连接”等术语,其是指二或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触;举例来说,若文中描述第一装置耦接于第二装置,则代表第一装置可直接电性连接于第二装置,或者透过其他装置或连接手段间接地电性连接至第二装置。

65.参照图1,图1是本案一些实施例的混成式电感装置10的示意图。混成式电感装置10包含磁芯20、第一绕组30及第二绕组40。磁芯20可为由氧化铁混合物组成的一种烧结磁性金属氧化物,例如烧结磁性锰

‑

锌铁氧化物、镍

‑

锌铁氧化物等。第一绕组30及第二绕组40可由金属线实现。金属线可为单芯线、多芯绞线等。虽然图1仅绘示二个绕组,但本实用新型不限于此,混成式电感装置10的绕组的数量可以依据实际设计需求而调整。

66.磁芯20定义有第一绕组区21及第二绕组区23。虽然图1仅绘示二个绕组区,但本实用新型不限于此,磁芯20的绕组区的数量可以依据实际设计需求而调整。第一绕组区21与第二绕组区23位于磁芯20的不同位置,且彼此分隔。也就是说,第一绕组区21与第二绕组区23不互相重叠。举例来说,磁芯20依据其中心轴cl而区分为二区域(于后称上半区域及下半区域),第一绕组区21位于磁芯20的上半区域,第二绕组区23位于磁芯20的下半区域,且第一绕组区21的二端与第二绕组区23的二端之间以间隙25所分隔。

67.在一些实施例中,第一绕组30位于第一绕组区21,第二绕组40位于第二绕组区23。由于第一绕组区21与第二绕组区23之间彼此分隔,第一绕组区21及第二绕组区23的第一绕组30与第二绕组40之间具有较低的杂散电容值,致使混成式电感装置10可同时具有良好的高频滤波能力及低频滤波能力。

68.第一绕组30包含第一线圈31及第二线圈33。第一线圈31具有多个第一线圈匝311、自磁芯20的顶面延伸出的第一起始端ta1,及自磁芯20的底面延伸出的第一结束端ta2。第一线圈匝311绕制于第一绕组区21。举例来说,如图1所示,第一线圈31的第一起始端ta1位于第一绕组区21的左端,第一线圈31往第一绕组区21的右侧绕,并绕到位于第一绕组区21的右端的第一结束端ta2,以形成第一线圈匝311。

69.第二线圈33具有多个第二线圈匝331、自磁芯20的顶面延伸出的第二起始端tb1,及自磁芯20的底面延伸出的第二结束端tb2。第二线圈匝331绕制于第一绕组区21。第二线圈匝331的绕制方式与第一线圈匝311相同,为使说明书简洁,于此不做赘述。第一线圈匝311与第二线圈匝331于第一绕组区21具有同一绕制方向。举例来说,如图1所示,第一线圈31及第二线圈33都是从第一起始端ta1及第二起始端tb1开始,以先从磁芯20的顶面绕往磁芯20的底面,再从磁芯20的底面绕往磁芯20的顶面的方式,沿着第一绕组区21的左端往第一绕组区21的右端绕(即由左至右),而于第一结束端ta2及第二结束端tb2结束。在此,第一起始端ta1相邻于第二起始端tb1,第一结束端ta2相邻于第二结束端tb2。例如,第一起始端ta1及第二起始端tb1皆位于第一绕组区21的左端,第一结束端ta2及第二结束端tb2皆位于第一绕组区21的右端。

70.每一第一线圈匝311分别平行每一第二线圈匝331。在一些实施例中,第一线圈匝

311与第二线圈匝331彼此间隔排列。例如,如图1所示,由第一绕组区21的左端至其右端(即,由左至右),第一线圈匝311与第二线圈匝331的排列顺序为“第一线圈匝311、第二线圈匝331、第一线圈匝311、第二线圈匝331、第一线圈匝311、第二线圈匝331、第一线圈匝311、第二线圈匝331

…

等”。

71.图2是本案一些实施例的混成式电感装置10的示意图,图3是本案一些实施例的部分结构35的剖面示意图。如图2及图3所示,在一些实施例中,第一线圈匝311与第二线圈匝331重叠。举例来说,第一线圈31及第二线圈33可整合在一起而由单一的多芯绞线实现,此时第一线圈匝311可重叠于第二线圈匝331之上或是重叠于第二线圈匝331之下。例如,如图3所示,部分结构35具有第一线圈匝311及第二线圈匝331,由图3可见,第一线圈匝311重叠于第二线圈匝331之上。在一些实施例中,由于第一线圈31及第二线圈33可整合在一起而由单一的多芯绞线实现,因而,第一起始端ta1与第二起始端tb1重叠,第一结束端ta2与第二结束端tb2重叠(例如,第一起始端ta1可重叠于第二起始端tb1之上或是重叠于第二起始端tb1之下,且第一结束端ta2可重叠于第二结束端tb2之上或是重叠于第二结束端tb2之下)。

72.再次参照图1。同样地,第二绕组40包含第三线圈41及第四线圈43。第三线圈41具有多个第三线圈匝411、自磁芯20的顶面延伸出的第三起始端tc1、及自磁芯20的底面延伸出的第三结束端tc2。第四线圈43具有多个第四线圈匝431、自磁芯20顶面延伸出的第四起始端td1、及自磁芯20的底面延伸出的第四结束端td2。第三线圈匝411及第四线圈匝431绕制于第二绕组区23。第三起始端tc1与第四起始端td1相邻(例如,第三起始端tc1及第四起始端td1皆位于第二绕组区23的右端),第三结束端tc2与第四结束端td2相邻(例如,第三结束端tc2及第四结束端td2皆位于第二绕组区23的左端),第三线圈匝411及第四线圈匝431具有同一绕制方向。例如,第三线圈匝411与第四线圈匝431的绕制方向可为始于第三起始端tc1及第四起始端td1,以先从磁芯20的顶面绕往磁芯20的底面,再从磁芯20的底面绕往磁芯20的顶面的方式,沿着第二绕组区23的右端往第二绕组区23的左端绕(即由右至左),而于第三结束端tc2及第四结束端td2结束。

73.第一起始端ta1及第二起始端tb1相邻于第三结束端tc2及第四结束端td2,第一结束端ta2及第二结束端tb2相邻于第三起始端tc1及第四起始端td1。举例来说,第一绕组区21的左端相邻于第二绕组区23的左端(具体而言,第一绕组区21的左端与第二绕组区23的左端以间隙25所分隔),第一绕组区21的右端相邻于第二绕组区23的右端(具体而言,第一绕组区21的右端与第二绕组区23的右端以间隙25所分隔),由于第一起始端ta1及第二起始端tb1位于第一绕组区21的左端,第三结束端tc2及第四结束端td2位于第二绕组区23的左端,因而,第一起始端ta1及第二起始端tb1相邻于第三结束端tc2及第四结束端td2。相似地,由于第一结束端ta2及第二结束端tb2位于第一绕组区21的右端,第三起始端tc1及第四起始端td1位于第二绕组区23的右端,因而,第一结束端ta2及第二结束端tb2相邻于第三起始端tc1及第四起始端td1。在一些实施例中,如图1所示,第一起始端ta1、第二起始端tb1、第三起始端tc1及第四起始端td1位于同一轴线(于后称为第一轴线l1)上,第一结束端ta2、第二结束端tb2、第三结束端tc2及第四结束端td2位于同一轴线(于后称为第二轴线l2)上,且第一轴线l1与第二轴线l2相互垂直。

74.需说明的是,如图1所示,与第一线圈匝311及第二线圈匝331相似地,每一第三线圈匝411分别平行每一第四线圈匝431。同样地,在一些实施例中,如图1所示,与第一线圈匝

311及第二线圈匝331相似地,第三线圈匝411与第四线圈匝431彼此间隔排列,例如由第二绕组区23的右端至其左端(即由右至左),第三线圈匝411与第四线圈匝431的排列顺序为“第四线圈匝431、第三线圈匝411、第四线圈匝431、第三线圈匝411、第四线圈匝431、第三线圈匝411、第四线圈匝431、第三线圈匝411

…

等”。同样地,在一些实施例中,如图2所示,与第一线圈匝311及第二线圈匝331相似地,第三线圈匝411与第四线圈匝431重叠。同样地,在一些实施例中,如图2所示,与第一起始端ta1、第二起始端tb1、第一结束端ta2及第二结束端tb2相似地,第三起始端tc1与第四起始端td1重叠,第三结束端tc2与第四结束端td2重叠。

75.在一些实施例中,如图1所示,第一线圈匝311及第二线圈匝331沿着第一方向d1缠绕于第一绕组区21。第三线圈匝411及第四线圈匝431沿着第二方向d2缠绕于第二绕组区23。第一方向d1与第二方向d2互为相反方向。例如,第一方向d1为由第一绕组区21的左端往第一绕组区21的右端的方向(即,由左至右),第二方向d2为由第二绕组区23的右端往第二绕组区23的左端的方向(即,由右至左)。

76.在一些实施例中,第一绕组30中的第一线圈匝311、第二线圈匝331可以具有同一匝数。例如,第一线圈匝311与第二线圈匝331的匝数均为四个,但本实用新型不限于此,匝数可依实际需求做调整。在一些实施例中,第二绕组40中的第三线圈匝411、第四线圈匝431可以具有同一匝数。例如,第三线圈匝411与第四线圈匝431的匝数均为四个,但本实用新型不限于此,匝数可依实际需求做调整。在一些实施例中,由于第一绕组30与第二绕组40可大致呈对称,因此,第一线圈匝311、第二线圈匝331与第三线圈匝411、第四线圈匝431具有同一匝数。借此以提升混成式电感装置10的抑制杂讯(例如,共模杂讯或是差模杂讯)或是限流等的效能。

77.在一些实施例中,磁芯20可由闭合磁芯或非闭合磁芯来实施。在一些实施例中,在磁芯20是由闭合磁芯来实施的情形下,闭合磁芯可以是圆形磁芯、椭圆磁芯、矩形磁芯、ee型磁芯或是其他形状的闭合磁芯。

78.起始端(即第一起始端ta1至第四起始端td1)及结束端(即,第一结束端ta2至第四结束端td2)为线圈(即,第一线圈31、第二线圈33、第三线圈41、第四线圈43)用以耦接至外部电路元件或是电信号的元件。例如,第一起始端ta1及第一结束端ta2为第一线圈31的对外连接的端子;第二起始端tb1及第二结束端tb2为第二线圈33的对外连接的端子;第三起始端tc1及第三结束端tc2为第三线圈41的对外连接的端子;第四起始端td1及第四结束端td2为第四线圈43的对外连接的端子。借此,线圈经由起始端及结束端耦接至相应的电路元件或电信号后,混成式电感装置10便可应用于多种电路结构之中。在此,起始端及结束端,所表达的是线圈缠绕的开始与结束,而非限制电流通过的方向。

79.参照图1及图4。图4是本案一些实施例的混成式电感装置10的等效电路示意图。在一些实施例中,在电流分别经由第一线圈31的第一结束端ta2及第三线圈41的第三结束端tc2流至第一线圈31的第一起始端ta1及第三线圈41的第三起始端tc1时,第一线圈31与第三线圈41形成共模电感。

80.参照图1、图4及图5。图5是本案一些实施例的混成式电感装置10的共模信号抑制应用电路。举例来说,第一结束端ta2耦接电源200的正电端201的一正电源信号v+,第三结束端tc2耦接电源200的负电端203的一负电源信号v

‑

,第一起始端ta1耦接外部的欲滤波电路(于后称为外接电路300)的输入端(于后称为第一输入端301),第三起始端tc1耦接外接

电路300的另一输入端(于后称为第二输入端303)。当外接电路300耦接参考地信号gnd时(例如外接电路300的壳体接地),由于外接电路300与其耦接的参考地信号gnd之间具有杂散电容c,致使电源200的正电源信号v+及负电源信号v

‑

与参考地信号gnd之间会产生杂散信号(例如共模杂讯)。

81.因此,当共模杂讯发生时,电流(例如共模电流,亦即电源200的正电端201透过杂散电容c所产生的杂散电流的电流方向a1(于图5以一点链线表示)相同于电源200的负电端203透过杂散电容c所产生的杂散电流的电流方向a2(于图5以二点链线表示))经由第一结束端ta2流至第一线圈31的第一起始端ta1而经由外接电路300的参考地信号gnd返回电源200,并经由第三结束端tc2流至第三线圈41的第三起始端tc1而经由外接电路300的参考地信号gnd返回电源200,使第一线圈31及第三线圈41产生同方向的磁场,而增强了第一线圈31及第三线圈41的电感量,亦即增强了抑制共模电流的电感抗(换言之,此时的第一线圈31及第三线圈41形成为共模电感),达到滤除杂讯的效果。

82.相似地,在一些实施例中,在电流分别经由第二线圈33的第二起始端tb1及第四线圈43的第四起始端td1流至第二线圈33的第二结束端tb2及第四线圈43的第四结束端td2时,第二线圈33与第四线圈43形成共模电感。在此,由于第二线圈33及第四线圈43形成共模电感的方式与第一线圈31及第三线圈41相同,为使本案说明书简洁,于此不作赘述。

83.在一些实施例中,在电流分别经由第一线圈31的第一结束端ta2及第四线圈43的第四结束端td2流至第一线圈31的第一起始端ta1及第四线圈43的第四起始端td1时,第一线圈31与第四线圈43透过电流产生同一磁场方向而形成差模电感。

84.参照图1、图4及图6。图6是本案一些实施例的混成式电感装置10的差模信号抑制应用电路。举例来说,第一结束端ta2耦接电源200的正电端201的正电源信号v+,第四起始端td1耦接电源200的负电端203的负电源信号v

‑

,第一起始端ta1耦接外接电路300的第一输入端301,第四结束端td2耦接外接电路300的第二输入端303。由于电源线的信号(正电源信号v+与负电源信号v

‑

)之间会产生杂讯,且此杂讯(亦即差模杂讯)一般为串联耦接电源线。当差模杂讯发生时,电流(例如差模电流,亦即作为差模电流的杂讯电流的电流方向a4(于图6中以二点链线表示)相同于电源电流的电流方向a3(于图6中以一点链线表示))经由第一结束端ta2流至第一线圈31的第一起始端ta1而流经外接电路300,并从外接电路300经由第四结束端td2流至第四线圈43的第四起始端td1,使第一线圈31及第四线圈43产生同方向的磁场(亦即产生同一磁场方向),而增强了第一线圈31及第四线圈43的电感量,亦即增强了抑制差模电流的电感抗(换言之,此时的第一线圈31及第四线圈43形成为差模电感),达到滤除杂讯的效果。

85.相似地,在一些实施例中,在电流分别经由第二线圈33的第二结束端tb2及第三线圈41的第三结束端tc2流至第二线圈33的第二起始端tb1及第三线圈41的第三起始端tc1时,第二线圈33与第三线圈41透过电流产生同一磁场方向而形成差模电感。在此,由于第二线圈33与第三线圈41形成差模电感的方式与第一线圈31及第四线圈43相同,为使本案说明书简洁,于此不作赘述。

86.在一些实施例中,第一起始端ta1与第二起始端tb1相互耦接,在电流经由第一结束端ta2流至第二结束端tb2时,第一线圈31与第二线圈33形成无感电阻。

87.参照图1、图4及图7。图7是本案一些实施例的混成式电感装置10的无感电阻应用

电路。举例来说,第一结束端ta2耦接电源200的正电端201的正电源信号v+,第二结束端tb2耦接外接电路300的第一输入端301。当欲对外接电路300进行限流、降低其衰弱的频率响应(例如增加其负载)等时,将第一起始端ta1耦接第二起始端tb1(即,将第一起始端ta1与第二起始端tb1短路),电流经由第一结束端ta2流经第一线圈31及第二线圈33后,流至外接电路300。由于第一线圈31及第二线圈33互相产生反方向的磁场,因而相互抵消磁场而未产生电感抗,换言之,此时第一线圈31及第二线圈33为不具有电感抗的电阻(例如,仅具有线圈的电阻值)或是仅具有微小漏感所产生的电感,亦即第一线圈31及第二线圈33形成实质的无感电阻,以应用于外接电路300所需使用的功能(例如限流、降低衰落的频率响应等)。

88.相似地,在一些实施例中,第三起始端tc1与第四起始端td1相互耦接,在电流经由第三结束端tc2流至第四结束端td2时,第三线圈41与第四线圈43形成无感电阻。在此,由于第三线圈41与第四线圈43形成无感电阻的方式与第一线圈31及第二线圈33相同,为使本案说明书简洁,于此不作赘述。

89.在一些实施例中,电流可为直流电流或交流电流。换言之,混成式电感装置10可为使用于直流电系统或交流电系统。在一些实施例中,混成式电感装置10可适用于π型滤波器或t型滤波器。

90.由上述可见,混成式电感装置10具有简单的线圈绕组架构,因而能透过绕线机自动绕线来实现,而提升产品生产效率,且还可降低线圈绕组之间的相互干扰。

91.综上所述,依据一些实施例,通过于单一磁芯绕制多个绕组,且每个绕组具有多个线圈,同一绕组的每个线圈具有同一绕制方向,且同一绕组的每个线圈的线圈匝相互平行(例如第一线圈的线圈匝与第二线圈的线圈匝相互平行),以使在电流产生时,根据不同的线圈组合而形成共模电感、差模电感或无感电阻,而可降低电源滤波器的电路大小,并降低所占用的电源滤波器的内部空间,以满足电源滤波器小型化的产品需求。依据一些实施例,通过多个同一绕制方向的线圈形成绕组,而使此绕组得以透过绕线机自动绕线来实现(即可避免费时的手动绕线),致使提升产品生产效率。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1