一种半导体芯片封装结构的制作方法

1.本实用新型涉及半导体技术领域,尤其涉及一种半导体芯片封装结构。

背景技术:

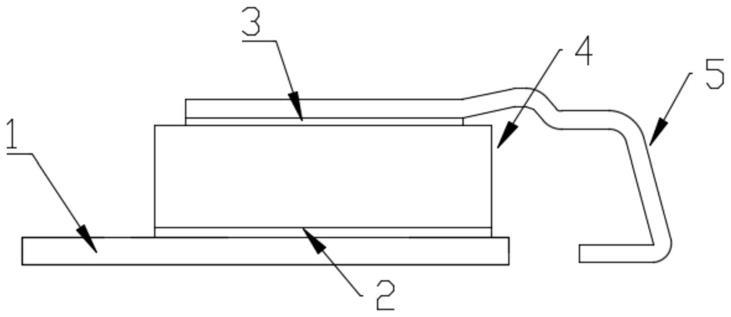

2.现有的半导体芯片封装通常为通过焊料合金回流、导电环氧树脂等安装在贴片电极上,安装好的半导体芯片包封于环氧化合物等材料中。随着对半导体器件的功率要求提高,半导体芯片的面积也逐渐增大,而如图1所示,对于大面积半导体芯片,芯片的热应力较高,尤其是靠近第一贴片电极的一侧的热应力过大,因此很容易出现由于热应力而开裂或导致器件故障,因此,本技术旨在提供一种可有效减少芯片热应力的半导体芯片局部封装结构。

技术实现要素:

3.为了克服上述现有技术的缺陷,本实用新型所要解决的技术问题是提供一种有效减少芯片热应力的半导体芯片封装结构。

4.为了解决上述技术问题,本实用新型采用的技术方案为:一种半导体芯片封装结构,包括依次层叠设置的第一贴片电极、芯片和第二贴片电极,所述芯片与第二贴片电极之间焊接,所述第一贴片电极和芯片之间具有第一间隙,所述第一间隙内填充有第一连接层,所述第一连接层包括第一焊接层和围绕第一焊接层设置的第一隔离层,所述第一焊接层的两端面分别与第一贴片电极和芯片焊接。

5.进一步的,所述第一隔离层呈回字形结构,所述第一焊接层对应回字形结构的中心位置设置,且所述第一焊接层对应芯片的安装面的中心位置设置。

6.进一步的,所述第一焊接层与所述第一隔离层的表面齐平。

7.进一步的,所述第一焊接层与芯片的接触面积小于或等于芯片的安装面的面积的50%。

8.进一步的,所述第一焊接层的厚度小于100微米。

9.进一步的,所述第二贴片电极和芯片之间具有第二间隙,所述第二间隙内填充有第二连接层,所述第二连接层包括第二焊接层和围绕第二焊接层设置的第二隔离层,所述第二焊接层的两端面分别与第二贴片电极和芯片焊接。

10.进一步的,所述第二贴片电极与芯片的接触面积小于所述芯片的安装面的面积。

11.进一步的,所述第二贴片电极与芯片的接触面上设有凸台,所述凸台远离第二贴片电极的一端面与芯片接触且所述凸台与芯片的接触面积小于所述芯片的安装面的面积。

12.进一步的,所述第二贴片电极设有弯折部,所述弯折部上设有通孔。

13.进一步的,还包括壳体,所述壳体包覆芯片、第一贴片电极和第二贴片电极,所述第一贴片电极部分伸出壳体外部且所述第一贴片电极伸出至壳体外部的部分上设有限位孔。

14.本实用新型的有益效果在于:

15.一种半导体芯片封装结构,通过设置隔离层将焊接区域缩小,从而实现芯片与第一贴片之间为局部焊接,进而缩小了芯片与第一贴片电极的焊接面积,有效减小了芯片的热应力,防止器件开裂和故障;同时,采用隔离层围绕焊接层的方式,可防止焊接材料溢出,从而有效提升焊接工艺效率。

附图说明

16.图1所示为现有半导体芯片封装结构示意图;

17.图2所示为本实用新型实施例一的半导体芯片封装结构示意图;

18.图3所示为本实用新型实施例二的半导体芯片封装结构示意图;

19.图4所示为本实用新型实施例二的半导体芯片封装结构俯视图;

20.图5所示为本实用新型实施例三的半导体芯片封装结构示意图;

21.图6所示为本实用新型实施例三的半导体芯片封装结构俯视图;

22.图7所示为本实用新型实施例三的半导体芯片封装结构主视图。

23.标号说明:

[0024]1‑

第一贴片电极;2

‑

第一焊接层;3

‑

第二焊接层;4

‑

芯片;5

‑

第二贴片电极;6

‑

第一隔离层;7

‑

第一隔离层;8

‑

通孔;9

‑

壳体;10

‑

限位孔。

具体实施方式

[0025]

为详细说明本实用新型的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

[0026]

请参照图2至图7所示,本实用新型的一种半导体芯片封装结构,包括依次层叠设置的第一贴片电极、芯片和第二贴片电极,所述芯片与第二贴片电极之间焊接,所述第一贴片电极和芯片之间具有第一间隙,所述第一间隙内填充有第一连接层,所述第一连接层包括第一焊接层和围绕第一焊接层设置的第一隔离层,所述第一焊接层的两端面分别与第一贴片电极和芯片焊接。

[0027]

从上述描述可知,本实用新型的有益效果在于:

[0028]

一种半导体芯片封装结构,在焊接层的外围设置隔离层,可防止焊接材料溢出,有效提升焊接工艺效率,同时,在芯片和第一贴片电极之间采用局部焊接的方式,缩小了芯片与第一贴片电极的焊接面积,从而有效减小了芯片的热应力,防止器件开裂和故障。

[0029]

进一步的,所述第一隔离层呈回字形结构,所述第一焊接层对应回字形结构的中心位置设置,且所述第一焊接层对应芯片的安装面的中心位置设置。

[0030]

从上述描述可知,回字形结构的第一隔离层可防止焊接材料溢出,将焊接区域设置在芯片安装面的中央,可以确保芯片与贴片之间导电均匀,结构上可使各部位受到的应力也倾于平衡。

[0031]

进一步的,所述第一焊接层与所述第一隔离层的表面齐平。

[0032]

从上述描述可知,第一焊接层与所述第一隔离层的表面齐平,从而保证芯片与第一贴片电极之间没有空隙,实现良好的连接。

[0033]

进一步的,所述第一焊接层与芯片的接触面积小于或等于芯片的安装面的面积的50%。

[0034]

从上述描述可知,根据大量实验证明,第一凸台的接触面的面积小于或等于芯片的安装面的面积的50%时,效果较好。

[0035]

进一步的,所述第一焊接层的厚度小于100微米。

[0036]

从上述描述可知,根据大量实验证明,焊接层的厚度小于100微米更有利于导电、热传导及方便散热。

[0037]

进一步的,所述第二贴片电极和芯片之间具有第二间隙,所述第二间隙内填充有第二连接层,所述第二连接层包括第二焊接层和围绕第二焊接层设置的第二隔离层,所述第二焊接层的两端面分别与第二贴片电极和芯片焊接。

[0038]

从上述描述可知,在第二焊接层的外围设置第二隔离层,在芯片和第二贴片电极之间采用局部焊接的方式,缩小了芯片与第二贴片电极的焊接面积,从而有效减小了芯片的热应力。

[0039]

所述第一焊接层和第二焊接层的材质可以是锡等焊料,第一隔离层和第二隔离层的材质可以是绝缘胶、阻焊剂等绝缘阻焊材料。

[0040]

上述半导体芯片封装结构可以采用但不限于以下方式制得:在芯片的一安装面划分焊接区域和围绕该焊接区域的隔离区域,然后在所述隔离区域设置阻焊剂形成第一隔离层,再在焊接区域填充焊料形成第一焊接层,最后将第一贴片电极设于第一隔离层和第一焊接层上并与熔融的焊料接合,实现第一贴片电极和芯片之间局部焊接。第二贴片电极和芯片之间的局部焊接依此类推,此处不在赘述。

[0041]

进一步的,所述第二贴片电极与芯片的接触面积小于所述芯片的安装面的面积。

[0042]

从上述描述可知,通过减小第二贴片电极与芯片的接触面积,从而进一步减小芯片的热应力。

[0043]

进一步的,所述第二贴片电极与芯片的接触面上设有凸台,所述凸台远离第二贴片电极的一端面与芯片接触且所述凸台与芯片的接触面积小于所述芯片的安装面的面积。

[0044]

从上述描述可知,通过上述结构设计,可进一步减少芯片热应力、焊接应力和电流通量。

[0045]

进一步的,所述第二贴片电极设有弯折部,所述弯折部上设有通孔。

[0046]

从上述描述可知,通过在第二贴片电极增加通孔设计,减少了引脚折弯时的机械应力传导,有利于减少应力导致的电性失效及产品可靠性的提高。

[0047]

进一步的,还包括壳体,所述壳体包覆芯片、第一贴片电极和第二贴片电极,所述第一贴片电极部分伸出壳体外部且所述第一贴片电极伸出至壳体外部的部分上设有限位孔。

[0048]

从上述描述可知,壳体的设置对于芯片具有一定的保护作用,而在第一贴片电极伸出至壳体外部的部分上设置限位孔,可用于注塑定位。

[0049]

请参照图2所示,本实用新型的实施例一为:

[0050]

本实用新型提供的一种半导体芯片封装结构,包括依次层叠设置的第一贴片电极1、芯片4和第二贴片电极5,所述芯片4与第二贴片电极5之间焊接,所述第一贴片电极1和芯片4之间具有第一间隙,所述第一间隙内填充有第一连接层,所述第一连接层包括第一焊接层2和围绕第一焊接层设置的第一隔离层6,第一隔离层6呈回字形结构,所述第一焊接层2对应回字形结构的中心位置设置,第一焊接层2与所述第一隔离层6的表面齐平,且所述第

一焊接层2对应芯片4的安装面的中心位置设置,所述第一焊接层2的两端面分别与第一贴片电极1和芯片4焊接。

[0051]

本实施例中,第一焊接层与芯片的接触面积小于或等于芯片的安装面的面积的50%,第一焊接层的厚度小于100微米。

[0052]

请参照图3

‑

图4,本实用新型的实施例二为:

[0053]

与上述实施例一的区别在于,进一步对第二贴片电极5进行结构改进,具体为:所述第二贴片电极5和芯片4之间具有第二间隙,所述第二间隙内填充有第二连接层,所述第二连接层包括第二焊接层3和围绕第二焊接层设置的第二隔离层7,所述第二焊接层3的两端面分别与第二贴片电极5和芯片4焊接。

[0054]

本实施例中,第二贴片电极5与芯片4的接触面积小于芯片4的安装面的面积,优选的,在第二贴片电极5与芯片4的接触面上设置凸台,凸台远离第二贴片电极5的一端面与芯片4接触且凸台与芯片4的接触面积小于芯片4的安装面的面积

[0055]

与实施例一相比,第二贴片电极与芯片的接触面积减少,从而进一步减小芯片的热应力。

[0056]

请参照图5

‑

图7,本实用新型的实施例四为:

[0057]

与上述实施例一的区别在于,包括壳体9且进一步对第二贴片电极5进行结构改进,具体为:所述壳体9包覆芯片4、第一贴片电极1和第二贴片电极5,所述第一贴片电极1部分伸出壳体8外部且所述第一贴片电极1伸出至壳体9外部的部分上设有限位孔10;第二贴片电极5设有弯折部,所述弯折部上设有通孔8,所述通孔8为应力释放孔,其形状包括但不限于圆形、椭圆形等。

[0058]

与实施例一相比,壳体对芯片具有一定的保护作用,在第一贴片电极伸出至壳体外部的部分上设置限位孔,可用于注塑定位,同时通过在第二贴片电极增加应力释放孔设计,减少了第二贴片电极与芯片接触区域连接处的电极材料体积,从而达到减少壳体注塑成型合模及黑胶注塑时作用在晶粒上的剪切力。

[0059]

综上所述,本实用新型提供的一种半导体芯片封装结构,在焊接层的外围设置隔离层,可防止焊接材料溢出,有效提升焊接工艺效率,同时,在芯片和第一贴片电极之间采用局部焊接的方式,缩小了芯片与第一贴片电极的焊接面积,从而有效减小了芯片的热应力,防止器件开裂和故障。

[0060]

以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1