集成电路芯片、显示面板及显示装置的制作方法

1.本实用新型属于显示技术领域,具体涉及一种集成电路芯片、显示面板及显示装置。

背景技术:

2.cop(chip on plastic)封装方案通常应用于dic(display driver ic,显示驱动ic)芯片中,而对于tddi(touch&display driver ic,整合显示功能和触控功能的ic)芯片,通常采用cof(chip on film,覆晶薄膜)封装方式,目前还没有tddi芯片采用cop封装的方案。

技术实现要素:

3.本实用新型旨在至少解决现有技术中存在的技术问题之一,提供一种集成电路芯片、显示面板及显示装置,能够解决tddi芯片无法采用cop封装的问题。

4.第一方面,本实用新型实施例提供一种集成电路芯片,包括相互连接的第一边缘和第二边缘以及多个用于与显示面板进行绑定连接的第一引脚,所述第一边缘的长度小于所述第二边缘的长度,各所述第一引脚沿至少一个所述第一边缘排列为至少两列。

5.在一些实施例中,针对至少一组相邻两列第一引脚,在沿所述第二边缘的方向上,其中一列的所述第一引脚位于另一列中相邻两个所述第一引脚之间。

6.在一些实施例中,针对每组相邻两列第一引脚,在沿所述第二边缘的方向上,其中一列的所述第一引脚位于另一列中相邻两个所述第一引脚之间。

7.在一些实施例中,所述第一引脚与所述集成电路芯片表面平行的截面包括相互连接的第三边缘和第四边缘,所述第三边缘的长度小于所述第四边缘的长度,所述第一引脚至少满足以下条件之一:

8.所述第三边缘的长度大于或等于20μm且小于或等于25μm;

9.所述第四边缘的长度大于或等于60μm且小于或等于75μm。

10.在一些实施例中,所述集成电路芯片为tddi芯片或dic芯片。

11.在一些实施例中,当所述集成电路芯片为tddi芯片时,所述第一引脚包括电源引脚和/或凸出于所述tddi芯片表面的凸起结构;或者,

12.当所述集成电路芯片为dic芯片时,所述第一引脚为凸出于所述tddi芯片表面的凸起结构。

13.第二方面,本实用新型实施例还提供一种显示面板,所述显示面板包括衬底基板,所述衬底基板包括相互连接的第五边缘和第六边缘以及多个设置在所述衬底基板所在表面的第二引脚,所述第五边缘的长度小于所述第六边缘的长度,各所述第二引脚沿一个所述第五边缘排列为至少两列。

14.在一些实施例中,针对至少一组相邻两列第二引脚,在沿所述第六边缘的方向上,其中一列的所述第二引脚位于另一列中相邻两个所述第二引脚之间。

15.在一些实施例中,针对每组相邻两列第二引脚,在沿所述第六边缘的方向上,其中一列的所述第二引脚位于另一列中相邻两个所述第二引脚之间。

16.在一些实施例中,所述第二引脚至少满足以下条件之一:

17.在沿所述第五边缘的方向上,相邻两个所述第二引脚之间的间隔大于或等于12μm;

18.在沿所述第六边缘的方向上,相邻两列中的所述第二引脚之间的间隔大于或等于8μm。

19.在一些实施例中,所述第二引脚包括相互连接的第七边缘和第八边缘,所述第七边缘的长度小于所述第八边缘的长度,所述第二引脚至少满足以下条件之一:

20.所述第七边缘的长度大于或等于50μm且小于或等于55μm;

21.所述第八边缘的长度大于或等于70μm且小于或等于80μm。

22.第三方面。本实用新型实施例还提供一种显示装置,包括如前所述的集成电路芯片和如前所述的显示面板,所述第一引脚与所述第二引脚绑定连接。

23.在一些实施例中,所述集成电路芯片为如前所述的集成电路芯片,所述显示面板为如前所述的显示面板,所述集成电路芯片和所述显示面板至少满足以下条件之一:

24.所述第二引脚的第七边缘的长度与所述第一引脚的第三边缘的长度之差为30μm;

25.所述第二引脚的第八边缘的长度与所述第一引脚的第四边缘的长度之差为10μm。

26.在一些实施例中,所述集成电路芯片与所述显示面板之间至少满足以下之一:

27.在沿所述第五边缘的方向上,所述第一引脚与相邻的未绑定连接的所述第二引脚之间的最小间距g=a-(y-(c-b)/2);

28.在沿所述第六边缘的方向上,所述第一引脚与相邻列中所述第二引脚之间的最小间距h=f-(x-(e-d)/2);

29.所述第一引脚和所述第二引脚的搭接面积s=(b+(c-b)/2-y)*(d+(e-d)/2-x);

30.其中,a为同一列中相邻两个所述第二引脚之间的间隔,b为所述第一引脚的第三边缘的长度,c为所述第二引脚的第七边缘的长度,x为沿所述第六边缘的方向的绑定偏移量,y为沿所述第五边缘的方向的绑定偏移量,f为相邻列中两个所述第二引脚之间的间隔,x和y为常数;d为所述第一引脚的第四边缘的长度,e为所述第二引脚的第八边缘的长度。

附图说明

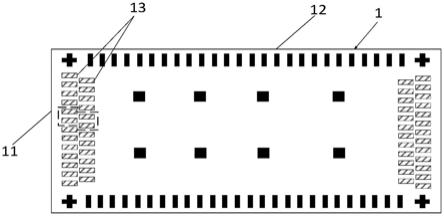

31.图1为相关技术的dic芯片的结构示意图;

32.图2为相关技术的tddi芯片的结构示意图;

33.图3为本实用新型实施例提供的集成电路芯片的示意图;

34.图4为图3中虚线框内的第一引脚的放大示意图;

35.图5为本实用新型实施例提供的显示面板的结构示意图;

36.图6为图5中虚线框内的第二引脚的放大示意图;

37.图7为本实用新型实施例提供的显示装置的结构示意图;

38.图8为本实用新型实施例提供的显示装置中显示面板与集成电路芯片绑定的示意图;

39.图9为相关技术的集成电路芯片与显示面板绑定偏移的示意图;

40.图10为本实用新型实施例提供的集成电路芯片与显示面板绑定偏移的示意图。

具体实施方式

41.为使本领域技术人员更好地理解本实用新型的技术方案,下面结合附图和具体实施方式对本实用新型作进一步详细描述。

42.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表示存在至少一个。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

43.相关技术的dic芯片结构如图1所示,包括功能引脚10和第一引脚13,功能引脚10位于dic芯片长边的两侧(即图1中上下两侧),第一引脚13为dummy bump(凸起结构),分布在dic芯片短边的两侧(即图1中左右两侧)和dic芯片的中间区域,起到填充空间和支撑dic芯片的作用,相关技术中dic芯片通常采用cop封装方式。

44.相关技术的tddi芯片,由于触控和显示驱动被整合到一起,为了避免信号出现互相干扰,目前对于tddi芯片通常采用cof封装方式。如图2所示,tddi芯片包括功能引脚10和第一引脚13,tddi芯片中用于实现触控功能的第一引脚13被称为触控通道,触控通道均匀分布在tddi芯片的两个短边侧。结合图1和图2所示,tddi芯片中第一引脚13的数量相对于dic芯片中第一引脚13的数量要多出一倍左右。受集成电路芯片尺寸限制及成本考虑,如图2所示,采用cof封装的tddi芯片中的第一引脚13的尺寸通常较小,以便在有限尺寸的tddi芯片中排布足够多数量的触控通道,得益于cof与集成电路芯片的共晶工艺,即使尺寸较小的第一引脚13也可以实现cof和tddi芯片之间的绑定连接。

45.在cop封装方案中,dic芯片与显示面板通过acf(anisotropic conductive film,异方性导电胶膜)绑定连接而非通过共晶工艺实现绑定连接,而acf绑定工艺对dic芯片中各第一引脚13之间以及显示面板绑定区中的各第二引脚之间的间隔有最小安全距离的要求。由于tddi芯片中第一引脚13的数量比常规dic芯片中相应位置的第一引脚13的数量增加一倍左右,因此,在第一引脚13数量一定的情况下,tddi芯片很难实现cop封装。

46.为了解决上述问题,如图3所示,本实用新型实施例提供一种集成电路芯片1,集成电路芯片1包括相互连接的第一边缘11和第二边缘12以及多个第一引脚13,第一边缘11的长度小于第二边缘12的长度,第一引脚13用于与显示面板进行绑定连接,各第一引脚13沿至少一个第一边缘11排列为至少两列。

47.本实用新型实施例的集成电路芯片1包括相互连接的第一边缘11和第二边缘12以及多个用于与显示面板进行绑定连接的第一引脚13,第一边缘11的长度小于第二边缘12的长度,各第一引脚13沿至少一个第一边缘11排列为至少两列。本实用新型实施例通过将各第一引脚13在集成电路芯片1的短边以至少两列的方式排布,在第一引脚13数量不变的情

况下,可以增加各第一引脚13之间的间隔以及显示面板绑定区中各第二引脚之间的间隔,这样就可以达到acf工艺要求的最小安全距离,避免绑定过程中发生短路,由此可以实现tddi芯片采用cop封装方式进行封装。

48.集成电路芯片1通常为矩形,因此集成电路芯片1具有两个第一边缘11和两个第二边缘12,在本公开实施例中,以各第一引脚13分别在两个第一边缘11按照至少两列排布为例进行说明。当然,本领域技术人员可知,一部分第一引脚13在其中一个第一边缘11按照至少两列排布,另一部分第一引脚13在另一个第一边缘11按照一列排布也是可行的。

49.在一些实施例中,结合图3和图4所示,针对至少一组相邻两列第一引脚13,在沿第二边缘12的方向上,其中一列的第一引脚13位于另一列中相邻两个第一引脚13之间。也就是说,在沿第二边缘12的方向上,至少一组相邻两列中的第一引脚13交错设置。沿第二边缘12的方向为x轴方向,在x轴方向上,至少2个第一引脚13的位置不在一条直线上。以第一引脚13排布为两列为例,在x轴方向上,其中位于一列的一个第一引脚13在位于另一列的两个第一引脚之间,即位于不同列的第一引脚13的中心位置的连线与第二边缘12并不平行。不同列的第一引脚13之间交错设置,可以进一步增加不同列的第一引脚13之间的间隔,进一步降低绑定过程中短路的风险。

50.在一些实施例中,针对每组相邻两列第一引脚13,在沿第二边缘12的方向上,其中一列的第一引脚13位于另一列中相邻两个第一引脚13之间。也就是说,在沿第二边缘12的方向上,任意相邻两列中的第一引脚13交错设置。以第一引脚13大于两列排布为例,在x轴方向上,其中位于一列的一个第一引脚13在位于其相邻列的两个第一引脚13之间,即奇数列的第一引脚13的中心位置的连线呈一条直线,偶数列的第一引脚13的中心位置的连线呈另一条直线。通过在沿第二边缘12的方向上将任意相邻两列中的第一引脚13交错设置,使得各个第一引脚13均交错设置,可以将绑定过程中短路风险降到最低。

51.acf工艺除了对各第一引脚13之间的间隔有最小安全距离的要求,还对第一引脚13的面积有最小导通面积的要求,保证导通位置有足够多的金属粒子,以保证绑定的有效性。为了解决该问题,在本实用新型实施例中,增加第一引脚13的面积。

52.由于最小安全距离与最小导通面积相互制约,因此为了兼顾二者,需要对第一引脚13的尺寸进行合理设置。在一些实施例中,如图4所示,第一引脚13与集成电路芯片表面平行的截面包括相互连接的第三边缘131和第四边缘132,第三边缘131的长度b小于第四边缘132的长度d,第一引脚13至少满足以下条件之一:

53.第三边缘的长度b大于或等于20μm且小于或等于25μm;

54.第四边缘的长度d大于或等于60μm且小于或等于75μm。

55.在相关技术中,集成电路芯片的第一引脚的第三边缘的长度为19μm,第四边缘的长度为40μm,在本技术实施例中,20μm≤第一引脚13的第三边缘131的长度b≤25μm,60μm≤第一引脚13的第四边缘132的长度d≤75μm,增加了第一引脚13两个边缘的长度,相应增加了第一引脚13的面积,可以达到最小导通面积的要求,保证绑定的有效性,同时也满足各第一引脚13之间的最小安全距离,避免绑定过程中出现短路。

56.在一些实施例中,集成电路芯片可以为tddi芯片或dic芯片。

57.在一些实施例中,当集成电路芯片为tddi芯片时,第一引脚13包括电源引脚和/或凸出于tddi芯片表面的凸起结构,凸起结构起到填充空间和支撑的作用。

58.在一些实施例中,当集成电路芯片为dic芯片时,第一引脚13为凸出于tddi芯片表面的凸起结构。

59.本实用新型实施例可以应用于tddi芯片,以解决目前tddi芯片无法采用cop方式封装的问题,需要说明的是,本实用新型实施例同样可以应用于dic芯片,提供了一种不同于相关技术的集成电路芯片第一引脚的排布方式和尺寸的新型dic芯片,以实现cop封装方式。

60.基于相同构思,如图5所示,本实用新型实施例还提供一种显示面板,显示面板包括衬底基板3,衬底基板3包括相互连接的第五边缘31和第六边缘32以及多个设置在衬底基板3所在表面的第二引脚33,第五边缘31的长度小于第六边缘32的长度,各第二引脚33沿一个第五边缘31排列为至少两列。

61.显示面板通常为矩形,因此衬底基板3具有两个第一边缘31和两个第二边缘32,而绑定区通常位于衬底基板3的一个短边的位置,第二引脚33位于显示面板的绑定区,即各第二引脚33沿一个第五边缘31按照至少两列排布。第二引脚33能够与集成电路芯片的第一引脚绑定连接,从而实现集成电路芯片与显示面板绑定连接。

62.需要说明的是,为了实现显示面板与集成电路芯片的绑定,显示面板的各第二引脚33的排布方式与集成电路芯片1的各第一引脚13的排布方式相对应。

63.衬底基板3为柔性衬底,显示面板为柔性显示面板,由于柔性显示面板的可弯折性,可以实现将绑定完成的集成电路芯片弯折到显示面板的背面,从而将下边框做到最窄,实现cop封装。

64.本实用新型实施例的显示面板包括衬底基板3,衬底基板3包括相互连接的第五边缘31和第六边缘32以及多个设置在衬底基板3所在表面的第二引脚33,第五边缘31的长度小于第六边缘32的长度,第二引脚33沿一个第五边缘31排列为至少两列。本实用新型实施例通过将各第二引脚33在显示面板的短边以至少两列的方式排布,在第二引脚33数量不变的情况下,可以增加各第二引脚33之间的间隔以及集成电路芯片中各第一引脚之间的间隔,这样就可以达到acf工艺要求的最小安全距离,避免绑定过程中发生短路,由此可以实现tddi芯片采用cop封装方式进行封装。

65.图6为图5中虚线框内的第二引脚的放大示意图,结合图5和图6所示,在一些实施例中,针对至少一组相邻两列第二引脚33,在沿第六边缘32的方向上,其中一列的第二引脚33位于另一列中相邻两个第二引脚33之间。也就是说,在沿第六边缘32的方向上,至少一组相邻两列中的第二引脚33交错设置。沿第六边缘32的方向为x轴方向,在x轴方向上,至少2个第二引脚33的位置不在一条直线上。以第二引脚33排布为两列为例,在x轴方向上,其中位于一列的一个第二引脚33在位于另一列的两个第二引脚33之间,即位于不同列的第二引脚33的中心位置的连线与第六边缘32并不平行。不同列的第二引脚33之间交错设置,可以进一步增加不同列之间第二引脚33之间的间隔,进一步降低绑定过程中短路的风险。

66.在一些实施例中,针对每组相邻两列第二引脚33,在沿第六边缘32的方向上,其中一列的第二引脚33位于另一列中相邻两个第二引脚33之间。也就是说,在沿第六边缘32的方向上,任意相邻两列中的第二引脚33交错设置。以第二引脚33大于两排布列为例,在x轴方向上,其中位于一列的一个第二引脚33在位于其相邻列的两个第二引脚33之间,即奇数列的第二引脚33的中心位置的连线呈一条直线,偶数列的第二引脚33的中心位置的连线呈

另一条直线。通过在沿第六边缘32的方向上将任意相邻两列中的第二引脚33交错设置,使得各个第二引脚33均交错设置,可以将绑定过程中短路风险降到最低。

67.结合图5和图6所示,在一些实施例中,第二引脚33至少满足以下条件之一:

68.在沿第五边缘31的方向上,相邻两个第二引脚33之间的间隔a大于或等于12μm;

69.在沿第六边缘32的方向上,相邻两列中的第二引脚33之间的间隔f大于或等于8μm。

70.相关技术的显示面板中各第二引脚以一列方式排布,因此,在沿第六边缘32的方向上,不存在相邻两列中的第二引脚33之间的间隔,而在沿第五边缘31的方向上,相邻两个第二引脚33之间的间隔a通常为5μm。在本技术实施例中,增加了每列中各第二引脚33之间的间隔a,可以在y轴方向满足第二引脚33之间的最小安全距离,将相邻两列中第二引脚33之间的间隔f设置为至少8μm,可以在x轴方向满足第二引脚33之间的最小安全距离,避免绑定过程中出现短路。

71.acf工艺除了对各第二引脚33之间的间隔有最小安全距离的要求,还对第二引脚33的面积有最小导通面积的要求,保证导通位置有足够多的金属粒子,以保证绑定的有效性。为了解决该问题,在本实用新型实施例中,增加第二引脚33的面积。

72.由于最小安全距离与最小导通面积相互制约,因此为了兼顾二者,需要对第二引脚33的尺寸进行合理设置。在一些实施例中,如图6所示,第二引脚33包括相互连接的第七边缘331和第八边缘332,第七边缘331的长度小于第八边缘332的长度,第二引脚33至少满足以下条件之一:

73.第七边缘331的长度c大于或等于50μm且小于或等于55μm;

74.第八边缘332的长度e大于或等于70μm且小于或等于80μm。

75.在相关技术中,显示面板的第二引脚的第七边缘的长度为35μm,第八边缘的长度为50μm,在本技术实施例中,50μm≤第二引脚33的第七边缘331的长度c≤55μm,70μm≤第二引脚33的第八边缘332的长度e≤80μm,增加了第二引脚33两个边缘的长度,相应增加第二引脚33的面积,可以达到最小导通面积的要求,保证绑定的有效性,同时也满足各第二引脚33之间的最小安全距离,避免绑定过程中出现短路。

76.本实用新型实施例还提供一种显示装置,结合图7和图8所示,所述显示装置包括集成电路芯片1和显示面板2,集成电路芯片1为如前所述的集成电路芯片,显示面板2为如前所述的显示面板,其中,第一引脚13与第二引脚33绑定连接。

77.在本技术实施例中,显示装置为柔性显示装置。

78.本实用新型实施例的显示装置包括集成电路芯片1和显示面板2,集成电路芯片1包括相互连接的第一边缘11和第二边缘12以及多个用于与显示面板进行绑定连接的第一引脚13,第一边缘11的长度小于第二边缘12的长度,各第一引脚13沿至少一个第一边缘11排列为至少两列;显示面板2包括衬底基板3,衬底基板3包括相互连接的第五边缘31和第六边缘32以及多个设置在衬底基板3所在表面的第二引脚33,第五边缘31的长度小于第六边缘32的长度,第二引脚33沿一个第五边缘31排列为至少两列。本实用新型实施例通过将各第一引脚13在集成电路芯片的短边以至少两列的方式排布,以及将各第二引脚33在显示面板的短边以至少两列的方式排布,在第一引脚13和第二引脚33数量不变的情况下,可以增加各第一引脚13之间的间隔以及各第二引脚33之间的间隔,这样就可以达到acf工艺要求

的最小安全距离,避免绑定过程中发生短路,由此可以实现tddi芯片采用cop封装方式进行封装。

79.图8为本实用新型实施例提供的显示装置中显示面板与集成电路芯片绑定的示意图,如图8所示,第二引脚33的尺寸大于第一引脚13的尺寸,在一些实施例中,集成电路芯片1和显示面板2至少满足以下条件之一:

80.第二引脚33的第七边缘331的长度c与第一引脚13的第三边缘131的长度b之差为30μm;

81.第二引脚33的第八边缘332的长度e与第一引脚13的第四边缘132的长度d之差为10μm。

82.在进行显示面板2与集成电路芯片1绑定连接的过程中,由于绑定设备自身不可避免存在误差,集成电路芯片1的第一引脚13与显示面板2的第二引脚33之间会出现偏移,通常,在x轴方向上最大偏移量为6μm,在y轴方向上最大偏移量为20μm。图9为相关技术的集成电路芯片与显示面板绑定偏移的示意图,如图9所示,在相关技术的显示装置中,集成电路芯片的第一引脚13和显示面板的第二引脚33均呈单列排布,因此发生绑定偏移会对y轴方向产生影响。

83.在发生y轴方向绑定偏移的情况下,第一引脚13与第二引脚33之间的最小间距f’=a-(y-(c-b)/2),其中,a为相邻两个第二引脚33之间的间隔,a=5μm,b为第一引脚13的第三边缘的长度,b=19μm,c为第二引脚33的第七边缘的长度,c=35μm,y为y轴方向的绑定偏移量,y=20μm,因此,第一引脚13与第二引脚33之间的最小间距f’=-7μm。由此可知,考虑发生绑定设备y轴方向偏移的情况下,相邻引脚间会出现搭接,引起短路的情况,无法满足acf绑定工艺中的最小安全距离7μm的要求。

84.另外,第一引脚13和第二引脚33的搭接面积为s,s=(b+(c-b)/2-y)*(d+(e-d)/2-x),其中,d为第一引脚13的第四边缘的长度,d=40μm,e为第二引脚33的第八边缘的长度,e=50μm,因此,搭接面积s=273μm2,也无法满足acf绑定的最小导通面积的要求650μm2。

85.图10为本实用新型实施例提供的集成电路芯片与显示面板绑定偏移的示意图,结合图3-6、8-10所示,在本实用新型实施例中,在发生x轴方向和y轴方向绑定偏移的情况下,集成电路芯片1与显示面板2之间至少满足以下之一:

86.在沿第五边缘31的方向上,第一引脚13与相邻的未绑定连接的第二引脚33之间的最小间距g=a-(y-(c-b)/2);

87.在沿第六边缘32的方向上,第一引脚13与相邻列中第二引脚33之间的最小间距h=f-(x-(e-d)/2);

88.第一引脚13和第二引脚33的搭接面积s=(b+(c-b)/2-y)*(d+(e-d)/2-x)。

89.其中,a为同一列中相邻两个第二引脚33之间的间隔,b为第一引脚13的第三边缘131的长度,c为第二引脚33的第七边缘331的长度,x为沿第六边缘32的方向的绑定偏移量,y为沿第五边缘31的方向的绑定偏移量,f为相邻列中两个第二引脚33之间的间隔,x、y和f为常数;d为第一引脚13的第四边缘132的长度,e为第二引脚33的第八边缘332的长度。

90.在本公开实施例中,g=a-(y-(c-b)/2)=25μm,可以满足7μm最小安全距离;h=f-(x-(e-d)/2)=15μm,可以满足7μm最小安全距离。搭接面积s=(b+(c-b)/2-y)*(d+(e-d)/2-x)=960μm2,可以满足650μm2的最小导通面积的要求。

91.由于tddi芯片中触控通道分布在tddi芯片的短边,相关技术的cop封装方式在用于绑定的引脚上的最小导通面积以及最小安全距离均无法满足acf的工艺要求。针对该问题,本实用新型实施例提出了一种“z”字形的引脚排布方式,通过对集成电路芯片和显示面板绑定区中引脚的排布及尺寸进行调整,满足了acf绑定工艺的相关要求,为后续柔性产品的tddi芯片采用cop封装方式奠定了基础。

92.本实用新型可以应用于柔性oled显示领域,尤其涉及tddi、cop以及fsloc(柔性单层外挂式触控面板)的应用。本实用新型方案应用于柔性oled显示领域,随着系统集成度变高,tddi芯片在柔性oled显示中的需求度开始变高,配合on-cell(外挂式触控)的触控解决方案以及cop方式的ic封装,可以实现高集成度,对比现有方案可大幅降低成本。

93.可以理解的是,以上实施方式仅仅是为了说明本实用新型的原理而采用的示例性实施方式,然而本实用新型并不局限于此。对于本领域内的普通技术人员而言,在不脱离本实用新型的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1