一种增强型氮化镓高电子迁移率晶体管结构的制作方法

1.本实用新型涉及hemt器件结构技术领域,尤其涉及一种增强型氮化镓高电子迁移率晶体管结构。

背景技术:

2.氮化镓(gan)材料作为第三代半导体,具有远超硅的临界击穿电场(4mv/cm)和电子峰值速度(3

×

107cm/s),在大功率、高频领域有广泛的应用前景。近来一种基于氮化镓的高电子迁移率晶体管的器件(hemt,high electron mobility transistor)被提出。

3.氮化镓高电子迁移率晶体管,利用氮化镓与铝镓氮异质结由于能带不匹配而形成的量子阱中的二维电子气导电。然而,由于二维电子气在没有外加电压的情况下就存在,需要外加电压耗尽这层二维电子气,才能实现器件的关断,所以氮化镓高电子迁移率晶体管是耗尽型的,即其阈值电压是负值。这对实际应用不利,因为为了使系统具有更好的可靠性,尤其使功率应用,我们往往希望晶体管是增强型的。现在主要的增强型氮化镓高电子迁移率晶体管的制造工艺如下:

4.1、级联(cascade)方式,分别制造一个耗尽型高电子迁移率晶体管和一个增强型金属氧化物半导体场效应晶体管(mosfet),并通过封装或者板级互连的方式,把它们串联起来。

5.2、栅槽刻蚀方式,通过刻蚀减薄栅下边的铝镓氮厚度,削弱栅区铝镓氮的极化效应,使栅压为0时,二维电子气处于被耗尽的状态。

6.3、氟(f)离子注入方式,在栅区铝镓氮中注入氟离子,抬高铝镓氮能带,耗尽二维电子气,使栅零压状态下,二维电子气被耗尽。

7.4、p型氮化镓工艺,在栅与铝镓氮之间插入一层p型掺杂的氮化镓,形成异质结,抬高氮化镓能带,耗尽二维电子气。

8.上述制造工艺2、3、4的工艺比较复杂,有很多问题需要解决,使制备后的晶体管的性能不稳定。目前比较常用的是上述制造工艺1的级联方式,即分别在两个晶圆上制造增强型硅金属氧化物半导体场效应晶体管和耗尽型氮化镓高电子迁移率晶体管,通过封装或者板级互连把它们级联起来。这种级联的方式主要有以下两方面的缺点:第一,级联器件选择增强型硅金属氧化物半导体场效应晶体管,它的温度稳定性,工作频率以及功率特性都不如氮化镓高电子迁移率晶体管,削弱了其优势。第二,集成方式选择板级和封装级的互连,这种方式互连寄生效应大,会影响级联系统的频率特性,并且分别封装制造封装成本比较高、难以减小系统体积。

技术实现要素:

9.为了解决上述技术问题,本实用新型提供了一种增强型氮化镓高电子迁移率晶体管结构,在氮化镓基功率器件上单片集成后端工艺晶体管,互连寄生效应小,提高了系统的频率特性,有利于系统体积的缩小和成本的降低。

10.为实现上述目的,本实用新型解决其技术问题所采用的技术方案是:所述增强型氮化镓高电子迁移率晶体管结构,包括氮化镓基功率器件,所述氮化镓基功率器件通过钝化层与后端工艺晶体管相连,所述钝化层内设置有导电柱,所述导电柱将所述氮化镓基功率器件的电极层与所述后端工艺晶体管的电极层相连。

11.所述钝化层内光刻有介质过孔,所述介质过孔内填充导电金属后形成所述导电柱。

12.所述钝化层的厚度为500~1000nm。

13.所述导电柱设置有多个,多个导电柱将所述氮化镓基功率器件的源电极ⅰ、漏电极ⅰ和栅电极ⅰ与所述后端工艺晶体管对应的源电极ⅱ、漏电极ⅱ和栅电极ⅱ相连分别形成源电极焊盘、漏电极焊盘和栅电极焊盘。

14.所述氮化镓基功率器件包括衬底,所述衬底上依次生长氮化镓层和铝镓氮层,所述铝镓氮层上设置源电极ⅰ、漏电极ⅰ和栅电极ⅰ,所述栅电极ⅰ与所述铝镓氮层之间设置绝缘介质层。

15.所述衬底和所述氮化镓层之间设置高阻缓冲层,和/或所述氮化镓层与所述铝镓氮层之间设置高阻缓冲层。

16.所述后端工艺晶体管包括碳纳米晶体管、氧化物半导体晶体管或二维材料晶体管。

17.所述后端工艺晶体管包括沉积在钝化层上的晶体管薄膜,所述晶体管薄膜的两端设置源电极ⅱ和漏电极ⅱ,所述源电极ⅱ、漏电极ⅱ与晶体管薄膜的上表面覆盖有栅极氧化层,所述源电极ⅱ和漏电极ⅱ之间的栅极氧化层上表面形成栅电极ⅱ。

18.本实用新型的有益效果是:

19.1、本实用新型采用后端工艺晶体管替代传统的硅金属氧化物半导体场效应晶体管与氮化镓基功率器件级联,在制备完成氮化镓基功率器件后,直接在后端工艺制备后端工艺晶体管,并通过层间介质导电柱进行互连,互连寄生效应小,提升了系统的频率特性,减小了系统的体积,降低了制备成本。

20.2、本实用新型采用碳纳米晶体管替代传统的硅金属氧化物半导体场效应晶体管与氮化镓基功率器件级联,由于碳纳米晶体管这些远超硅金属氧化物半导体场效应晶体管的特性,与氮化镓基功率器件连接更匹配,使整个晶体管结构具有更高的电子峰值速度、驱动能力、截止频率和温度稳定性等特性,弥补了硅金属氧化物半导体场效应晶体管的负面影响。

21.综上,本实用新型在氮化镓基功率器件上单片集成后端工艺晶体管,互连寄生效应小,提升了系统的频率特性,减小了系统的体积,降低了制备成本。

附图说明

22.下面对本实用新型说明书各幅附图表达的内容及图中的标记作简要说明:

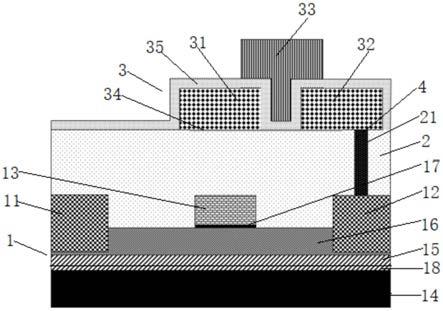

23.图1为本实用新型的结构示意图;

24.上述图中的标记均为:1.氮化镓基功率器件,11.源电极ⅰ,12.漏电极ⅰ,13.栅电极ⅰ,14.衬底,15.氮化镓层,16.铝镓氮层,17.绝缘介质层,18.高阻缓冲层,2.钝化层,21.介质过孔,3.后端工艺晶体管,31.源电极ⅱ,32.漏电极ⅱ,33.栅电极ⅱ,34.晶体管薄膜,35.

栅极氧化层,4.导电柱。

具体实施方式

25.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对实施例中的技术方案进行清楚、完整地描述,以下实施例用于说明本实用新型,但不用来限制本实用新型的范围。

26.在本实用新型的描述中,需要说明的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

27.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

28.本实用新型具体的实施方案为:如图1所示,一种增强型氮化镓高电子迁移率晶体管结构,包括氮化镓基功率器件1,氮化镓基功率器件1通过钝化层2与后端工艺晶体管3相连,钝化层2内设置有导电柱4,导电柱4将氮化镓基功率器件1的电极层与后端工艺晶体管3的电极层相连。本实用新型采用后端工艺晶体管3替代传统的硅金属氧化物半导体场效应晶体管与氮化镓基功率器件1级联,在制备完成氮化镓基功率器件1后,直接在后端工艺制备后端工艺晶体管3,并通过层间介质导电柱4进行互连,互连寄生效应小,提升了系统的频率特性,减小了系统的体积,降低了制备成本。

29.具体地,其中的钝化层2可选择氮化硅、氧化硅、氮化铝等绝缘材料通过等离子增强化学气相沉积或磁控溅射的方式生长在氮化镓基功率器件1的表面,钝化层2的厚度为500~1000nm,钝化层2内光刻有介质过孔21,介质过孔21内填充导电金属(如钨)后形成导电柱4,以实现两种晶体管的互联。

30.具体地,其中的导电柱4设置有多个,多个导电柱4将氮化镓基功率器件1的源电极ⅰ11、漏电极ⅰ12和栅电极ⅰ13与后端工艺晶体管3对应的源电极ⅱ31、漏电极ⅱ32和栅电极ⅱ33相连分别形成源电极焊盘、漏电极焊盘和栅电极焊盘,实现了两种晶体管的电性连接。

31.具体地,其中的氮化镓基功率器件1包括由硅、蓝宝石、碳化硅、氮化镓等材料制备的衬底14,衬底14上通过化学气相沉积的方法依次外延生长氮化镓层15和铝镓氮层16,铝镓氮层16上设置源电极ⅰ11、漏电极ⅰ12和栅电极ⅰ13,栅电极ⅰ13与铝镓氮层16之间设置绝缘介质层17,该绝缘介质层17可由氮化硅制备,提高了绝缘性能。其中的衬底14和氮化镓层15之间可设置高阻缓冲层18,也可在氮化镓层15与铝镓氮层16之间设置高阻缓冲层18,用于吸收应力,以获得更好的外延结构。

32.具体地,其中的后端工艺晶体管3指在后端工艺可以制造的晶体管,主要有两个要求:第一,沟道材料能够在后端工艺获得;第二,制备工艺不涉及足以损坏前端工艺器件和后端工艺互连的高温过程。满足上述要求的晶体管包括碳纳米晶体管、氧化物半导体(igzo、iwo、ito等)晶体管或二维材料(mos2、wse2等)晶体管,其中,碳纳米晶体管具有极高

的载流子迁移率(~10000cm2v-1

s-1

),文献报道的电子峰值速度可达3

×

107cm/s,截止频率可达300ghz,温度稳定性0.5%/300k-80k,驱动电流可达ma/um量级。碳纳米晶体管这些远超硅金属氧化物半导体场效应晶体管的特性,使其比硅金属氧化物半导体场效应晶体管更适合用于增强型氮化镓高电子迁移率晶体管的级联结构,使整个晶体管结构具有更高的电子峰值速度、驱动能力、截止频率和温度稳定性等特性,弥补了硅金属氧化物半导体场效应晶体管的负面影响。另外,由于硅金属氧化物半导体场效应晶体管不能在后端工艺制造,只能通过封装或者板级互连的方式级联,带来极大的寄生效应,引起功耗和延时的损失。而碳纳米晶体管可以在后端工艺制造,可以跟制备好的氮化镓高电子迁移率晶体管在芯片内级联,通过层间介质过孔21互连,寄生效应显著减小。

33.其中的后端工艺晶体管3包括沉积在钝化层2上的晶体管薄膜34,晶体管薄膜34的两端设置源电极ⅱ31和漏电极ⅱ32,源电极ⅱ31、漏电极ⅱ32与晶体管薄膜34的上表面覆盖有栅极氧化层35,源电极ⅱ31和漏电极ⅱ32之间栅极氧化层35上表面的沟道通过湿法转移等低温转移工艺获得,在沟道上沉积金属形成栅电极ⅱ33。

34.综上,本实用新型在氮化镓基功率器件上单片集成后端工艺晶体管,互连寄生效应小,提升了系统的频率特性,减小了系统的体积,降低了制备成本。

35.以上所述,只是用图解说明本实用新型的一些原理,本说明书并非是要将本实用新型局限在所示所述的具体结构和适用范围内,故凡是所有可能被利用的相应修改以及等同物,均属于本实用新型所申请的专利范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1