具有切割对位记号的导线架组件的制作方法

1.本实用新型涉及一种导线架,特别是涉及一种具有切割对位记号的导线架组件。

背景技术:

2.一般导线架于设置芯片并封装形成导线架封装组件后,会利用形成于导线架之边框的对位孔作为切割对位记号,对所述导线架封装组件的切单(dicing),以得到独立的封装晶粒。

3.然而,目前用于封装后切割的切割对位孔是于导电片材蚀刻形成具有多个导线架单元的导线架结构时,即同时形成于所述导线架结构的边框。因此,当对所述导线架结构利用封胶以模注方式进行封装时,由于所述导线架结构于模注过程与模具的对位误差或是模注封胶过程推挤因素,导致封装后形成的导线架组件的封胶层与切割对位孔之间会有偏移问题,因此,当利用所述切割对位孔对所述导线架组件进行对位切割时,容易发生切割对位不精确,使得切割后的各个封装单体产生尺寸面积差异过大的问题。

技术实现要素:

4.本实用新型的目的在于提供一种具有切割对位记号的预成型导线架。

5.本实用新型具有切割对位记号的导线架组件包含导线架主体、封胶单元,及多个切割对位单元。

6.所述导线架主体由导电材料构成,包括多个导线架单元、外框,及多个形成于所述外框的贯通孔,所述导线架单元成阵列排列且彼此连接,所述外框框围所述导线架单元并与至少部分邻近所述外框的所述导线架单元彼此连接。

7.所述封胶单元具有填置于每一个导线架单元的间隙、任相邻的导线架单元之间的间隙的下胶部,及形成于所述导线架单元的顶面的上胶部。

8.所述切割对位单元分别位于所述贯通孔。每一个切割对位单元具有填置于相应的贯通孔并与所述封胶单元于同一制程形成的胶层,及由所述胶层定义出且口径小于所述贯通孔的切割对位孔,且所述切割对位单元可形成至少一沿一x方向延伸的第一切割定位线,及至少一沿y方向延伸的第二切割定位线。

9.较佳地,本实用新型具有切割对位记号的导线架组件,其中,所述导线架单元沿所述x方向及所述y方向成阵列排列分布,所述外框框围所述导线架单元而成四边形,且至少其中一贯通孔对应形成于所述外框的其中一顶角。

10.较佳地,本实用新型具有切割对位记号的导线架组件,其中,对应位于所述其中一顶角的所述贯通孔的切割对位单元具有两个切割对位孔,且所述两个切割对位孔分别位于所述外框相邻的两个侧边。

11.较佳地,本实用新型具有切割对位记号的导线架组件,其中,所述导线架单元沿所述x方向及所述y方向成阵列排列分布,所述外框框围所述导线架单元而成四边形,所述贯通孔至少位于所述外框的相邻的两个侧边,且所述至少一第一切割定位线,及所述至少一

第二切割定位线分别与所述两个侧边平行。

12.较佳地,本实用新型具有切割对位记号的导线架组件,其中,所述切割对位单元的胶层、所述导线架单元、所述外框及所述下胶部的顶面齐平而位于同一平面。

13.较佳地,本实用新型具有切割对位记号的导线架组件,其中,所述封胶单元还包含外框胶部,所述外框胶部形成于所述外框的顶面并令所述切割对位单元对外裸露。

14.较佳地,本实用新型具有切割对位记号的导线架组件,其中,每一个导线架单元具有至少一供用于设置半导体芯片的芯片座,所述上胶部框围所述导线架单元的芯片座,且令每一个芯片座的至少部分表面对外裸露。

15.较佳地,本实用新型具有切割对位记号的导线架组件,其中,所述外框胶部与所述上胶部的顶面齐平。

16.本实用新型的有益效果在于:通过令用于切割对位的切割对位孔与所述封胶单元于同一制程形成,而可避免现有于模注形成封胶层的过程因导线架与模具的对位误差,导致后续形成的封胶层与导线架的切割对位孔的对位产生偏移,而造成封装切割后的封装单体的面积误差问题。

附图说明

17.本实用新型的其他特征及功效,将于参照附图的实施方式中清楚地呈现,其中:

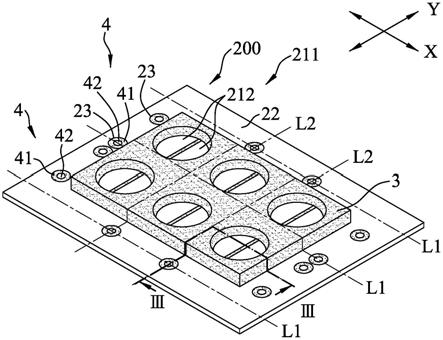

18.图1是说明本实用新型的实施例的俯视示意图;

19.图2是说明本实用新型所述实施例的导线架主体的一示意图;

20.图3是说明图1中iii-iii割线的剖视结构;

21.图4是说明所述切割对位单元的另一实施态样的一局部放大示意图,及

22.图5是说明所述封胶单元的另一实施态样的示意图。

具体实施方式

23.在本实用新型被详细描述之前,应当注意在以下的说明内容中,类似的组件是以相同的编号来表示。此外,附图中仅为表示组件及膜层之间的空间关系,并非各组件及膜层的实质厚度、尺寸或相对比例关系。

24.本实用新型具有切割对位记号的导线架组件是用于供半导体芯片封装,并提供封装后切单过程可供切割对位的切割对位记号,以提升切割对位的精准度。于本实用新型的所述半导体芯片是以发光二极管芯片为例说明,然实际实施时并不以此为限。

25.接着,以下述实施例详细说明本实用新型具有切割对位记号的导线架组件。

26.参阅图1~图3,本实用新型具有切割对位记号的导线架组件200的一实施例,包含导线架主体2、封胶单元3,及多个切割对位单元4。

27.所述导线架主体2由导电材料,例如铜系合金或铁镍合金材料构成,包括多个导线架单元21、外框22、多个形成于所述外框22的贯通孔23,及多条连接引脚24。

28.所述导线架单元21沿一x方向及一y方向成阵列排列分布而概成四边形且彼此连接,且每一个导线架单元21具有至少一芯片座211。于本实施例中所述导线架单元21是以供封装发光二极管芯片为例,因此,所述每一个导线架单元21的芯片座211是以具有两个彼此成一间隙间隔的接触电极212为例说明。

29.所述外框22会框围所述导线架单元21而概成四边型,且所述贯通孔23为形成于所述外框22的至少两侧边。图1中是以所述贯通孔23为分别形成于所述外框22的四个侧边的圆孔,且所述外框22的每一侧边均具有多个贯通孔23为例,然而,实际实施时,所述贯通孔23的形状也可以为方型、椭圆、不规则型并无需特别限制,且所述贯通孔23也可以是仅形成于所述外框22的其中相邻两侧边,或相对两侧边,只要是可以让后续借由形成于所述贯通孔23内的切割对位单元4可形成至少一条沿所述x方向延伸的第一切割定位线l1,及至少一条沿所述y方向延伸的第二切割定位线l2即可。

30.所述连接引脚24用于连接所述导线架单元21,以及所述外框22与所述导线架单元21,而可令所述外框22可与至少部分邻近所述外框22的所述导线架单元21彼此连接,进而让所述导线架单元21与所述外框22连接成一体而不分散。于本实施例中是以任相邻的导线架单元21的接触电极212之间,以及与所述外框22相邻的所述导线架单元21的接触电极212,均有多条用于连接的连接引脚24为例,然而,要说明的是,所述连接引脚24的数量、形状及位置可视实际设计及需求而有所不同,并不以此为限。

31.所述封胶单元3具有一填置于任相邻的导线架单元21之间的间隙及每一个导线架单元21的间隙的下胶部31,及一形成于所述导线架单元21及所述下胶部31顶面的上胶部32。所述上胶部32框围所述导线架单元21的芯片座211(接触电极212),且令每一个芯片座211(接触电极212)的至少部分表面对外裸露。

32.所述切割对位单元4分别位于所述贯通孔23。具体的说,以所述贯通孔23为如图1所示分别形成于所述外框22的四个侧边的圆孔为例说明:每一个切割对位单元4具有一填置于相应的一贯通孔23且与所述封胶单元3于同一制程形成的胶层41,及由所述胶层41定义出且口径小于所述贯通孔23的一切割对位孔42,且通过所述切割对位单元4可形成多条沿所述x方向延伸的第一切割定位线l1,及多条沿所述y方向延伸的第二切割定位线l2。且所述切割对位单元4的胶层41、所述导线架单元21,及所述下胶部31的顶面齐平而位于同一平面。

33.要说明的是,所述切割对位孔42的形状可以如图1所示为圆形,或是哑铃形、椭圆,或是其它对称性或非对称性图案,只要是具有可供对位之几何中心即可,并无需特别限制。

34.此外,配合参阅图4,每一个贯通孔23内的切割对位孔42可以如图1所示为一个,也可以如图4所示,所述贯通孔23可以分别形成所述外框22的四个顶角(图4仅显示形成于其中一个顶角及其中一侧边的贯通孔23)并延伸至相邻的两侧边而具有哑铃状,而对应位于每一个贯通孔23的切割对位单元4,则可通过所述胶层41分别于相邻两侧边各定义出一切割对位孔42,而于每一个贯通孔23形成具有2个切割对位孔42的切割对位单元4;或是让位于所述外框22侧边的其中至少部分的贯通孔23内的切割对位单元4具有2个或多个切割对位孔42,同样也可利用所述切割对位孔42对位而形成多条第一切割定位线l1,及多条第二切割定位线l2。

35.参阅图5,于一些实施例中,所述封胶单元3还可再具有一外框胶部33。其中,所述外框胶部33对应形成所述导线架主体2的外框22顶面并至少令所述切割对位单元4的切割对位孔42对外裸露,且所述外框胶部33与所述上胶部32的顶面齐平。利用所述外框胶部33可让整体切割高度更平均。

36.接着,将所述实施例的制作方法说明如下:

37.(a)首先,提供一由铜、铜系合金或铁镍合金导电材料构成的基片,将所述基片不必要的部分蚀刻移除,得到如图2所示的所述导线架主体2。

38.(b)准备一模具(图未示),所述模具具有供所述导线架主体2对位的对位单元,以及多个对应位于所述外框22的所述贯通孔23位置设置且径宽小于所述贯通孔23的定位柱。

39.(c)将所述导线架主体2置入所述模具对位并同时令所述定位柱插入所述贯通孔23。然后,将一高分子封胶材料注入所述模具中,让所述高分子封胶材料填充于所述导线架主体2的间隙并延伸覆盖所述接触电极212的部分顶面,以及填充于所述贯通孔23中未被所述定位柱占据的间隙。待所述高分子封胶材料固化后将整体自所述模具取出并将所述定位柱自所述贯通孔23移出,即可得到如图1所示所述具有切割对位记号的导线架组件。其中,于模注过程填入所述贯通孔23的间隙的高分子封胶材料固化后即为所述胶层41,而所述定位柱移除后形成的通孔即为所述切割对位孔42。

40.当利用前述所述具有切割对位记号的导线架组件进行芯片封装得到导线架封装组件,并进行封装晶粒切单时,即可利用所述切割对位单元4形成的第一切割定位线l1及第二切割定位线l2作为切割对位依据,依序对所述导线架封装组件进行切割,即可得到各自独立的封装单体。

41.综上所述,本实用新型具有切割对位记号的导线架组件,由于所述切割对位单元4是与所述封胶单元3于同一制程形成,因此具有相同的对位条件,而可避免习知用于切割对位的切割对位孔与封胶层是于前、后不同制程形成,导致封胶层与对位切割孔之间产生对位误差,而造成后续切割后的封装单体的尺寸误差问题,所以确实可达成本实用新型的目的。

42.以上所述,仅为本实用新型的实施例而已,当不能以此限定本实用新型实施的范围,即凡依本实用新型权利要求书及说明书内容所作的简单的效变化与修饰,皆仍属本实用新型的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1