具有加强隔离的多芯片封装的制作方法

1.本公开涉及经封装半导体隔离(iso)装置,且更具体来说,涉及经封装多芯片iso装置。

背景技术:

2.在用于存在高电压(hv)的应用(例如用于电动机控制)的电路设计中,通常有必要采取措施来降低对电气系统的用户的潜在风险。这些措施传统上包含绝缘、接地及通过建立与hv的电介质分离来隔离危险的hv电平。已知用于在集成电路(ic)裸片之间的通信通道中跨越电介质分离传递信号信息及功率的技术。经封装iso装置防止直流电(dc)及非所要ac电流在一个裸片上的其输入与另一裸片上的其输出之间传播,同时允许所要ac信号在裸片之间发射。

3.iso装置使用第一与第二ic裸片之间的具有高击穿电压及低电流泄漏的隔离势垒来实现此功能。跨隔离势垒存在高电阻路径,但iso装置仍然可通过电容耦合、电感耦合(变压器隔离)或光学耦合将编码在所要ac信号中的信息跨过隔离势垒从一个ic裸片传递到另一ic裸片。在变压器隔离的情况下,已知磁增强叠层变压器,其包括具有磁场增强磁芯的线圈1(具有n1匝)及线圈2(具有n2匝),所述磁场增强磁芯包括通常包括铁氧体的顶部磁芯及底部磁芯。

4.一些市售iso装置包括具有5kv均方根(rms)加强隔离额定值的dc/dc转换器,其经设计以将高效的隔离功率提供到需要具有经良好调节的输出电压的偏压电源的隔离电路。此iso装置包含变压器及dc/dc控制器,其可以高功率转换效率及低电磁干扰(emi)提供500mw(典型)的隔离功率。

5.在隔离用于使系统能够正常运作但不一定用作防止电击的势垒的情况下,其常规地被称为功能隔离。在只要绝缘势垒完好无损隔离就能提供足够的防电击保护的情况下,其常规地被称为基本隔离。安全法规要求基本隔离辅以用于冗余的次级隔离势垒,使得即使第一iso势垒失效,额外势垒也提供电击保护。这常规地被称为双重隔离。为了使包括iso装置的系统紧凑并节省成本,希望仅具有一个级别的隔离,其具有所需电强度、可靠性及常规地由两个级别的基本隔离提供的冲击保护。这种隔离布置常规地被称为加强隔离。

技术实现要素:

6.提供本发明内容以依简化形式介绍所公开的概念的简要选择,这些概念在下文包含所提供的附图的具体实施方式中进一步描述。本发明内容不意在限制所主张的标的物的范围。

7.所公开的方面认识到遵守由例如保险商实验室(ul)1577、国际电工委员会(iec)60747及ul60950的各种工业标准定义的漏电规则,归因于缺乏经暴露裸片垫而限制常规加强iso装置封装(例如,包含支持具有ic裸片-ic裸片隔离的dc/dc转换器的两个ic裸片)的热耗散能力,且因此阻碍此类iso装置封装支持高输出功率(例如,》1w)应用。iso装置封装

的大小也被常规地扩大以满足漏电要求。

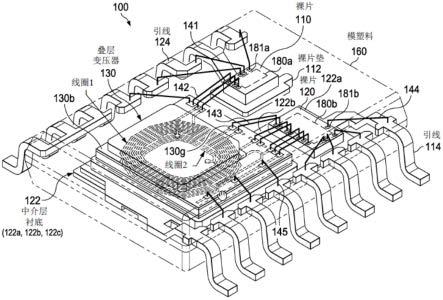

8.所公开的方面包含通过添加经隔离中介层衬底来解决具有加强隔离封装的常规iso装置封装的上述问题的解决方案,这种及中介层衬底包含作为都可为铜的顶部与底部金属层之间的导热介电层。所公开的iso装置封装包含含有发射器或接收器的第一ic裸片及含有发射器或接收器的第二ic裸片,其中叠层变压器提供耦合在相应ic裸片上的发射器及接收器之间的加强隔离。

9.所公开的方面包含一种多芯片iso装置封装,所述多芯片iso装置封装包含:引线框架,其包含引线;中介层衬底,其包含顶部铜层及底部金属层,介电层在中间。第一ic裸片及第二ic裸片都包含含有发射器或接收器的电路,且所述第一ic裸片上的第一接合垫及所述第二ic裸片上的第二接合垫顶侧朝上附接在所述封装中。叠层变压器附接到定位成横向于所述ic裸片的所述顶部铜层。接合线将所述第一接合垫线接合到所述叠层变压器上的第一垫及所述引线或引线端子的第一群组,且接合线将所述第二接合垫线接合到所述叠层变压器上的第二垫及所述引线或所述引线端子的第二群组,且模塑化合物为所述iso装置封装提供囊封。

附图说明

10.现在将参考附图,这些附图不一定按比例绘制,其中:

11.图1是展示实例多芯片iso装置封装的顶部透视图,其包含:第一ic裸片,其包含包括发射器或接收器的电路;及第二ic裸片,其包含包括发射器或接收器的电路,使得封装提供至少一个通信通道;及叠层变压器,其安装到中介层衬底,所述中介层衬底上具有耦合在相应ic裸片的发射器及接收器之间的叠层变压器,这提供加强隔离。

12.图2a是描绘多芯片iso装置封装的俯视视图,其包含安装到中介层衬底的叠层变压器。提供在此图的右侧的此iso装置封装的仰视图展示中介层衬底的介电层上的底部金属层。

13.图2b是沿图2a中展示的切割线a-a截取的图2a中展示的iso装置封装的侧横截面视图,其中顶部铜层是图案化层,其展示顶部铜层上的第一ic裸片,所述第一ic裸片具有线接合到位于中介层衬底上的叠层变压器的叠层电介质上的接合垫的接合垫。

14.图2c是沿图2a中展示的切割线b-b截取的图2a中展示的iso装置封装的侧横截面视图,其展示裸片垫上的第二ic裸片,所述第二ic裸片具有线接合到位于中介层衬底的顶部铜层上的叠层变压器的叠层电介质上的接合垫的接合垫。

15.图2d是描绘实例多芯片iso装置封装的俯视图,其包含安装到中介层衬底上的叠层变压器。在这种布置中,顶部铜层是图案化层,且中介层衬底本质上占据封装的整个区域,使得叠层变压器以及第一ic裸片及第二ic裸片都在中介层衬底的顶部铜层的区域上。

16.图2e是描绘实例多芯片iso装置封装的俯视图,其包含安装到中介层衬底上的叠层变压器。在这种布置中,中介层衬底仅占据封装的足够区域,使得叠层变压器位于其上,且存在用于第一ic裸片及第二ic裸片的引线框架的分开的裸片垫。

17.图3是展示根据实例方面的用于形成多芯片iso装置封装的实例方法中的步骤的流程图,所述多芯片iso装置封装包含安装到中介层衬底上的叠层变压器。

具体实施方式

18.参考附图描述实例方面,其中类似参考数字用于表示类似或等效元件。所说明的动作或事件的顺序不应被认为是限制性的,因为一些动作或事件可以不同顺序发生及/或与其它动作或事件同时发生。此外,可不需要一些所说明的动作或事件来实施根据本公开的方法。

19.此外,如本文使用的术语“耦合到”或“与

…

耦合”(及类似者)在不进一步限定的情况下意在描述间接或直接电连接。因此,如果第一装置“耦合”到第二装置,那么连接可通过直接电连接(其中只有路径中存在寄生)或通过经由包含其它装置及连接的中介项的间接电连接。对于间接耦合,中介项通常不修改信号的信息,但可调整其电流电平、电压电平及/或功率电平。

20.所公开的方面认识到中介层衬底(例如具有拥有相当好的热导率的陶瓷芯介电层(例如氧化铝或氮化铝)的直接接合铜(dbc)衬底)的使用以至少2种方式促进多芯片iso装置封装的性能。陶瓷芯材料在封装内部及外部提供iso装置封装的hv及低电压节点之间的电隔离。中介层衬底的通常较厚的顶部铜层与中介层衬底的介电层通常包括的陶瓷材料的相对较高热导率组合帮助增强热耗散,这实现更高功率多芯片iso装置封装解决方案。已知的多芯片iso装置封装解决方案(例如经暴露裸片附接垫(dap)小外形集成电路(soic)封装)是非隔离的,且通常也违反漏电要求。

21.所公开的iso装置大体上提供具有经暴露热垫的最小面积封装,其满足加强隔离要求。中介层衬底的底部厚铜层提供增强的热传递能力。底部铜层还使得能够附接散热器,所述散热器将归因于芯陶瓷材料的介电特性而与封装内部的第一ic裸片及第二ic裸片组件隔离。

22.图1是展示实例多芯片iso装置封装100的顶部透视图,其包含:第一ic裸片110,其包含包括发射器或接收器的电路;及第二ic裸片120,其包含包括发射器或接收器的电路,使得封装提供至少一个通信通道。iso装置封装100还包括安装到中介层衬底122(例如,dbc衬底,例如针对其介电层122b,包含陶瓷,例如氧化铝(al2o3)、氮化铝(aln)或氮化硅)的叠层变压器130,所述中介层衬底包含顶部铜层122a及底部金属层122c,其中介电层122b位于这些金属层之间。

23.叠层变压器130位于顶部铜层122a上,其中变压器130耦合在相应ic裸片110、120的发射器与接收器之间,这提供加强隔离。叠层变压器130通常支持在一分钟测试时间内的至少1kv的均方根(rms)击穿电压,从而通常提供至少2.5kv到5kv的击穿电压。ucc12050根据ul1577进行一分钟的击穿测试,ul1577是隔离装置的最流行的标准之一。

24.中介层衬底可包括除dbc衬底之外的衬底,例如也可用作中介层的绝缘金属衬底(ims)。此项技术中已知的ims由金属底板(通常使用铝,因为其低成本及密度)组成,所述金属底板由薄介电层(通常是环氧基层,通常是fr-4)及顶部铜层(通常约35μm到超过200μm厚)覆盖。基于fr-4的电介质通常提供为薄的(约100μm厚),因为与dbc衬底中使用的陶瓷相比,其具有更低热导率。作为另一替代方案,中介层衬底还可包含活性金属钎焊衬底(amb),其中使用锡膏将金属箔焊接到陶瓷。与dbc相比,amb通常是更高成本的布置,但从技术上来说,amb与dbc具有本质上相同的配置。

25.在iso装置封装操作期间通常是iso装置封装中的最热组件的叠层变压器130附接

到中介层衬底122的顶部铜层122a使得由叠层变压器130产生的热能够垂直地传导出去。iso装置封装100的热传递路径首先通过顶部铜层122a,接着通过介电层122b,且接着最后从底部金属层122c离开到用作iso装置封装100的散热器的环境。

26.如上文提及,介电层122b可包括陶瓷层,其可在20℃下提供至少20w/m

·

k的热导率。例如,氧化铝在20℃下具有28到35w/m

·

k的热导率,氮化铝在20℃下具有约70到180w/m

·

k的热导率,氮化硅在20℃下具有约30w/m

·

k的热导率。

27.例如,针对图1中的iso装置封装100展示中介层衬底122,所述中介层衬底122为l形以容纳叠层变压器130及第二ic裸片120。在此实例中,第一ic裸片110横向于中介层衬底122的区域,且代替地位于横向于中介层衬底122的区域的引线框架的裸片垫112上。

28.在一些所公开的布置中,中介层衬底122还可本质上占据iso装置封装的整个区域,使得叠层变压器130以及第一及第二ic裸片110、120都在中介层衬底122的图案化顶部铜层122a部分上。在下文描述的图2d中展示此布置。在另一布置中,中介层衬底122仅占据封装的足够区域,使得叠层变压器130位于其上,且存在用于第一ic裸片110及第二ic裸片120的引线框架的分开裸片垫。在下文描述的图2e中展示此另一布置。

29.底部金属层122c可包括铜或铝。在裸片垫112上展示包含电路180a及接合垫181a的第一ic裸片110,而在中介层衬底122的顶部铜层122a上展示包含电路180b及接合垫181b的第二ic裸片120。此项技术中已知的ic裸片110、120上的电路180a、180b包括形成于半导体衬底中(例如在块状衬底上的外延层中)的电路元件(包含晶体管,且通常包含二极管、电阻器、电容器等),所述电路元件经配置在一起以通常各自实现至少一个发射器或接收器,其中ic裸片中的至少一者提供至少一个额外电路功能。实例额外电路功能包含模拟(例如,放大器或功率转换器)、射频(rf)、数字或非易失性存储器功能。

30.顶部铜层122a经蚀刻或以其它方式图案化以允许将第二ic裸片120与叠层变压器130电隔离。在图1中未展示的第一及第二ic裸片110、120都在叠层变压器130上的情况下,顶部铜层122a经图案化以将第一及第二ic裸片110、120彼此隔离,并提供与叠层变压器130的隔离。

31.在iso装置封装100的一个侧上的引线被展示为124,且在iso装置封装100的与引线124相对的另一侧上展示引线114。在一些引线124与第一ic裸片110上的一些接合垫181a之间存在展示为141的接合线,且在第一ic裸片110上的一些接合垫181a与叠层变压器130的叠层电介质130b上的一些接合垫130g之间存在接合线142。如此项技术中已知,展示为叠层电介质130b的物体通常包括叠层衬底,所述叠层衬底具有多个金属层(层级),其在相应金属层之间具有穿过电介质材料的通孔连接以将所有信号带到叠层衬底的最上表面。因此,ic裸片110、120与叠层变压器130之间的接合线142、143通常将形成与叠层衬底的最上铜层的连接件,其连接到叠层变压器130的顶部芯(展示为线圈2)或底部芯(展示为线圈1)。

32.因此,在叠层变压器130上的一些接合垫130g与第二ic裸片120上的一些接合垫181b之间存在接合线143,且在第二ic裸片120上的一些接合垫181b与一些引线114之间存在一些接合线144。在叠层变压器130上的一些接合垫130g与一些引线114之间也存在接合线145。还展示模塑化合物160。

33.尽管中介层衬底122在图1中展示为跨越iso装置封装100的足以容纳叠层变压器130及展示为第二ic裸片120的ic裸片中的一者的区域,但情况不必如此,例如在引线框架

包含用于安装第一ic裸片110及第二ic裸片120的第一裸片垫及第二裸片垫的情况下。因此,中介层衬底122的顶部铜层122a可在其上具有两个ic裸片及叠层变压器130中的任一者,ic裸片110、120及叠层变压器130中的两者,或仅具有叠层变压器130。在这种情况下,顶部铜层122a经图案化,ic裸片110、120都可安装在中介层衬底122的介电层122b上,或一个或两个ic裸片110、120可具有介电层122b上的顶部铜层122a的分开区域以提供装置隔离。

34.应注意,在中介层衬底122包括dbc衬底的情况下,因为dbc衬底通常比引线框架布置更昂贵,所以通常最好保持dbc衬底的面积尽可能小。其上具有所有组件(叠层变压器130、第一ic裸片110及第二ic裸片120)的更大面积dbc衬底的优点是热效益。具有大面积的顶部铜层122a通过利用更大的面积来帮助热扩散。因此,针对iso装置封装100,存在成本与热性能之间的折衷。

35.尽管图1中展示的多芯片iso装置封装100仅包含2个ic裸片110、120,但当需要时,所公开的多芯片iso装置封装可具有多于2个ic裸片。例如,在一个所公开的多芯片iso装置封装中,可包含3个ic裸片而不是仅包含2个ic裸片。因此,所公开的多芯片iso装置封装提供取决于终端应用的可伸缩性。

36.所公开的多芯片ic装置封装通常可用于任何电力电子电路拓扑,而不仅用于dc-dc转换器。除dc-dc转换器之外的实例还可包含数字隔离器、隔离式反激控制器、隔离式模/数转换器(adc)、隔离式栅极驱动器及隔离式放大器。

37.图2a是描绘实例多芯片iso装置封装200的俯视图,其包含安装到中介层衬底122的叠层变压器130以及第一及第二ic裸片110、120。叠层变压器130通常包括各自具有磁场增强磁芯的线圈1(具有n1匝)及线圈2(具有n2匝),所述磁场增强磁芯包括通过展示为130b的叠层电介质彼此隔开的顶部磁芯130a及底部磁芯130c(通常都包括铁氧体)。提供在此图的右侧的此iso装置封装200的仰视图展示中介层衬底122b的介电层122b上的底部金属层122c。在此布置中,类似于其中仅展示为第二ic裸片120的ic裸片中的一者及叠层变压器130位于中介层衬底122上的图1,中介层衬底122再次具有足够大的面积以容纳叠层变压器130以及现在展示为第一ic裸片110的ic裸片中的一者,而第二ic裸片120展示为横向于中介层衬底122的区域,而不是在引线框架的裸片垫112上。

38.图2b是沿图2a中展示的切割线a-a截取的图2a中展示的iso装置封装200的侧横截面视图,其中顶部铜层122a是图案化层。图2b展示中介层衬底的顶部铜层122a的一部分上的第一ic裸片110,所述第一ic裸片110具有通过接合线142线接合到叠层变压器130的叠层电介质130b的接合垫130g的接合垫181a,所述叠层变压器130也在顶部铜层122a的另一部分上。展示模塑化合物160,其中中介层衬底122的底部金属层122c展示为从iso装置封装200暴露以为叠层变压器130提供增强冷却。

39.图2c是沿图2a中展示的切割线b-b截取的图2a中展示的iso装置封装200的侧横截面视图,其展示裸片垫112上的第二ic裸片120。第二ic裸片120具有线接合到叠层变压器130的叠层电介质130b上的接合垫130g的接合垫181b,其中叠层变压器130位于中介层衬底122的顶部铜层122a上。可看到第二ic裸片120横向于中介层衬底122,而不是在引线框架的裸片垫112上。

40.可如图2b中那样再次看到中介层衬底122的底部金属层122c从iso装置封装200的底侧暴露。所公开的布置可自由地选择iso装置封装的冷却侧。例如,如果终端应用需要顶

侧冷却封装,那么通过翻转图2c中展示的iso装置封装200的视图,也可在iso装置封装的顶侧上暴露中介层衬底的背侧(例如用于dbc衬底的铜)以用于顶侧散热器附接。

41.图2d是描绘实例多芯片iso装置封装240的俯视图,其包含安装到展示为122l的中介层衬底的叠层变压器130。在此布置中,中介层衬底122l本质上占据iso装置封装240的整个区域,使得叠层变压器130以及第一ic裸片110及第二ic 120都位于中介层衬底122l的顶部铜层122a的分开(图案化)区域上。

42.图2e是描绘实例多芯片iso装置封装260的俯视图,其包含安装到展示为122s的中介层衬底上的叠层变压器130。在此布置中,中介层衬底122s仅占据iso装置封装260的足够区域,使得叠层变压器130位于其上,且引线框架为相应ic裸片提供分开的裸片垫,其中为第一ic裸片110提供裸片垫112a且为第二ic裸片120提供另一裸片垫112b。

43.图3是展示根据实例方面的用于形成多芯片iso装置封装的实例方法300中的步骤的流程图,所述多芯片iso装置封装包含安装到隔离中介层衬底上的叠层变压器。展示为“原材料准备”的步骤301包括提供第一ic裸片110、第二ic裸片120、叠层变压器130、中介层衬底122及包含引线或引线端子(图1中展示的引线114、124)的引线框架,所述引线框架任选地包含一或多个裸片垫。取决于封装设计,如上文描述,引线框架可包含0、1或2个裸片垫,其中ic裸片可位于裸片垫上,或直接位于中介层衬底的顶部铜层上,其中顶部铜层任选地是图案化层。在引线框架不提供裸片垫(仅引线或引线端子)的情况下,中介层衬底可具有足以容纳iso装置封装的所有组件的面积,例如上文描述的图2d中展示。

44.步骤302包括将引线框架(通常为引线框架面板/阵列)安装到夹具上,且接着拾取引线框架的引线或引线端子内部的中介层衬底并将其放置到夹具上。夹具可提供引线框架与中介层衬底之间的精确对准以使得能够将中介层衬底放置在引线框架中的开口内,且引线框架上的拉杆可用于将中介层衬底物理连接到引线框架面板/阵列。这种物理连接可通过使用粘合材料连同回流步骤或使用机械夹紧来实现。步骤303包括在中介层衬底的顶部铜层上及任选地在一或多个裸片垫上施配粘合剂。如上文提及,粘合剂通常具有至少2w/m

·

k@20℃,例如至少20w/m

·

k@20℃的热导率。

45.步骤304包括拾取叠层变压器并将其放置在中介层衬底的顶部铜层上的粘合剂上,且当顶部铜层是图案化层时将第一ic裸片及第二ic裸片放置在中介层衬底的顶部铜层上的粘合剂上,或当引线框架包含裸片垫时将第一ic裸片及第二ic裸片放置在裸片垫上。步骤305包括固化或回流工艺以使粘合剂固化,例如在约200℃的温度下固化约一分钟。步骤306包括线接合。步骤307包括模制工艺以形成模塑化合物,且步骤308包括封装修整及成形,包含切割引线框架的拉杆。

46.所公开的方面可集成到各种组装流程中以形成各种不同多芯片iso封装及相关产品。组合件可包括包含多个堆叠半导体裸片的配置。可使用各种封装衬底。半导体裸片可包含在其中的各种元件及/或在其上的层,包含势垒层、介电层、装置结构、有源元件及无源元件,包含源极区、漏极区、位线、基极、发射极、集电极、导电线、导电通孔等。此外,半导体裸片可由包含双极、绝缘栅双极晶体管(igbt)、cmos、bicmos及mems的各种工艺形成。

47.本公开涉及的领域所属的技术人员将理解,在所主张发明的范围内,所公开的方面的许多变化是可能的,且在不脱离本公开的范围的情况下,可对上述方面进行进一步添加、删除、替换及修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1