堆叠在用于高压隔离电容器的裸片上的叠层的制作方法

1.本描述涉及高压隔离器装置。

背景技术:

2.电流隔离是隔离电气系统的功能区段以防止电流在所述区段之间流动的原理。为了提供电流隔离,不允许直接传导(dc)路径。能量或信息仍可通过其它手段在所述区段之间交换,例如电容、电感或电磁波,或通过光学、声学或机械手段。

3.电流隔离通常在两个或更多个电子电路需要通信能但它们的接地可处于不同电势的情况下使用。电流隔离是通过防止非所要电流在共用接地导体的两个单元之间流动来断开接地回路的有效方法。电流隔离也用于安全目的,防止意外电流通过人体到达接地。

4.以前,工业、医疗及其它隔离系统的设计者在实施安全隔离时具有有限的选择;唯一合理的选择是光耦合器。数字隔离器目前在性能、大小、成本、功率效率及集成方面具有优势。隔离带来例如延迟、功耗、成本及大小的约束。数字隔离器的目标是满足安全要求,同时最小化所引起的损失。

5.数字隔离器跨隔离势垒耦合数据。这是通过使用调制器跨势垒传输高频载波以表示高数字状态或低数字状态且没有信号表示其它数字状态来实现。接收器在高级信号调节之后解调信号以通过缓冲级产生隔离输出。

6.高压(hv)隔离器装置通常使用专用晶片制造工艺技术及所述工艺技术内的hv组件来构建。hv隔离通常包括光学隔离、电容隔离或电感隔离。隔离结构通常位于第一ic与第二ic之间。

技术实现要素:

7.提供本发明内容以按简化形式介绍所描述概念的简要选择,这些概念在下文包含所提供的附图的具体实施方式中进一步描述。本发明内容不限制所主张的标的物的范围。

8.所描述的方面认识到通常限于单基硅制造技术的常规hv隔离器装置技术的高成本及大占据面积的问题。这些问题通过所描述的方面来解决,所述方面通过使用非导电裸片附接(ncda)材料将具有提供第一板的叠层金属层的叠层裸片堆叠到具有包含第二板的顶部金属层的ic上来产生具有hv电容器的电容隔离器装置。hv电容器的电介质包括叠层裸片的通常相对较厚的电介质叠层、ncda及ic上的钝化层(其在第一板与第二板之间),其中借助于通过这些相应电介质的电容耦合来提供通信。

9.所描述的方面包含一种隔离器装置,其包括具有电介质叠层材料的叠层裸片,在所述电介质叠层材料的一个侧上具有金属叠层,所述金属叠层是提供至少第一板的图案化层,所述图案化层包含所述第一板上方的电介质层,所述电介质层包含暴露所述第一板的一部分的孔隙。包含具有半导体表面的衬底的ic包含含有传输器及/或接收器的电路,所述ic包含提供耦合到所述电路中的节点的至少第二板的顶部金属层,在所述顶部金属层上具有至少一个钝化层。ncda材料用于将所述电介质叠层材料的与所述金属叠层相对的一侧附

接到所述ic,使得所述第一板至少部分位于所述第二板上方以提供电容器。

附图说明

10.现在将参考附图,这些附图不一定按比例绘制,其中:

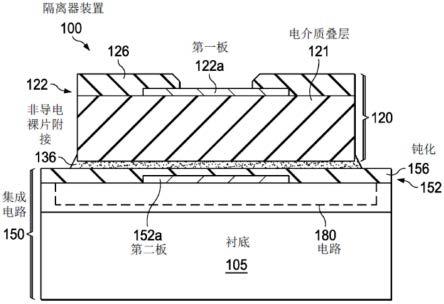

11.图1是根据实例方面的实例电容隔离器装置的横截面图。

12.图2a是根据实例方面的利用单电容器隔离的隔离器装置封装的描绘,所述隔离器装置封装包括具有分裂裸片附接垫(dap)的引线框架,其中电容隔离器装置安装在分裂dap的第一裸片垫部分上,且第二ic安装在分裂dap的单独第二裸片垫部分上,且接合线在第一板与第二ic上的接合垫之间。为简单起见,未展示引线及模塑料。

13.图2b是从图2a中展示的隔离器装置封装修改为现在利用串联电容器隔离的隔离器装置封装的描绘,其中图2a中右侧的ic已被另一隔离器装置取代。如此项技术中已知,与单独的单个电容器相比,包含两个串联电容器的串联电容器隔离提供更高击穿电压(如果电容器相同,那么是电容器的击穿电压的2倍)。

14.图2c是从图2a中展示的隔离器装置封装修改为添加任选额外电容器的隔离器装置封装的描绘,所述任选额外电容器通过接合线耦合到引线以感测在隔离器装置的侧上提供到隔离器装置封装的电压。

15.图3a是根据实例方面的包括具有分裂dap的引线框架的隔离器装置封装的描绘。存在安装在分裂dap的第一部分上的电容隔离器装置、安装在分裂dap的单独部分上的第二ic以及在第一板与第二ic上的接合垫之间的接合线,其中展示引线及模塑料。

16.图3b是根据实例方面的包括具有分裂dap的引线框架的实例隔离器装置封装的描绘。存在安装在分裂dap的第一部分上的电容隔离器装置及安装在分裂dap的单独部分上的另一电容隔离器装置,其中所述电容隔离器装置包含含有传输器及/或接收器的ic上的叠层裸片,且所述另一电容隔离器装置包含含有传输器及/或接收器的ic上的叠层裸片。

17.图4是展示根据实例方面的用于形成电容隔离器装置的实例方法中的步骤的流程图。

具体实施方式

18.参考附图描述实例方面,其中类似参考数字用于表示类似或等效元件。所说明的动作或事件的顺序并非限制性的,因为一些动作或事件可以不同顺序发生及/或与其它动作或事件同时发生。此外,可不需要一些所说明的动作或事件来实施根据本描述的方法。

19.所描述的方面认识到电容隔离器装置具有两个部分:用于提供hv隔离的厚电介质材料;以及从传输(tx)电路到接收(rx)电路的通信方法,所述通信方法可为光学的、电容的或电感的。所描述的电容隔离器包含共同提供至少一个hv电容器且利用电容通信的ic及叠层裸片,其中hv电容器的厚电介质材料包括三种材料的堆叠组合,所述三种材料包含叠层电介质(例如通常用于异型叠层产品的双马来酰亚胺三嗪(bt)叠层)、ncda及ic上的钝化层(也称为保护涂层)。电容通信在由ic的顶部金属层提供的第二板与由堆叠在ic的顶部上的叠层裸片的金属叠层提供的第一板之间。

20.图1是根据实例方面的实例电容隔离器装置100的横截面图。电容隔离器装置100包含叠层裸片120。一般来说,叠层裸片120从叠层裸片的二维阵列中单粒化。叠层裸片120

包括电介质叠层材料121,在电介质叠层材料121的一个侧上具有金属叠层122。

21.金属叠层122是提供第一板122a的图案化层。在第一板122a上方存在电介质层126,其包含暴露第一板122a的内部的孔隙,所述孔隙能够将接合线放置在第一板122a上。电介质层126通常包括非导电的可光成像聚合物材料,所述材料也与封装工艺及模塑料材料兼容。这种可光成像聚合物材料通常被称为焊料掩模材料。

22.尽管叠层裸片120在图1中被展示为其平面尺寸与ic 150相比仅略小,但叠层裸片120通常仅为ic 150的面积的一小部分,例如面积与第二板152a相比更小,使得叠层裸片120可具有常规接合垫的大小,因此例如叠层裸片120可为ic 150的大小的约0.1%。这使得能够接达连接到电路180中的节点的ic 150的接合垫,这也使得能够接合到ic150的接合垫,尽管叠层裸片120在ic 150的顶部上。尽管图1中展示的叠层裸片120仅具有单个第一板122a,但叠层裸片120可具有多个第一板122a以使隔离器装置100(具有来自ic 150的多个第二板152a)能够提供多个所描述hv电容器。还可将两个或更多个叠层裸片120并排放置在单个ic 150上以也提供多个所描述hv电容器。

23.ic 150包括具有半导体表面(例如包括硅,其上包含任选外延层)的衬底105,所述衬底105包含经配置用于通常除了接收或传输功能之外的功能的电路180,其中ic 150包含提供至少第二板152a的顶部金属层152(其任选地可为ic 150上的唯一金属互连层)。第二板152a耦合到电路180中的节点,在顶部金属层152上具有至少一个钝化层156。如展示,钝化层156通常在第二板122a的整个区域上方,且为ic 150的接合垫提供孔隙。

24.可看到,第一板122a及第二板152a彼此重叠,且还任选地在图1中展示的方向上具有相同尺寸,其也可具有相同形状及相同面积。在下文描述的用于形成所描述电容隔离器装置的组装工艺中,通常需要叠层裸片120与ic 150之间的对准(例如40μm的最大错位)以最大化hv电容器的电容值。关于电容隔离器装置100的此对准所需的结构,ic 150通常在叠层裸片120的区域外具有对准标记以供放置工具使用,其中在一个实例中,对准标记具有a+符号的形状。

25.由ic 150提供的电路180包括电路元件(包含晶体管,且通常包含二极管、电阻器、电容器等),这些电路元件可形成于块体衬底材料上的外延层中,所述电路元件配置在一起以通常实现除传输或接收功能之外的至少一种电路功能。实例额外电路功能包含模拟及混合模拟(例如,模/数转换器、数/模转换器、放大器、栅极驱动器或功率转换器)、射频(rf)、数字或非易失性存储器功能。

26.电容隔离器装置100还包含ncda材料136,其用于将电介质叠层材料121的与金属叠层122相对的底侧附接到ic 150的顶侧,使得第一板122a至少部分位于第二板152a上方以提供hv电容器。ncda材料136通常可为非导电的任何聚合物粘合剂,且可在附接叠层裸片120之前将其施配到ic 150上达25到50μm的厚度。ncda材料136的常见实例包括由阿宾斯克(abelstik)提供的称为loctite ablebond 84-3的环氧基材料,此材料是其实际成分是专有的可热固化聚合物材料。尽管隔离器装置100被展示为具有单个所描述hv电容器,但如上文提及,通过包含含有多个第二板152a及单个叠层裸片120上的多个第一板122a的ic,或通过包含多个叠层裸片120(例如对于下文描述的图2a及2b中展示的电容隔离器装置100),可存在多个所描述hv电容器。

27.所描述的电容隔离器装置的优点包含通过叠层裸片120到ic 150的裸片堆叠实现

的较小总裸片占据面积,这提供相对较小封装,或可用于提供具有较高功能性的较大ic。关于所描述的电容隔离器装置封装,由于所描述的工艺及组装工艺与裸片制造工艺无关,因此提供隔离器装置与ic装置制造工艺技术的独立性及成本节省,这能够改进成本及功能性能。

28.图2a是利用单电容器隔离的隔离器装置封装200的描绘,所述隔离器装置封装包括具有分裂dap的引线框架,所述隔离器装置封装包括展示为安装在分裂dap的第一部分160a上的电容隔离器装置100的电容隔离器装置以及安装在分裂dap的单独部分160b上的第二ic 140。在电容隔离器装置100的第一板122a与第二ic 140上的接合垫132之间展示接合线151。隔离器装置封装200被展示为支持两个差分数据通道,展示为ch1及ch2,其中每个通道利用两个所描述的hv电容器来支持差分信号,其中此特定通道布置仅被展示为实例。如图2a中展示,每个ic 140及ic 150都包含传输器及/或接收器电路,展示为tx或rx,其经配置使得隔离器装置封装200支持两个差分数据通道。

29.在ic 150的衬底105的顶表面上存在外部接合垫128,且在ic 140的衬底105'的顶表面上存在外部接合垫129。外部接合垫128可用于在例如在外部接合垫128与引线框架的引线或引线端子之间附接接合线。

30.图2b是从图2a中展示的隔离器装置封装200修改为现在利用串联电容器隔离(展示为两个串联电容器)的隔离器装置封装250的描绘,其中图2a中展示的第二ic 140已被现在展示为100b的另一电容隔离器装置取代,且图2a中展示的电容隔离器装置100现在展示为100a。两个电容隔离器装置100a、100b都包含展示为150a、150b的其相应ic上的所描述叠层裸片120a、120b。如此项技术中已知,与单独的单个hv电容器相比,包含两个串联电容器的串联电容器隔离提供更高击穿电压(如果电容器相同,那么是电容器的击穿电压的2倍)。所描述的hv电容器通常提供至少一千伏的击穿电压。

31.图2c是从图2a中展示的隔离器装置封装修改为添加包括hv感测电容器216的任选额外电容器的隔离器装置封装280的描绘,所述hv感测电容器216展示为通过接合线238耦合到展示为231的引线框架的引线以感测在现在展示为100c的电容隔离器装置的侧上提供到隔离器装置封装200的电压。hv感测电容器216可由另一叠层裸片或由叠层裸片120提供。hv感测电容器216可用于提供与存在于隔离势垒的电容隔离器装置100c侧上的hv成比例的模拟信号。在这种情况下,hv感测电容器216感测hv,并包含可在所展示的电路180内的相关联模拟信号产生电路。此hv感测电容器216及相关联模拟信号产生电路不用于跨隔离势垒进行通信。

32.图3a是包括具有分裂dap的引线框架的隔离器装置封装300的描绘,其中电容隔离器装置100安装在分裂dap的第一部分412上,第二ic 150b安装在分裂dap的单独部分413上,且在第一板122a与第二ic上的接合垫132之间存在接合线。展示引线424及模塑料160。正如图1中展示的电容隔离器装置100,电容隔离器装置100包括现在示为150a的ic上的叠层裸片120,其中在这种布置中,ic 150a上的电路包含传输器及/或接收器且通常包含用于实现至少一个其它功能的电路。

33.图3b是包括具有分裂dap的引线框架的实例隔离器装置封装350的描绘。存在安装在分裂dap的第一部分上的电容隔离器装置100a及安装在分裂dap的单独部分上的另一电容隔离器装置100b,其中电容隔离器装置100a包含含有传输器及/或接收器的ic 150a上的

叠层裸片120a,且电容隔离器装置100b包含含有传输器及/或接收器的ic 150c上的叠层裸片120b。类似于图2b中展示的隔离器装置封装250的隔离器装置封装350实施串联电容器隔离。在叠层裸片120a的第一板122a与叠层裸片120b的第一板122b之间存在接合线427。存在通过接合线128耦合到ic 150a的接合垫的引线424及通过接合线427耦合到ic 150c的接合垫的引线414。还展示模塑料160。

34.如上文描述,可在具有多个第二板152a及至少包括传输器及/或接收器的电路的ic上使用具有多个第一板122a的一个叠层裸片120以提供用于为多个通信通道提供电容隔离的多个hv电容器。在图3b中展示的具体情况中,在其电容隔离器装置100a及100b中的每一者上具有其4个hv电容器的隔离器装置封装300可支持四个单通信通道或两个差分通信通道。图3b中的这种每一叠层裸片120a、120b包含两个或更多个第一板122a的布置与包括各自具有单个hv电容器的多个叠层裸片(为此,组装将需要其自身的图片及放置操作来将每一叠层裸片放置到ic上)的布置相比提供更低成本。

35.图4是展示根据实例方面的用于形成电容隔离器装置的实例方法400中的步骤的流程图,其中参考数字来自图1中展示的电容隔离装置100。步骤401包括提供(i)包括提供第一板122a的叠层金属层122下方的叠层电介质层121的叠层裸片120及(ii)包括具有包含提供传输器及/或接收器的电路180的半导体表面的衬底105的ic 150。ic 150包含提供耦合到电路180中的节点的至少一个第二板152a的顶部金属层152,在顶部金属层上具有至少一个钝化层156。步骤402包括将图案化电介质层126形成到叠层金属层上,所述图案化电介质层具有暴露第一板122a的区域以附接接合线的孔隙。

36.步骤403包括使用ncda材料136在叠层电介质层朝上的情况下安装叠层裸片,使得第一板122a至少部分位于第二板152a上方以提供电容器。如上文提及,第一板122a通常具有与第二板152a的面积相比更小的面积,且第一板122a通常对准为在第二板152a的面积的至少50%上方。步骤404包括固化ncda材料136,例如通过包括热固化的工艺。步骤405包括通常跟随的线接合,包括涉及ic 150上的接合垫、第一板122a及引线框架的引线或引线端子、第二ic或第二隔离器装置的线接合。还可在线接合之前包含等离子体处理,这可改进线接合的质量,也可改进模塑料与叠层的粘合性。

37.所描述的方面可集成到各种组装流程中以形成各种不同电容隔离器装置及相关产品。组合件可包括单个半导体裸片或两个或更多个(多个)半导体裸片,例如包括多个堆叠半导体裸片的配置。可使用各种封装衬底。半导体裸片可包含其中的各种元件及/或其上的层,包含势垒层、电介质层、装置结构、有源元件及无源元件,包含源极区、漏极区、位线、基极、发射极、集电极、导电线、导电通孔等。此外,半导体裸片可由包含双极、绝缘栅双极晶体管(igbt)、cmos、bicmos及mems的各种工艺形成。

38.本描述涉及的领域所属的技术人员将理解,在所主张发明的范围内,所描述的方面的许多变化是可能的,且在不脱离本描述的范围的情况下,可对上述方面进行进一步添加、删除、替换及修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1