升压的回写电压的制作方法

升压的回写电压

附图说明

1.图1是图示根据一个实施例的动态随机存取存储器(dram)系统的框图。

2.图2是图示示例升压回写感测放大器的图。

3.图3是图示偏移补偿升压回写感测放大器的元件的图。

4.图4a至图4c是图示升压回写操作的图。

5.图5是图示升压电压写入操作的图。

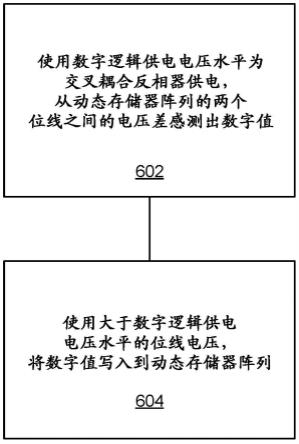

6.图6是图示升压回写方法的流程图。

7.图7是图示升压写入方法的流程图。

8.图8是操作存储器设备的方法。

9.图9是调整回写电压的方法。

10.图10是处理系统的框图。

具体实施方式

11.降低电子设备和计算机系统的功耗是一个持续的目标。因此,降低动态随机存取存储器(dram)设备的功耗是该工作的部分。导致dram设备功耗的主要因素与公式p=cv2f相关联,其中p是功耗,c是电容,v是切换电压,f是切换频率。因此,由于电压在上式中为平方,因此降低切换电压对降低功耗具有重要影响。

12.在一个实施例中,dram设备的(多个)动态存储器阵列使用至少两个电压进行操作。第一电压是dram设备的大多数数字逻辑电路系统的操作(即切换)电压,第一电压用于在感测(即读取)操作和大多数其他列操作(例如,预充电、激活、写入)期间为感测放大器供电。确定写入到dram单元的电容器的电压(即位线电压)的第二电压大于dram设备的大多数数字逻辑电路系统的操作(即切换)电压。换句话说,数字逻辑电路系统使用低于写入到dram阵列的电容器的电压的供电电压进行操作。这允许较低电压摆幅(因此较低的功率)数字逻辑用于dram设备上的大部分逻辑,同时将较大的电压写入到dram单元以用于保留时间的目的。由大多数逻辑使用的较低电压摆幅降低了dram阵列的感测放大器和dram的其他数字逻辑的功耗,这又降低了整体dram设备的功耗。

13.图1是图示根据一个实施例的动态随机存取存储器(dram)系统的框图。在图1中,存储器系统100包括dram存储器设备110和控制器180。控制器180和存储器设备110是集成电路类型的设备,诸如通常被称为“芯片”。诸如控制器180的存储器控制器管理进出存储器设备的数据流。存储器控制器可以是单独的独立芯片,或者可以被集成到另一个芯片中。例如,存储器控制器可以被包括在具有微处理器的单个裸片上,或者被包括作为更复杂的集成电路系统的部分,诸如片上系统(soc)的块。

14.控制器180包括物理接口185。物理接口185包括命令/地址(ca)接口181和双向数据(dq)接口182。存储器设备110包括物理接口电路系统175。物理接口电路系统175包括命令/地址(ca)接口171和双向数据(dq)接口172。控制器180的命令/地址接口181可操作地耦合到存储器设备110的ca接口171,以向存储器设备110发送命令和地址。控制器180经由双

向数据接口182可操作地耦合到存储器设备110。控制器180可操作地耦合到存储器设备110以与存储器设备110通信数据。存储器设备110经由双向数据接口172传送数据。

15.在图1中,dram存储器设备110包括多个存储体/子存储体、控制电路系统160和接口电路系统175。dram存储器设备110可以是至少一个集成电路、在至少一个集成电路上或包括至少一个集成电路。dram存储体包括子阵列(例如,子阵列128)、感测放大器条(例如,感测放大器条135)、列解码器140和字线控制电路系统150。感测放大器条135包括感测放大器(例如,感测放大器130)和局部-全局开关(例如,局部-全局开关127)。子阵列包括存储器位单元(例如,单元123)。存储器位单元123连接到字线122、位线121和列选择线124。感测放大器130连接到位线121和局部数据线125。局部-全局开关127连接到局部数据线125和全局数据线126。

16.控制电路系统160可操作地耦合到dram存储体,以至少处理经由ca接口171接收的列地址、行地址和/或命令。控制电路系统160包括数字逻辑电路系统,数字逻辑电路系统在正常操作模式下,使用选择的(例如,由dram存储器设备110的制造商选择的)数字逻辑供电电压(又称为vdd)进行操作。控制电路系统160可以包括使用互补金属氧化物半导体(cmos)型逻辑门实现的电路系统中的大部分电路系统。控制电路系统160可以包括使用在高k/金属栅极(hkmg)cmos制造工艺中实现的cmos逻辑实现的电路系统。全摆幅cmos逻辑门的信号摆幅(即,在逻辑

‘1’

和逻辑

‘0’

之间)的范围可以从对应于负供电/基准/衬底电压的最小值到对应于数字逻辑供电电压的最大电压。

17.在一个实施例中,在正常操作模式(即,非测试模式)中,dram存储器设备110(并且特别地,感测放大器130)使用dram存储器设备110上的大部分数字逻辑的数字逻辑供电和/或最大信号摆幅水平(相对于与位线电压所参考的相同的负供电/基准/衬底电压),来感测存储器位单元(例如,单元123)的状态。

18.然而,当将数据写入到存储器位单元(例如,单元123)时,dram设备(并且特别地,感测放大器130)可以将位线充电到一种电压(即,相对于负供电/基准/衬底电压的最大电压),该电压高于dram存储器设备110上的大多数数字逻辑的数字逻辑供电和/或最大信号摆幅水平(相对于与位线电压所参考的相同的负供电/基准/衬底电压)。特别地,在写入和回写操作期间,位线121可以使用大于控制电路系统160的最大电压来充电。为简洁起见,该升压位线电压在本文中可以被称为vblhi。

19.正常操作(非测试)模式包括在非生产和非测试环境中使用的存储器系统100中的dram存储器设备110的预期操作模式。例如,dram存储器设备110在被包括在更大的系统(例如,完整的计算机系统、消费电子设备等)中之前,可以以一种或多种测试模式进行测试或以其他方式操作。这些测试模式可以在各种制造过程和/或阶段期间被使用,并且在系统由最终用户(例如消费者、数据中心等)使用时通常不被使用。

20.例如,有时,诸如在老化(burn-in)期间,可以使用测试模式对dram设备110施加

‘

压力’,以确认dram设备110的功能和/或可靠性。同样,在测试期间,数字逻辑供电电压可以被降低到低于升压位线电压,以确认dram存储器设备110的功能和/或可靠性。然而,在

‘

正常’操作期间通常不使用测试模式,因为dram设备110的功能、性能、寿命和/或可靠性在以一种或多种测试模式(与

‘

正常’操作模式相反)操作时可能降级。

21.在正常操作模式下,感测放大器条135和其中的感测放大器(例如感测放大器130)

可以使用选择的(例如由制造商选择的)升压位线电压(和/或位线电压范围)进行操作。在正常操作模式下,字线控制电路系统150可以使用数字逻辑供电电压和/或分开的编程供电电压(vpp)进行操作,分开的编程供电电压(vpp)可以存在以支持与升压位线电压兼容的字线电压要求。在正常操作模式下,列解码器140可以使用数字逻辑供电电压进行操作。在正常操作模式下,控制电路系统(和所包括的数据路径电路系统)160可以使用数字逻辑供电电压进行操作。在正常操作模式下,接口电路系统175可以使用输入/输出(i/o)供电电压和/或数字逻辑供电电压进行操作。

22.在一个实施例中,控制电路系统160、列解码器140和行解码器150共同至少处理列地址和行地址,以检索存储在至少子阵列128中的数据。控制电路系统160、列解码器140和行解码器150使用数字逻辑供电电压进行操作。在感测操作和列操作期间,感测放大器130还使用数字逻辑供电电压进行操作。在回写操作期间,感测放大器130还使用大于第一数字逻辑供电电压的升压位线电压进行操作。控制电路系统160、列解码器140和/或行解码器150可以使用高k金属栅极工艺来进行实现。

23.感测放大器130包括以双稳态触发器配置的交叉耦合反相器对,该交叉耦合反相器对耦合到动态存储器阵列的相应位线。这些交叉耦合反相器均具有负供电节点和正供电节点。在回写操作期间,升压位线电压可以选择性地耦合到交叉耦合反相器的正供电节点。这使得感测放大器电路将阵列的单元123充电到升压位线电压,而不是数字逻辑供电电压。与利用数字逻辑供电电压对单元123充电相比,增加对单元123充电的电压增加了单元123的数据保持时间。

24.在一个实施例中,在感测操作和列操作期间,数字逻辑供电电压选择性地耦合到交叉耦合反相器的正供电节点。在回写操作期间,数字逻辑供电电压选择性地从交叉耦合反相器的正供电节点去耦。以该方式,避免了数字逻辑供电电压和升压位线电压之间的驱动冲突。在一个实施例中,在刷新操作期间,升压位线电压选择性地耦合到交叉耦合反相器的正供电节点。特别地,在感测操作期间,升压位线电压选择性地耦合到交叉耦合反相器的正供电节点,而无需首先使用数字逻辑供电电压进行感测。以该方式,在开始利用升压位线电压对位线充电之前,无需等待交叉耦合反相器使用数字逻辑供电电压达到稳定状态,即可以完成刷新操作。与单独感测操作之后进行单独(升压)回写操作相比,这可以允许刷新操作在较少时间内完成。

25.在一个实施例中,升压位线电压可以是基于从控制器180接收的命令。例如,控制器180可以将值写入到控制电路系统160中设置升压位线电压的寄存器。在另一个示例中,命令(例如,刷新、写入等)可以指示升压位线电压(例如,利用升压的写入、没有升压的刷新等)。在另一个示例中,控制器180可以使用控制电路系统160中的寄存器和指示升压位线电压的命令的组合,来指示升压位线电压。在一个实施例中,控制器180可以基于存储器设备110的温度来选择升压位线电压。在一个实施例中,控制器可以基于对被感测的数据的使用来选择升压位线电压。例如,如果控制器180知道数据将不再被存储在存储器设备110中,则控制器180可以指示“读取而不升压回写”命令。“读取而不升压回写”或“刷新而不升压回写”命令可以选择用于回写的等于数字逻辑供电电压的位线电压。与总是使用升压位线电压相比,这些命令可以影响(例如,减少)命令的处理时间,从而增加存储器设备110的产量。

26.在一个实施例中,存储器设备110可以选择升压位线电压。存储器设备110可以基

于存储器设备110的温度来选择升压位线电压。在一个实施例中,存储器设备110可以基于存储器设备110的温度和从控制器180接收的一个或多个指示符(例如,寄存器值或命令),来选择升压位线电压。例如,存储器设备110可以基于存储器设备110的温度和从控制器180接收的温度与升压位线电压系数指示符来选择升压位线电压。

27.图2是图示示例升压回写感测放大器的图。感测放大器200可以是dram存储器设备110和/或感测放大器条135的部分(即,特别地,作为感测放大器130)。在图2中,感测放大器200包括功能块210、220、225、230、240,250和250。虽然在图2中被图示为一个感测放大器200的部分,但是功能块220、225、230、240和250可以与多个放大器块210共享以形成多个感测放大器。类似地,尽管在图2中被图示为接近放大器块210,但功能块220、225、230、240和250可以位于dram阵列内相对远离放大器块210的各个位置。

28.感测放大器200执行对真(blt)位线和补(blc)位线上的电压差的评估。感测放大器200还通过将真位线(blt)和补(blc)位线强制(充电)到数字逻辑供电电压(vdd)和/或升压位线电压(vblhi),来执行数据到存储器单元(例如,单元123)的写入和/或回写。

29.放大器块210包括交叉耦合反相器对,交叉耦合反相器对由评估控制块220接通。放大器块210的交叉耦合反相器包括n沟道场效应晶体管(nfet)211和212,以及p沟道场效应晶体管(pfet)213和214。nfet 211和pfet 214形成第一反相器,该第一反相器交叉耦合到使用nfet 212和pfet 214形成的第二反相器。每个反相器的输出被提供到其他反相器的输入(即交叉耦合)。到放大器块210的反相器的负供电和正供电由评估控制块220和/或升压位线控制块225选择性地提供。

30.到这些反相器的供电san和sap由评估控制块220选择性地(可切换地)提供给放大器块210。供电sap由升压位线控制块225选择性地(可切换地)提供给放大器块210。到这些反相器的供电san和sap由评估控制块220选择性地(可切换地)提供给放大器块210,以便允许放大器块210的内部节点/到放大器块210的外部节点(包括位线blt和位线blc,以及供电san和sap)被均衡,并且然后被激活以评估位线blt和位线blc上的电压。供电sap由升压位线控制块225选择性地(可切换地)提供给放大器块210,以便将取决于放大器块210状态的位线blt和位线blc中的一个位线的上的电压充电到升压位线电压vblhi。

31.评估控制块220包括nfet 221和pfet 222。在nset节点上的信号的控制下,nfet 221可切换地将负(基准)供电电压(其是用于放大器块210的负供电)连接到节点san以及将其断开连接。在pset节点上的信号的控制下,pfet 222可切换地将数字逻辑供电电压(其是用于放大器块210的正供电)连接到节点sap以及将其断开连接。提供给nset节点(即,nfet 221的栅极)的信号可以具有小于升压位线电压的摆幅。因此,在正常操作中,耦合到评估控制块220的控制电路系统(例如,控制电路系统160)可以包括可以向nset节点提供信号的电路系统,该信号达到数字逻辑供电电压,但没有达到vblhi(或甚至没有达到vblhi减去pfet 222的阈值电压)。

32.在一个实施例中,在正常的非回写操作中,由pfet 222连接到sap的数字逻辑供电电压小于升压位线电压vblhi。pset(即,pfet 222的栅极)上的信号的摆幅可以等于要连接到sap的数字逻辑供电电压(例如,vdd)(或比其低小于pfet 222的阈值电压)。因此,在正常的非回写操作中,耦合到评估控制块220的控制电路系统可以包括可以向pset节点提供信号的电路系统,该信号达到数字逻辑供电电压vdd,但没有达到vblhi(或者甚至没有达到

vblhi减去pfet 222的阈值电压)。

33.感测放大器均衡块230,当经由节点sns_amp_eq上的信号被激活时,将sap和san连接在一起并且连接到均衡供电电压vbleq。感测放大器均衡块230包括nfet 231-233。nfet 231-233的栅极可操作地耦合在一起,并且耦合到节点sns_amp_eq。nfet 231的源极节点和漏极节点分别连接到san和sap。nfet 232的源极节点和漏极节点分别连接到san和vbleq。nfet 233的源极节点和漏极节点分别连接到vbleq和sap。提供给sns_amp_eq的信号可以具有小于升压位线电压vblhi的摆幅。因此,在正常操作中,耦合到感测放大器均衡块230的控制电路系统(例如,控制电路系统160)可以包括可以向sns_amp_eq节点提供信号的电路系统,该信号达到数字逻辑供电电压,但没有达到vblhi(或甚至没有达到vblhi减去pfet 222的阈值电压)。

34.位线均衡块240,当经由节点eql上的信号被激活时,将位线blt和位线blc连接在一起并且连接到均衡供电电压vbleq。位线均衡块240包括nfet 241-243。nfet 241-243的栅极可操作地耦合在一起并且耦合到节点eql。nfet 241的源极节点和漏极节点分别连接到blt和blc。nfet 242的源极节点和漏极节点分别连接到blt和vbleq。nfet 243的源极节点和漏极节点分别连接到vbleq和blc。提供给eql的信号可以具有小于升压位线电压vblhi的摆幅。因此,在正常操作中,耦合到位线均衡块240的控制电路系统(例如,控制电路系统160)可以包括可以向eql节点提供信号的电路系统,该信号达到数字逻辑供电电压但没有达到vblhi(或者甚至没有达到vblhi减去pfet 222的阈值电压)。

35.列连接块250选择性地(可切换地)将位线blt和位线blc分别连接(又称为门控)到局部数据线ldqt和ldqc。列连接块250包括nfet 251-252。nfet 251-252的栅极可操作地耦合在一起并且耦合到节点csl。nfet 251的源极节点和漏极节点分别连接到blt和ldqt。nfet 252的源极节点和漏极节点分别连接到blc和ldqt。csl(即,nfet 251-252的栅极)上的信号的摆幅可以等于数字逻辑供电电压。

36.在一个实施例中,在pseth节点上的信号的控制下,pfet 226可切换地将升压位线电压vblhi连接到节点sap以及将其断开连接。当pfet 226将升压位线电压vblhi连接到节点sap时,在pset节点上的信号的控制下,pfet 222可切换地将数字逻辑供电电压vdd与节点sap断开连接。为了将数字逻辑供电电压vdd与节点sap断开连接,可以将pset节点上的电压升压到vblhi。数字逻辑供电电压vdd与节点sap的断开连接避免了升压位线电压vblhi和数字逻辑供电电压vdd之间的驱动冲突。当pfet 226将升压位线电压vblhi连接到节点sap时,放大器块210状态选择的位线blt和位线blc中的一个位线被充电到升压位线电压vblhi。在一个实施例中,pfet 226将升压位线电压vblhi连接到节点sap以评估位线blt和位线blc上的电压。在该实施例中,pfet 226可以将升压位线电压vblhi连接到节点sap,而无需首先将数字逻辑供电电压vdd连接到节点sap。

37.图3是图示偏移补偿升压回写感测放大器的元件的图。感测放大器300可以是dram存储器设备110和/或感测放大器条135的部分(即,特别地,作为感测放大器130)。在图3中,感测放大器300包括功能块310、320和340。为了简洁起见,从图3省略了感测放大器300的其他功能块。感测放大器300执行对真(blt)和补(blc)位线上的电压差的评估。感测放大器300还通过将真(blt)和补(blc)位线强制(充电)到数字逻辑供电电压(vdd)和/或升压位线电压(vblhi),来执行数据到存储器单元(例如,单元123)的写入和/或回写。

38.放大器块310包括交叉耦合反相器对,交叉耦合反相器对由评估控制块320接通。放大器块310的交叉耦合反相器包括n沟道场效应晶体管(nfet)311和312,以及p沟道场效应晶体管(pfet)313和314。nfet 311和pfet 314形成第一反相器,该第一反相器交叉耦合到使用nfet 312和pfet 314形成的第二反相器。每个反相器的输出被提供到其他反相器的输入(即交叉耦合)。到放大器块310的反相器的负供电和正供电由评估控制块320选择性地提供。

39.到这些反相器的供电san和sap由评估控制块320选择性地(可切换地)提供给放大器块310,以便允许放大器块310的内部节点/到放大器块310的外部节点(包括位线blt、blc、内部节点sablt、sablc以及供电san和sap)被均衡,并且然后被激活以评估位线blt和位线blc上的电压。供电sap由升压位线控制块325选择性地(可切换地)提供给放大器块310。供电sap由升压位线控制块325选择性地(可切换地)提供给放大器块310以便将取决于放大器块310状态的位线blt和位线blc中的一个位线的上的电压充电到升压位线电压vblhi。

40.评估控制块320包括nfet 321和pfet 322。在nset节点上的信号的控制下,nfet 321可切换地将负(基准)供电电压(其是用于放大器块310的负供电)连接到节点san以及将其断开连接。在pset节点上的信号的控制下,pfet 322可切换地将数字逻辑供电电压vdd(其是用于放大器块310的正供电)连接到节点sap以及将其断开连接。在nset节点上的信号的控制下,nfet 321可切换地将负(基准)供电电压(其是用于放大器块310的负/基准供电)连接到节点san以及将其断开连接。提供给nset节点(即,nfet 321的栅极)的信号可以具有小于位线电压的摆幅。因此,在正常操作中,耦合到评估控制块320的控制电路系统(例如,控制电路系统160)可以包括可以向nset节点提供信号的电路系统,该信号达到数字逻辑供电电压vdd,但没有达到vblhi(或甚至没有达到vblhi减去pfet 322的阈值电压)。

41.在一个实施例中,在正常操作中,由pfet 322连接到sap的正供电电压小于升压位线电压vblhi。pset(即,pfet 322的栅极)上的信号的摆幅可以等于要连接到sap的数字逻辑供电电压(例如,vdd)(或比其低小于pfet 322的阈值电压)。因此,在正常的非回写操作中,耦合到评估控制块320的控制电路系统可以包括可以向pset节点提供信号的电路系统,该信号达到数字逻辑供电电压vdd,但没有达到vblhi(或者甚至没有达到vblhi减去pfet 322的阈值电压)。

42.偏移补偿开关块340,当经由节点iso和oc上的信号被激活时,将位线blt和位线blc分别与内部放大器块310的节点sablt和节点sablc断开连接;将blt连接到sablc;以及将blc连接到sablt。偏移补偿开关块340包括nfet 341-544。nfet 341-542的栅极可操作地耦合在一起并且耦合到节点iso(又称为隔离)。nfet 341的源极节点和漏极节点分别连接到blt和sablt。nfet 342的源极节点和漏极节点分别连接到blc和sablc。nfet 343的源极节点和漏极节点分别连接到blt和sablc。nfet 344的源极节点和漏极节点分别连接到blc和sablt。oc(即,nfet 343-344的栅极)上的信号的摆幅可以等于数字逻辑供电电压vdd。因此,在正常操作中,耦合到偏移补偿开关块340的控制电路系统可以包括可以向oc节点提供信号的电路系统,该信号至少达到vdd,但没有达到vblhi。

43.在一个实施例中,在pseth节点上的信号的控制下,pfet 326可切换地将升压位线电压vblhi连接到节点sap以及将其断开连接。当pfet 326将升压位线电压vblhi连接到节

点sap时,在pset节点上的信号的控制下,pfet 322可切换地将数字逻辑供电电压与节点sap断开连接。为了将数字逻辑供电电压vdd与节点sap断开连接,可以将pset节点上的电压升压到vblhi。数字逻辑供电电压vdd与节点sap的断开连接避免了升压位线电压vblhi和数字逻辑供电电压vdd之间的驱动冲突。当pfet 326将升压位线电压vblhi连接到节点sap时,放大器块310状态选择的位线blt和位线blc中的一个位线被充电到升压位线电压vblhi。在一个实施例中,pfet 326将升压位线电压vblhi连接到节点sap以评估位线blt和位线blc上的电压。在该实施例中,pfet 326可以将升压位线电压vblhi连接到节点sap,而无需首先将数字逻辑供电电压vdd连接到节点sap。

44.图4a-图4c是图示升压回写操作的图。通常,在升压回写操作期间,pset应当处于vblhi以将vblhi与vdd完全断开连接。这可以通过以下方式实现:(1)两水平操作,其中pset在vss和vblhi之间切换;或者,(2)三水平操作,其中pset在非回写操作期间在0和vdd之间切换,并且在回写操作期间被升压到vblhi。图4a中图示了示例三水平操作。图4b、图4c和图5中图示了示例两水平操作。

45.在图4a中,执行感测(读取)操作,接着是回写操作。在图4a中,波形401和波形402表示位线(例如感测放大器200的位线blt和位线blc)上的电压。在第一阶段(预充电操作)中,波形401-402说明位线被预充电到相同的电压水平vbleq。在一些实施例中,vbleq可以大约等于vdd/2。在该第一预充电阶段期间,pset被驱动到vdd,并且pseth被驱动到升压位线电压vblhi。这是为了允许将位线充电到vbleq,在图4a中,vbleq小于vdd和vblhi两者。

46.下一个(第二)阶段是信号发展。当均衡电路系统(例如,感测放大器均衡块230和位线均衡块240)关闭并且字线断开,而感测放大器尚未被切换到感测时,信号发展开始。信号发展与位线共享单元的电荷,并且将真位线和补位线稍微分离以产生一个信号,然后该信号在感测阶段中被放大。

47.在第三阶段(感测操作)中,pset被驱动到负基准电压vss,并且pseth保持在vblhi。当pset被驱动到负基准电压时,感测放大器的放大器块(例如,放大器块210)的正供电节点sap连接到vdd。这连同连接到vss的负节点(图4a中未示出)使得感测放大器的交叉耦合反相器(例如,放大器块210)评估位线上的电压差。在评估电压差时,交叉耦合反相器相互反馈以根据位线上的电压差驱动位线。这在图4a中通过波形401充电到vdd以及波形402放电到vss来进行图示。

48.在第四阶段(回写操作)中,pset被驱动到升压位线电压vblhi,并且pseth被驱动到负基准电压vss。这使得vblhi被施加到正供电节点sap。作为响应,波形401图示了被充电到vdd的位线进一步充电到vblhi。波形402图示了被放电到vss的位线保持在vss。因此,从图4a可以看出,波形401图示了位线被“升压”到高于vdd至vblhi。波形401图示的位线上的电压确定了dram单元(例如单元123)中的电容器上的电压。因此,dram单元中的电容器上的电压也被“升压”。

49.在第五阶段(预充电操作)中,pseth被驱动到升压位线电压vblhi,并且pset被降低到vdd。这允许将位线预充电回起始电压水平vbleq。这在图4a中通过波形401-402返回到vbleq来进行图示。

50.在图4b中,执行感测(读取)操作,接着是回写操作。在图4b中,波形403和波形404表示位线(例如,感测放大器200的位线blt和位线blc)上的电压。在第一阶段(预充电操作)

中,波形403-404图示了位线被预充电到相同的电压水平vbleq。在一些实施例中,vbleq可以大约等于vdd/2。在该第一预充电阶段期间,pset和pseth被驱动到升压位线电压vblhi。这是为了允许将位线充电到vbleq,在图4b中,vbleq小于vdd和vblhi两者。

51.下一个(第二)阶段是信号发展。在第三阶段(感测操作)中,pset被驱动到负基准电压vss,并且pseth保持在vblhi。当pset被驱动到负基准电压时,感测放大器的放大器块(例如,放大器块210)的正供电节点sap连接到vdd。这连同连接到vss的负节点(图4b中未示出)使得感测放大器的交叉耦合反相器(例如,放大器块210)评估位线上的电压差。在评估电压差时,交叉耦合反相器相互反馈以根据位线上的电压差驱动位线。这在图4b中通过波形403充电到vdd以及波形404放电到vss来进行图示。

52.在第四阶段(回写操作)中,pset被驱动到vblhi并且pseth被驱动到负基准电压vss。这使得升压位线电压vblhi被施加到正供电节点sap。作为响应,波形403图示了被充电到vdd的位线进一步充电到vblhi。波形404图示了被放电到vss的位线保持在vss。因此,从图4b可以看出,波形403图示了位线被“升压”到高于vdd至vblhi。波形403图示的位线上的电压确定了dram单元(例如单元123)中的电容器上的电压。因此,dram单元中的电容器上的电压也被“升压”。

53.在第五阶段(预充电操作)中,pseth和pset被驱动到升压位线电压vblhi。这允许将位线预充电回起始电压水平vbleq。这在图4b中通过返回到vbleq的波形403-404来进行图示。

54.图4c图示了升压位线电压刷新操作。在图4c中,波形405和波形406表示位线(例如,感测放大器200的位线blt和位线blc)上的电压。在第一阶段(预充电操作)中,波形405-406图示了位线被预充电到相同的电压水平vbleq。在一些实施例中,vbleq可以大约等于vdd/2。在该第一预充电阶段期间,pset和pseth被驱动到vblhi。波形405-406图示了位线都被充电到vbleq,在图4c中,vbleq小于vdd和vblhi两者。

55.下一个(第二)阶段是信号发展。在第三阶段(组合感测和回写操作),pset仍然被驱动到vblhi,并且pseth被驱动到负基准电压vss。这使得vblhi被施加到正供电节点sap。当pset被驱动到负基准电压时,感测放大器的放大器块(例如,放大器块210)的正供电节点sap连接到vblhi。这连同连接到vss的负节点(图4c中未示出)使得感测放大器的交叉耦合反相器(例如,放大器块210)评估位线上的电压差。在评估电压差时,交叉耦合反相器相互反馈以根据位线上的电压差驱动波形405-406。这在图4c中通过波形405充电到vblhi以及波形406放电到vss来进行图示。

56.因此,从图4c可以看出,在一个操作中,波形405被“升压”到高于vdd至vblhi。波形405图示的位线上的电压确定dram单元(例如单元123)中的电容器上的电压。因此,dram单元中的电容器上的电压也被“升压”。在第四阶段(预充电操作)中,pseth被驱动到升压位线电压vblhi,并且pset保持在vblhi。这允许波形405-406被预充电回起始电压水平vbleq。

57.图5是图示升压电压写入操作的图。在图5中,波形501和波形502表示位线(例如,感测放大器200的位线blt和位线blc)上的电压。在第一阶段(感测操作结束)中,波形501-502分别图示了位线被充电到vss和vdd。位线的状态可以已经由先前的感测操作或写入操作确定,先前的感测操作或写入操作设置放大器块(例如,放大器块210)中的反相器的状态。在该阶段结束时,pset被驱动到vss,pseth被驱动到vblhi,并且列选择线csl被驱动到

vss。这是为了允许由波形501图示的位线被充电上至vdd,但没有vblhi那么高。这也防止了局部数据线上的电压重写放大器块中的反相器的状态。

58.在第二阶段(写入操作)中,pset保持在vss,并且pseth保持在vblhi,并且列选择线(csl)被驱动到vdd。当csl被驱动到vdd时,局部数据线上的电压重写放大器块中的反相器的状态。这在图5中通过波形501充电到vdd以及波形502放电到vss来进行图示。

59.在第三阶段(回写操作)中,pset被驱动到vblhi,pseth被驱动到负基准电压vss,并且csl被驱动到vss。这使得vblhi被施加到正供电节点sap。作为响应,被充电到vdd的波形501进一步充电到vblhi。被放电到vss的波形502保持在vss。因此,从图5可以看出,波形501被“升压”到高于vdd到vblhi。波形501上的电压确定dram单元(例如单元123)中的电容器上的电压。因此,dram单元中的电容器上的电压也被“升压”。

60.在第四阶段(预充电操作)中,pseth被驱动到升压位线电压vblhi,pset保持在vblhi,并且csl保持在vss。这允许由波形501-502图示的位线被预充电回起始电压水平vbleq。

61.图6是图示升压回写方法的流程图。图6中图示的一个或多个步骤可以由例如存储器系统100、感测放大器200、感测放大器300和/或它们的组件来执行。使用数字逻辑供电电压水平为交叉耦合反相器供电,从动态存储器阵列的两个位线之间的电压差感测出数字值(602)。例如,使用数字逻辑供电电压vdd为放大器块210的交叉耦合反相器供电,感测放大器200可以使用连接到感测放大器200的真(blt)和补(blc)位线之间的电压差,来感测对应于该电压差的数字值。

62.使用大于数字逻辑供电电压水平的位线电压,将数字值写入到动态存储器阵列(604)。例如,感测放大器200的升压位线控制块可以将大于vdd的升压位线电压vblhi耦合到放大器块210的正供电节点sap。这允许放大器块210的交叉耦合反相器中的一个反相器将升压位线电压vblhi驱动到动态存储器阵列(例如,子阵列128)中,其中升压位线电压vblhi将对动态存储器阵列单元(例如,单元123)的电容器充电。

63.图7是图示升压写入方法的流程图。图7中图示的一个或多个步骤可以由例如存储器系统100、感测放大器200、感测放大器300和/或它们的组件来执行。使用数字逻辑供电电压水平为交叉耦合反相器供电,设置动态存储器阵列的感测放大器的交叉耦合反相器对的状态(702)。例如,在基于局部数据线ldqt和ldqc上的电压设置它们的状态的写入操作期间,感测放大器200的放大器块210的交叉耦合反相器可以由来自评估控制块320的vdd水平电压供电。

64.使用大于数字逻辑供电电压水平的位线电压,将感测放大器的交叉耦合反相器对的状态写入到动态存储器阵列(704)。例如,基于交叉耦合反相器的状态,感测放大器200可以将大于vdd的升压位线电压vblhi驱动到与交叉耦合反相器的状态相对应的真(blt)和补(blc)位线中的一个位线。这允许感测放大器200将升压位线电压vblhi驱动到动态存储器阵列(例如,子阵列128)中,其中升压位线电压vblhi将对动态存储器阵列单元(例如,单元123)的电容器充电。

65.图8是操作存储器设备的方法。图8中图示的一个或多个步骤可以由例如存储器系统100和/或其组件来执行。将第一命令传送到存储器设备以操作作为存储器设备的动态存储器阵列的部分的多个感测放大器电路,以在感测操作和列操作期间使用数字逻辑供电电

压水平(802)。例如,控制器180可以经由接口185传送命令(和/或设置寄存器值),该命令(和/或设置寄存器值)使存储器设备110将感测放大器130配置成使用数字逻辑供电电压水平(例如,vdd)和/或最大信号摆幅水平(相对于与位线电压所参考的相同的负供电/基准/衬底电压),来感测存储器位单元(例如单元123)的状态,该数字逻辑供电电压水平(例如,vdd)和/或最大信号摆幅水平由dram存储器设备110上的大多数数字逻辑使用。

66.在回写操作期间,存储器设备被控制为使用大于数字逻辑供电电压的位线电压(804)。例如,控制器180可以经由接口185传送命令(和/或设置寄存器值),该命令(和/或设置寄存器值)使存储器设备110将感测放大器130配置成使用升压位线供电(例如vblhi)和/或最大信号摆幅水平(相对于与数字逻辑供电电压水平所参考的相同的负供电/基准/衬底电压),来回写存储器位单元(例如,单元123)的状态,该升压位线供电(例如vblhi)和/或最大信号摆幅水平大于dram存储器设备110上的大多数数字逻辑使用的数字逻辑供电电压水平。

67.图9是调整回写电压的方法。图9中图示的一个或多个步骤可以由例如存储器系统100和/或其组件来执行。将第一命令传送到存储器设备以操作作为存储器设备的动态存储器阵列的部分的多个感测放大器电路,以在感测操作和列操作期间使用数字逻辑供电电压水平(902)。例如,控制器180可以经由接口185传送寄存器值(和/或命令),该寄存器值(和/或命令)使存储器设备110将感测放大器130配置成使用数字逻辑供电电压水平(例如,vdd)和/或最大信号摆幅水平(相对于与位线电压所参考的相同的负供电/基准/衬底电压),来感测存储器位单元(例如单元123)的状态,该数字逻辑供电电压水平(例如,vdd)和/或最大信号摆幅水平由dram存储器设备110上的大多数数字逻辑使用。

68.将第二指示符传送到存储器设备,以在回写操作期间以第一位线电压操作多个感测放大器电路(904)。例如,控制器180可以经由接口185传送寄存器值(和/或命令),该寄存器值(和/或命令)使存储器设备110将感测放大器130配置成使用升压位线供电(例如vblhi)和/或最大信号摆幅水平,来回写存储器位单元(例如单元123)的状态。

69.将第三指示符传送到存储器设备,以在回写操作期间以第二位线电压操作多个感测放大器电路,其中第二位线电压不等于第一位线电压(904)。例如,控制器180可以经由接口185传送寄存器值(和/或命令),该寄存器值(和/或命令)使存储器设备110将感测放大器130配置成使用不同的升压位线供电和/或最大信号摆幅水平,来回写存储器位单元(例如,单元123)的状态。在另一个示例中,控制器180可以经由接口185传送寄存器值(和/或命令),该寄存器值(和/或命令)使存储器设备110改变vblhi的电压水平。

70.上述方法、系统和设备可以在计算机系统中实现,或者由计算机系统存储。上述方法也可以被存储在非暂态计算机可读介质上。本文中描述的设备、电路和系统可以使用本领域中可用的计算机辅助设计工具来实现,并且可以通过包含这种电路的软件描述的计算机可读文件来体现。这包括但不限于存储器系统100、感测放大器200、感测放大器300和它们的组件。这些软件描述可以是:行为、寄存器传输、逻辑组件、晶体管和布局几何级描述。此外,软件描述可以存储在存储介质上或者通过载波进行通信。

71.可以实现这种描述的数据格式包括但不限于:如c的支持行为语言的格式、如verilog和vhdl的支持寄存器传输级别(rtl)语言的格式、支持几何描述语言的格式(诸如gdsii、gdsiii、gdsiv、cif和mebes),以及其他适当的格式和语言。此外,这种文件在机器可

读介质上的数据传输可以在因特网上通过各种介质以电子方式进行,或者例如经由电子邮件来进行。注意,物理文件可以在机器可读介质上实现,诸如:4mm磁带、8mm磁带、3-1/2英寸软盘介质、cd、dvd等。

72.图10是示出用于包括、处理或生成电路组件1020的表示的处理系统1000的一个实施例的框图。处理系统1000包括一个或多个处理器1002、存储器1004和一个或多个通信设备1006。处理器1002、存储器1004和通信设备1006使用任何适当类型、数目和/或配置的有线和/或无线连接1008进行通信。

73.处理器1002执行存储在存储器1004中的一个或多个过程1012的指令,以响应于用户输入1014和参数1016而处理和/或生成电路组件1020。过程1012可以是用于设计、模拟、分析和/或验证电子电路系统和/或生成用于电子电路系统的光掩模的任何适当的电子设计自动化(eda)工具或其部分。表示1020包括描述存储器系统100、感测放大器200、感测放大器300和它们的组件的数据,如图中所示的。

74.表示1020可以包括行为、寄存器传输、逻辑组件、晶体管和布局几何级描述中的一种或多种。此外,表示1020可以存储在存储介质上或者通过载波进行通信。

75.可以实现表示1020的数据格式包括但不限于:如c的支持行为语言的格式、如verilog和vhdl的支持寄存器传输级别(rtl)语言的格式、支持几何描述语言的格式(诸如gdsii、gdsiii、gdsiv、cif和mebes),以及其他适当的格式和语言。此外,这种文件在机器可读介质上的数据传输可以在因特网上通过各种介质以电子方式进行,或者例如经由电子邮件来进行。

76.用户输入1014可以包括来自键盘、鼠标、语音识别接口、麦克风和扬声器、图形显示器、触摸屏或其他类型的用户接口设备的输入参数。该用户接口可以分布在多个接口设备中间。参数1016可以包括被输入以帮助定义表示1020的规范和/或特性。例如,参数1016可以包括定义设备类型(例如,nfet、pfet等)、拓扑结构(例如,框图、电路描述、原理图等)和/或设备描述(例如,设备属性、设备尺寸、供电电压、仿真温度、仿真模型等)的信息。

77.存储器1004包括存储过程1012、用户输入1014、参数1016和电路组件1020的任何适当类型、数目和/或配置的非暂态计算机可读存储介质。

78.通信设备1006包括将信息从处理系统1000传送给另一个处理或存储系统(未示出)和/或从另一个处理或存储系统(未示出)接收信息的任何适当类型、数目和/或配置的有线和/或无线设备。例如,通信设备1006可以将电路组件1020发送给另一个系统。通信设备1006可以接收过程1012、用户输入1014、参数1016和/或电路组件1020,并且可以使过程1012、用户输入1014、参数1016和/或电路组件1020被存储在存储器1004中。

79.本文讨论的实施方式包括但不限于以下示例:

80.示例1:一种动态随机存取存储器(dram)设备,包括:数字逻辑电路系统,用于至少处理列地址和行地址以检索被存储在动态存储器阵列中的数据,所述数字逻辑电路系统使用第一数字逻辑供电电压水平进行操作;以及感测放大器电路,作为所述动态存储器阵列的部分,用于在感测操作和列操作期间使用所述第一数字逻辑供电电压水平进行操作,并且用于在回写操作期间使用升压位线电压进行操作,该升压位线电压大于所述第一数字逻辑供电电压水平。

81.示例2:根据示例1所述的dram设备,其中所述数字逻辑电路系统是使用高k金属栅

极工艺来实现的。

82.示例3:根据示例1所述的dram设备,其中所述感测放大器电路包括以双稳态触发器配置的交叉耦合反相器对,所述交叉耦合反相器对被耦合到所述动态存储器阵列的相应位线,所述交叉耦合反相器对各自具有负供电节点和正供电节点。

83.示例4:根据示例3所述的dram设备,其中在回写操作期间,所述升压位线电压被选择性地耦合到所述交叉耦合反相器对的所述正供电节点。

84.示例5:根据示例4所述的dram设备,其中在感测操作和列操作期间,所述第一数字逻辑供电电压水平被选择性地耦合到所述交叉耦合反相器对的所述正供电节点。

85.示例6:根据示例4所述的dram设备,其中在刷新操作期间,所述升压位线电压被选择性地耦合到所述交叉耦合反相器对的所述正供电节点。

86.示例7:根据示例4所述的dram设备,其中所述升压位线电压使用p沟道场效应晶体管(pfet)被选择性地耦合到所述交叉耦合反相器对的所述正供电节点,所述p沟道场效应晶体管(pfet)具有pfet栅极节点,所述pfet栅极节点使用某逻辑来进行控制,该逻辑向所述pfet栅极节点施加一定电压,该电压至少达到所述升压位线电压减去所述pfet的阈值电压。

87.示例8:一种动态随机存取存储器(dram)设备,包括:感测放大器电路,作为动态存储器阵列的部分,用于在第一多个感测操作和第一多个列操作期间使用第一数字逻辑供电电压水平进行操作,并且用于在所述第一多个感测操作中的相应感测操作之后出现的第一多个回写操作期间使用第一位线电压进行操作,以回写由所述第一多个感测操作中的所述相应感测操作感测的数据,该第一位线电压大于所述第一数字逻辑供电电压水平;以及数字逻辑,用于至少处理所接收的命令、列地址和行地址,以检索被存储在所述动态存储器阵列中的数据,所述数字逻辑使用所述第一数字逻辑供电电压水平进行操作。

88.示例9:根据示例8所述的dram,其中所述第一位线电压是基于第一接收命令的。

89.示例10:根据示例9所述的dram,其中所述感测放大器电路用于:基于第二接收命令,并且在感测操作之后出现的回写操作期间,使用第二位线电压进行操作以回写由所述感测操作感测的数据,所述第二位线电压等于所述第一数字逻辑供电电压水平。

90.示例11:根据示例9所述的dram,其中所述感测放大器电路用于:基于第二接收命令,并且在感测操作之后出现的回写操作期间,使用第二位线电压进行操作以回写由所述感测操作感测的数据,所述第二位线电压不等于所述第一位线电压并且大于或等于所述第一数字逻辑供电电压水平。

91.示例12:根据示例10所述的dram,其中所述第二位线电压是基于所述dram的温度。

92.示例13:根据示例8所述的dram,其中所述感测放大器电路用于:基于第一接收命令,将所述动态存储器阵列的相应位线预充电到从所述第一数字逻辑供电电压水平导出的预充电电压。

93.示例14:根据示例8所述的dram,其中所述感测放大器电路用于:基于第一接收命令,使用第二位线电压来执行刷新操作,所述第二位线电压等于所述第一数字逻辑供电电压水平。

94.示例15:一种存储器控制器,包括:命令接口,用于将第一指示符和第二指示符传送到存储器设备,至少基于所述第一指示符,所述存储器设备用于在第一感测操作和第一

列操作期间使用第一数字逻辑供电电压水平来操作多个感测放大器电路,该多个感测放大器电路是所述存储器设备的动态存储器阵列的部分,并且该存储器设备用于在所述第一感测操作之后出现的第一回写操作期间使用第一位线电压进行操作,以回写由所述第一感测操作感测的数据,该第一位线电压大于所述第一数字逻辑供电电压水平;至少基于所述第二指示符,所述存储器设备用于在第二感测操作之后出现的第二回写操作期间使用第二位线电压进行操作,以回写由所述第二感测操作感测的数据,该第二位线电压等于所述第一数字逻辑供电电压水平;以及数据接口,用于接收由所述第一多个感测操作中的相应感测操作感测的数据。

95.示例16:根据示例15的所述存储器控制器,其中所述第一指示符是基于命令的。

96.示例17:根据示例15的所述存储器控制器,其中所述命令接口用于将第三指示符传送到所述存储器设备,所述存储器设备用于:基于所述第三指示符,并且在第三感测操作之后出现的第三回写操作期间,使用第三位线电压来操作所述多个感测放大器电路以回写由所述第三感测操作感测的数据,所述第三位线电压不等于所述第一位线电压并且大于或等于所述第一数字逻辑供电电压水平。

97.示例18:根据示例15所述的存储器控制器,其中所述第三指示符是基于命令的。

98.示例19:根据示例15所述的存储器控制器,其中所述第一位线电压是基于所述存储器设备的温度的。

99.示例20:根据示例17所述的存储器控制器,其中所述第三位线电压是基于所述存储器设备的温度的。

100.本发明的前述描述出于说明和描述的目的而被呈现。不旨在穷举本发明或将本发明限制为所公开的精确形式,并且根据以上教导,其他修改和变型是可能的。实施例被选择和描述是为了最好地解释本发明的原理及其实际应用,从而使得本领域其他技术人员能够以适于预期的特定用途的各种实施例和各种修改来最好地利用本发明。意图在于,将所附权利要求解释为包括本发明的其他备选实施例,除非受到现有技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1