光接收元件和电子设备的制作方法

1.本公开涉及光接收元件和电子设备。具体地,本公开涉及检测来自物体的光的光接收元件和其中使用光接收元件的电子设备。

背景技术:

2.常规,使用其中放置多个像素的光接收元件,该像素包括检测来自物体的光的光电转换单元。光接收元件例如用于测量到物体的距离的测距装置。可以通过利用来自附接的光源的光照射对象、检测经对象反射的光以及测量来自光源的光在对象与光源之间往复运动的时间来测量到对象的距离。这种用于测量到物体的距离的光接收元件需要以高速高灵敏度检测光。用作光电转换单元的是作为一种光电二极管的雪崩光电二极管(apd)或单光子雪崩二极管(spad)。这些二极管是在施加接近击穿电压的反向偏压的同时执行光电转换的光电二极管。这些二极管实现具有高灵敏度的高速响应。

3.光电探测器被用作光接收元件。光电检测器包括例如作为像素中的光电转换单元布置的apd、分离相邻像素的分离区域以及分离区域的侧壁上的霍尔存储区域(例如,参见ptl1)。从形成在半导体基板的端面上的像素边界处的界面状态发射的电子被霍尔存储区域捕获,从而减少由来自界面状态的电子引起的暗电流。这里,暗电流是基于与入射光无关地产生的电荷的电流,并且是信号输出误差(噪声)的原因。

4.上述光电探测器中,apd的信号通过电极焊盘传输到外部。电极焊盘设置在与半导体基板的布置有apd的正面相邻的布线层中,并且位于从半导体基板的后侧形成的焊盘开口的底部。通过所述焊盘开口进行引线接合,然后将接合线连接至所述电极焊盘。电极焊盘的信号可经由焊线传输至外部电子电路等。

5.[引用列表]

[0006]

[专利文献]

[0007]

[ptl 1]

[0008]

jp 2018-201005 a

技术实现要素:

[0009]

[技术问题]

[0010]

遗憾的是,前述技术可能导致电极焊盘和接合线之间的不良连接。为了提高灵敏度,光电转换单元形成在具有相对大厚度的半导体基板上。在进行测距时,使用红外光,光电转换单元接收红外光。由于长波红外光到达半导体基板的相对深的区域,所以使用具有大厚度的半导体基板。具有大厚度的半导体基板具有深的焊盘开口。这导致难以形成焊盘开口,增加了故障发生的概率。具体而言,在焊盘开口部的底部的电极焊盘的表面产生蚀刻残渣。此外,通过蚀刻产生的反应生成物可以不被排出而沉积在焊盘开口的底部附近。在这种情况下,堆积的反应生成物有可能腐蚀电极焊盘。这些故障可能导致电极焊盘与接合线之间的不良连接。

[0011]

考虑到上述问题设计了本公开。本公开的目的是防止在电极焊盘与接合线之间发生不良连接。

[0012]

[问题的解决方案]

[0013]

已经设计本公开以解决这些问题。本公开的第一方面是一种光接收元件,包括:布线区域,布置为紧邻半导体基板的正面,布线区域包括用于传输信号的布线层和用于使布线层绝缘的绝缘层,布线层连接至布置在半导体基板中并且对入射光执行光电转换的光电转换单元;电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;第一凹部,其形成在所述半导体基板的背面,所述背面与所述半导体基板的所述正面相反,所述第一凹部的所述底部在所述半导体基板的所述正面附近且在所述电极焊盘附近;以及第二凹部,其形成在上述第一凹部的正面,并且具有形成在上述电极焊盘的表面上的底部。

[0014]

在第一方面中,第二凹部可以被配置为具有与第一凹部不同的开口尺寸。

[0015]

在第一方面中,在半导体基板的背面,第二凹部在平面图中可以具有与第一凹部不同的开口面积。

[0016]

在第一方面中,第二凹部在半导体基板的正面在平面图中可以与第一凹部具有不同的开口面积。

[0017]

在第一方面中,第二凹部可以具有互不相同的开口面积和底部面积。

[0018]

在第一方面中,第二凹部在半导体基板的背面的形状可以比第二凹部的底面侧的形状大。

[0019]

在第一方面中,第二凹部的截面可以是锥形。

[0020]

在第一方面中,第二凹部在截面上可以具有倾斜角度不同的多个锥形形状。

[0021]

在第一方面中,第一凹部可以具有互不相同的开口面积和底部面积。

[0022]

在第一方面中,第一凹部在半导体基板的背面的形状可以比第一凹部的底面的形状大。

[0023]

在第一方面中,第一凹部的截面可以是锥形。

[0024]

在第一方面中,第一凹部可以具有竖直壁面。

[0025]

在第一方面中,第一凹部可以被配置为具有弯曲侧面。

[0026]

在第一方面中,第一凹部可以具有截面呈线性形状的底部。

[0027]

在第一方面中,第一凹部可以具有弯曲底部。

[0028]

在第一观点中,可以在蚀刻时在第一凹部堆积反应生成物。

[0029]

在第一方面中,光电转换单元可以包括光电二极管。

[0030]

在第一方面中,光电转换单元可包括光电二极管,光电二极管将通过入射光的光电转换产生的电荷乘以高反向偏压。

[0031]

在第一方面中,光电转换单元可以允许在包括p型半导体区域和n型半导体区域的pn结处将所产生的电荷相乘。

[0032]

在第一方面中,光电转换单元可以具有包括n型半导体区域的阴极区域。

[0033]

在第一方面中,光电转换单元可具有布置在半导体基板的正面上的阴极区域。

[0034]

在第一方面中,光电转换单元可以具有设置在半导体基板的正面上的阳极区域。

[0035]

本公开的第二方面是一种光接收元件,包括:布线区域,布置为紧邻半导体基板的

正面,布线区域包括用于传输信号的布线层和用于使布线层绝缘的绝缘层,布线层连接至布置在半导体基板中并且对入射光执行光电转换的光电转换单元;电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;第一凹部,其形成在半导体基板的背面,且其底部不到达电极焊盘的程度;以及第二凹部,其被配置为底部从第一凹部的底部到达电极焊盘。

[0036]

本公开的第三方面是光接收元件,该光接收元件包括:布线区域,布置为紧邻半导体基板的正面,布线区域包括用于传输信号的布线层和用于使布线层绝缘的绝缘层,布线层连接至布置在半导体基板中并且对入射光执行光电转换的光电转换单元;电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;第一凹部,其形成在所述半导体基板的背面,所述背面与所述半导体基板的所述正面相反,所述第一凹部的所述底部在所述半导体基板的所述正面附近且在所述电极焊盘附近;第二凹部,其形成在所述第一凹部的正面,并且形成在所述电极焊盘的表面;以及处理基于光电转换产生的信号的处理电路。

[0037]

在第三方面中,光电转换单元可以对从光源发射、经对象反射并进入光电转换单元的入射光执行光电转换,并且处理电路可以执行通过测量从来自光源的光发射到信号的产生的时间来测量到对象的距离的处理。

[0038]

在第三方面中,处理电路可执行检测信号的改变的处理。

[0039]

在第三方面中,所述处理电路可以通过与预定阈值比较来检测所述改变。

[0040]

在第三方面中,所述处理电路可以设置在接合到所述半导体基板的另一半导体基板上。

[0041]

根据本公开的各方面,电极焊盘在半导体基板的背面上通过第一凹部和第二凹部开口。通过形成凹部的两个步骤,电极焊盘在半导体基板的背面开口。

附图说明

[0042]

图1是示出根据本公开的第一实施例的光接收元件的配置实例的示图。

[0043]

图2是示出根据本公开的第一实施例的像素的配置实例的示图。

[0044]

图3是示出根据本公开第一实施例的像素的配置实例的截面图。

[0045]

图4是示出根据本公开第一实施例的像素的另一配置实例的截面图。

[0046]

图5是示出了根据本公开第一实施例的焊盘开口的配置实例的平面图。

[0047]

图6是示出了根据本公开第一实施例的焊盘开口的配置实例的截面图。

[0048]

图7是示出焊盘开口的配置的比较实例的截面图。

[0049]

图8是示出了根据本公开第一实施例的焊盘开口的制造方法的实例的示图。

[0050]

图9是示出了根据本公开第一实施例的焊盘开口的制造方法的实例的示图。

[0051]

图10是示出了根据本公开的第二实施例的焊盘开口的配置实例的截面图。

[0052]

图11是示出根据本公开的第二实施例的焊盘开口的另一配置实例的截面图。

[0053]

图12是示出了根据本公开第二实施例的焊盘开口的另一配置实例的截面图。

[0054]

图13是示出了根据本公开的第三实施例的像素的配置实例的截面图。

[0055]

图14是示出了根据本公开的技术可应用于的测距装置的光接收元件的配置实例的示图。

[0056]

图15是示出了根据本公开的技术可应用于的测距装置的像素的配置实例的电路图。

[0057]

图16是示出了根据本公开的技术可应用于的测距装置的成像装置的配置实例的示图。

[0058]

图17是示出根据本公开的技术可应用于的dvs的光接收元件的配置实例的示图。

[0059]

图18是示出根据本公开的技术可应用的dvs的像素的配置实例的示图。

[0060]

图19是示出根据本公开的技术可适用的用于dvs的电流-电压转换电路的配置实例的示图。

[0061]

图20是示出根据本公开的技术可应用的dvs的差动装置和量化器的配置实例的示图。

[0062]

图21是示出根据本公开的技术可应用于的dvs的成像装置的配置实例的示图。

具体实施方式

[0063]

以下,参照附图对用于实施本发明的方式(以下称为实施例)进行说明。在以下附图中,相同或相似的部分由相同或相似的参考标号和符号表示。另外,将按照以下顺序描述实施例。

[0064]

1.第一实施例

[0065]

2.第二实施例

[0066]

3.第三实施例

[0067]

4.应用于测距设备的实例

[0068]

5.应用至dvs的实例

[0069]

《1.第一实施例》

[0070]

[光接收元件的配置]

[0071]

图1是示出根据本公开的第一实施例的光接收元件的配置实例的示图。图1是示出了光接收元件2的配置实例的平面图。平面图示出了用光接收元件2的入射光照射的光接收表面的配置。

[0072]

像素阵列单元10被设置在光接收元件2的光接收表面上。像素阵列单元10是布置在光接收元件2的中心部分处的区域,并且包括用于检测入射光的像素(稍后描述的像素100),像素以二维晶格形式布置。在像素100中,设置用于入射光的光电转换的光电转换单元(稍后描述的光电转换单元101)。接收的光信号根据由光电转换单元101的光电转换产生的电荷产生,并且从像素100输出。所接收的光信号允许入射光的检测。多个焊盘开口180布置在光接收元件2的端部上。在焊盘开口180的底部,布置电极焊盘(稍后描述的电极焊盘128和148)。如后面将要描述的,光接收元件2被配置为彼此接合的两个半导体芯片。

[0073]

[像素配置]

[0074]

图2是示出根据本公开的第一实施例的像素的配置实例的示图。图2是示出了像素100的配置实例的平面图。在图2的像素100中示出是形成在半导体基板110上的半导体区域(半导体区域111和113)、设置在像素100的边界处并且被配置为类似穿透半导体基板110的壁的分离区域150、以及布线层122至124。在图2中具有点阴影线的区域表示半导体区域111等,而具有对角线阴影线的区域表示布线层122等。

[0075]

半导体区域111设置在像素100的中心部分并构成阴极区域。半导体区域113被布置在像素100的圆周边缘处并且构成阳极区域。布线层122构成阳极布线,并与半导体区域113连接。布线层123构成阴极布线,与半导体区域111连接。布线层124是用于屏蔽的接地线。屏蔽抑制电噪声的影响。布线层124设置在布线层122和123之间的区域中。

[0076]

[截面中的像素的配置]

[0077]

图3是示出根据本公开第一实施例的像素的配置实例的截面图。图3是沿着图1的线a-a’截取的截面图;并且示出了光接收元件2和像素100的配置实例。如图3所示光接收元件2被配置为彼此结合的传感器芯片191和逻辑芯片192。传感器芯片191是其中布置光电转换单元101的半导体芯片。稍后将描述光电转换单元101。逻辑芯片192是其中设置处理电路以处理由光电转换单元101产生的信号的半导体芯片。

[0078]

图3中的像素100包括半导体基板110、布线区域120、半导体基板130、布线区域140、分离区域150、保护膜171和片上透镜172。半导体基板110、绝缘层121和布线层122至124布置在传感器芯片191中。半导体基板130、绝缘层141和布线层142设置在逻辑芯片192中。

[0079]

半导体基板110是其中设置有用于入射光的光电转换的光电转换单元101的半导体基板。例如,由硅(si)制成的半导体基板可用作半导体基板110。图3中的光电转换单元101是spad配置的示例。光电转换单元101包括半导体基板110的阱区111、设置在阱区111中的n型半导体区域112、p型半导体区域113和半导体区域114。构成阴极区域的n型半导体区域112与p型半导体区域113构成pn结。通过阱区111向pn结施加反向偏压,形成耗尽层。

[0080]

通过图3的光电转换单元101的光电转换在阱区111中执行。当由光电效应产生的电荷的电子由于漂移而到达pn结的耗尽层时,电子被基于反向偏置电压的电场加速。超过击穿电压的反向偏置电压被施加至构成spad的光电转换单元101。具体而言,施加约20v的反向偏压。由反向偏置电压产生的强电场引起连续的电子雪崩,从而快速地增加电荷。由此,光电转换单元101可以检测单个光子的进入。通过布置由此配置的光电转换单元101,像素100可以被配置为高灵敏度。半导体区域112和113之间的界面的pn结附近的区域是电荷被倍增的区域。该区域被称为倍增区域。p型半导体区域114被设置为紧邻阱区111并且构成阳极区域。p型半导体区域114被配置为包围n型半导体区域112附近的阱区111。

[0081]

半导体基板110被配置为具有相对大的厚度。该配置旨在改善光电转换单元101的灵敏度,该光电转换单元101具有构成spad的阱区111的大厚度。例如,半导体基板110可以被配置为具有几μm的厚度。阱区111设置在半导体基板110的背面,并且入射光从半导体基板110的背面进入。半导体基板110的背面相当于光入射面。在半导体基板110的正面(即,与背面相反的表面)上,布置布线区域120。布线区域120在后面叙述。分别构成阴极区域和阳极区域的半导体区域112和114设置在半导体基板110的正面。

[0082]

光电转换单元101的配置不限于该实例。例如,半导体区域112、113和114的导电类型可以彼此交换。具体地,可以使用p型半导体区域112以及n型半导体区域113和114。在这种情况下,半导体区域112用作阳极区域,而半导体区域114用作阴极区域。此外,将稍后描述的霍尔存储区域115改变为电子存储区域115。电子存储区域115是包括n型半导体并存储电子的区域。半导体区域的导电类型可以被表示为第一导电类型和第二导电类型,而不是p型和n型。

[0083]

霍尔存储区域115可以设置在半导体基板110中,与稍后将描述的分离区域150相邻。霍尔存储区域115被设置为捕获从在半导体基板的端面上形成的界面状态发射的电子。可以使用p型半导体区域配置霍尔存储区域115。来自界面状态的电子通过与存储在霍尔存储区域115中的霍尔重组来捕获。通过设置霍尔存储区域115,可以减少由来自界面状态的电子引起的暗电流。此外,来自界面状态的电子的加速和倍增可能导致故障。通过设置霍尔存储区域115,可以防止发生暗电流和故障。图3中的霍尔存储区域115设置在构成阳极的半导体区域114的旁边并且电连接到阳极。另一霍尔存储区域可布置在半导体基板110的背面上的界面处。

[0084]

布线区域120是布置在半导体基板110的正面并且包括用于将信号传输至光电转换单元101等的布线的区域。在布线区域120中,设置绝缘层121和布线层122至124。布线层122至124是用于传输光电转换单元101的信号等的布线。布线层122等可由诸如铜(cu)的金属制成。绝缘层121使布线层122等绝缘。绝缘层121可由例如氧化硅(sio2)制成。布线区域120还包括用于连接半导体基板110的半导体区域和布线层122的接触插塞125。布线层122经由接触插塞125连接到构成光电转换单元101的阳极区域的半导体区域114。同样,布线层123连接到构成阴极区域的半导体区域112。接触插塞125可由例如钨(w)制成。

[0085]

布线区域120还包括焊盘127和通孔插塞126。焊盘127是设置在布线区域120的前表面的电极。焊盘127例如可以由cu构成。过孔插塞126连接布线层122等和焊盘127。通孔插塞126可由例如cu制成。

[0086]

半导体基板130是接合至半导体基板110的半导体基板。在半导体基板130中,可形成用于处理由光电转换单元101产生的信号的处理电路等的元件的扩散区域。

[0087]

布线区域140是设置在半导体基板130的正面的布线区域。在布线区域140中,布置布线层142和绝缘层141。在布线区域140的表面上,设置焊盘147并通过过孔插塞146连接至布线层142。布线层142和半导体基板130通过接触插塞145彼此连接。当传感器芯片191接合到逻辑芯片192时,焊盘147和焊盘127彼此接合。这使焊盘147和127电连接。信号可以通过焊盘147和焊盘127在设置于半导体基板110和130中的元件之间发射和接收。布线可经配置以连接光电转换单元与处理电路。以这种方式,电连接光电转换单元101和电路的布线可以布置在布线区域120和140中。此外,布线区域120和140可包括构成光学屏蔽的布线层,该光学屏蔽反射已经穿过半导体基板110的入射光并且使光再次进入半导体基板110。

[0088]

分离区域150布置在半导体基板110中像素100之间的边界处,并分离光电转换单元101。分离区域150被配置为像围绕像素100的壁一样并分离相邻像素100的光电转换单元101。此外,分离区域150阻挡入射光。对角地通过相邻像素100的入射光被分离区域150阻挡。这可以减少串扰的发生。如图2所示分离区域150以晶格形式设置。分离区域150可由在穿过半导体基板110形成的凹槽中嵌入的金属材料(诸如w或铝(al))构成。

[0089]

保护膜171设置在半导体基板110的背侧上并保护半导体基板110。该保护膜171例如可以由sio2构成。

[0090]

此外,固定电荷膜可布置在半导体基板110与保护膜171之间。固定电荷膜是设置在半导体基板110的表面上并且具有用于钉扎半导体基板110的界面状态的固定电荷的膜。固定电荷膜例如可以由hfo2构成。

[0091]

固定电荷膜还可设置在半导体基板110的凹槽中,分离区域150设置在凹槽中。此

外,使由金属制成的分离区域150绝缘的绝缘膜可布置成紧邻分离区域150。绝缘膜可以与保护膜171同时形成。

[0092]

片上透镜172是聚集入射光的透镜。片上透镜172在半导体基板110的背面被配置为半球形,并且将入射光聚集到光电转换单元101上。片上透镜172可由诸如氮化硅(sin)的无机材料或者诸如丙烯酸树脂的有机材料制成。

[0093]

在光接收元件2的端部上,布置电极焊盘148和焊盘开口180。电极焊盘148是用于在光接收元件2和光接收元件2外部的电子电路之间传输信号的电极。电极焊盘148设置在逻辑芯片192的布线区域中并且连接至布线层142。焊盘开口180被配置为类似于穿过传感器芯片191和逻辑芯片192的绝缘层141的正面的孔,并且被成形为从光接收元件2的光接收表面到达电极焊盘148的表面。电极焊盘148通过焊盘开口180进行引线接合,从而将电极焊盘148与外部电子电路电连接。电极焊盘148可由例如诸如al或au的金属制成。

[0094]

分离区域150a可布置在焊盘开口180周围。分离区域150a被配置为围绕焊盘开口180并且分离焊盘开口180。此外,分离区域150b可以布置在传感器芯片191的端部上的半导体基板110中。分离区域150b是沿着半导体基板110的外缘配置的分离区域。所布置的分离区域150a和150b可以防止湿气从半导体基板110的端面吸收,从而防止半导体基板110的端面上的裂纹扩展。

[0095]

像素100的配置不限于该实例。例如,多个光电转换单元可以被布置在像素100中。在由此配置的像素100中,分离光电转换单元的分离区域可以设置在其中。可以通过半导体基板110形成分离光电转换单元的分离区域。此外,可以在光电转换单元之间的边界处在半导体基板110和片上透镜172之间设置分离区域。分离区域是在光电转换单元之间的边界阻挡光的分离区域,并且可以由金属膜等构成。可替换地,包括光电转换单元的像素100可以被配置为仅设置在像素100之间的边界处的分离区域。霍尔存储区域115还可设置在半导体基板110的后侧上。

[0096]

[像素的截面的另一配置]

[0097]

图4是示出根据本公开第一实施例的像素的另一配置实例的截面图。图4是示出如图3中的像素100的配置实例的截面视图。像素100与图3中的像素100不同。电极焊盘128代替电极焊盘148而布置。电极焊盘128是设置在传感器芯片191的布线区域120中的电极焊盘,并且连接至逻辑芯片192的布线区域120的布线层或布线区域140的布线层。图4中的焊盘开口180穿过传感器芯片191的半导体基板110形成并且被成形为从光接收元件2的光接收表面到达电极极板128的表面。

[0098]

[焊盘开口的配置]

[0099]

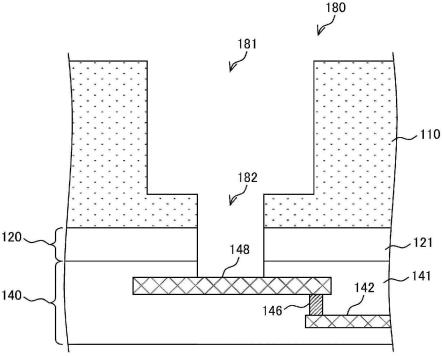

图5是示出了根据本公开第一实施例的焊盘开口的配置实例的平面图。图5是示出了图3中示出的焊盘开口180的配置实例的平面图参照图5,下面将具体描述焊盘开口180的配置。

[0100]

如上所述,焊盘开口180是到达设置在光接收元件2的端部上的布线区域140中的电极焊盘148的开口和从半导体基板110的背侧产生的开口。图5中的虚线矩形表示电极焊盘148的外形。图5中的焊盘开口180包括第一凹部181和形成在第一凹部181内部的第二凹部182。图5示出了被配置为类似矩形的电极焊盘148和焊盘开口180的实例。

[0101]

[焊盘开口在截面中的配置]

[0102]

图6是示出了根据本公开第一实施例的焊盘开口的配置实例的截面图。电极焊盘148设置在布线区域140中,布线区域140设置在半导体基板130的正面。如上所述,半导体基板110和半导体基板130彼此接合。此时,布线区域120和布线区域140彼此接合。因此,布线区域140设置在半导体基板110的正面。电极焊盘148经由过孔插塞146连接至布线层142。如图3所示,布线层142经由焊盘147和127连接到布线区域120的布线层122等,并且连接到光电转换单元101。焊盘开口180包括第一凹部181和第二凹部182。

[0103]

第一凹部181是形成在半导体基板110的背面的电极焊盘148附近的凹部。第一凹部181形成在半导体基板110的背面上并且具有靠近半导体基板110的正面的底部。第一凹部181可以通过蚀刻半导体基板110来形成。对于该蚀刻,可以使用各向异性的干蚀刻。第一凹部181在半导体基板110的区域具有底部,从而保护电极焊盘148附近的布线层142。图6示出了被配置为竖直壁面的第一凹部181的实例。图6中的第一凹部181示出了底部在截面中线性成形的实例。

[0104]

第二凹部182是形成在第一凹部181的正面上的凹部。第二凹部182的底部形成在电极焊盘148的表面上。换言之,第二凹部182是成形为从第一凹部181的底部到达电极焊盘148的凹部。第二凹部182可以被配置为具有与第一凹部181不同的开口尺寸。具体地,第二凹部182可以被配置为具有比第一凹部181更小的开口尺寸。第二凹部182可以被配置为具有比第一凹部181的底部更小的开口尺寸。另外,第二凹部183在半导体基板110的背面的开口面积与第一凹部181的俯视开口面积不同。另外,第二凹部183在半导体基板110的正面侧的开口面积与第一凹部181的俯视开口面积不同。图6中的第二凹部182示出了竖直壁面的实例。

[0105]

可以通过蚀刻半导体基板110和绝缘层121和141来形成第二凹部182。如上所述,图6中的焊盘开口180可以通过两步蚀刻在两个凹部上形成。可以对第一凹部181和第二凹部182施加不同的蚀刻条件。例如,当形成第二凹部182时,可以使用不同于第一凹部181的蚀刻气体并且在蚀刻气体离子化时使用功率和气体压力执行蚀刻。

[0106]

应当理解,图6中的焊盘开口180的配置也可应用于在图4所示的像素100。在这种情况下,电极焊盘128布置在焊盘开口180的底部。

[0107]

[焊盘开口的比较实例]

[0108]

图7是示出焊盘开口的配置的比较实例的截面图。图7是示出了通过单步蚀刻形成的焊盘开口180的实例的示图。

[0109]

图7中的a表示具有在半导体基板110的区域中在截面上倒锥形的凹部401的焊盘开口的实例。在用于形成凹部401的干法蚀刻中,分别连续地蚀刻构成半导体基板110和绝缘层121的si和sio2。在这种情况下,碳氟化合物气体被用作蚀刻气体。利用该蚀刻气体对sio2进行蚀刻,生成氟化合物的反应生成物。如果半导体基板110具有较大的厚度,则凹部401相对较深,使得反应生成物可以不被排出而部分地沉积在凹部401的壁面上。此外,如在图7中示出的,而截面呈倒锥形的凹部401可以增加倒锥形侧壁上的反应的产生。图7中的反应生成物402表示沉积的氟化合物。反应生成物402对电极焊盘148的腐蚀可导致电极焊盘和接合线之间的不良连接。

[0110]

图7中的b表示截面为纵型的凹部403的一例。如果凹部403相对较深,则底部难以蚀刻,在电极焊盘148的表面上留下蚀刻残渣404。蚀刻残余物404可导致电极焊盘148与接

合线之间的不良连接。

[0111]

如上所述,通过单步蚀刻形成的相对较深的焊盘开口180可能导致故障。

[0112]

[焊盘开口的制造方法]

[0113]

图8以及图9是示出了根据本公开的第一实施例的焊盘开口的制造方法的实例的示图。图8以及图9是示出了焊盘开口180的制造过程的实例的示图。

[0114]

首先,具有布线区域120的半导体基板110和具有布线区域140的半导体基板130(未示出)相互接合以接合绝缘层121和绝缘层141。接着,在半导体基板110的背面配置抗蚀剂405。在该抗蚀剂405中,开口406设置在要形成第一凹部181的区域中(图8中的a)。

[0115]

接着,以抗蚀剂405为掩模对半导体基板110进行蚀刻。对于该蚀刻,可以使用干法蚀刻。因此,形成凹部181(图8中的b)。

[0116]

然后去除抗蚀剂405,并且布置另一抗蚀剂408。在该抗蚀剂408中,开口409设置在要形成第二凹部182的区域中(图9中的c)。

[0117]

然后使用抗蚀剂408作为掩模进行蚀刻以形成第二凹部182(图9中的d)。此后,去除抗蚀剂408,从而产生焊盘开口180。

[0118]

开口180的配置不限于该实例。例如,开口180还可以配置为具有不同开口大小的三个或更多个凹部。第一凹部181的形状不限于该示例。例如,该配置可以具有弯曲的侧面。

[0119]

在该配置中,第一凹部181和第二凹部182构成焊盘开口180,从而保持电极焊盘148的清洁表面。由此,能够防止引线接合时的电极焊盘与焊线的连接不良。

[0120]

《2.第二实施例》

[0121]

在第一实施例的光接收元件2中,设置具有垂直壁面的第二凹部182。根据本公开的第二实施例的光接收元件2与第一实施例的光接收元件的不同之处在于使用在截面上渐缩的第二凹部。

[0122]

[焊盘开口的配置]

[0123]

图10是示出了根据本公开的第二实施例的焊盘开口的配置实例的截面图。图10是示出了图6中的焊盘开口180的配置实例的截面图配置与在图6中示出的分离区域150不同。设置第二凹部183来代替第二凹部182。

[0124]

图10中的a表示包括第一凹部181和第二凹部183的焊盘开口180的实例。第二凹部183是开口和底部具有不同尺寸的凹部。第二凹部183可以被成形为使得开口和底部具有不同的面积。在该结构中,开口区域表示半导体基板110的背面的表面的开口面积,底部区域表示凹陷部的底部的与半导体基板110的背面的表面平行的表面的面积。例如,可以将第二凹部183配置为在半导体基板110的背面具有大尺寸,在电极焊盘148附近具有小尺寸。图10中的第二凹部183示出了截面逐渐变细的凹部的实例。此外,通过使第二凹部183的截面形成为锥形,能够减少蚀刻时的反应生成物的堆积。

[0125]

图10中的b表示在截面中以不同倾斜角度渐缩的多个第二凹部的实例。图10的b中的焊盘开口180包括第一凹部181、第二凹部183和第二凹部184。第二凹部184是靠近第一凹部181的底部设置的凹部,并且以比第二凹部183的截面更小的倾斜角逐渐变细。第二凹部184设置在第一凹部181和第二凹部183之间。由此,将第二凹部183与第一凹部181的底部接触的部分倒角,能够进一步降低蚀刻时的反应生成物的堆积。

[0126]

图10中的第二凹部183和184可以通过调整抗蚀剂的形状来形成。

[0127]

[焊盘开口的其他配置]

[0128]

图11和图12是示出了根据本公开第二实施例的焊盘开口的其他配置实例的截面图。图11中的a表示开口180的实例,其包括锥形形状的第一凹部181和第二凹部183,其中,开口和底部的尺寸基本相同。图11中的b表示包括锥形形状的第一凹部181和锥形形状的第二凹部183的开口180的实例。图12中的a表示包括具有弯曲侧的第一凹部181的开口180的实例。图12中的b表示包括具有弯曲侧的第二凹部183的开口180的实例。与图10中的开口180类似、开口180可减少在蚀刻期间反应生成物的沉积。还可以理解的是,图12的a中的第一凹部181在底部是弯曲的。

[0129]

除配置之外的光接收元件2的配置与本公开的第一实施例中描述的光接收元件2的配置相同,并且因此省略其描述。

[0130]

如上所述,在截面上锥形的第二凹部用于根据本公开的第二实施例的光接收元件2,从而减少蚀刻期间反应生成物的沉积。

[0131]

《3.第三实施例》

[0132]

对于根据第一实施例的光接收元件2,使用光电转换单元101。光电转换单元101包括将通过spad或apd的光电转换生成的电荷乘以反向偏置电压的光电二极管。根据本公开的第四实施例的光接收元件2与第一实施例的光接收元件的不同之处在于使用包括典型光电二极管的光电转换单元。

[0133]

[截面中的像素的配置]

[0134]

图13是示出了根据本公开的第三实施例的像素的配置实例的截面图。图13是示出了如图3中的像素100的配置实例的截面视图。像素100与图3中的像素100不同。设置包括光电二极管的光电转换单元201。

[0135]

图13中的光电转换单元201包括在半导体基板110中的p型阱区111和设置在阱区111中的n型半导体区域116。使用n型半导体区域116与半导体区域116周围的p型阱区111之间的pn结配置的光电二极管对应于光电转换单元201。阱区111和半导体区域116分别构成阳极区域和阴极区域。

[0136]

在图13的半导体基板110中、进一步设置半导体区域117和半导体区域118。半导体区域117是具有相对高的n型杂质浓度的半导体区域以及与半导体区域116相邻并且电连接到半导体区域116的半导体区域。接触插塞125连接至半导体区域117。半导体区域118是具有相对高的p型杂质浓度的半导体区域以及与阱区相邻并与阱区电连接的半导体区域。接触插塞125还连接至半导体区域118。半导体区域118是构成所谓的阱接触的半导体区域。

[0137]

布线层122、123配置在布线区域120中。布线层122经由接触插塞125和半导体区域118连接至构成阳极区域的阱区111。布线层123经由接触插塞125和半导体区域117连接至构成阴极区域的半导体区域116。省略布线层124。

[0138]

同样在图13的焊盘开口180中、第一凹部181和第二凹部182被设置为如在图5中示出的由此防止电极焊盘148与接合线之间的不良连接的发生。

[0139]

除配置之外的光接收元件2的配置与本公开的第一实施例中描述的光接收元件2的配置相同,并且因此省略其描述。

[0140]

如上所述,在根据本公开的第三实施例的光接收元件2中使用光电转换单元101时,焊盘开口180包括第一凹部181和第二凹部182,从而防止电极焊盘148与接合线之间的

不良连接的发生。

[0141]

《4.应用于测距装置的实例》

[0142]

根据本公开的技术可以应用于各种产品。例如,根据本公开的技术可应用于测距装置。测距装置是用于测量到物体的距离的装置。

[0143]

[光接收元件的配置]

[0144]

图14是示出了根据本公开的技术可应用于的测距装置的光接收元件的配置实例的示图。图14中的光接收元件2包括像素阵列单元10、偏置电源单元20和接收光信号处理单元30。

[0145]

像素阵列单元10被配置为具有以二维晶格形式布置的像素100,像素100包括用于入射光的光电转换的光电转换单元。像素100检测入射光并且输出接收的光信号作为检测结果。对于光电转换单元,例如,可以使用apd或spad。在下文中,假设像素100包括布置为光电转换单元的spad。信号线21和31连接到每个像素100。信号线21是提供像素100的偏压的信号线。信号线31是传输从像素100接收的光信号的信号线。图14的像素阵列单元10示出了像素100放置在四行和五列中的实例。布置在像素阵列单元10中的像素100的数量不限于此。

[0146]

偏置电源单元20是向像素100提供偏置电压的电源。偏置电源单元20经由信号线21提供偏置电压。

[0147]

接收光信号处理单元30处理从布置在像素阵列单元10中的多个像素100输出的接收光信号。例如,接收光信号处理单元30的处理对应于基于由像素100检测的入射光来检测距物体的距离的处理。具体地,接收光信号处理单元30可以执行tof(飞行时间)型距离检测,当测量至成像设备(诸如车载相机)中的远程对象的距离时使用该tof型距离检测。在该距离检测中,通过利用来自设置在成像装置中的光源的光照射对象、检测经对象反射的光以及测量来自光源的光在对象与光源之间往复运动的时间来检测距离。将能够以高速检测光的spad用作用于距离检测的设备。接收光信号处理部30是权利要求中记载的处理电路的一例。

[0148]

下面将描述设置在根据上述实施例的像素阵列单元10中的像素100的电路配置。

[0149]

[像素配置]

[0150]

图15是示出了根据本公开的技术可应用于的测距装置的像素的配置实例的电路图。图15是示出在图14中示出的像素100的配置实例的电路图。图15中的像素100包括光电转换单元101、电阻器102和反相缓冲器103。图15中的信号线21包括施加光电转换单元101的击穿电压的信号线vbd和提供用于检测光电转换单元101的击穿状态的电力的信号线vd。

[0151]

光电转换单元101的阳极连接到信号线vbd。光电转换单元101的阴极连接到电阻器102的一端和反相缓冲器103的输入端。电阻器102的另一端连接到信号线vd。反相缓冲器103的输出连接到信号线31。

[0152]

在图15的光电转换单元101中、信号线vbd和信号线vd施加反向偏置电压。

[0153]

电阻器102是用于执行淬火的电阻器。淬火是用于使处于击穿状态的光电转换单元101返回到稳定状态的处理。当光电转换单元101通过由入射光引起的倍增而被置于击穿状态时,快速反向电流通过光电转换单元101。反向电流使电阻102的端子电压上升。因为电阻器102与光电转换单元101串联连接,所以由电阻器102产生电压降,并且使光电转换单元

101的端子电压降至能够保持击穿状态的电压以下。由此,光电转换单元101能够从击穿状态返回到稳态。电阻器102可以替换为包括mos晶体管的恒流电路。

[0154]

反转缓冲器103是基于光电转换单元101到击穿状态的转变和返回来整形脉冲信号的缓冲器。由于反相缓冲器103,基于穿过光电转换单元101的电流的接收的光信号根据辐射光生成并被输出到信号线31。

[0155]

[成像装置的配置]

[0156]

图16是示出了根据本公开的技术可应用于的测距装置的成像装置的配置实例的示图。图16是示出了构成测距装置的成像装置1的配置实例的框图。图16中的成像装置1包括光接收元件2、控制单元3、光源装置4和透镜5。图16示出了距离测量的对象601。

[0157]

透镜5是用于在光接收元件2上形成物体的图像的透镜。在图10中示出的光接收元件2可以用作图16中的光接收元件2。

[0158]

光源装置4向进行测距的对象物照射光。作为光源装置4,例如能够使用射出红外光的激光光源。

[0159]

控制单元3控制整个成像装置1。具体地,控制单元3控制光源装置4向对象601发射出射光束602,并且向光接收元件2通知发射的开始。被通知出射光束602的发射的光接收元件2检测来自对象601的反射射线603,测量从出射光束602的发射到反射光束603的检测的时间,并且测量到对象601的距离。所测量的距离作为距离数据输出至成像装置1的外部。成像装置1是在权利要求中描述的电子设备的实例。

[0160]

《5.应用至dvs的实例》

[0161]

根据本公开的技术可以应用于各种产品。例如,根据本公开的技术可以应用于动态视觉传感器(dvs)。dvs是输出关于具有改变的亮度的像素的信息的摄像装置。

[0162]

[光接收元件的配置]

[0163]

图17是示出根据本公开的技术可应用于的dvs的光接收元件的配置实例的示图。图17中的光接收元件2包括像素阵列单元10、行驱动电路50、列驱动电路60和信号处理电路70。

[0164]

像素阵列单元10被配置为具有以二维晶格形式布置的像素100,像素100包括用于入射光的光电转换的光电转换单元。像素100检测入射光并且如果检测的入射光改变则输出检测信号。在下文中,假设光电二极管被设置为像素100中的光电转换单元。信号线51、61和71连接到每个像素100。信号线51是用于传输行驱动信号的信号线。信号线51是用于传输列驱动信号的信号线。信号线71是用于传送来自像素100的检测信号的信号线。图17的像素阵列单元10示出了像素100放置在四行和四列中的实例。布置在像素阵列单元10中的像素100的数量不限于此。

[0165]

行驱动电路50选择像素阵列单元10的行地址,并且使与所选行地址对应的像素100输出检测信号。行驱动电路50将控制信号(行驱动信号)输出至信号线51。

[0166]

列驱动电路60选择像素阵列单元10的列地址,并且使与所选列地址对应的像素100输出检测信号。列驱动电路60将控制信号(列驱动信号)输出至信号线61。

[0167]

信号处理电路70对来自像素100的检测信号执行预定信号处理。信号处理电路70将检测信号与像素阵列单元10的像素阵列100相关联以生成二维图像数据,然后执行图像识别等。信号处理电路70是权利要求中描述的处理电路的示例。

[0168]

[像素配置]

[0169]

图18是示出根据本公开的技术可应用的dvs的像素的配置实例的示图。图18中的像素100包括光电转换单元201、电流-电压转换电路210、缓冲器220、差动装置230、量化器240和传送电路250。

[0170]

光电转换单元201检测入射光。光电转换单元201将对应于入射光的吸收电流输出到后级的电流-电压转换电路210。

[0171]

电流-电压转换电路210是将来自光电转换单元201的输出电流转换成电压的电路。在转换期间,执行对数压缩并且将压缩的电压信号输出至缓冲器220。

[0172]

缓冲器220是放大电流-电压转换电路210的电压信号并将该信号输出至后级的差动装置230的缓冲器。

[0173]

差动装置230检测从缓冲器220输出的电压信号的差,从而检测电压信号的变化。在从行驱动电路50输入行驱动信号之后,差动装置230开始检测电压信号的变化。所检测的电压信号的变化通过信号线239输出。

[0174]

量化器240对来自差动装置230的电压信号进行量化并且输出信号作为检测信号。检测信号通过信号线249输出。

[0175]

传送电路250是基于来自列驱动电路60的列驱动信号将检测信号输出至信号处理电路70的电路。

[0176]

[电流-电压转换电路的配置]

[0177]

图19是示出根据本公开的技术可适用的用于dvs的电流-电压转换电路的配置实例的示图。图19是示出电流-电压转换电路210的配置实例的电路图。图19的电流-电压转换电路210包括mos晶体管211至213和电容器214。作为mos晶体管211和213,可以使用n沟道mos晶体管。作为mos晶体管212,可以使用p沟道mos晶体管。此外,电源线vdd和电源线vbias设置在图19的电流-电压转换电路210中电源线vdd是用于向电流电压转换电路210供电的电源线。电源线vbias是用于提供偏置电压的电源线。图19还示出了光电转换单元201。

[0178]

光电转换单元201的阳极接地,光电转换单元201的阴极连接到mos晶体管211的源极、mos晶体管213的栅极和电容器214的一端。电容器214的另一端连接到mos晶体管211的栅极、mos晶体管212的漏极、mos晶体管213的漏极以及信号线219。mos晶体管211的源极连接到电源线vdd,mos晶体管213的源极接地。mos晶体管212的栅极连接到电源线vbias,源极连接到电源线vdd。

[0179]

mos晶体管211是向光电转换单元201提供电流的mos晶体管。与入射光对应的吸收电流通过光电转换单元201。mos晶体管211提供吸收电流。此时,mos晶体管211的栅极由稍后将描述的mos晶体管213的输出电压驱动,并且输出等于光电转换单元201的吸收电流的源电流。mos晶体管的栅极-源极电压vgs对应于源电流,使得mos晶体管的源极电压对应于光电转换单元201的电流。由此,光电转换单元201的电流被转换为电压信号。

[0180]

mos晶体管213是放大mos晶体管211的源极电压的mos晶体管。mos晶体管212构成mos晶体管213的恒定电流负载。放大的电压信号被输出到mos晶体管213的漏极。电压信号输出到信号线219,并返回到mos晶体管211的栅极。当mos晶体管211的vgs等于或低于阈值电压时,源极电流相对于vgs的变化呈指数变化。因此,mos晶体管213的输出电压(即,返回至mos晶体管211的栅极的输出电压)对应于通过对光电转换单元201的输出电流进行对数

压缩而获得的电压信号,输出电流等于mos晶体管211的源极电流。

[0181]

电容器214是用于相位补偿的电容器。电容器214连接在mos晶体管213的漏极与栅极之间,并且对构成放大器电路的mos晶体管213执行相位补偿。

[0182]

[差动装置和量化器的配置]

[0183]

图20是示出根据本公开的技术可应用的dvs的差动装置和量化器的配置实例的示图。图20是示出差动装置230和量化器240的配置实例的电路图。

[0184]

图20的差动装置230包括反相放大器231、电容器232和233、以及开关234。

[0185]

电容器232连接在信号线229与反相放大器231的输入之间。反相放大器231的输出连接至信号线239。并联连接的电容器233和开关234连接在反相放大器231的输入与输出之间。开关234的控制输入端连接到信号线51。

[0186]

电容器232是去除从缓冲器220输出的电压信号的直流分量的耦合电容器。与电压信号的改变对应的信号由电容器232发送。

[0187]

反相放大器231是根据由电容器232传输的电压信号的变化对电容器233充电的放大器。反相放大器231和电容器232构成积分电路并且对由电容器232传输的电压信号的变化进行积分。

[0188]

开关234是使电容器233放电的开关。使开关234导通以使电容器232放电并且将电压信号的变化重置为0v,该变化由电容器232积分。开关234由信号线51传输的行驱动信号控制。

[0189]

差动装置230整合电压信号的变化并且输出整合的变化,该变化对应于响应于行驱动信号重置之后的周期中的入射光。由此,能够降低噪声的影响。

[0190]

量化器240包括比较器241和242。信号线239连接至比较器241的非反相输入端和比较器242的反相输入端。预定阈值电压vth1被施加到比较器241的反相输入端,并且预定阈值电压vth2被施加到比较器242的非反相输入端。比较器241和242的输出各自构成信号线249。

[0191]

比较器241比较阈值电压vth1和来自差动装置230的输出电压。当来自差动装置230的输出电压高于阈值电压vth1时,输出值“1”。

[0192]

比较器242比较阈值电压vth2和来自差动装置230的输出电压。当来自差动装置230的输出电压低于阈值电压vth2时,输出值“1”。

[0193]

阈值电压vth1被设定为比差动装置230被复位时所确定的输出电压高的阈值电压,阈值电压vth2被设定为比差动装置230被复位时所确定的输出电压低的阈值电压。因此,可以在两个方向上检测到变化:光电转换单元201的输出信号的增加和减少。比较器241和242对来自差动装置230的输出电压进行二值化和量化。

[0194]

由量化器240量化的信号被输入到传送电路250。响应于具有值“1”的信号的输入,传送电路250可以将作为检测信号的入射光量的变化传送到信号处理电路70,该变化超过预定阈值。当由传送电路250传送检测信号时,信号处理电路70保持信号的传送作为地址事件,使行驱动单元50将行驱动信号输出至像素100,并且重置差动装置230。因此,在发生地址事件的像素100中,重新开始根据入射光的电压信号的变化的积分。

[0195]

[成像装置的配置]

[0196]

图21是示出根据本公开的技术可应用于的dvs的成像装置的配置实例的示图。图

21是示出构成dvs的成像装置1的配置实例的框图。图21中的成像装置1包括光接收元件2、控制单元3、透镜5和记录单元6。

[0197]

透镜5是用于在光接收元件2上形成物体的图像的透镜。在图15中示出的光接收元件2可以用作图21中的光接收元件2。

[0198]

控制单元3控制光接收元件2以捕获图像数据的图像。记录单元6记录来自光接收元件2的图像数据。

[0199]

光接收元件2可以通过获得其中检测到地址事件的像素100来检测具有改变的亮度的区域。图像数据仅在该区域中更新时产生,使得能够以高速成像。成像装置1是在权利要求中描述的电子设备的实例。

[0200]

根据第二实施例的光接收元件2可以与根据第三实施例的光接收元件2组合。具体地,图10中的焊盘开口180的配置可应用于图13中的像素100。

[0201]

最后,上述实施例的描述仅是本公开的实例,并且本公开不限于上述实施例。因此,不言而喻,在不背离本公开的技术精神的范围内,可根据设计等做出除了上述实施例之外的各种变化。

[0202]

此外,本说明书中描述的效果仅是示例性的并且不受限制。也可以获得其他效果。

[0203]

另外,上述实施例中的附图是示意性的,各部分的尺寸比等不一定与实际一致。另外,附图当然包括彼此的尺寸关系、比率不同的部分。

[0204]

本技术还可具有以下配置。

[0205]

(1)一种光接收元件,包括:布线区域,设置为紧邻半导体基板的正面,所述布线区域包括用于传输信号的布线层和用于使所述布线层绝缘的绝缘层,所述布线层连接至光电转换单元,所述光电转换单元设置在所述半导体基板中并且对入射光执行光电转换;

[0206]

电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;

[0207]

第一凹部,其形成在所述半导体基板的背面,所述背面与所述半导体基板的所述正面相反,所述第一凹部的所述底部在所述半导体基板的所述正面附近且在所述电极焊盘附近;以及

[0208]

第二凹部,所述第二凹部形成在所述第一凹部的所述正面上,并且所述第二凹部具有形成在所述电极焊盘的表面上的底部。

[0209]

(2)根据(1)所述的光接收元件,其中所述第二凹部配置为与所述第一凹部不同的开口尺寸。

[0210]

(3)根据(2)所述的光接收元件,其中在所述半导体基板的背面,所述第二凹部在平面图中具有与所述第一凹部不同的开口面积。

[0211]

(4)根据(2)所述的光接收元件,其中在所述半导体基板的所述正面,所述第二凹部在平面图中具有与所述第一凹部不同的开口面积。

[0212]

(5)根据(2)所述的光接收元件,其中所述第二凹部具有彼此不同的开口面积和底部面积。

[0213]

(6)根据(5)所述的光接收元件,其中所述第二凹部在所述半导体基板的背面的形状比在所述第二凹部的底面的形状大。

[0214]

(7)根据(6)所述的光接收元件,其中所述第二凹部的截面呈锥形。

[0215]

(8)根据(7)所述的光接收元件,其中所述第二凹部具有截面具有不同倾斜角的多个锥形形状。

[0216]

(9)根据(1)至(8)中任一项所述的光接收元件,其中所述第一凹部具有彼此不同的开口面积和底部面积。

[0217]

(10)根据(9)所述的光接收元件,其中所述第一凹部在所述半导体基板的背面的形状比所述第一凹部的底面的形状大。

[0218]

(11)根据(10)所述的光接收元件,其中所述第一凹部的截面呈锥形。

[0219]

(12)根据(1)至(11)中任一项所述的光接收元件,其中所述第一凹部被配置为竖直壁面。

[0220]

(13)根据(1)至(11)中任一项所述的光接收元件,其中所述第一凹部被配置为弯曲侧面。

[0221]

(14)根据(1)至(13)中任一项所述的光接收元件,其中所述第一凹部的截面具有线性形状的底部。

[0222]

(15)根据(1)至(13)中任一项所述的光接收元件,其中所述第一凹部被配置为具有弯曲底部。

[0223]

(16)根据(1)至(15)中任一项所述的光接收元件,其中在蚀刻时在所述第一凹部堆积反应生成物。

[0224]

(17)根据(1)至(16)中任一项所述的光接收元件,其中所述光电转换单元包括光电二极管。

[0225]

(18)根据(16)所述的光接收元件,其中所述光电转换单元包括光电二极管,所述光电二极管将由入射光的光电转换产生的电荷乘以高反向偏压。

[0226]

(19)根据(18)所述的光接收元件,其中所述光电转换单元允许在包括p型半导体区域和n型半导体区域的pn结处对所生成的电荷进行倍增。

[0227]

(20)根据(19)所述的光接收元件,其中所述光电转换单元具有包括所述n型半导体区域的阴极区域。

[0228]

(21)根据(20)所述的光接收元件,其中所述光电转换单元具有设置在所述半导体基板的正面上的所述阴极区域。

[0229]

(22)根据(19)所述的光接收元件,其中所述光电转换单元具有设置在所述半导体基板的正面上的阳极区域。

[0230]

(23)一种光接收元件,包括:布线区域,设置为紧邻半导体基板的正面,所述布线区域包括用于传输信号的布线层和用于使所述布线层绝缘的绝缘层,所述布线层连接至光电转换单元,所述光电转换单元设置在所述半导体基板中并且对入射光执行光电转换;

[0231]

电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;

[0232]

第一凹部,其形成在上述半导体基板的背面,且底部不到达上述电极焊盘的程度;以及

[0233]

第二凹部,所述第二凹部被配置为具有从所述第一凹部的底部到达所述电极焊盘的底部。

[0234]

(24)一种电子设备,包括:布线区域,布置为紧邻半导体基板的正面,所述布线区

域包括用于传输信号的布线层和用于使所述布线层绝缘的绝缘层,所述布线层连接至光电转换单元,所述光电转换单元设置在所述半导体基板中并且对入射光执行光电转换;

[0235]

电极焊盘,所述电极焊盘设置在所述布线区域中并且连接至所述布线层以电连接至所述外部;

[0236]

第一凹部,其形成在所述半导体基板的背面,所述背面与所述半导体基板的所述正面相反,所述第一凹部的所述底部在所述半导体基板的所述正面附近且在所述电极焊盘附近;

[0237]

第二凹部,其形成在所述第一凹部的正面,并且形成在所述电极焊盘的表面;以及

[0238]

处理电路,处理基于所述光电转换产生的信号。

[0239]

(25)根据(24)所述的电子设备,其中所述光电转换单元对从光源发射、经对象反射并进入所述光电转换单元的所述入射光执行光电转换,以及

[0240]

所述处理电路通过测量从来自所述光源的光发射到所述信号的生成的时间来执行测量到所述对象的距离的处理。

[0241]

(26)根据(24)所述的电子设备,其中所述处理电路执行检测所述信号的变化的处理。

[0242]

(27)根据(26)所述的电子设备,其中所述处理电路通过与预定阈值相比较来检测所述变化。

[0243]

(28)根据(24)所述的电子设备,其中所述处理电路设置在接合到所述半导体基板的另一半导体基板上。

[0244]

[参考标号列表]

[0245]

1 成像装置

[0246]

2 光接收元件

[0247]

10 像素阵列单元

[0248]

30 接收光信号处理单元

[0249]

70 信号处理电路

[0250]

100 像素

[0251]

101,102 光电转换单元

[0252]

110,130 半导体基板

[0253]

120,140 布线区域

[0254]

121,141 绝缘层

[0255]

122,123,124,142 布线层

[0256]

126,146 通路插塞

[0257]

127,147 焊盘

[0258]

128,148 电极垫

[0259]

180 垫开口

[0260]

181 第一凹部

[0261]

182,183,184 第二凹部

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1