具有改进的短路能力的基于功率碳化硅的半导体装置和制造此类装置的方法与流程

本发明涉及半导体装置,并且更具体地涉及功率半导体装置。

背景技术:

1、金属氧化物半导体场效应晶体管(“mosfet”)是可以用作开关装置的众所周知类型的晶体管。mosfet包括由沟道区域隔开的源极区域和漏极区域,以及通过诸如氧化硅层之类的薄栅极绝缘层与沟道区域隔开的栅极电极。mosfet可以通过向栅极电极施加栅极偏置电压来开启或关闭。当通过施加大于或等于用于装置的“阈值”电压的栅极偏置电压而开启mosfet时,电流通过mosfet的源极区域和漏极区域之间的沟道区域传导。当偏置电压从栅极电极移除(或降低至低于阈值电压水平)时,电流停止通过沟道区域传导。举例来说,n型mosfet具有n型源极和漏极区域以及p型沟道。n型mosfet可以被设计为在足以在p型沟道区域中创建导电n型反型层的栅极偏置电压被施加到栅极电极时开启,该导电n型反型层电连接n型源极和漏极区域,从而允许其间的多数载流子传导。mosfet也可以被设计为“常开”装置,通过向栅极电极施加栅极偏置电压而被关闭。

2、因为mosfet的栅极电极通过栅极绝缘层与沟道区域绝缘,因此要求最小的栅极电流来将mosfet维持在其导通状态或将mosfet在其导通状态和关断状态之间切换。栅极电流在开关期间保持小,因为栅极电极与沟道区域形成电容器。因此,在开关期间仅要求最小的充电和放电电流,从而允许不太复杂的栅极驱动电路系统。

3、对可以在其“导通”状态下通过大电流(例如,数百安培)并在其反向阻塞状态下阻塞大电压(例如,数千伏特)的高功率mosfet和其它栅极电极控制的半导体装置的需求在不断增加。为了支持高电流密度并阻塞此类高电压,功率mosfet通常具有垂直结构,其中源极和漏极位于厚半导体层结构的相对侧。在非常高功率的应用中,功率mosfet通常以宽带隙半导体材料系统形成。在本文中,术语“宽带隙半导体”涵盖具有至少1.4ev的带隙的任何半导体,诸如例如碳化硅(sic)。碳化硅具有多个有利的特点,包括例如高电场击穿强度、高热导率、高电子迁移率、高熔点和高饱和电子漂移速度。相对于使用其它半导体材料(诸如例如硅)形成的装置,使用碳化硅形成的电子装置可以具有在更高温度、在高功率密度、在更高速度、在更高功率电平和/或在更高辐射密度下操作的能力。

技术实现思路

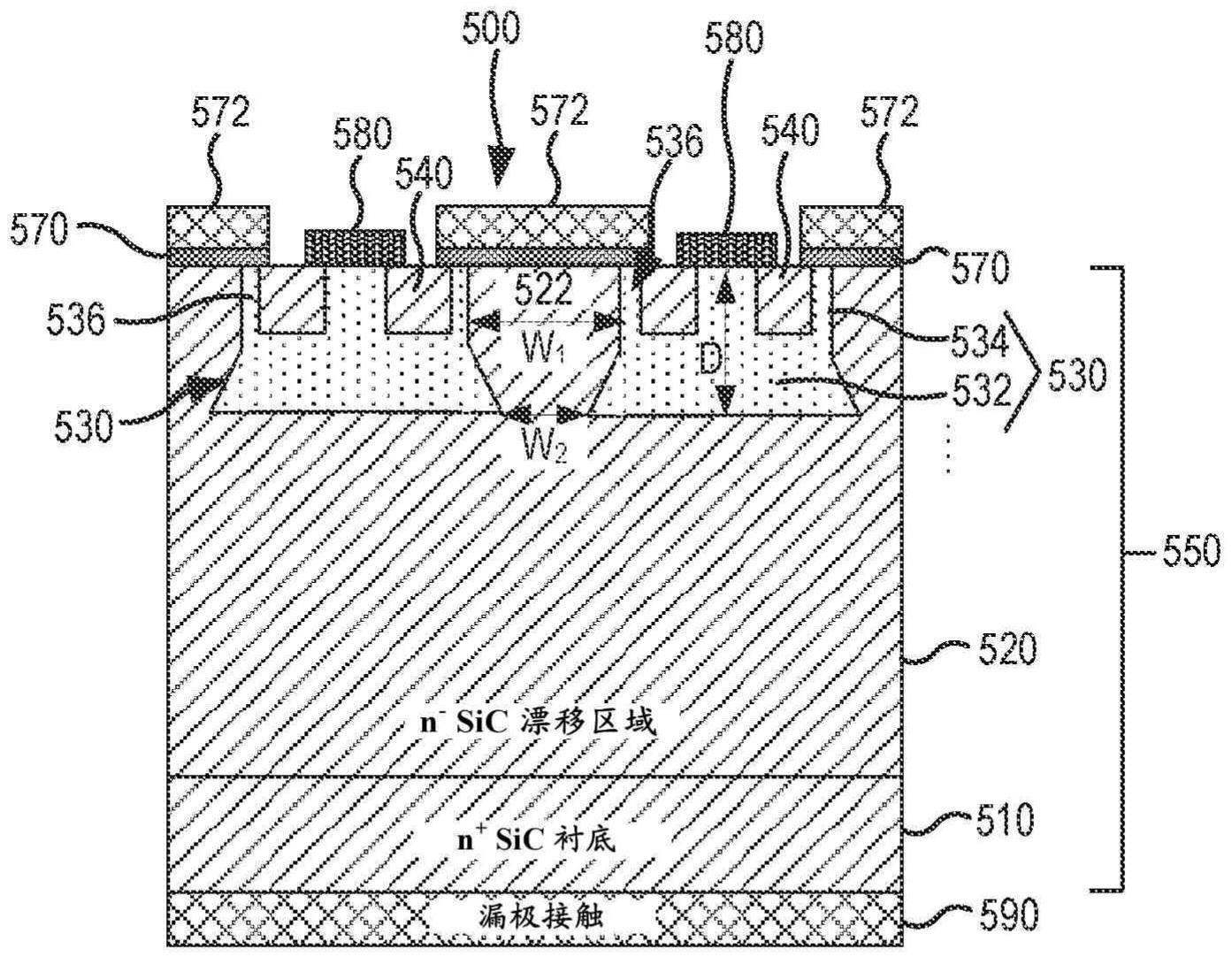

1、根据本发明的一些实施例,提供了具有半导体层结构的功率半导体装置,该半导体层结构包括具有第一导电类型的碳化硅漂移区域,位于碳化硅漂移区域的上部部分中的第一阱,第一阱掺杂有具有与第一导电类型不同的第二导电类型的掺杂剂,位于碳化硅漂移区域的上部部分中的第二阱,第二阱与第一阱间隔开,第二阱掺杂有具有第二导电类型的掺杂剂,以及在碳化硅漂移区域中第一阱和第二阱之间的jfet区域。jfet区域的掺杂浓度超过碳化硅漂移区域的掺杂浓度,并且jfet区域的上半部分的最大宽度比jfet区域的下半部分的最小宽度大至少30%。

2、在一些实施例中,第一阱可以包括第一主阱以及位于第一主阱和jfet区域之间的第一侧阱,并且第二阱可以包括第二主阱以及位于第二主阱之间的第二侧阱。第一侧阱可以包括第一沟道区域,并且第二侧阱可以包括第二沟道区域。

3、在一些实施例中,第一侧阱距半导体层结构的上表面的深度为至少1.0微米。

4、在一些实施例中,功率半导体装置还可以包括在碳化硅漂移区域的下表面上的第一源极/漏极接触,在第一主阱的上部部分中具有第一导电类型并延伸到第一阱的上表面的源极/漏极区域,源极/漏极区域的上表面上的第二源极/漏极接触,jfet区域上和第一阱上的栅极绝缘层,以及栅极绝缘层上的栅极电极。

5、在一些实施例中,jfet区域距半导体层结构的上表面的深度可以等于或超过第一侧阱距半导体层结构的上表面的深度。

6、在一些实施例中,第一侧阱的峰掺杂浓度可以超过5x1017/cm3并且出现在半导体层结构的上表面下方0.8和1.2微米之间的深度处。

7、在一些实施例中,第一侧阱距半导体层结构的上表面的深度可以小于1.6微米。

8、在一些实施例中,jfet区域距半导体层结构的上表面的深度可以在第一侧阱距半导体层结构的上表面的深度的1.0和1.2倍之间。

9、在一些实施例中,第一侧阱的上部0.2微米的峰掺杂浓度可以比第一侧阱的峰掺杂浓度小至少一个数量级。

10、在一些实施例中,jfet区域的上部部分的最大宽度可以比jfet区域的下部部分的最小宽度大至少50%。

11、在一些实施例中,第一侧阱的峰掺杂浓度可以出现在距半导体层结构的上表面的第一深度处,并且jfet区域的在距半导体层结构的上表面的第一深度处的掺杂浓度可以比第一侧阱的峰掺杂浓度低至少一个数量级。

12、在一些实施例中,第一侧阱的深度可以在距半导体层结构的上表面1.0和1.5微米之间,jfet区域距半导体层结构的上表面的深度可以在1.0和1.7微米之间,并且jfet区域的深度可以至少与第一侧阱的深度一样深。

13、在一些实施例中,第一侧阱和第二侧阱之间的距离可以小于1.5微米。

14、在一些实施例中,jfet区域可以包括注入有具有第一导电类型的掺杂剂的注入区域。

15、在一些实施例中,jfet区域的上半部分的最大宽度可以比jfet区域的下半部分的最小宽度大40%和80%之间。

16、在一些实施例中,jfet区域的下半部分的宽度可以小于jfet区域的深度的50%。

17、在一些实施例中,jfet区域可以在第一阱下方延伸。

18、根据本发明的进一步的实施例,提供了具有半导体层结构的功率半导体装置,该半导体层结构包括具有第一导电类型的碳化硅漂移区域、位于碳化硅漂移区域的上部部分中的第一阱,第一阱掺杂有具有与第一导电类型不同的第二导电类型的掺杂剂,位于碳化硅漂移区域的上部部分中的第二阱,第二阱与第一阱间隔开,第二阱掺杂有具有第二导电类型的掺杂剂,以及在碳化硅漂移区域中第一阱和第二阱之间的jfet区域。jfet区域距半导体层结构的上表面的深度超过第一阱距半导体层结构的上表面的深度,并且jfet区域的上半部分的最大宽度大于最小宽度jfet区域的下半部分的最小宽度。

19、在一些实施例中,jfet区域的掺杂浓度可以超过碳化硅漂移区域的掺杂浓度,并且第一阱距半导体层结构的上表面的深度可以是至少1.0微米,并且第一阱的峰掺杂浓度超过第一阱的在距半导体层结构的上表面0.2微米的深度处的掺杂浓度达至少一个数量级。

20、在一些实施例中,第一阱的峰掺杂浓度可以超过5x1017/cm3并且出现在半导体层结构的上表面下方0.8和1.2微米之间的深度处。

21、在一些实施例中,第一阱距半导体层结构的上表面的深度可以在1.0和1.6微米之间。

22、在一些实施例中,jfet区域距半导体层结构的上表面的深度可以小于第一阱距半导体层结构的上表面的深度的1.2倍。

23、在一些实施例中,jfet区域的上半部分的最大宽度可以比jfet区域的下半部分的最小宽度大至少50%。

24、在一些实施例中,第一阱的峰掺杂浓度可以出现在距半导体层结构的上表面的第一深度处,并且jfet区域的在距半导体层结构的上表面的第一深度处的掺杂浓度可以比第一阱的峰掺杂浓度低至少一个数量级。

25、在一些实施例中,jfet区域的上半部分的最大宽度可以比jfet区域的下半部分的最小宽度大40%和80%之间。

26、在一些实施例中,jfet区域可以在第一阱下方延伸。

27、根据本发明的还有另外的实施例,提供了具有半导体层结构的功率半导体装置,该半导体层结构包括具有第一导电类型的碳化硅漂移区域,位于碳化硅漂移区域的上部部分中的第一阱,第一阱掺杂有具有与第一导电类型不同的第二导电类型的掺杂剂,位于碳化硅漂移区域的上部部分中的第二阱,第二阱与第一阱间隔开,第二阱掺杂有具有第二导电类型的掺杂剂,以及在碳化硅漂移区域中第一阱和第二阱之间的jfet区域。jfet区域的掺杂浓度超过碳化硅漂移区域的掺杂浓度。第一阱的峰掺杂浓度出现在距半导体层结构的上表面的第一深度处,并且jfet区域在第一深度处的掺杂浓度比第一阱的峰掺杂浓度低至少一个数量级。jfet区域距半导体层结构的上表面的深度超过第一阱距半导体层结构的上表面的深度。

28、在一些实施例中,第一的峰掺杂浓度可以超过5x1017/cm3并且可以出现在半导体层结构的上表面下方0.7和1.2微米之间的深度处。

29、在一些实施例中,jfet区域距半导体层结构的上表面的深度可以小于第一阱距半导体层结构的上表面的深度的1.2倍。

30、在一些实施例中,第一阱的上部0.2微米的峰掺杂浓度可以比第一阱的峰掺杂浓度小至少一个数量级。

31、在一些实施例中,jfet区域的上半部分的最大宽度可以比jfet区域的下半部分的最小宽度大至少50%。

32、在一些实施例中,jfet区域可以包括注入有第一导电类型掺杂剂的注入区域。

33、在一些实施例中,jfet区域可以在第一阱下方延伸。

34、根据本发明的附加实施例,提供了形成功率半导体装置的方法。根据这些方法,提供具有第一导电类型的碳化硅漂移区域。第二导电类型掺杂剂被注入到碳化硅漂移区域的上部部分中以形成第一阱和第二阱。经由离子注入将第一导电类型掺杂剂注入到碳化硅漂移区域的在第一阱和第二阱之间上部部分中以在第一阱和第二阱之间形成jfet区域,其中碳化硅漂移区域以及第一阱和第二阱是半导体层结构的部分。jfet区域的上半部分的最小宽度比jfet区域的下半部分的最小宽度大至少30%。

35、在一些实施例中,第一阱可以包括第一主阱以及位于第一主阱和jfet区域之间的第一侧阱,第一侧阱包括第一沟道区域,并且第二阱可以包括第二主阱以及位于第二主阱和jfet区域之间的第二侧阱,第二侧阱包括第二沟道区域,并且第一侧阱距半导体层结构的上表面的深度可以是至少1.0微米。

36、在一些实施例中,第一侧阱的峰掺杂浓度可以超过5x1017/cm3并且可以出现在半导体层结构的上表面下方0.8和1.2微米之间的深度处。

37、在一些实施例中,jfet区域距半导体层结构的上表面的深度可以在第一侧阱距半导体层结构的上表面的深度的1.0和1.2倍之间。

38、在一些实施例中,第一侧阱的上部0.2微米的峰掺杂浓度可以比第一侧阱的峰掺杂浓度小至少一个数量级。

39、在一些实施例中,可以在形成第一阱和第二阱之前形成jfet区域。

40、在一些实施例中,jfet区域可以在第一阱和第二阱下方延伸。

- 还没有人留言评论。精彩留言会获得点赞!