包含块之间的不同介电结构的存储器装置的制作方法

1.本文中所描述的实施例涉及包含存储器单元的块之间的介电结构分离的存储器装 置。

背景技术:

2.存储器装置广泛地用于计算机和许多其它电子项目中。存储器装置通常具有用于存 储信息(例如,数据)的众多存储器单元和将信息(呈电信号形式)携载进出存储器单元的数 据线。在存储器装置的制造期间,存储器单元常常划分成物理块。在形成存储器装置的 一些常规工艺中,存储器装置中的块易受块弯曲误差影响,其中块的结构可弯曲。中等 的块弯曲误差可导致这种导电元件之间的不良电连接。严重的块弯曲误差可引起存储器 装置中的一些电连接中的故障。

技术实现要素:

附图说明

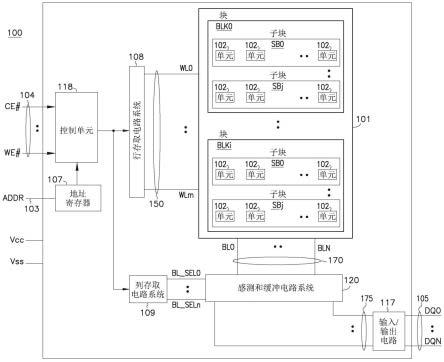

3.图1展示根据本文中所描述的一些实施例的呈存储器装置形式的设备的框图。

4.图2展示根据本文中所描述的一些实施例的包含具有块(存储器单元的块)和块中的 每一个中的子块的存储器阵列的存储器装置的一部分的大体示意图。

5.图3展示根据本文中所描述的一些实施例的包含图2的存储器装置的块中的两个邻 近块的详细示意图。

6.图4展示根据本文中所描述的一些实施例的包含存储器阵列、楼梯区和存储器装置 的块之间的介电结构的图3的存储器装置的一部分的结构的俯视图。

7.图5展示根据本文中所描述的一些实施例的包含延伸穿过且分离块的控制栅极的介 电结构的图4的存储器装置的一部分的结构的侧视图(例如,横截面)。

8.图6展示根据本文中所描述的一些实施例的包含邻近块、块中的柱和介电结构的细 节的图4和图5的存储器装置的一部分的结构的俯视图。

9.图7展示根据本文中所描述的一些实施例的包含存储器装置的块中的一个的楼梯结 构的一部分的图6的存储器装置的一部分的侧视图。

10.图8展示根据本文中所描述的一些实施例的包含块的控制栅极和介电材料的边缘和 柱的更多细节的图4的存储器装置的一部分的结构的侧视图(例如,横截面)。

11.图9展示根据本文中所描述的一些实施例的图8的存储器装置的控制栅极和柱的一 部分的横截面(例如,俯视图)。

12.图10a和图10b至图22a和图22b展示根据本文中所描述的一些实施例的在形成 存储器装置的工艺期间元件的不同视图。

包含例如感测放大器和页缓冲电路(例如,数据锁存器)的组件。感测和缓冲电路系统120 可响应于来自列存取电路系统109的信号bl_sel0到bl_seln。感测和缓冲电路系统 120可配置成确定(例如,通过感测)从存储器块blk0到blki的存储器单元102(例如, 在读取操作期间)读取的信息的值且将信息的值提供到线(例如,全局数据线)175。感测 和缓冲电路系统120还可配置成使用线175上的信号以基于(例如,在写入操作期间)线 175上的信号的值(例如,电压值)确定(例如,在写入操作期间)待存储(例如,编程)在块 blk0到blki的存储器单元102中的信息的值。

20.存储器装置100可包含输入/输出(i/o)电路系统117以在块blk0到blki的存储器 单元102与线(例如,i/o线)105之间交换信息。线105上的信号dq0到dqn可表示从 块blk0到blki的存储器单元102读取或存储在其中的信息。线105可包含存储器装 置100内的节点或其中可驻留存储器装置100的封装上的引脚(或焊球)。在存储器装置 100外部的其它装置(例如,存储器控制器或处理器)可通过线103、104和105与存储器 装置100通信。

21.存储器装置100可接收供电电压,包含供电电压vcc和vss。供电电压vss可在接 地电位(例如,具有大约零伏特的值)下操作。供电电压vcc可包含从例如电池或交流电 到直流电(ac-dc)转换器电路系统的外部电源供应到存储器装置100的外部电压。

22.存储器单元102中的每一个可编程以存储表示至多一个位(例如,单个位)的值或例 如两个、三个、四个或另一数目个位的多个位的值的信息。举例来说,存储器单元102 中的每一个可编程以存储表示单个位的二进制值“0”或“1”的信息。每单元单个位有 时称为单层级单元。在另一实例中,存储器单元102中的每一个可编程以存储表示多个 位的值的信息,所述值例如两个位的四个可能值“00”、“01”、“10”和“11”中的一个、 三个位的八个可能值“000”、“001”、“010”、“011”、“100”、“101”、“110”和“111

”ꢀ

中的一个,或另一数目个多个位(例如,每一存储器单元中的多于三个位)的其它值中的 一个。具有存储多个位的能力的单元有时称为多层级单元(或多状态单元)。

23.存储器装置100可包含非易失性存储器装置,且存储器单元102可包含非易失性存 储器单元,使得存储器单元102可在电源(例如,电压vcc、vss或两者)与存储器装置 100断开连接时保持存储在其上的信息。举例来说,存储器装置100可为快闪存储器装 置,例如nand快闪(例如,3d nand)或nor快闪存储器装置,或另一种类的存储器 装置,例如可变电阻存储器装置(例如,相变存储器装置或电阻性随机存取存储器(ram) 装置)。

24.所属领域的一般技术人员可认识到,存储器装置100可包含其它组件,其中的若干 组件未展示于图1中以便不混淆本文中所描述的实例实施例。存储器装置100的至少一 部分可包含结构且进行与下文参考图2至图22b所描述的存储器装置中的任一个的结构 和操作类似或相同的操作。

25.图2展示根据本文中所描述的一些实施例的包含具有块(存储器单元的块)blk0到 blki和所述块中的每一个中的子块sb0到sbj的存储器阵列201的存储器装置200的 一部分的大体示意图。存储器装置200可对应于图1的存储器装置100。举例来说,存 储器阵列201可形成图1的存储器阵列101的部分。

26.在存储器装置200的物理结构中,块blk0到blki可布置(例如,形成)为一个块 紧邻另一块,使得每一块邻近另一块。邻近块为相邻块且紧邻彼此定位。

27.块blk0到blki中的每一个中的子块sb0到sbj为每一块的较小部分。块blk0 到

blki可包含相同数目个子块。举例来说,块blk0到blki中的每一个可包含四个 子块(例如,子块sb0、sb1、sb2和sb3)。

28.如图2中所示,每一子块(例如,sb0或sbj)具有其自身的可与相应选择电路相关 联(例如,耦合到相应选择电路)的存储器单元串。存储器装置200的块(例如,块blk0 到blki)的子块可具有相同数目个存储器单元串和相关联选择电路。

29.举例来说,块blk0的子块sb0具有存储器单元串231a、232a和233a和分别相关 联的选择电路(例如,漏极选择电路)241a、242a和243a,和分别选择电路(例如,源极 选择电路)241'a、242'a和243'a。在另一实例中,块blk0的子块sbj具有存储器单元 串234a、235a和236a和分别相关联的选择电路(例如,漏极选择电路)244a、245a和246a, 和分别选择电路(例如,源极选择电路)244'a、245'a和246'a。

30.类似地,块blk1的子块sb0具有存储器单元串231b、232b和233b和分别相关联 的选择电路(例如,漏极选择电路)241b、242b和243b,和分别选择电路(例如,源极选 择电路)241'b、242'b和243'b。块blk1的子块sbj具有存储器单元串234b、235b和 236b和分别相关联的选择电路(例如,漏极选择电路)244b、245b和246b,和分别选择 电路(例如,源极选择电路)244'b、245'b和246'b。

31.图2展示子块中(例如,子块sb0中)的三个存储器单元串和其相关联电路的实例。 块blk0到blki的每一子块中的存储器单元串和其相关联选择电路的数目可变化。存 储器装置200的存储器单元串中的每一个可包含串联连接的存储器单元(展示于图3和图 4中的细节中)和柱(例如,图5中的柱550),其中串联连接的存储器单元可沿着柱的相 应部分定位(例如,竖直地定位)。

32.如图2中所示,存储器装置200可包含分别携载信号bl0到bln的数据线2700到 270n。数据线2700到270n中的每一个可构造为可包含导电材料(例如,导电掺杂的多晶 硅(掺杂多晶硅)、金属或其它导电材料)的导电线。

33.块blk0到blki的存储器单元串可共享数据线2700到270n以携载从存储器装置 200的所选存储器单元(例如,块blk0或blk1中的所选存储器单元)的存储器单元读取 或待存储在其中的信息(呈信号形式)。举例来说,(块blk0的)存储器单元串231a、234a、 (块blk1的)231b和234b可共享数据线2700。(块blk0的)存储器单元串232a、235a、 (块blk1的)232b和235b可共享数据线2701。(块blk0的)存储器单元串233a、236a、 (块blk1的)233b和236b可共享数据线2702。

34.存储器装置200可包含可携载信号(例如,源极线信号)src的源极(例如,源极线、 源极板或源极区)290。源极290可构造为存储器装置200的导电线或导电板(例如,导 电区)。源极290可为块blk0到blki的共同源极(例如,共同源极板或共同源极区)。 替代地,块blk0到blki中的每一个可具有类似于源极290的其自身的源极。源极290 可耦合到存储器装置200的接地连接。

35.块blk0到blki中的每一个可具有其自身的一组控制栅极以用于控制对相应块的 子块的存储器单元串的存储器单元的存取。如图2中所示,存储器装置200可包含块 blk0中的控制栅极(例如,字线)2200、2210、2220和2230,所述控制栅极可为存储器 装置200的导电路径(例如,存取线)2560的部分。存储器装置200可包含块blk1中的 控制栅极(例如,字线)2201、2211、2221和2231,所述控制栅极可为存储器装置200的 其它导电路径(例如,存取线)

2561的部分。导电路径2560和2561可对应于图1的存储 器装置100的存取线150的部分。

36.如图2中所示,控制栅极2200、2210、2220和2230可彼此电分离。控制栅极2201、 2211、2221和2231可彼此电分离。控制栅极2200、2210、2220和2230可与控制栅极2201、 2211、2221和2231电分离。因此,可单独地存取(例如,一次一个地存取)块blk0到blk1。 举例来说,可使用控制栅极2200、2210、2220和2230在一个时间(例如,时间t1)存取块 blk0,且可在另一时间(例如,时间t2)使用控制栅极2201、2211、2221和2231在另一 时间存取块blk1。

37.存储器装置200可具有存储器装置200的块(例如,块blk0到blki)当中的相同数 目个控制栅极。在图2的实例中,存储器装置200具有块blk0到blki中的每一个中 的四个控制栅极。图2展示包含块blk0到blki中的每一个中的四个控制栅极的存储 器装置200作为实例。存储器装置200的块(例如,块blk0到blki)的控制栅极的数目 可不同于四个。举例来说,块blk0到blki中的每一个可包含多达数百(或更多)个控 制栅极。

38.控制栅极2200、2210、2220和2230中的每一个可为位于存储器装置200的层级中的 导电材料(例如,导电材料层)的结构(例如,层级)的部分。控制栅极2200、2210、2220和2230可携载对应信号(例如,字线信号)wl00、wl10、wl20和wl30。存储器装置200 可使用信号wl00、wl10、wl20和wl30在操作(例如,读取、写入或擦除操作)期间选 择性地控制对块blk0的存储器单元的存取。举例来说,在读取操作期间,存储器装置 200可使用信号wl00、wl10、wl20和wl30控制对块blk0的所选存储器单元的存取, 以从块blk0的存储器单元读取(例如,感测)信息(例如,先前存储的信息)。在另一实例 中,在写入操作期间,存储器装置200可使用信号wl00、wl10、wl20和wl30控制对 块blk0的所选存储器单元的存取,以将信息存储在块blk0的所选存储器单元中。

39.控制栅极2201、2211、2221和2231中的每一个可为位于存储器装置200的层级中的 导电材料(例如,导电材料层)的结构(例如,层级)的部分。控制栅极2201、2211、2221和2231可携载对应信号(例如,字线信号)wl00、wl10、wl20和wl30。存储器装置200 可使用信号wl01、wl11、wl21和wl31在操作(例如,读取、写入或擦除操作)期间选 择性地控制对块blk0的存储器单元的存取。举例来说,在读取操作期间,存储器装置 200可使用信号wl01、wl11、wl21和wl31控制对块blk1的所选存储器单元的存取, 以从块blk1的存储器单元读取(例如,感测)信息(例如,先前存储的信息)。在另一实例 中,在写入操作期间,存储器装置200可使用信号wl01、wl11、wl21和wl31控制对 块blk1的所选存储器单元的存取,以将信息存储在块blk1的所选存储器单元中。

40.如图2中所示,在块blk0的子块sb0中,存储器装置200可包含可由选择电路 241a、242a和243a共享的选择线(例如,漏极选择线)2800。在块blk0的子块sbj中, 存储器装置200可包含可由选择电路244a、245a和246a共享的选择线(例如,漏极选择 线)280j。块blk0可包含可由选择电路241'a、242'a、243'a、244'a、245'a和246'a共享 的选择线(例如,源极选择线)284。

41.在块blk1的子块sb0中,存储器装置200可包含选择线(例如,漏极选择线)2800, 所述选择线2800与块blk1的选择线2800电分离。块blk1的选择线2800可由选择电 路241b、242b和243b共享。在块blk1的子块sbj中,存储器装置200可包含可由选 择电路244b、245b和246b共享的选择线(例如,漏极选择线)280j。块blk1的选择线 2800和280j与块blk0的选择线2800和280j电分离。块blk1可包含可由选择电路241'b、 242'b、243'b、244'b、245'b和

246'b共享的选择线(例如,源极选择线)284。

42.图2展示其中存储器装置200包含由子块(例如,块blk0的子块sb0)中的选择电 路(例如,选择电路241a、242a或243a)共享的一个漏极选择线(例如,选择线2800)的实 例。然而,存储器装置200可包含由子块中的选择电路共享的多个漏极选择线。图2展 示其中存储器装置200包含由子块(例如,块blk0的子块sb0)中的源极选择电路(例如, 选择电路241'a、242'a或243'a)共享的一个源极选择线(例如,选择线284)的实例。然而, 存储器装置200可包含由子块中的源极选择电路共享的多个源极选择线。

43.在图2中,存储器装置200的漏极选择电路中的每一个可包含相应数据线与相应存 储器单元串之间的漏极选择栅极(例如,晶体管,图3中所示)。漏极选择栅极(例如,晶 体管)可基于提供到信号的电压由相应漏极选择线上的信号控制(例如,导通或截止)。

44.在图2中,存储器装置200的源极选择电路中的每一个可包含耦合在源极290与相 应存储器单元串之间的源极选择栅极(例如,晶体管,图3中所示)。源极选择栅极(例如, 晶体管)可基于提供到信号的电压由相应源极选择线上的信号控制(例如,导通或截止)。

45.在图2中,存储器装置200的存储器单元串中的每一个具有布置成串(例如,相互之 间串联耦合)的存储器单元(图3中所示)以存储信息。在存储器装置200的操作(例如,读 取、写入或擦除操作)期间,存储器单元串可个别地选择以存取所选存储器单元串中的存 储器单元,以便将信息存储在所选存储器单元串中或从所选存储器单元串读取信息。与 所选存储器单元串相关联的一个或两个选择电路(漏极选择电路和源极选择电路)可取决 于存储器装置200对所选存储器单元串进行哪一操作而激活(例如,通过导通选择电路 (或所选电路)中的选择栅极(例如,晶体管))。

46.在存储器装置200的操作期间激活存储器装置200的选择电路当中的特定选择电路 可包含将具有某些值的电压提供(例如,施加)到与所述特定选择电路相关联的选择线上 的信号。当激活存储器装置200的特定漏极选择电路时,其可将与所述特定选择电路相 关联的所选存储器单元串电连接(例如,从其形成电流路径)到相应数据线(例如,数据线 2700到270n中的一个)。当激活特定源极选择电路时,其可将与所述特定选择电路相关 联的所选存储器单元串电连接(例如,从其形成电流路径)到源极290。

47.图3展示根据本文中所描述的一些实施例的包含图2的存储器装置200的块blk0 和blk1的块的详细示意图。在存储器装置200的物理结构中,块blk0和blk1为邻 近块(例如,相邻块)。邻近块紧邻彼此而定位,使得邻近块之间不存在额外块(或不存在 多个额外块)。

48.在图3中,图3中的方向x、y和z可相对于存储器装置200的结构的物理方向(例 如,三维(3d)维度)。举例来说,z方向可为垂直于存储器装置200的衬底(例如,展示 于图5中的衬底599)的方向(例如,相对于所述衬底的竖直方向)。z方向垂直于x方向 和y方向(例如,z方向垂直于存储器装置200的x-y平面)。

49.为简单起见,在图3中仅标记图2的存储器装置200的存储器单元串中的一些和选 择电路中的一些。如图3中所示,每一选择线可携载相关联的单独选择信号。举例来说, 在块blk0的子块sb0中,选择线(例如,漏极选择线)2800可携载信号(例如,漏极选 择栅极信号)sgd00。在块blk0的子块sbj中,选择线(例如,漏极选择线)280j可携载 信号(例如,漏极选择栅极信号)sgd0j。块blk0的子块sb0和sbj可共享可携载信号(例 如,源极选择栅极信

号)sgs0的选择线284。

50.在块blk1的子块sb0中,选择线(例如,漏极选择线)280j可携载信号(例如,漏极 选择栅极信号)sgd0j。在块blk1的子块sbj中,选择线(例如,漏极选择线)280j可携 载信号(例如,漏极选择栅极信号)sgd0j。块blk1的子块sb0和sbj可共享可携载信 号(例如,源极选择栅极信号)sgs1的选择线284。

51.为简单起见,给予本文中所描述的存储器装置(例如,存储器装置200)中的类似或 相同元件相同标记。举例来说,如图3中所示,为简单起见,给予类似漏极选择线(和其 相关联信号)相同标记。然而,如图3中所示,存储器装置200的漏极选择线(来自相同 块或来自不同块)彼此电分离且携载不同信号(尽管给予信号相同标记)。

52.如图3中所示,存储器装置200可包含:存储器单元210、211、212和213;选择 栅极(例如,漏极选择栅极或晶体管)260;和选择栅极(例如,源极选择栅极)264,其可 相对于存储器装置200的结构(展示于图4中)以例如x、y和z方向(例如,维度)的三 维(3d)形式实体地布置。

53.在图3中,存储器装置200的存储器单元串中的每一个(例如,存储器单元串231a) 可包含串联连接的存储器单元,所述串联连接的存储器单元包含存储器单元210中的一 个、存储器单元211中的一个、存储器单元212中的一个和存储器单元213中的一个。 图3展示每一存储器单元串中的四个存储器单元210、211、212和213的实例。每一存 储器单元串中的存储器单元的数目可变化。举例来说,每一存储器串可包含多达数百(或 更多)个存储器单元。

54.如图3中所示,每一漏极选择电路(例如,选择电路241a)可包含选择栅极260中的 一个。每一源极选择电路(例如,选择电路241'a)可包含选择栅极264中的一个。

55.图3中的选择栅极260中的每一个可类似于晶体管而操作。举例来说,选择电路241a 的选择栅极260可类似于例如金属-氧化物半导体fet(mosfet)的场效应晶体管(fet) 而操作。这种mosfet的实例包含n通道mos(nmos)晶体管。

56.如图3中所示,在子块中的特定选择电路当中共享的选择线可由那些特定选择电路 的相应选择栅极共享(例如,可用于控制所述相应选择栅极)。举例来说,块blk0的子 块sb0的选择线2800可由块blk0的子块sb0的选择电路241a、242a和243a的选择 栅极260共享(例如,可用于控制所述选择栅极260)。在另一实例中,块blk0的子块 sb0的选择线284可由块blk0的子块sb0的选择电路241'a、242'a和243'a的选择栅 极264共享。

57.选择线(例如,块blk0的子块sb0的选择线2800)可携载信号(例如,信号sgd00), 但其并不类似于开关(例如,晶体管)而操作。选择栅极(例如,选择电路241a的选择栅 极260)可从相应选择线(例如,块blk0的子块sb0的选择线2800)接收信号(例如,信 号sgd00)且可类似于开关(例如,晶体管)而操作。

58.在存储器装置200的物理结构中,选择线(例如,块blk0的子块sb0的选择线2800) 可为位于存储器装置200的单个层级中的导电材料(例如,导电材料层(例如,片)或导电 材料区)的结构(例如,层级)。导电材料可包含金属、掺杂多晶硅或其它导电材料。

59.在存储器装置200的物理结构中,选择栅极(例如,块blk0的子块sb0的选择电 路241a的选择栅极260)可包含以下各者(可由以下各者形成):相应选择线(例如,块blk0 的子块sb0的选择线2800)的导电材料的一部分、通道材料(例如,多晶硅通道)的一部分, 和

导电材料的部分与通道材料的部分之间的介电材料(例如,类似于晶体管(例如,fet) 的栅极氧化物)的一部分。

60.图3展示其中存储器装置200包含每一漏极选择电路中的一个漏极选择栅极(例如, 选择栅极260)和耦合到存储器单元串的每一源极选择电路中的一个源极选择栅极(例如, 选择栅极264)的实例。然而,存储器装置200可包含每一漏极选择电路中的多个漏极选 择栅极(例如,串联连接的多个选择栅极260)、每一源极选择电路中的多个源极选择栅 极(例如,串联连接的多个选择栅极264),或耦合到存储器单元串的多个漏极选择栅极 和多个源极选择栅极两者。

61.如上文所描述,存储器装置200(图3)可包含块bl0到blj。图2展示块blk0和 blk1的详细示意图。下文描述存储器装置的一部分的结构。

62.图4展示根据本文中所描述的一些实施例的包含存储器阵列201的图2和图3的存 储器装置200的一部分的结构的俯视图,所述存储器阵列201包含块blk0、blk1、blk2 和blk3,和将一个块与另一块分离的介电结构(例如,介电分隔物)424和451。为简单 起见,可从图式的特定图省略存储器装置200(和本文中所描述的其它存储器装置)的一 些元件,以便不混淆正在特定图中描述的元件(或多个元件)的视图或描述。另外,本文 中所描述的图式中的存储器装置200(和其它存储器装置)的元件的尺寸(例如,物理结构) 未按比例调整。此外,上文参考图2和图3所描述的存储器装置200的相同元件的描述 也不重复。

63.如图4中所示,块blk0、blk1、blk2和blk3为位于紧邻彼此定位的四个邻近 块(例如,四个相邻块)。举例来说,块blk0和blk1为邻近块。块blk1和blk2为 邻近块。块blk2和blk3为邻近块。块blk0、blk1、blk2和blk3具有用于相应 块的相应存储器单元的单独控制栅极。

64.如图4中所示,块blk0的控制栅极(与信号wl00、wl10、wl20、wl30相关联) 在y方向上从存储器装置200的存储器阵列201到存储器装置的楼梯区454(详细展示 于图7中)具有长度。块blk0的控制栅极可在z方向上堆叠在彼此之上(展示于图5中 的侧视图中)。如图4中所示,块blk0的选择线(与信号sgs0相关联)可位于块blk0 的控制栅极下(相对于z方向)。

65.块blk0可包含存储器装置200的楼梯区454处的楼梯结构4200。楼梯结构4200可由块blk0的控制栅极(与信号wl00、wl10、wl20、wl30相关联)的部分(例如,末 端部分)形成。如下文参考图7(其展示楼梯结构4200的侧视图)详细描述,导电触点(例 如,导电触点(例如,字线触点)765)可形成于块blk0的相应控制栅极上的楼梯结构4200处,以允许通过楼梯结构4200处的导电触点将信号(例如,信号wl00、wl10、wl20、 wl30)提供到块blk0的相应控制栅极。块blk1、blk2和blk3分别具有其自身的楼 梯4201、4202和4203。

66.如图4中所示,块blk0可包含分别与信号sgd00、sgd10、sgd20和sgd30相关 联的子块(例如,四个子块)sb0、sb1、sb2和sb3和选择线(例如,四个漏极选择线)。 选择线可包含相应导电区(例如,导电材料),所述导电区彼此电分离且可位于相同层级 上(相对于z方向)和块blk0的控制栅极之上(相对于z方向)。如图4中所示,选择线 中的每一个(与信号sgd00、sgd10、sgd20和sgd30相关联)可在y方向上从存储器阵 列201到楼梯区454具有长度。

67.块blk1、blk2和blk3可具有类似于块blk0的结构。如图4中所示,块blk1 可包含与信号wl01、wl11、wl21和wl31相关联的控制栅极(也展示于图3中)、与信 号sgs1相关联的选

择线(例如,源极选择线)(也展示于图3中)、子块sb0、sb1、sb2 和sb3、选择线(例如,漏极选择线)sgd01、sgd11、sgd21和sgd31,和楼梯结构4201。 导电触点(例如,字线触点)可形成于楼梯结构4201处,以允许通过楼梯结构4201处的导 电触点将信号(例如,信号wl01、wl11、wl21、wl31)提供到块blk2的相应控制栅极。

68.块blk2可包含与信号wl02、wl12、wl22和wl32相关联的控制栅极、与信号 sgs2相关联的选择线(例如,源极选择线)、子块sb0、sb1、sb2和sb3、选择线(例如, 漏极选择线)sgd02、sgd12、sgd22和sgd32,和楼梯结构4202。导电触点(例如,字 线触点)可形成于楼梯结构4202处,以允许通过楼梯结构4202处的导电触点将信号(例如, 信号wl02、wl12、wl22、wl32)提供到块blk2的相应控制栅极。

69.块blk3可包含与信号wl03、wl13、wl23和wl33相关联的控制栅极、与信号 sgs3相关联的选择线(例如,源极选择线)、子块sb0、sb1、sb2和sb3、选择线(例如, 漏极选择线)sgd03、sgd13、sgd23和sgd33,和楼梯结构4203。导电触点(例如,字 线触点)可形成于楼梯结构4203处,以允许通过楼梯结构4203处的导电触点将信号(例如, 信号wl03、wl13、wl23、wl33)提供到块blk3的相应控制栅极。

70.在存储器装置200的物理结构中,每一块的选择线(例如,与块blk0中的信号 sgd00、sgd10、sgd20和sgd30相关联的四个选择线)可包含导电区(例如,四个相应 导电区或导线),所述导电区彼此电分离且可具有在平行于介电结构424和451的长度的 y方向上的相应长度。

71.图4展示其中存储器装置200的每一块可具有四个子块的实例。然而,子块的数目 可不同于四个。

72.如图4中所示,介电结构424可(在x方向上)与介电结构451交错,使得介电结构 424中的每一个可位于两个介电结构451之间。介电结构424和451还可构造(例如,布 置)成使得介电结构424和451中的每一个可位于两个邻近块之间,且将邻近块的控制栅 极彼此电分离。举例来说,块blk0与blk1之间的介电结构424可将控制栅极(与信号 wl00、wl10、wl20、wl30相关联)与块blk1的控制栅极(与信号wl01、wl11、wl21、 wl31相关联)电分离。

73.在另一实例中,块blk1与blk2之间的介电结构451可将块blk1的控制栅极(与 信号wl01、wl11、wl21、wl31相关联)与块blk2的控制栅极(与信号wl02、wl12、 wl22、wl32相关联)电分离。

74.在另一实例中,块blk2与blk3之间的介电结构424可将块blk2的控制栅极(与 信号wl02、wl12、wl22、wl32相关联)与块blk3的控制栅极(与信号wl03、wl13、 wl23、wl33相关联)电分离。

75.介电结构424中的每一个可具有在y方向上的长度,和在z方向上的高度(例如, 深度)(展示于图5中),和在x方向上的宽度w1。宽度w1还可视为介电结构424在x 方向上的厚度,所述x方向为从一个块到另一块的方向。举例来说,块blk0与块blk1 之间的介电结构424具有在从块blk0到块blk1的方向(例如,x方向)上的宽度w1(或 厚度)。

76.介电结构451中的每一个可具有在y方向上的长度,和在z方向上的高度(例如, 深度)(展示于图5中),和在x方向上的宽度w2。宽度w2还可视为介电结构451在x 方向上的厚度,所述x方向为从一个块到另一块的方向。举例来说,块blk0与块blk1 之间的介电结构451具有在从块blk0到块blk1的方向(例如,x方向)上的宽度w2(或 厚度)。

77.介电结构424和451中的每一个可包含形成于沿着两个邻近块之间的长度的狭缝(例 如,沟槽)中的介电材料(或材料)。介电结构424和451中的每一个可形成为将邻近块的 控制栅极彼此电分离。

78.宽度w1和宽度w2中的每一个可以米的分数为单位(例如,以纳米(nm)为单位)测 量。宽度w1可小于宽度w2。举例来说,宽度w1可具有200nm到220nm的范围。 宽度w2可具有250nm到280nm的范围。

79.因此,如图4中所示,存储器装置200可具有块(例如,块blk0、bl1、blk2和 blk3)之间的不同介电结构(例如,介电结构424和451)。两个块可邻近介电结构424, 且两个块可邻近介电结构451。

80.如图4中所示的存储器装置200的结构可允许其具有优于一些常规存储器装置的改 进和益处。举例来说,由于介电结构中的一些(例如,介电结构424)可相比于其它介电 结构(例如,介电结构451)由相对较小宽度(例如,宽度w1)形成,所以与其中介电结构 相同(例如,具有类似于宽度w2的宽度)的常规存储器装置相比,存储器装置200的大 小(例如,在x方向上)可相对较小。另外,与这种常规存储器装置相比,存储器装置200 的给定区域的存储器单元密度可相对较高(归因于较小大小)。

81.图5展示根据本文中所描述的一些实施例的包含块blk0、blk1、blk2和blk3 和延伸穿过块blk0、blk1、blk2和blk3且分离块blk0、blk1、blk2和blk3 的控制栅极的介电结构424和451的图4的存储器装置200的一部分的结构的侧视图(例 如,横截面)。如图5中所示,存储器装置200可包含衬底599、形成于衬底之上的源极 290,和衬底599之上的在z方向上的不同层级501到511(其为存储器装置200的物理 装置层级)。块blk0、blk1、blk2和blk3中的每一个的相应子块sb0、sb1、sb3 和sb3的存储器单元串(例如,图3中的存储器单元串231a)的存储器单元210、211、212 和213(图3)可形成于衬底599和源极290之上(例如,在层级501到511当中的相应层 级中在z方向上竖直地形成)。

82.在图5中,数据线270可为图4中的数据线2700到270n中的一个。信号bl可为 图4中的信号bl0到bln中的一个。

83.在图5中,由信号sgd指示的选择线(例如,四个漏极选择线)可对应于块blk0、 blk1、blk2和blk3当中的相应块的相应选择线。举例来说,在块blk0的子块sb0、 sb1、sb2和sb3中,由信号sgd指示的选择线(例如,四个漏极选择线)可对应于与图 4中所示的块blk0的信号sgd00、sgd10、sgd20和sgd30相关联的相应选择线。在 另一实例中,在块blk1的子块sb0、sb1、sb2和sb3中,由信号sgd指示的选择线 (例如,四个漏极选择线)可对应于与图4中所示的块blk1的信号sgd01、sgd11、sgd21和sgd31相关联的相应选择线。

84.如图5中所示,相同块(例如,块blk0)中的选择线(例如,四个漏极选择线)可包含 相应导电区(例如,四个导电区),所述导电区彼此电分离且可在存储器装置200的z方 向上位于相同层级(例如,层级511)上且位于相应块的控制栅极之上(在z方向上)。不同 块(例如,块blk0、blk1、blk2和bll3)之间的选择线的导电区还可在存储器装置 200的z方向上位于相同层级(例如,层级511)上。

85.在图5中,为简单起见,块blk0、blk1、blk2和blk3的控制栅极(例如,四个 控制栅极)由相同信号wl0、wl1、wl2和wl3指示。举例来说,在块blk0中,由 信号wl0、wl1、wl2和wl3指示的控制栅极可对应于分别与图4中所示的块blk0 的信号wl00、wl10、wl20和wl30相关联

的相应控制栅极。在另一实例中,在图5 中的块blk1中,由信号wl0、wl1、wl2和wl3指示的控制栅极可对应于分别与图 4中所示的块blk0的信号wl01、wl11、wl21和wl31相关联的相应控制栅极。如图 5中所示,相同块中的控制栅极(与信号wl0、wl1、wl2和wl3相关联)位于存储器 装置200的z方向上的不同层级(例如,层级503、505、507和509)上(例如,堆叠在彼 此之上)。

86.存储器装置200可包含位于层级502、504、506、508和510上的介电材料(例如, 二氧化硅)521。相应块中的介电材料521与相应块中的控制栅极(与信号wl0、wl1、 wl2和wl3相关联)交错。

87.由信号sgs指示的选择线(例如,源极选择线)可对应于块blk0、blk1、blk2和 blk3的相应选择线。举例来说,在块blk0中,由信号sgs指示的选择线可对应于与 图4中所示的块blk0的信号sgs0相关联的选择线(例如,源极选择线)。在另一实例 中,在块blk1中,由信号sgs指示的选择线可对应于与图4中所示的块blk1的信号 sgs1相关联的选择线(例如,源极选择线)。

88.如图5中所示,介电结构424和451中的每一个可具有在z方向上的高度(例如, 深度)。每一介电结构424和451的深度可为源极290与数据线270之间的距离(例如, 竖直距离)(例如,图4中的数据线2700到270n中的一个)。

89.如图5中所示,存储器装置200可包含块bl0、blk1、blk2和blk3中的柱(存 储器单元柱)550。柱550中的每一个可为相应存储器单元串(例如,存储器单元串231a) 的部分。柱550中的每一个可具有从衬底599在衬底599与数据线270之间向外延伸(例 如,在z方向的方向上竖直延伸)的长度。

90.如图5中所示,相应存储器单元串(例如,存储器单元串231a)的存储器单元210、 211、212和213可在存储器装置200的z方向上位于不同层级(例如,层级503、505、 507和509)中。块blk0、blk1、blk2和blk3中的每一个的控制栅极(与信号wl0、 wl1、wl2和wl3相关联)可位于存储器单元210、211、212和213所位于的相同层级 (例如,层级503、505、507和509)上。因此,存储器单元210、211、212和213和块 blk0、blk1、blk2和blk3的控制栅极可在z方向上沿着柱550的相应部分(例如, 层级503、505、507和509上的部分)定位(例如,竖直地定位)。

91.存储器装置200的衬底599可包含单晶(也称为单晶体)半导体材料。举例来说,衬 底599可包含单晶硅(也称为单晶体硅)。衬底599的单晶半导体材料可包含杂质,使得 衬底599可具有特定导电性类型(例如,n型或p型)。

92.尽管图5中未展示,但存储器装置200可包含位于衬底599中(例如,形成于衬底 599中)的电路系统。电路系统的至少一部分可位于在块blk0、blk1、blk2和blk3 的存储器单元串下(例如,正下)的衬底599的一部分中。电路系统可包含解码器电路、 驱动器电路(例如,字线驱动器)、缓冲器、感测放大器、电荷泵和存储器装置200的其 它电路系统。

93.在图5中,源极290可包含导电材料(或材料(例如,不同层级的不同材料))且可具有 在x方向上延伸的长度。图5展示其中源极290可形成于衬底599的一部分之上(例如, 通过在衬底599之上沉积导电材料)的实例。替代地,源极290可形成于衬底599的一部 分中或形成于其上(例如,通过掺杂衬底599的一部分)。

94.存储器装置200还可包含与存储器装置200的不同层级中的其它元件交错(例如,

与 块blk0、blk1、blk2和blk3的控制栅极交错)的介电材料(未在图5中标记)。举例 来说,存储器装置200可包含与块blk0、blk1、blk2和blk3的控制栅极(与信号 wl0、wl1、wl2和wl3相关联)交错的介电材料(例如,二氧化硅)。

95.块blk0、blk1、blk2和blk3的控制栅极(与信号wl0、wl1、wl2和wl3 相关联)的实例材料包含单种导电材料(例如,单种金属(例如,钨))或不同导电材料层的 组合。举例来说,块blk0、blk1、blk2和blk3的控制栅极中的每一个可包含(例如, 多层)氧化铝、氮化钛和钨。

96.块blk0、blk1、blk2和blk3的选择线(与信号sgs和sgd相关联)可具有与块 blk0、blk1、blk2和blk3的控制栅极(与信号wl0、wl1、wl2和wl3相关联) 相同的材料(或多种材料)。替代地,与信号sgs、sgd或两者相关联的选择栅极具有不 同于控制栅极的材料的材料(或多种材料)。

97.图6展示根据本文中所描述的一些实施例的包含块blk0和blk1、介电结构424 和451、柱550的图4的存储器装置200的一部分的结构的俯视图。在图6中,与块blk0 中的信号sgd00、sgd10、sgd20和sdg30和块blk1中的信号sgd01、sgd11、sgd21和sdg31相关联的选择线部分地展示为虚线。子块sb0、sb1、sb2和sb3中的每一个 可包含与相应选择线(与信号sgd00、sgd10、sgd20和sdg30相关联的选择线中的一 者)相关联的多个行的柱550。如图6中所示,多个行的柱550平行于介电结构424和451 的长度(在y方向上)。举例来说,块blk0的子块sb0可包含与相关联于信号sgd00的选择线相关联的四行的柱550。在另一实例中,块blk0的子块sb1可包含与相关联 于信号sgd01的选择线相关联的四行的柱550(不同于子块sb0的柱550)。其它子块可 包含如图6中所示的相应柱550。因此,块blk0可包含16行的柱550(四个子块中的 每一个中的四行的柱550)。类似地,块blk1可具有16行的柱550。因此,在存储器装 置200中,邻近介电结构424的两个块(例如,块blk0和blk1)可具有总共32行的柱 550。

98.如图6中所示,柱550中的每一个可具有宽度(例如,直径)w3。宽度小于宽度w1。 宽度w3可具有100nm到110nm的范围。

99.图6展示其中每一子块包含四行的柱550的实例。然而,子块中的行的数目可小于 四或大于四。

100.在图6中,为简单起见,部分地展示数据线2700到270n。数据线2700到270n可(在 x方向上)跨块(例如,块bl0和bl1)延伸且位于柱550之上。柱550与数据线2700到 270n之间的连接(例如,在z方向上的竖直连接)未在图6中展示。然而,块的相同子块 中的每一柱550可耦合到数据线2700到270n当中的单独(例如,唯一)数据线。数据线 2700到270n中的每一个可耦合到来自块的每一子块的一个柱550。举例来说,数据线 2700可耦合到块blk0中的四个柱550(例如,由所述四个柱550共享),一个柱550来 自块blk0的子块sb0、sb1、sb2和sb3中的每一个。在另一实例中,数据线2701可 耦合到块blk0中的另四个柱550(例如,由所述另四个柱550共享),一个柱550来自 块blk0的子块sb0、sb1、sb2和sb3中的每一个。在另一实例中,数据线270n可耦 合到块blk0中的四个柱550(例如,由所述四个柱550共享),一个柱550来自块blk0 的子块sb0、sb1、sb2和sb3中的每一个。

101.类似地,数据线2701可耦合到块blk1中的四个柱550(例如,由所述四个柱550 共享),一个柱550来自块blk1的子块sb0、sb1、sb2和sb3中的每一个。在另一实 例中,数据线270n可耦合到块blk1中的四个柱550(例如,由所述四个柱550共享), 一个柱550来自块

口(例如,孔)720。存储器装置200可包含形成于相应开口720的侧壁上的介电材料(例 如,介电衬里)731。存储器装置200可包含形成于相应开口720中的导电触点765。导 电触点765可接触(例如,电耦合到)相应控制栅极和选择线。

110.存储器装置200还可包含耦合到相应导电触点765的导电路径(例如,类似于图2 的存储器装置200的导电路径2560)。导电路径可耦合到存储器装置200的其它电路系 统(例如,衬底599中的驱动器电路)。可通过导电路径和导电触点765将信号wl00、 wl10、wl20和wl30、sgd0和sgs0提供到相应控制栅极和选择线。

111.图8展示根据本文中所描述的一些实施例的包含块blk0和blk1的柱550和控制 栅极的细节的图2至图7中所示的存储器装置200的一部分的结构的侧视图(例如,横截 面)。图9(下文描述)展示沿图8的线9-9截取的存储器装置200的控制栅极2230和柱 550的一部分的横截面(例如,俯视图)。

112.图8中的存储器装置200的结构对应于展示于图3中的存储器装置200的示意图的 部分和展示于图5中的存储器装置200的结构(侧视图)。为简单起见,仅在图8中展示 图5的存储器装置200的一部分且不重复类似或相同元件的详细描述。

113.存储器装置200可包含耦合在相应柱550与相应数据线(例如,数据线2700)之间的 导电结构(例如,导电插塞)875。耦合到存储器单元串(例如,存储器单元串231a)的柱 550的导电结构875可在存储器装置200的操作(例如,读取或写入操作)期间形成位于 数据线(例如,数据线2700)与源极290之间的穿过相应存储器单元串的导电路径(例如, 电流路径)的部分。

114.如图8中所示,存储器装置200可包含可为相应柱550的部分的结构830和介电材 料805。结构830和介电材料805可沿着相应柱550的长度连续地延伸。介电材料805 可包含二氧化硅。结构830可电耦合到源极290和相应数据线(例如,数据线2700)。块 中的相应柱550的结构830邻近(例如,接触)所述块的相应控制栅极的部分。举例来说, 块blk0中的柱550的结构830邻近(例如,接触)块blk0的控制栅极2200、2210、2220和2230。

115.图8展示具有特定形状(例如,展示于图8中的竖直圆柱形形状)的结构830的实例。 然而,结构830可具有不同形状(例如,非圆柱形形状)。图9中展示沿着线9-9的柱550 的结构的实例横截面。

116.如图8中所示,结构830可包含部分801、802、803和804。存储器单元串的存储 器单元210、211、212和213中的每一个可包含邻近控制栅极中的一个(控制栅极2200、 2210、2220和2230、2201、2211、2221和2231中的一个)定位的部分801、802、803和 804中的每一个的部分。举例来说,存储器单元串231a的存储器单元213可包含邻近控 制栅极2230的结构830的部分(部分801、802、803和804)。在另一实例中,存储器单 元串231a的存储器单元212可包含邻近控制栅极2220的结构830的部分(部分801、802、 803和804)。

117.结构830可包含导电结构(例如,部分804),所述导电结构可为导电路径(例如,柱 通道结构)的部分以在耦合到结构830的相应数据线(例如,数据线2700)与源极290之间 传导电流。结构830可为onos(sio2、si3n4、sio2、si)结构的部分。举例来说,部分 801可包含sio2,所述sio2可与邻近控制栅极的部分组合以形成能够阻挡电荷的隧穿的 电荷阻挡材料(或多种电荷阻挡材料)。部分802可包含电荷存储元件(例如,电荷存储部 分、电荷存储材料(或多种电荷存储材料),例如si3n4),所述电荷存储元件可提供电荷 存储功能(例如,捕

获电荷)以表示存储在存储器单元210、211、212或213中的信息的 值。部分803可包含介电质,例如一或多种隧道介电材料(例如,sio2),所述介电质能 够允许电荷(例如,电子)的隧穿。部分804可包含多晶硅(例如,掺杂或未掺杂的多晶硅), 且可为可在存储器装置200的操作期间传导电流的通道结构(例如,柱通道)。作为实例, 部分803可允许电子在写入操作期间从部分804隧穿到部分802,且允许电子在存储器 装置200的擦除操作期间从部分802隧穿到部分804。

118.在替代性布置中,结构830可为sonos(si、sio2、si3n4、sio2、si)结构、tanos (tan、al2o3、si3n4、sio2、si)结构、manos(金属、al2o3、si3n4、sio2、si)结构或 其它结构的部分。替代地,结构830可为浮动栅极结构的部分(例如,部分802(电荷存 储部分)可为多晶硅)。

119.存储器装置200的控制栅极和介电材料521可包含邻近(例如,接触)相应介电结构 424和451的相应边缘(例如,竖直边缘)。图8展示块blk0、blk1和blk3的控制栅 极中的一些的边缘e

cg1

、e

cg2

、e

cg3

、e

cg4

、e

cg5

和e

cg6

,和块blk0、blk1和blk3 的介电材料521中的一些的边缘e

ox1

、e

ox2

、e

ox3

、e

ox4

、e

ox5

和e

ox6

。

120.如图8中所示,块blk0的控制栅极2200、2210、2220和2230中的每一个可包含邻 近(例如,接触)介电结构451(图8的右方上的介电结构451)的材料451l的边缘(例如, 控制栅极2220的边缘e

cg2

),和邻近(例如,接触)介电结构424的材料424l(左侧上的材 料424l)的边缘(例如,控制栅极2220的边缘e

cg3

)。

121.块blk1的控制栅极2201、2211、2221和2231中的每一个可包含邻近介电结构424 的材料424l(右侧上的材料424l)的边缘(例如,控制栅极2221的边缘e

cg3

),和邻近介 电结构451(图8的右方上的介电结构451)的材料451l(左侧上的材料451l)的边缘(例 如,控制栅极2221的边缘e

cg5

)。块blk2的控制栅极(与信号wl02、wl12、wl22和 wl32相关联)还可包含邻近介电结构451(图8的右方上的介电结构451)的材料451l的 相应边缘(例如,边缘e

cg6

)。

122.类似地,材料521还可包含邻近介电结构424和451的相应边缘(例如,竖直边缘)。 举例来说,在块blk0中,介电材料521中的每一个可包含邻近介电结构451(图8的左 方上的介电结构451)的材料451l(右侧上的材料451l)的边缘(例如,边缘e

ox2

),和邻 近介电结构424的材料424l(左侧上的材料424l)的边缘(例如,边缘e

ox3

)。在块blk1 中,介电材料521中的每一个可包含邻近介电结构424的材料424l(右侧上的材料424l) 的边缘(例如,边缘e

ox4

),和邻近介电结构451(图8的右方上的451)的材料451l(左侧 上的材料424l)的边缘(例如,边缘e

ox5

)。

123.因此,如图8中所示,介电结构424的(在左侧上的)材料424l可接触块blk0的控 制栅极2200、2210、2220和2230中的每一个(例如,接触其边缘),且介电结构424的(在 右侧上的)材料424l可接触块blk1的控制栅极2201、2211、2221和2231中的每一个。 介电结构424的(在左侧和右侧上的)材料424l还可接触邻近块(例如,块blk0和blk1) 的相应介电材料521(例如,接触其边缘)。

124.如图8中所示,位于存储器装置200的相同层级上的邻近块的相对控制栅极可彼此 分离基于(例如,等于)宽度w1或宽度w2的距离。举例来说,相应控制栅极2220和222

1 (其位于相同层级507上)的边缘e

cg3

和e

cg4

可彼此分离等于边缘e

cg3

与e

cg4

之间的介 电结构424的宽度(例如,宽度w1)的距离。在另一实例中,位于层级507上的控制栅极 2220的边缘e

cg2

和相对控制栅极(未标记)的边缘e

cg1

可彼此分离等于边缘e

cg1

与e

cg2

之间的介电结构451的宽

度(例如,宽度w2)的距离。在另一实例中,位于层级507上的 控制栅极2221的边缘e

cg5

和相对控制栅极(与信号wl22相关联)的边缘e

cg6

可彼此分离 等于边缘e

cg5

与e

cg6

之间的介电结构451的宽度(例如,宽度w2)的距离。

125.类似地,如图8中所示,位于存储器装置200的相同层级上的邻近块的介电材料521 可彼此分离基于(例如,等于)宽度w1或宽度w2的距离。举例来说,层级504上的相 应介电材料521的边缘e

ox3

和e

ox4

可彼此分离等于边缘e

ox3

与e

ox4

之间的介电结构 424的宽度(例如,宽度w1)的距离。在另一实例中,位于层级504上的介电材料521的 边缘e

ox2

和相对介电材料(未标记)的边缘e

ox1

可彼此分离等于边缘e

ox1

与e

ox2

之间的 介电结构451的宽度(例如,宽度w2)的距离。在另一实例中,位于层级504上的介电材 料521的边缘e

ox5

和相对介电材料(未标记)的边缘e

ox6

可彼此分离等于边缘e

ox5

与e

ox6

之间的介电结构451的宽度(例如,宽度w2)的距离。

126.如图8中所示,块中的控制栅极中的每一个可具有在x方向上的宽度。可从相应控 制栅极的一个边缘到相应控制栅极的另一边缘测量相应控制栅极的宽度。举例来说,控 制栅极2220可具有从边缘e

cg2

到边缘e

cg3

所测量的宽度。块中的相应控制栅极的宽度 还可为块的宽度。存储器装置200的块可具有相同宽度。举例来说,块(例如,块blk0 和blk1)中的每一个可具有在2微米到2.2微米范围内的宽度。因此,存储器装置200 的控制栅极(控制栅极2200、2210、2220和2230)中的每一个可具有在2微米到2.2微米 范围内的宽度。

127.图9展示根据本文中所描述的一些实施例的包含存储器单元串231a的存储器单元 213处的控制栅极2230和邻近柱550的一部分的图8的存储器装置200的一部分的横截 面。存储器装置200的存储器单元串的其它控制栅极和柱具有展示于图9中的类似或相 同结构。如图9中所示,控制栅极2230可包围柱550。部分801、802、803和804可包 含如图9中所示的形状。柱550的介电材料805可由部分(例如,柱通道结构的部分)804 包围。图9展示其中部分804为中空结构(因为其包围介电材料805)的实例。替代地, 可省略介电材料805,使得部分804的材料还可占据介电材料805的位置。

128.如图9中所示,柱550可包含宽度w3。宽度w3可小于宽度w1(图8)。如上文所 提及,本文中所描述的图式中的元件未按比例调整。宽度w3可小于宽度w1(图8)。举 例来说,宽度w1可大于2倍宽度w3且小于3倍宽度w3(例如,2w3《w1《4w3)。

129.参考图2至图9的以上描述描述存储器装置200的结构。存储器装置200的结构中 的一些或全部可使用与下文参考图10a和图10b至图19a和图19b所描述的工艺相关 联的工艺形成。

130.图10a和图10b至图19a和图19b展示根据本文中所描述的一些实施例的在形成 存储器装置1000的工艺期间元件的不同视图。为简单起见,图10a和图10b至图19a 和图19b部分地展示存储器装置1000的部分以便不混淆本文中所描述的实施例。

131.图10a展示在介电材料(介电材料层级)1021和介电材料(介电材料层级)1022替代 地形成于衬底1099之上之后存储器装置1000的在x方向上的侧视图(例如,横截面)。 衬底1099类似于(例如,可对应于)存储器装置200的衬底599(图5和图8)。介电材料 1021和1022可以交错方式在衬底1099之上一种材料接一种材料地依序形成,使得介电 材料1021可与介电材料1022交错。

132.图10b展示沿图10a的线10b-10b截取的存储器装置200的部分(例如,在x-y平 面

中)的俯视图。展示于图10a中的存储器装置1000的侧视图(在x-z方向上)是沿图10b 的线(例如,横截面线)10a-10a截取。

133.如图10a中所示,形成存储器装置1000的过程可包含在衬底1099之上形成材料 1090。材料1090可形成类似于图5的源极290的源极(例如,与信号src相关联)的部 分。

134.所属领域的技术人员将容易认识到,本文中参考图10a和图10b至图19a和图19b 所描述的形成存储器装置1000的工艺可包含在图10a中的存储器装置1000的部分1091 和1092(以虚线展示)中形成额外元件(未展示)。举例来说,部分1091中的额外元件可包 含类似于选择电路(例如,源极选择电路)241'a、244'a、241'b和244'b的选择电路和存储 器装置200的其它元件(例如,图2、图3和图5、图8)。在另一实例中,部分1092中 的额外元件可包含类似于选择电路(例如,漏极选择电路)241a、244a、241b和244b的 选择电路和存储器装置200的其它元件(例如,图2、图3和图5、图8)。为简单起见且 不混淆本文中所描述的实施例,从本文中的描述省略对部分1091和1092(图10a)中的 这种额外元件的形成的描述。

135.在以下描述中,后续工艺中的存储器装置1000的不同视图是基于图10a和图10b 的存储器装置1000的视图且遵循图10a和图10b的视图(例如,侧视图和俯视图)的相 同布置。举例来说,图11a展示沿图11b的线(例如,横截面线)11a-11a截取的存储器 装置1000的一部分的侧视图。图11b展示沿图11a的线11b-11b截取的图11a的存储 器装置1000的一部分的俯视图。为简单起见,以下描述省略从一个工艺到下一工艺的 存储器装置1000的部分的重复特定视图(例如,侧视图和俯视图)和特定横截面线。

136.在本文中的描述中,给予相同数字标记的元件为类似或相同元件。举例来说,柱550 (图5和图8)和柱550'(图12a)为类似或相同元件。在另一实例中,控制栅极2200、2210、 2220和2230(图8)和控制栅极220'0、221'0、222'0和223'0(图17a)为类似或相同元件。 在另一实例中,控制栅极2201、2211、2221和2231(图8)和控制栅极220'1、221'1、222'1和223'1(图17a)为类似或相同元件。因此,为简单起见,可能不重复类似或相同元件的 详细描述。

137.图11a和图11b展示在穿过介电材料1021和1022形成开口(例如,孔)1150之后 存储器装置1000的不同视图。形成开口1150可包含在开口1150的位置处去除(例如, 蚀刻)介电材料1021和1022的一部分。

138.图12a和图12b展示在存储器单元串231'a和231'b的柱550'和存储器单元210'、 211'、212'和213'形成之后存储器装置1000的不同视图。形成柱550'可包含在相应开口1150(在图11a中标记)中形成结构830'和介电材料805'。柱550'类似于(例如,可对应于) 图8的柱550。结构830'和介电材料805'分别类似于(例如,可对应于)图8的结构830 和介电材料805。为简单起见,从图12a和图12b省略每一柱550'的结构830'的细节。

139.图12a中的结构830'可形成图12a的存储器装置1000的相应存储器单元串的存储 器单元210'、211'、212'和213'的部分。图12b的存储器单元210'、211'、212'和213'分 别类似于(例如,可对应于)图8的存储器装置200的存储器单元210、211、212和213。 存储器装置1000的存储器单元串231'a和231'b类似于(例如,可对应于)图8的存储器 装置200的存储器单元串231a和231b。

140.在图12a中,介电材料1022层级(例如,层)(或替代地,包含介电材料1021层级 和介电材料1022层级的两个邻近层级)可称为存储器装置1000的层次。如图12a中所 示,存储器装置800的层次可在衬底1099之上在z方向上位于(例如,堆叠在)彼此之上, 使得两个邻

近层次可由相应介电材料(例如,二氧化硅)1021层级(例如,层)彼此分离。 图12a展示可随后处理以形成存储器装置1000的每一块中的四个对应控制栅极和四个 存储器单元层级的特定数目个层次(例如,四个层次)的实例。然而,存储器装置1000可 在图12a中包含多达(或多于)一百个层次,所述层次可处理以形成对应控制栅极和存储 器单元层级的多达(或多于)一百个层次。

141.图13a、图13b和图13c展示在形成狭缝(例如,开口、沟槽或切口)1324之后的 存储器装置1000。狭缝1324可形成为将介电材料1021和1022和柱550'分离(例如,划 分)成多个部分1301。为简单起见,以下描述描述图13a和图13b的狭缝1324。图13c 中的其它狭缝1324具有类似结构。

142.如图13a和图13b中所示,狭缝1324可形成为使得其可延伸穿过介电材料1021 和1022的层级。狭缝1324可包含在x方向上的宽度w1。狭缝1324可包含在x方向 上彼此相对的侧壁1324a和1324b。侧壁1324a和1324b为可包含在狭缝1324处暴露 的介电材料1021和1022的相应部分的竖直侧壁。因此,宽度w1也为位于相同层级(在 z方向上)且暴露于相应侧壁1324a和1324b处的介电材料1021的相应部分(例如,竖 直边缘)之间的距离。

143.狭缝1324可形成为将相应存储器单元串的介电材料1021和1022和柱550'分离(例 如,划分)成多个部分。举例来说,如图13a和图13b中所示,狭缝1324可将存储器单 元串231'a和231'b的介电材料1021和1022和柱550'分离成狭缝1324的左方和右方上 的部分1301。

144.图14a、图14b和图14c展示在介电结构424'形成于狭缝1324(标记于图13a中) 中之后的存储器装置1000。形成介电结构424'可包含在狭缝1324中(例如,在狭缝1324 的侧壁上)形成材料(例如,衬里)424'l且接着在材料424'l之间形成材料(例如,多晶硅) 424'p。介电结构424'和材料424'l和424'p分别类似于(例如,可对应于)上文参考图8 和图4所描述的存储器装置200的介电结构424和材料424l和424p。在形成图14a和 图14b中的存储器装置1000的介电结构424'的替代性工艺中,可省略形成材料424'p 的工艺。因此,在存储器装置1000的替代性结构中,材料424'l可形成为还占据材料 424'p的位置,使得材料(例如,二氧化硅)424'l可填充狭缝1324。

145.因此,如图14a、图14b和图14c中所示,形成介电结构424'可在x方向上将介 电材料1021和1022分离(例如,划分)成多个部分1301。多个部分1301中的每一个可 包含存储器装置1000的存储器单元串的柱550'的相应部分。

146.图15a、图15b和图15c展示在形成狭缝(例如,开口、沟槽或切口)1551之后的 存储器装置1000。狭缝1551可形成为与其中形成介电结构424'的狭缝1324(标记于图 13c中)交错,使得部分1301(标记于图13c中)中的介电材料1021和1022和柱550'可 分离(例如,划分)成多个块blk。块blk可形成存储器装置1000的相应块(例如,块 blk、blk0、blk1和blk2)。为简单起见,以下描述描述图15a和图15b的狭缝1551。 图15c中的其它狭缝1551具有类似结构。

147.如图15a中所示,狭缝1551可形成为使得其可延伸穿过介电材料1021和1022的 层级。狭缝1551可包含在x方向上的宽度w2。狭缝1551可包含在x方向上彼此相对 的侧壁1551a和1551b。如图15a中所示,侧壁1551a和1551b为可包含暴露于狭缝 1551处的介电材料1021和1022的相应部分的竖直侧壁。因此,宽度w2也为位于相同 层级(在z方向上)且暴

露于相应侧壁1551a和1551b处的介电材料1021的相应部分(例 如,竖直边缘)之间的距离。

148.如图15a中所示,(在图15a的左方上的)狭缝1551可将介电材料1021和1022和 部分1301的柱550'(标记于图13c中)分离成块blk和blk0。(在图15a的右方上的) 狭缝1551可将介电材料1021和1022和柱550'分离成块blk1和blk2。

149.狭缝1551可包含在x方向上的宽度w2。宽度w2也为位于相应侧壁1551a和1551b 处的相同层级(在z方向上)的介电材料1021的相应部分的边缘(例如,竖直边缘)之间的 距离。宽度w2可大于宽度w1。

150.与图16a、图16b、图17a和图17b相关联的以下描述涉及工艺,所述工艺包含去 除且接着用相应材料层级替换介电材料(例如,氮化硅)1022层级以在存储器装置1000 中的相应层次中形成控制栅极。

151.图16a和图16b展示在从位置1522去除(例如,掘出)介电材料1022之后的存储器 装置1000。图16a中的位置1522为由图15a中的介电材料1022占据的空隙(空的空间)。 在后续工艺中,可在位置1522中形成材料以形成存储器装置1000的相应控制栅极。

152.如图16a中所示,每一柱550'可包含暴露于相应位置1522处的部分550'w。每一 部分550'w可为相应柱550的竖直侧壁的部分。每一部分550'w可在z方向上在也暴露 于相应位置1522处的两个邻近介电材料1021层级之间延伸。

153.如图16a中所示,介电结构424'可包含暴露于相应位置1522处的部分424'w。每 一部分424'w可为介电结构424'的竖直侧壁的部分。每一部分424'w可在z方向上在也 暴露于相应位置1522处的两个邻近介电材料1021层级之间延伸。

154.图17a和图17b展示在形成控制栅极220'0、221'0、222'0和223'0(在块blk0中) 和控制栅极220'1、221'1、222'1和223'1(在块blk1中)之后的存储器装置1000。块blk0 中的控制栅极220'0、221'0、222'0和223'0和块blk1中的控制栅极220'1、221'1、222'1和223'1分别类似于(例如,可对应于)存储器装置200(例如,图8)的块blk0中的控制 栅极2200、2210、2220和2230和块blk1中的控制栅极2201、2211、2221和2231。

155.形成控制栅极220'0、221'0、222'0和223'0(在块blk0中)和控制栅极220'1、221'1、 222'1和223'1(在块blk1中)可包含在这些控制栅极中的每一个中形成衬里结构1752和 材料1754。衬里结构1752可在形成材料1754之前。

156.衬里结构1752可包含单种材料(例如,单个材料层)或多种不同材料的组合(例如, 形成于彼此之上的多个不同材料层)。举例来说,线结构1752可包含介电材料。介电材 料可包含高k介电材料(例如,氧化铝(al2o3))或其它高k介电材料。在另一实例中,衬 里结构1752可包含介电材料(例如,al2o3)与导电材料(例如,氮化钛(tin))的组合。

157.材料1754可包含导电材料金属。举例来说,材料1754可包含金属(例如,钨或另一 金属)。图17a展示其中衬里结构1752包含形成于狭缝1551处的介电材料1021的相应 部分(例如,竖直边缘)上的部分1752v。然而,部分1752v可去除,使得介电材料1021 的部分(例如,竖直边缘)可暴露于狭缝1551处。在形成存储器装置1000的替代性工艺 中,可省略形成衬里结构1752的工艺。

158.图18a、图18b和图18c展示在介电结构451'形成于相应狭缝1551(标记于图15c 中)中之后的存储器装置1000。如图18a中所示,形成介电结构451'可包含在狭缝1551 中(例如,在狭缝1551的侧壁上)形成材料(例如,衬里)451'l,且接着在材料451'l之间 形成

材料451'p。介电结构451'和材料451'l和451'p分别类似于(例如,可对应于)上文 参考图6所描述的存储器装置200的介电结构451和材料451l和451p。如图18a中所 示,介电结构451'可将邻近块的控制栅极电分离。举例来说,(在图18a的右方上的)介 电结构451'可将块blk1的控制栅极220'1、221'1、222'1和223'1与块blk2的控制栅极(未 标记)分离。

159.因此,如上文所描述,介电结构424'(图14a和图14c)可形成为将介电材料1021 和1022和柱550'分离成多个部分(例如,图14c中的部分1301)。多个部分中的每一个 位于两个介电结构424'之间。多个部分中的每一个包含介电材料1021和1022和柱550' 的相应部分。接着,介电结构451'(图18c)可形成于多个部分中。介电结构451'在x方 向上交错,使得一个介电结构451'可位于两个介电结构424'之间,且一个介电结构424' 可位于两个介电结构451'之间。如图18c中所示,介电结构451'可将多个部分1301(标 记于图14c中)分离成存储器装置1000的块(例如,图18a中的块blk0、blk1和blk2)。 如图18a中所示,多个块中的两个邻近块(例如,块blk1和blk2)可由介电结构451' 中的一个彼此分离。多个块中的两个邻近块(例如,块blk0和blk1)可由介电结构424' 中的一个彼此分离。

160.如上文所描述形成存储器装置1000可提供优于一些常规技术的改进和益处。举例 来说,由于介电结构424'(图14c)在形成介电结构451'(图18c)之前形成,所以可减轻 或减少块弯曲误差。块弯曲误差可在用于形成存储器装置的块的部分具有相对较高纵横 比时发生。高纵横比可能降低这种部分的结构的稳定性(例如,削弱所述结构)且可导致 其弯曲(例如,在x方向上弯曲)。然而,在存储器装置1000中,在不同时间形成不同 介电结构(例如,介电结构424'在形成图18c中的介电结构551'之前形成于与图14c相 关联的工艺中)可合并随后用于形成邻近块的邻近部分。合并可减小用于形成存储器装置 1000的块的部分(例如,部分1301)的纵横比。这可提高这种部分的结构的稳定性(例如, 加强所述结构)。因此,可减轻或减少块弯曲误差。

161.此外,在形成存储器装置1000的一些结构中,可形成数个块弯曲吸收结构(例如, 虚设块)以减小块弯曲误差。然而,形成介电结构424'(其可加强用于形成块的部分(例如, 部分1301))可减少这种块弯曲吸收结构的数目(例如,虚设块的数目)。因此,存储器装 置1000的大小可相对小于一些常规装置,且存储器装置1000的存储器单元密度可增大。

162.图19a和图19b至图22a和图22b展示在形成用于存储器装置1000的块的楼梯结 构和导电触点(例如,字线触点)的工艺期间元件的不同视图。为简单起见,以下描述(图 19a至图22b)描述用于在存储器装置1000的块blk0的一部分处形成楼梯结构和导电 触点的工艺。然而,存储器装置1000的其它块的楼梯结构和导电触点可形成于相同工 艺中。

163.图19a和图19b展示包含存储器阵列201'和楼梯区454'处的块blk0的一部分的存 储器装置1000。存储器阵列201'和楼梯区454'分别类似于(例如,可对应于)存储器装置 200(例如,图4)的存储器阵列201'和楼梯区454'。

164.图19a展示在y-z方向上的块blk0的一部分的侧视图(例如,横截面)。y方向平 行于介电结构424'和451'(图18c)的长度。图19b展示沿图19b的线(例如,横截面线) 19a-19a截取的块blk0的一部分的俯视图。图20a和图20b、图21a和图21b和图 22a和图22b中的存储器装置1000的部分布置在相同视图(例如,分别为俯视图和侧视 图)中。

165.图19a和图19b展示在存储器装置1000的柱(例如,柱550')和存储器单元(例如, 存储器单元210'、211'、212'和213')形成于存储器阵列201中之后的存储器装置1000。 存

意味着仅a;仅b;或a和b。在另一实例中,如果列举项目a、b和c,那 么短语“a、b和c中的至少一个”意味着仅a;仅b;仅c;a和b(不包含c);a和 c(不包含b);b和c(不包含a);或所有的a、b和c。项目a可包含单个元件或多个 元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

181.在具体实施方式和权利要求书中,通过术语“中的一个”接合的项目列表可意味着 所列项目中的仅一个。举例来说,如果列举项目a和b,那么短语“a和b中的一个

”ꢀ

意味着仅a(不包含b)或仅b(不包含a)。在另一实例中,如果列出项目a、b和c,那 么短语“a、b和c中的一个”意味着仅a;仅b;或仅c。项目a可包含单个元件或 多个元件。项目b可包含单个元件或多个元件。项目c可包含单个元件或多个元件。

182.以上描述和图式说明本发明主题的一些实施例,以使所属领域的技术人员能够实践 本发明主题的实施例。其它实施例可并有结构性、逻辑、电性、工艺和其它变化。实例 仅代表可能的变化。一些实施例的部分和特征可包含在其它实施例的那些部分和特征 中,或代替那些部分和特征。在阅读和理解以上描述后,所属领域的技术人员将显而易 见许多其它实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1