半导体晶圆和其制造方法与流程

1.本文所述的主旨是关于半导体测试,且特别是关于在制造制程期间的半导体层监控。

背景技术:

2.半导体制造制程包括多个制造步骤或加工,其中各个步骤或加工对形成一或多个半导体层具有贡献。例如,可以通过掺杂部分的结晶半导体基板形成各层。另外,可以通过在结晶半导体基板上添加例如导电层、电阻层及/或绝缘层而形成一或多个层。

3.一或多个所制造的层可能由于制程变异(manufacturing variation)而具有缺陷。

技术实现要素:

4.根据本公开的实施例,提供一种制造半导体晶圆的方法,包括将半导体晶圆暴露至一或多个掺杂剂种类以形成一或多个第一布植层在半导体晶圆上、测试所形成的一或多个第一布植层的一或多个几何参数值,以及在测试一或多个几何参数值之后有条件地将半导体晶圆暴露至一或多个掺杂剂种类,以形成一或多个额外布植层在半导体晶圆上。方法还包括在形成一或多个额外布植层之后,有条件地形成一或多个额外电路层在半导体晶圆上以形成多个功能性电子电路在半导体晶圆上,以及以晶圆允收测试步骤有条件地测试半导体晶圆。

5.根据本公开的实施例,提供一种半导体晶圆,包括形成电路部分和第一测试部分的一或多个第一布植层,电路部分形成至少部分形成的半导体电路,其中第一测试部分中的第一剖面暴露第一测试部分的一或多个第一布植层。半导体晶圆还包括进一步形成电路部分和第二测试部分的一或多个第二布植层,其中第二测试部分中的第二剖面暴露第二测试部分的一或多个第二布植层,其中第一测试部分和第二测试部分分开,以及其中第一剖面和第二剖面不相交。

6.根据本公开的实施例,提供一种制造半导体晶圆的方法,包括将半导体晶圆暴露至一或多个掺杂剂种类以形成一或多个第一布植层在半导体晶圆上、切割半导体晶圆以暴露一或多个第一布植层,以及测试一或多个第一布植层的一或多个几何参数值,其中测试包括以探针接触所暴露的一或多个第一布植层。方法还包括在测试一或多个几何参数值之后,有条件地形成一或多个金属化层在半导体晶圆上以电性连接半导体晶圆上的多个功能性电子电路,以及以晶圆允收测试步骤有条件地测试半导体晶圆。

附图说明

7.当结合附图阅读时,从以下详细描述中可以最好地理解本公开的各方面。应注意,根据工业中的标准方法,各种特征未按比例绘制。实际上,为了清楚地讨论,可任意增加或减少各种特征的尺寸。

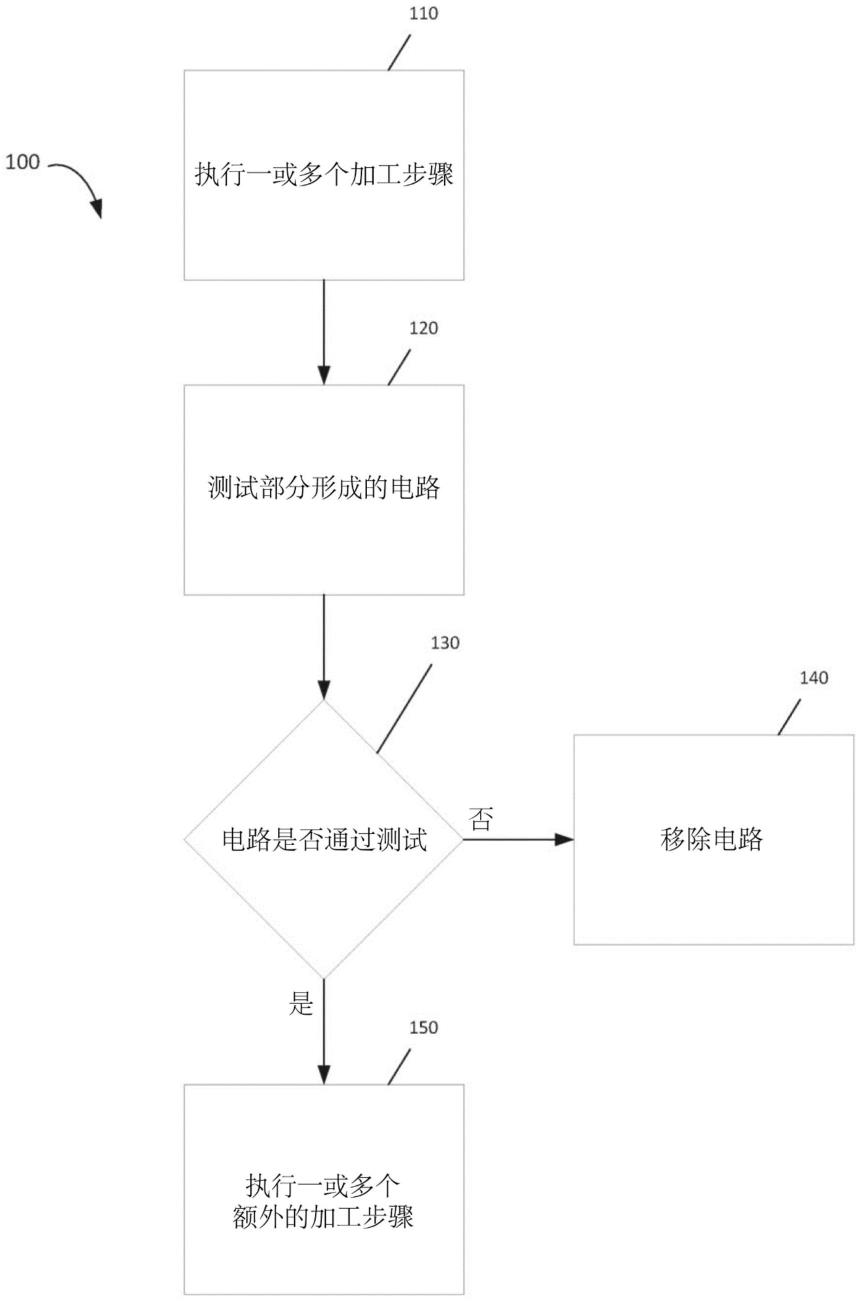

8.图1根据一些实施例绘示制造电路的方法流程图;

9.图2根据一些实施例绘示测试部分形成的半导体电路的方法流程图;

10.图3a根据一些实施例绘示在经过测试程序之前的部分形成的半导体电路的示意截面图;

11.图3b根据一些实施例绘示图3a的半导体电路在经过测试程序和进一步制程之后的示意截面图;

12.图4a根据一些实施例绘示在经过测试程序之前的部分形成的半导体电路和部分形成的测试电路的示意截面图;

13.图4b根据一些实施例绘示图4a的半导体电路和测试电路在经过测试程序和进一步制程之后的示意截面图;

14.图5根据一些实施例绘示部分形成的半导体及/或测试电路的示意截面图;

15.图6根据一些实施例绘示部分形成的半导体及/或测试电路的示意图;

16.图7根据一些实施例绘示半导体晶圆的示意图;

17.图8根据一些实施例绘示半导体电路制造制程的示意图;

18.图9a、图9b和图10是根据一些实施例的剖面的示意图;

19.图11a是根据一些实施例可以使用的扫描展延电阻显微镜系统的示意图;

20.图11b是根据一些实施例可以使用的扩散电阻分析系统的示意图。

21.实际上,相似的参考数字可表示相似的结构、特征或元件。

22.【符号说明】

23.100:方法

24.110,120,130,140,150:步骤

25.200:方法

26.210,220,230,240,250:步骤

27.300:半导体晶圆

28.310:基板

29.320:深p阱部分

30.330:单元p阱部分

31.340:深p阱部分

32.350:单元p阱部分

33.360:深n型嵌入式光电二极管布植部分

34.370:n型嵌入式光电二极管布植部分

35.380:深n型嵌入式光电二极管布植部分

36.390:n型嵌入式光电二极管布植部分

37.400:半导体晶圆

38.410:电路部分

39.420,430:测试部分

40.460:深p阱测试结构

41.470:单元p阱测试结构

42.490:深n型嵌入式光电二极管测试结构

43.500:半导体晶圆

44.510:测试电路

45.520:基板接触件

46.530:隔离结构

47.600:半导体晶圆

48.620:基板接触件

49.700:半导体晶圆

50.710:电路区域

51.721,722,723,724,725:测试部分

52.800:方法

53.802,804,806,808,810,812,818,820,822,824,826,830,832,836,838,840,842,844,846,848:步骤

54.910,920:剖面

55.1000:半导体晶圆

56.1010,1020,1030:剖面

57.1050:边缘

58.1110,1120,1130:探针

具体实施方式

59.为了实现提及主题的不同特征,以下公开内容提供了许多不同的实施例或示例。以下描述组件、配置等的具体示例以简化本公开。当然,这些仅仅是示例,而不是限制性的。例如,在以下的描述中,在第二特征之上或上方形成第一特征可以包括第一特征和第二特征以直接接触形成的实施例,并且还可以包括在第一特征和第二特征之间形成附加特征,使得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各种示例中重复参考数字和/或字母。此重复是为了简单和清楚的目的,并且本身并不表示所讨论的各种实施例和/或配置之间的关系。

60.此外,本文可以使用空间相对术语,诸如“在

…

下面”、“在

…

下方”、“下部”、“在

…

上面”、“上部”等,以便于描述一个元件或特征与如图所示的另一个元件或特征的关系。除了图中所示的取向之外,空间相对术语旨在包括使用或操作中的装置的不同取向。装置可以以其他方式定向(旋转90度或在其他方向上),并且同样可以相应地解释在此使用的空间相对描述符号。

61.本文的内容将结合附图描述数个做为示例的实施例。以下的内文仅提供实施例并且并非意图限制本公开的范畴、应用性或。相对而言,以下实施例的内文将提供本领域技术人员可以实现一或多个实施例的叙述。应理解的是,可以在元件的功能和配置上做多个变化,而免于偏离本公开的精神和范畴。在以下内容中,为了解释的目的,将阐述具体细节以提供对特定创造实施例的彻底了解。然而,应理解可以在免于这些具体细节的情况下实施多个实施例。附图和内文并非意图做为限制。本文中使用的用语“示例”或“例子”表示“做为示例、举例或绘示例”。本文所述做为“例子”或“示例”的任何实施例或设计并非需要推断成较佳或优于其他实施例或设计。

62.根据一些实施例,图1绘示制造半导体电路的方法100的流程图。如图中所示,在制造制程期间,在半导体晶圆上部分地加工半导体电路,并且另外测试针对制造规格的符合性。例如在测试时,可以尚未执行后段制程(back end of line,beol)或其他制程于部分加工的半导体晶圆上。

63.在步骤110,半导体制造设备执行或通过例如控制器控制半导体制造设备执行一或多个加工步骤,以在半导体晶圆上部分地形成半导体电路。例如,可以形成一或多个布植层在半导体晶圆上或半导体晶圆中。在一些实施例中,可以通过添加和图案化在半导体晶圆上方或半导体晶圆上的材料而形成一或多个额外层。

64.在一些实施例中,可以使用本领域技术人员已知的一或多个方法加工半导体晶圆,以形成半导体晶圆中的一或多个布植层。例如,可以使用电场将一或多个种类的掺杂剂离子加速进半导体晶圆。在一些实施例中,在布植离子进半导体晶圆之后,将半导体晶圆暴露至足够高的温度以导致布植的离子进一步扩散或者进一步融入半导体晶圆。在一些实施例中,可以使用本领域技术人员已知的其他技术形成半导体晶圆中的一或多个布植层。

65.在一些实施例中,可以使用本领域技术人员已知的一或多个方法进一步加工半导体晶圆,以形成半导体晶圆上方或半导体晶圆上的一或多个层。例如,可以使用例如本领域技术人员已知的微影技术,沉积和图案化一或多个电阻材料、导电材料或绝缘材料在半导体晶圆上。例如,材料可以包括一或多个导电材料(例如铝)、电阻材料(例如多晶硅)和绝缘材料(例如硅或氧化铪)。如本领域技术人员所理解,一旦形成这些层,这些层可以形成彼此之间的电性连接路径和隔离区域,以及一或多个布植层之间的电性连接路径和隔离区域。

66.在步骤120,半导体测试设备执行或通过例如控制器控制半导体测试设备执行在半导体晶圆上的测试程序,其中半导体晶圆具有半导体电路部分地形成于其上。例如,测试程序可以包括判定部分制造半导体晶圆的一或多个结构的一或多个几何、电性和物理特性。本文其他部分将进一步详细描述多个测试程序和其多个态样的实施例。

67.在一些实施例中,在执行测试程序之前,从半导体层生产设备移除具有部分形成的半导体电路的半导体晶圆,并且将半导体晶圆放置于半导体晶圆测试设备中,其中半导体晶圆测试设备是分开的并且从半导体层生产设备分离。在一些实施例中,并未从半导体层生产设备移除半导体晶圆,并且原位执行测试程序。

68.在步骤130,自动化测试设备或操作员使用测试设备判定半导体晶圆是否具有可接受的品质,以为了进一步制造半导体晶圆上的半导体电路而继续进一步加工。例如,如果部分制造的半导体晶圆的结构的全部几何、电性和物理特性经判定在可接受的范围内,部分制造的半导体晶圆可以视为通过测试。相对地,如果部分制造的半导体晶圆的结构的一或多个几何、电性和物理特性经判定在可接受的范围之外,部分制造的半导体晶圆可以视为未通过测试。

69.在一些实施例中,基于统计分析先前形成的层的母体(population)决定一或多个范围。例如,如果判定测量参数以多于任意约一个、两个、三个、四个或五个标准差偏离母体平均,可以判定半导体晶圆测试失败。在一些实施例中,可以使用另一个方法决定一或多个范围。

70.在步骤140,如果判定部分制造的半导体晶圆未通过测试,测试设备、制造设备或操作员从制造制程移除部分制造半导体晶圆。在一些实施例中,进一步分析和检查所移除

的半导体晶圆,以判定所移除的半导体晶圆的结构的一或多个额外的几何、电性和物理特性。在一些实施例中,做为对部分制造的半导体晶圆未通过测试的判定回应,检查及/或修改半导体晶圆制造设备的一或多个部分,例如通过变化制程特性(例如温度、压力、材料浓度和配方)。在一些实施例中,做为对部分制造的半导体晶圆未通过测试的判定回应,可以检查及/或修改一或多个其他制程特性。

71.结果而言,如果判定部分制造的半导体晶圆未通过测试,在执行随后的加工步骤以形成额外层之前即可发现半导体晶圆的不够好的品质。这些随后的加工步骤可能需要例如数周时间。因此,和在半导体电路完全形成之后测试半导体晶圆相比,上述方式可以提前数周采取改善制造品质的补救措施。此外,由于半导体晶圆具有不够好的品质,随后的加工步骤可能不具有价值。因此,原本用于随后加工步骤的制造资源可以用于形成另一个半导体晶圆上或另一个半导体晶圆中的有价值的半导体层。

72.在步骤150,如果判定部分制造的半导体晶圆通过测试,半导体制造设备执行一或多个随后的加工步骤以进一步形成半导体晶圆上的半导体电路。例如,可以另外形成一或多个布植层在半导体晶圆上或半导体晶圆中。在一些实施例中,可以通过添加和图案化半导体晶圆上方或半导体晶圆上的材料而形成一或多个额外层。例如,在测试之后,可以尚未执行后段制程或其他制程于半导体晶圆上。

73.在一些实施例中,在执行随后的制造步骤之前,从半导体晶圆测试设备移除具有部分形成的半导体电路的半导体晶圆,并且将半导体晶圆放置于半导体层生产设备中,其中半导体晶圆测试设备是分开的并且从半导体层生产设备分离。

74.本公开的发明者提供一种见解,在随着制造制程进行而沉积越来越多层在晶圆上之前,可以在制造制程的早期检查半导体晶圆的轮廓、层、其他特征或特性。传统上,在形成半导体晶圆上的电路之后,使用晶圆允收测试(wafer acceptance test,wat)测试半导体晶圆。例如,在后段制程期间,可以执行金属间(inter-metal,im)晶圆允收测试。也可以执行最终晶圆允收测试,而通过最终晶圆允收测试的各个晶圆才会运出。然而,这种传统晶圆允收测试的一个缺点是如果半导体晶圆具有线上(in-line)问题(可能涉及半导体晶圆的内部缺陷或可能发生在制程产线上),在晶圆允收测试才发现这个问题可能太晚,导致数天或甚至数周的延迟。

75.根据本公开,在制造制程期间,可以在线上获得半导体晶圆的轮廓(profile)。这样的轮廓可以示出进一步制造的半导体晶圆的不同区域的特性。这样的轮廓可以接着与预先决定的半导体晶圆标准进行比较,以判定半导体晶圆是否可能具有问题。

76.例如,根据本公开,可以使用扫描探针显微镜技术(scanning probe microscopy technique)对部分制造的半导体晶圆进行非破坏性剖面(non-destructively cross-sectioned)和检测。可以透过扫描获得部分制造的半导体晶圆的轮廓,并且此轮廓可以和技术计算机辅助设计(technology computer-aided design,tcad)模拟或表现数据库的数据进行比较(例如,和其他半导体晶圆的基线(baseline)进行比较)。

77.如另一个非限制性示例,可以使用扫描展延电阻显微镜(spreading resistance microscopy,ssrm)检测部分制造的半导体晶圆以获得轮廓。在这样的示例中,扫描展延电阻显微镜可以包括原子力显微镜(atomic force microscope,afm)模块,其可以执行晶圆的半导体晶圆截面上的扫描以测量包括探针所接触截面点的路径阻抗(impedance),或是

测量在原子力显微镜探针和截面上的样品区域之间的作用力。在示例实施方式中,可以在扫描展延电阻显微镜增加偏压(bias)以探测截面上不同面积/区域的电阻值。在这样的实施方式中,偏压可以在50mv至5000mv的范围中。

78.如上所述,透过获得半导体晶圆轮廓和图谱(mapping),如果部分制造的半导体晶圆视为不可接受的或具有一或多个可能导致最终产品中缺陷晶片的问题,可以在制造制程期间提早采取测量。例如,可以从制造制程彻底移除“有问题的(problematic)”部分制造的半导体晶圆。这可以改善制造制程的品质、效率、产量及/或任何其他要素。

79.根据一些实施例,图2绘示测试部分形成的半导体电路的方法200的流程图。方法200可以使用于例如上述的方法100的步骤120或步骤120的一部分。方法200可以做为参考方法100所述以外的其他制造制程的一部分。另外,方法100可以使用不同于方法200的方法来测试部分形成的半导体。

80.在步骤210,操作员或自动化测试机器或制造机器移除半导体晶圆,其中半导体晶圆具有例如半导体层生产设备所形成的部分形成的半导体电路于其上。例如,当移除部分加工的半导体晶圆时,部分加工的半导体晶圆可以不具有后段制程结构或其他制程执行于其上。

81.在步骤220,操作员或自动化测试机器或制造机器将半导体晶圆放置在半导体晶圆横切(cross-sectioning)设备中,其中半导体晶圆可以至少部分地剖面。在一些实施例中,半导体晶圆横切设备包括聚焦离子束(focused ion beam,fib)仪器。在一些实施例中,聚焦离子束仪器配置成将细小的离子束聚焦在半导体晶圆上的精确位置,从而烧蚀(ablate)精确位置的半导体晶圆并且暴露具有部分形成的半导体电路于其上的半导体晶圆的截面部分。在一些实施例中,半导体晶圆横切设备包括配置成将半导体晶圆剖面的其他装置。

82.在步骤230,半导体晶圆横切设备将至少部分的半导体晶圆剖面。由于进行剖面,暴露了即将测试的一或多个半导体层的一或多个部分。

83.在一些实施例中,切割出的截面从半导体晶圆实质上平坦的前表面延伸向半导体晶圆实质上平坦的背表面。在一些实施例中,切割出的截面从前表面实质上垂直地延伸。在一些实施例中,切割出的截面从前表面以角度约正负85度和90度之间、约正负60度和85度之间、约正负30度和60度之间和约正负10度和30度之间延伸。在一些实施例中,切割出的截面从前表面以另外的角度或角度范围延伸。

84.在一些实施例中,切割出的截面从半导体晶圆的前表面一路延伸到半导体晶圆的背表面。例如,如图9a中所示,剖面910的截面可以延伸穿过半导体基板,而使得切口(notch)部分的半导体基板暴露并且未由另一个层(例如层间介电质(interlayer dielectric,ild))所覆盖。之后可以执行后段制程于晶圆上。在一些实施例中,如图9b中所示,剖面920的截面可以从半导体晶圆的前表面只延伸至局部的半导体晶圆。例如,切割出的截面可以保留半导体基板的下部,并且在例如产品晶粒之间的测试线(testing line)中,使得之后的后段制程可以执行在整个晶圆上。

85.在一些实施例中,如图10中所绘示,剖面1010的截面可以从半导体晶圆1000的前表面上的第一点延伸至前表面上的第二点,其中第一点在周边边缘1050,第二点与最近的边缘1050分开。在一些实施例中,如图10中所绘示,剖面1020的截面可以从半导体晶圆1000

的前表面上的第一点延伸至前表面上的第二点,其中第一点在周边边缘1050,第二点在另一个周边边缘1050。在一些实施例中,如图10中所绘示,剖面1030的截面可以从半导体晶圆1000的前表面上的第一点延伸至半导体晶圆1000的前表面上的第二点,其中第一点与距离第一点最近的边缘1050分开,第二点与距离第二点最近的边缘1050分开。在一些实施例中,剖面具有长度在约1微米和约10微米之间。

86.在步骤240,使用特性测量系统定性截面所暴露的部分形成的半导体晶圆的一或多个层。例如,当定性部分加工的半导体晶圆时,可以尚未执行后段制程或其他制程于部分加工的半导体晶圆上。由于可以直接测试截面所暴露部分形成的半导体晶圆的层(例如在暴露层和测试设备之间不具有其他额外层),测试结果不受任何介入层干扰。例如,做为对操作员的输入及/或部分自动化软件驱动制程的回应,特性测量系统可以配置成执行轮廓定性,例如图11a中所绘示的扫描展延电阻显微镜或例如图11b中所绘示的扩散电阻分析(spreading resistance profiling,srp)定性方法,其可以使用例如原子力显微镜或相似的平台。在一些实施例中,特性测量系统可以配置成执行其他定性制程。应理解的是,此处提供的这些轮廓定性方法仅做为示例,因此不应解释成将本公开限制在这些轮廓定性方法。其他轮廓定性方法也涵括在本公开内。

87.在一些实施例中,使用扫描展延电阻显微镜可以具有优势的原因,至少是因为第一扫描展延电阻显微镜探针1110(参考图11a)方便直接接触垂直或实质上垂直暴露的测试部分(相对于水平的半导体晶圆表面),其中如本文其他内容所述,可以使用聚焦离子束制程方便暴露垂直或实质上垂直暴露的测试部分。另外,使用扫描展延电阻显微镜可以具有优势的原因,至少是因为可以方便定位扫描展延电阻显微镜系统的第二探针,从而可以与在测试部分中或接近测试部分的接触件电性连接,其中使用相同于形成电路接触件的半导体加工步骤形成接触件。

88.使用扫描展延电阻显微镜可以具有优势的原因,至少是因为探针接触可以具有尺寸在约8nm至约12nm的范围中。在一些实施例中,探针接触可以具有尺寸等于约10nm。使用扫描展延电阻显微镜可以具有优势的原因,至少是因为可以在约10微米和约2毫米之间的距离分离第一探针和第二探针。

89.在一些实施例中,使用扩散电阻分析具有优势的原因,至少是因为扩散电阻分析可以使用以例如约15微米的距离分离的两个探针(探针1120和探针1130)直接接触单一表面,其中单一表面可以例如是相对于半导体晶圆的顶表面的斜边,如图11b中所绘示。使用扩散电阻分析可以具有优势的原因,至少是因为探针接触可以具有尺寸在约1.8微米至约2.2微米的范围中。在一些实施例中,探针接触可以具有尺寸等于约2微米。

90.扫描探针显微镜是包括诊断半导体晶片的数种扫描技术的总称,例如导电式原子力显微镜(conducting atomic force microscopy)、扫描扩散电阻显微镜(scanning spreading resistance microscopy)、扫描电容显微镜和扫描穿隧显微镜(scanning tunneling microscopy)。根据本公开,在一些实施例中,在完全制造半导体晶圆上的电路之前执行扫描探针显微镜。

91.在一些实施例中,特性测量系统产生部分截面的二维图谱或表示图,其中二维图谱或表示图提供部分截面上的数个位置点中各者的成分指示。例如,特性测量系统可以产生指示图谱各点的电子电阻的二维图谱或表示图,其中图谱各点对应于截面上的位置点。

well,cpw)部分330和单元p阱部分350。在一些其他实施例,也包括其他层。

102.在一些实施例中,部分形成的半导体电路包括一或多个结构或层,其中当结合随后制造的其他结构或层(如果存在)时可以组成完整形成的半导体电路。在一些实施例中,完整形成的半导体电路包括例如具有一或多个晶体管和一或多个二极管的像素电路。在一些实施例中,完整形成的半导体电路包括具有数个晶体管和电性连接晶体管的导电元件的一或多个数字逻辑电路,以及具有例如数个晶体管、电阻器、电容器、二极管和电性连接晶体管、电阻器、电容器和二极管的导电元件的模拟(analog)电路。

103.可以根据图1的方法100的实施例制造半导体晶圆300。例如,在形成深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350之后,可以根据例如图2的方法200剖面和测试半导体晶圆300。例如,可以剖面深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350之中的一者或两者,并且测试一或多个参数。此外,一旦判定半导体晶圆300通过方法200的测试,可以执行随后的制造加工步骤以朝向形成其上的半导体电路而产生接续层。

104.根据一些实施例,图3b绘示部分半导体晶圆300的示意截面图,其中半导体晶圆300在经过测试程序之后具有接续层形成于部分形成的半导体电路上。绘示的实施例具有具体的结构形成在所绘示的层中。在一些实施例中,其他结构形成在所绘示的层中及/或其他层中。

105.如图中所绘示,形成在半导体晶圆300上的部分形成的半导体电路继续包括深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350。在此示例中,部分形成的半导体电路包括深n型嵌入式光电二极管(deep n-type pinned photodiode,dnppd)布植部分360和深n型嵌入式光电二极管布植部分380,以及n型嵌入式光电二极管(n-type pinned photodiode,nppd)布植部分370和n型嵌入式光电二极管布植部分390,做为半导体晶圆300通过测试的结果,上述部分形成在p型基板310上。在一些实施例中,也包括其他层。

106.在一些实施例中,制造剖面以形成图3a和图3b中所示的半导体晶圆300中的水平面,并且测试剖面的一或多个测试特征。

107.在一些实施例中,测试半导体晶圆300的一或多个测试特征,其中测试特征并未由切割操作所暴露。例如,在一些实施例中,可以测试半导体晶圆300的上表面上的测试特征,如图3a和图3b中所绘示。

108.根据一些实施例,图4a绘示部分半导体晶圆400的示意截面图,其中半导体晶圆400在经过测试程序之前具有部分形成的半导体电路形成于其上。绘示的实施例具有具体的结构形成在所绘示的层中。在一些实施例中,其他结构形成在所绘示的层中及/或其他层中。测试结构可以是例如具有布植深度在约1微米和约5微米之间。也可以使用其他深度。在一些实施例中,一或多个测试结构的布植深度在约1微米和约5微米之间,并且布植深度独立于相同布植层中的对应电路结构。在一些实施例中,一或多个测试结构的布植深度相同于或大约相同于相同布植层中的对应电路结构的布植深度。

109.如图中所绘示,形成在半导体晶圆400上的部分形成的半导体电路包括电路部分410,电路部分410具有形成在p型基板310上的深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350。另外,半导体晶圆400包括测试部分420,其中测试部分420与电路部分410分开,并且测试部分420包括深p阱测试结构460和单元p阱测试结构470。在一些

实施例中,电路部分410和测试部分420之中一者或两者也包括其他层。可以透过剖面制程暴露图4a中绘示的测试部分420的截面,例如参考图2的步骤230所述。

110.可以根据图1的方法100的实施例制造半导体晶圆400。例如,在制造制程期间可以同时形成深p阱部分320和深p阱部分340以及深p阱测试结构460。可以特定形成深p阱测试结构460做为测试结构。例如,可以按一定尺寸制造深p阱测试结构460,使得深p阱测试结构460具有在测试程序期间容易接触(access)的待测特征。例如,深p阱测试结构460可以比深p阱部分320和深p阱部分340宽。在一些实施例中,从图4a中所绘示的视图观察,深p阱测试结构460的宽度可以是至少1微米。例如,深p阱测试结构460的宽度可以在约1微米和约2微米之间。在一些实施例中,深p阱测试结构460可以与其他层分开,使得深p阱测试结构460实质上隔离,从而改善测试期间的接触。

111.相似地,在制造制程期间也可以同时形成单元p阱部分330和单元p阱部分350以及单元p阱测试结构470。可以特定形成单元p阱测试结构470做为测试结构。例如,可以按一定尺寸制造单元p阱测试结构470,使得单元p阱测试结构470具有在测试程序期间容易接触的待测特征。例如,单元p阱测试结构470可以比单元p阱部分330和单元p阱部分350宽。在一些实施例中,从图4a中所绘示的视图观察,单元p阱测试结构470的宽度可以是至少1微米。例如,单元p阱测试结构470的宽度可以在约1微米和约2微米之间。在一些实施例中,单元p阱测试结构470可以与其他层分开,使得单元p阱测试结构470实质上隔离,从而改善测试期间的接触。

112.因此,在一些实施例中,为了如本文所述测试制造制程的表现,形成做为测试结构的深p阱测试结构460和单元p阱测试结构470,并且不形成制程指标的功能性电路的一部分。例如,形成深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350以配合其他层执行例如信号处理操作的功能,而形成各个深p阱测试结构460和单元p阱测试结构470做为测试。

113.可以根据例如方法200的步骤230剖面测试部分420,以暴露深p阱测试结构460和单元p阱测试结构470。在一些实施例中,未对电路部分410进行剖面和测试。在剖面深p阱测试结构460和单元p阱测试结构470之中一者或两者之后,可以根据例如图2的方法200的步骤240和步骤250测试深p阱测试结构460和单元p阱测试结构470之中一者或两者。例如,可以测试深p阱测试结构460和单元p阱测试结构470之中一者或两者的一或多个参数。此外,一旦判定半导体晶圆400通过方法200的测试,可以执行随后的制造加工步骤以朝向形成其上的半导体电路而产生额外层。

114.根据一些实施例,图4b绘示部分半导体晶圆400的示意截面图,其中半导体晶圆400在经过测试程序之后具有额外层形成于部分形成的半导体电路上。如图中所绘示,形成在半导体晶圆400上的部分形成的半导体电路继续包括深p阱部分320和深p阱部分340以及单元p阱部分330和单元p阱部分350。半导体晶圆400也继续包括因剖面而暴露的测试部分420,尽管图4b中未绘示测试部分420。电路部分410另外包括深n型嵌入式光电二极管布植部分360和深n型嵌入式光电二极管布植部分380以及n型嵌入式光电二极管布植部分370和n型嵌入式光电二极管布植部分390,做为半导体晶圆400通过测试的结果,上述部分形成在p型基板310上。半导体晶圆400也包括测试部分430,其中测试部分430与测试部分420和电路部分410分开,并且测试部分430包括深n型嵌入式光电二极管测试结构490,在形成半导

体电路的更多层之前,深n型嵌入式光电二极管测试结构490可以用于进一步的测试。可以根据例如本文所述方法的一或多个态样测试深n型嵌入式光电二极管测试结构490。在一些实施例中,也可以包括其他层。可以透过剖面制程暴露图4b中绘示的测试部分430的截面,例如参考图2的步骤230所述。

115.在一些实施例中,第一剖面暴露深p阱测试结构460和单元p阱测试结构470,以及第二剖面暴露深n型嵌入式光电二极管测试结构490。在一些实施例中,第一剖面和第二剖面未相交。在一些实施例中,第一剖面未暴露深n型嵌入式光电二极管测试结构490。在一些实施例中,第二剖面未暴露深p阱测试结构460或单元p阱测试结构470。

116.在一些实施例中,制造剖面以形成图4a和图4b中所示的测试部分420中的水平面,并且测试测试部分420的一或多个测试特征。

117.在一些实施例中,测试测试部分420的一或多个测试特征,其中测试特征并未由切割操作所暴露。例如,可以测试测试部分420及/或测试部分430的上表面上的测试特征,如图4a和图4b中所绘示。

118.根据一些实施例,图5绘示部分半导体晶圆500的示意截面图,其中半导体晶圆500具有部分形成的测试电路510。测试电路510可以具有特征相似于或相同于本文所述半导体晶圆的电路部分中形成的结构,例如参考图4a所述的电路部分410。在一些实施例中,测试电路510可以具有特征相似于或相同于本文所述半导体晶圆的测试部分中形成的结构,例如参考图4a所述的测试部分420。在一些实施例中,测试电路510中也可以包括其他层。可以透过剖面制程暴露图5中绘示的部分形成的测试电路510的截面,例如参考图2的步骤230所述。

119.半导体晶圆500也包括基板接触件520。在测试程序的一些实施例中,使用连接至基板310的电性连接以提供测试设备的第一探针的导电途径。使用测试设备的第二探针接触沿着暴露截面的多个位置点。测试设备产生横跨第一探针和第二探针的电压,并且测量第一探针和第二探针之间的导电电流。因此,可以测量或计算阻抗并且和第二探针的各个接触位置点产生关联,以形成暴露截面的二维图谱或其他表示图。

120.可以根据图1的方法100的实施例制造半导体晶圆500。可以根据例如方法200的步骤230剖面测试电路510,以暴露测试电路510的测试特征。在一些实施例中,半导体晶圆500另外包括未剖面的电路部分(未示出)。在对测试电路510进行剖面之后,可以根据例如图2的方法200的步骤240和步骤250测试测试电路510。在测试测试电路510时,基板接触件520可以提供测试设备的探针的导电途径,如上所述。例如,可以测试测试电路510的一或多个参数。此外,一旦判定半导体晶圆500通过方法200的测试,可以执行随后的制造加工步骤以朝向形成其上的半导体电路而产生额外层。

121.基板接触件520可以包括一或多个导电布植层。在一些实施例中,基板接触件520另外包括导电金属化层(metallization layer)。在一些实施例中,和形成在半导体晶圆500上或半导体晶圆500中的一或多个电路结构相比,可以使用相同的半导体制造设备以及相同时间部分或整体形成基板接触件520。在一些实施例中,使用聚焦离子束制程部分或整体形成基板接触件520。

122.半导体晶圆500也包括环绕基板接触件520和测试电路510的隔离结构530。隔离结构530配置成提供电性隔离至基板接触件520和测试电路510,从而在测试期间减少来自测

试电路510之外的结构的电子干扰,或者电子干扰对测试结果不造成影响。例如,隔离结构530减少自由电子或空穴,或者自由电子或空穴因为隔离结构530而对测试结果不造成影响。

123.可以使用例如任何本领域技术人员已知的隔离结构形成隔离结构530。例如,隔离结构530可以包括一或多个掺杂物、氧化物或沟槽。在一些实施例中,隔离结构530是非导电的。在一些实施例中,隔离结构530是导电的,并且在测试程序期间接地或导电至一些其他直流电压。

124.根据一些实施例,图6绘示部分半导体晶圆600的示意图,其中半导体晶圆600具有部分形成的测试电路510。半导体晶圆600也包括基板接触件620。可以根据图1的方法100的实施例制造半导体晶圆600。可以透过剖面制程暴露图6中绘示的部分形成的测试电路510的截面,例如参考图2的步骤230所述。

125.基板接触件620可以包括一或多个导电布植层。在一些实施例中,基板接触件620另外包括导电金属化层。在一些实施例中,基板接触件620从半导体晶圆600的前表面或顶表面一路延伸至半导体晶圆600的相对背表面或底表面,其中基板接触件620未由层间介电质所覆盖。在一些实施例中,和形成在半导体晶圆600上或半导体晶圆600中的一或多个电路结构相比,可以使用相同的半导体制造设备以及相同时间部分或整体形成基板接触件620。在一些实施例中,使用聚焦离子束制程部分或整体形成基板接触件620。

126.在一些实施例中,基板接触件620直接接触测试电路510的一或多个层或结构。因此,在测试程序期间,测量的阻抗主要或实质上整体基于基板接触件620和测试电路510的一或多个层或结构的阻抗。

127.半导体晶圆600也包括环绕基板接触件620和测试电路510的隔离结构530。隔离结构530配置成提供电性隔离至基板接触件620和测试电路510,例如本文其他内容所述。

128.根据一些实施例,图7绘示半导体晶圆700的示意截面图。半导体晶圆700包括电路区域710和测试部分721、测试部分722、测试部分723、测试部分724和测试部分725。

129.电路区域710包括部分或完整形成的数个半导体电路,各个半导体电路形成或部分地形成功能性电子电路,例如具有特征相似于或相同于本文所述半导体晶圆的电路部分。在完成之后,半导体电路可以包括电性连接衬垫或端点,其可以由例如测试设备所接触以在半导体电路上执行电子操作测试。半导体电路可以与另一个半导体电路分开,从而可以使用切割操作分离半导体电路以形成数个半导体电路晶粒,各个半导体电路晶粒具有一或多个功能性半导体电路形成于其上。在一些实施例中,本文所述的方法包括测试半导体电路。在一些实施例中,本文所述的方法包括使用例如切割操作物理性彼此分离半导体电路。在一些实施例中,本文所述的方法包括将半导体电路晶粒封装进集成电路封装中。

130.各个测试部分721、测试部分722、测试部分723、测试部分724和测试部分725可以具有特征相似于或相同于本文所述半导体晶圆的测试部分。各个测试部分721、测试部分722、测试部分723、测试部分724和测试部分725可以具有特征相似于或相同于本文所述半导体晶圆的电路部分或形成在半导体晶圆上的其他产品晶粒。在一些实施例中,各个测试部分721、测试部分722、测试部分723、测试部分724和测试部分725具有测试结构和特征相似于或相同于测试部分721、测试部分722、测试部分723、测试部分724和测试部分725之中另一者。在一些实施例中,各个测试部分721、测试部分722、测试部分723、测试部分724和测

试部分725具有一或多个测试结构和特征不同于测试部分721、测试部分722、测试部分723、测试部分724和测试部分725之中的其他者。在一些实施例中,测试部分721、测试部分722、测试部分723、测试部分724和测试部分725可以设置在切口中或测试线中。在一些实施例中,测试部分721、测试部分722、测试部分723、测试部分724和测试部分725可以具有约1微米至5微米的深度,而产品装置的布植面积具有约1微米至10微米的侧宽度和约10微米至2毫米的长度。

131.在一些实施例中,在半导体晶圆700中或半导体晶圆700上形成一或多个第一层之后,并且在半导体晶圆700中或半导体晶圆700上形成一或多个第二层之前,对测试部分721、测试部分722、测试部分723、测试部分724和测试部分725的第一子集进行剖面和测试,以及在半导体晶圆700中或半导体晶圆700上形成一或多个第二层之后,对测试部分721、测试部分722、测试部分723、测试部分724和测试部分725的第二(不同的)子集进行剖面和测试。

132.根据一些实施例,图8绘示半导体电路制造制程方法800的示意图。制程方法800包括多个形成层的步骤802至步骤846,其中各个步骤可以包括数个步骤以形成一或多个半导体层。可以使用制程方法800的多个步骤,以形成例如半导体晶圆上的电路部分和测试部分的半导体层,如图3a、图3b、图4a、图4b、图5和图6中所绘示。在一些实施例中,使用制程方法800的步骤形成未绘示的其他结构。在一些实施例中,制程方法800包括本文未具体描述的其他步骤以在半导体晶圆上形成电路部分和测试部分的半导体层。在一些实施例中,省略一或多个所述的步骤。

133.在一些实施例中,图1的方法100和制造制程方法800一起使用。例如,在方法100的步骤110执行的加工步骤可以包括半导体电路制造制程方法800的一或多个形成多个层的步骤802至步骤844。在一些实施例中,在方法100的步骤150执行的加工步骤可以包括半导体电路制造制程方法800的一或多个形成多个层的步骤804至步骤846。

134.在一些实施例中,方法100与省略一或多个步骤802至步骤848及/或添加一或多个额外步骤的其他制造制程一起使用。在一些实施例中,省略方法100的一或多个步骤及/或在方法100添加一或多个步骤的方法和制造制程方法800一起使用。这些组合和变化全部在本公开考量的范围内。

135.在步骤802,执行氧化物产生步骤以在半导体晶圆的区域中产生一或多个氧化物层(oxide,od),其中这些区域随后不会接受主动区布植,例如源极和漏极扩散区域。在一些实施例中,也使用步骤802以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤802的结果或表现。使用本领域技术人员已知的技术执行步骤802。

136.在一些实施例中,在步骤802之后和在步骤804之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

137.在步骤804,执行场阱布植(field well implant,fld)以至少修复先前造成的任何布植损坏,以及减少或删减隔离结构530中的缺陷以减少或删减缺陷造成的隔离结构530中的漏电流。在一些实施例中,也使用步骤804以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤804的结果或表现。使用本领域技术人员已知的技术执行步骤804。

type pinned photodiode,nppd)。在一些实施例中,也使用步骤822以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤822的结果或表现。使用本领域技术人员已知的技术执行步骤822。

152.在一些实施例中,在步骤822之后和在步骤824之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

153.在步骤824,移除多晶硬遮罩(poly hard mask remove,pohm rm),例如定义多晶下布植(under poly implant)和后布植(post implant)区域的硬遮罩。在一些实施例中,也使用步骤824以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤824的结果或表现。使用本领域技术人员已知的技术执行步骤824。

154.在一些实施例中,在步骤824之后和在步骤826之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

155.在步骤826,执行布植步骤以产生一或多个轻掺杂的漏极层(logic lightly doped drain,logic ldd)。在一些实施例中,也使用步骤826以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤826的结果或表现。使用本领域技术人员已知的技术执行步骤826。

156.在一些实施例中,在步骤826之后和在步骤830之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

157.在步骤830,执行布植步骤以产生一或多个嵌入式光电二极管的p型布植层(p-type pinned photodiode,pppd)。在一些实施例中,也使用步骤830以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤830的结果或表现。使用本领域技术人员已知的技术执行步骤830。

158.在一些实施例中,在步骤830之后和在步骤832之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

159.在步骤832,通过沉积氧化物膜定义间隔物(spacer,sw)以保护多晶硅或类似者。在一些实施例中,也使用步骤832以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤832的结果或表现。使用本领域技术人员已知的技术执行步骤832。

160.在一些实施例中,在步骤832之后和在步骤836之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

161.在步骤836,执行布植步骤以产生一或多个n型晶体管的源极和漏极的n型布植层(n implant layer for source and drain,n+s/d)。在一些实施例中,也使用步骤836以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤836的结果或表现。使用本领域技术人员已知的技术执行步骤836。

162.在一些实施例中,在步骤836之后和在步骤838之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

163.在步骤838,执行布植步骤以产生一或多个p型晶体管的源极和漏极的p型布植层(p implant layer for source and drain,p+s/d)。在一些实施例中,也使用步骤838以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术

测试的特征,以测试步骤838的结果或表现。使用本领域技术人员已知的技术执行步骤838。

164.在一些实施例中,在步骤838之后和在步骤840之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

165.在步骤840,执行布植步骤以产生一或多个嵌入式光电二极管的p型布植层(p-type pinned photodiode,pppd)。在一些实施例中,也使用步骤840以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤840的结果或表现。使用本领域技术人员已知的技术执行步骤840。

166.在一些实施例中,在步骤840之后和在步骤842之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

167.在步骤842,执行沉积步骤以产生一或多个光阻保护层,例如一或多个光阻保护氧化物层(resist protection oxide layer,rpo)。在一些实施例中,也使用步骤842以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤842的结果或表现。使用本领域技术人员已知的技术执行步骤842。

168.在一些实施例中,在步骤842之后和在步骤844之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

169.在步骤844,执行沉积步骤以产生一或多个介电层(例如层间介电质(interlayer dielectric,ild))。在一些实施例中,也使用步骤844以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤844的结果或表现。使用本领域技术人员已知的技术执行步骤844。

170.在一些实施例中,在步骤844之后和在步骤846之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

171.在步骤846,为形成后段制程金属接触件定义接触件(contact,ct)。在一些实施例中,也使用步骤846以产生可以位于半导体晶圆的测试部分中的测试结构。测试结构可以包括能使用本文所述技术测试的特征,以测试步骤846的结果或表现。使用本领域技术人员已知的技术执行步骤846。

172.在一些实施例中,在步骤846之后和在另一个层的产生步骤(未示出)之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

173.在一些实施例中,在未描述的第一层产生步骤之后以及在未描述的第二层产生步骤之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

174.在一些实施例中,在未描述的第一层产生步骤之后以及在已描述的第二层产生步骤之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

175.在一些实施例中,在已描述的第一层产生步骤之后以及在未描述的第二层产生步骤之前,方法800包括相似于或相同于上方参考图1的步骤120、步骤130和步骤140所述的特征或行动。

176.在步骤848,执行晶圆允收测试(wafer acceptance test,wat)程序,例如本文其他内容所述的晶圆允收测试。

177.如上文中进一步详细所述,半导体制造制程包括形成多个独立且不同的层。这些

层可以包括例如一或多个结晶半导体基板(其中部分的基板各个掺杂不同的掺杂剂种类或掺杂剂种类浓度,如本领域技术人员所理解)、绝缘体(例如氧化物)、导体(例如铝)和电阻器(例如多晶硅)。通过特定的半导体制造制程形成各层,以及各层的多个特性因为例如温度、压力、时长、配方和数个其他制造和环境条件的变化而具有一些变异,如本领域技术人员所理解。有时这些变异导致形成的一或多个层具有不够好的品质,使得例如所产生的晶圆无法使用或具有不够好的品质,或者使得例如所产生的晶圆具有的晶粒数量少于可用电路或品质足够好的电路中可接受的晶粒数量。

178.在本文所述的多个实施例中,描述测试一或多个层具有足够好的品质的制造方法。测试发生在形成一或多个第一层之后以及在形成一或多个额外层之前,其中第一层和一或多个额外层两者集体形成在制造制程期间制造的电路。在测试制程期间,测试一或多个第一层。在一些实施例中,若发现测试层具有足够好的品质,进一步加工半导体晶圆,使得额外层形成在半导体晶圆中及/或半导体晶圆上。在一些实施例中,若发现测试层具有不够好的品质,从制造制程移除半导体晶圆。

179.本公开的一个态样是制造半导体晶圆的方法。方法包括将半导体晶圆暴露至一或多个掺杂剂种类以形成半导体晶圆上的一或多个第一布植层、测试所形成的一或多个第一布植层的一或多个几何参数值、在测试一或多个几何参数值之后有条件地将半导体晶圆暴露至一或多个掺杂剂种类以形成半导体晶圆上的一或多个额外布植层、在形成一或多个额外布植层之后有条件地形成半导体晶圆上的一或多个额外电路层以形成半导体晶圆上的多个功能性电子电路,以及使用晶圆允收测试步骤有条件地测试半导体晶圆。

180.在一些实施例中,测试所形成的一或多个第一布植层的一或多个几何参数值包括判定一或多个几何参数值,以及比较各个参数值与极限值。

181.在一些实施例中,形成半导体晶圆上的一或多个第一布植层包括形成包括一或多个第一布植层的电路部分、形成包括一或多个第一布植层的测试部分,以及测试所形成的一或多个第一布植层的一或多个几何参数值包括测试测试部分的一或多个第一布植层。

182.在一些实施例中,形成半导体晶圆上的一或多个第一布植层包括形成包括一或多个第一布植层的电路部分,以及形成包括一或多个第一布植层的测试部分,其中未测试电路部分的一或多个第一布植层。

183.在一些实施例中,一或多个第一布植层和一或多个额外的布植层配合形成至少局部的配置成处理电子信号的电子电路。

184.在一些实施例中,若一或多个几何参数值的测试判定一或多个几何参数值各个落入一或多个规定极限值内,形成半导体晶圆上的一或多个额外布植层,以及若一或多个几何参数值的测试判定一或多个几何参数值的至少一者各个落于一或多个规定极限值之外,不形成半导体晶圆上的一或多个额外布植层。

185.本公开的另一个态样是半导体晶圆,包括形成电路部分和第一测试部分的一或多个第一布植层,电路部分形成至少部分形成的半导体电路,其中第一测试部分中的第一剖面暴露第一测试部分的一或多个第一布植层,以及进一步形成电路部分和第二测试部分的一或多个第二布植层,其中第二测试部分中的第二剖面暴露第二测试部分的一或多个第二布植层,其中第一测试部分和第二测试部分分开,以及其中第一剖面和第二剖面不相交。

186.在一些实施例中,第一剖面未暴露一或多个第二布植层的任何一者。

187.在一些实施例中,第二剖面未暴露一或多个第一布植层的任何一者。

188.在一些实施例中,形成第一测试部分的一或多个第一布植层具有由第一剖面暴露的尺寸大于电路截面中形成电路部分的一或多个第一布植层的尺寸,其中电路截面和第一剖面以相同的角度相交半导体晶圆定义的一个平面。

189.在一些实施例中,隔离结构环绕各个第一测试部分和第二测试部分。

190.本公开的另一个态样是制造半导体晶圆的方法,方法包括将半导体晶圆暴露至一或多个掺杂剂种类以形成半导体晶圆上的一或多个第一布植层、切割半导体晶圆以暴露一或多个第一布植层,以及测试一或多个第一布植层的一或多个几何参数值,其中测试包括使用探针接触所暴露的一或多个第一布植层。方法也包括,在测试一或多个几何参数值之后,有条件地形成半导体晶圆上的一或多个金属化层以电性连接半导体晶圆上的多个功能性电子电路,和使用晶圆允收测试步骤有条件地测试半导体晶圆。

191.在一些实施例中,测试包括使用探针直接接触所暴露的一或多个第一布植层。

192.在一些实施例中,一或多个几何参数值包括所形成的一或多个第一布植层的至少一个尺寸。

193.在一些实施例中,测试所形成的一或多个第一布植层的一或多个几何参数值包括判定一或多个几何参数值,以及比较各个参数值与极限值。

194.在一些实施例中,方法进一步包括,在形成半导体晶圆上的一或多个金属化层之后,测试所形成的一或多个金属化层的一或多个额外几何参数值。

195.在一些实施例中,形成半导体晶圆上的一或多个第一布植层包括形成包括一或多个第一布植层的电路部分以及形成包括一或多个第一布植层的测试部分,其中测试所形成的一或多个第一布植层的一或多个几何参数值包括测试测试部分的一或多个第一布植层。

196.在一些实施例中,形成半导体晶圆上的一或多个第一布植层包括形成包括一或多个第一布植层的电路部分以及形成包括一或多个第一布植层的测试部分,其中未测试电路部分的一或多个第一布植层。

197.在一些实施例中,一或多个第一布植层和一或多个金属化层配合形成至少局部的配置成处理电子信号的电子电路。

198.在一些实施例中,若一或多个几何参数值的测试判定一或多个几何参数值各个落在一或多个规定极限值内,形成半导体晶圆上的一或多个金属化层,以及若一或多个几何参数值的测试判定一或多个几何参数值的至少一者各个落于一或多个规定极限值之外,不形成半导体晶圆上的一或多个金属化层。

199.在上述内文中和权利要求中,例如“至少一者”或“一或多个”的术语可以出现在元件或特征的连结清单之前。述与“及/或”也可以出现在两个或更多元件或特征的清单中。除非使用这些用语的内文中另外隐含或明确抵触,这样的用语是意图独自表示清单中的任何元件或特征,或者任何列出的元件或特征与任何其他列出的元件或特征的组合。例如,用语“a和b的至少一者”、“一或多个a和b”以及“a及/或b”各自意图表示“a自身、b自身或a和b一起”。相似的阐述也可以表示包括三个或更多个物件的清单。例如,用语“a、b和c的至少一者”、“一或多个a、b和c”以及“a、b及/或c”各自意图表示“a自身、b自身、c自身、a和b一起、a和c一起、b和c一起或者a、b和c一起”。在上文中和权利要求中使用术语“基于”是意图表示“至少一部分基于”,因此也允许未列出的特征或元件。

200.前面概述一些实施例的特征,使得本领域技术人员可更好地理解本公开的观点。本领域技术人员应该理解,他们可以容易地使用本公开作为设计或修改其他制程和结构的基础,以实现相同的目的和/或实现与本文介绍的实施例相同的优点。本领域技术人员还应该理解,这样的等同构造不脱离本公开的精神和范围,并且在不脱离本公开的精神和范围的情况下,可以进行各种改变、替换和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1