一种发光二极管及制作方法与流程

1.本发明涉及led技术领域,特别涉及一种发光二极管及制作方法。

背景技术:

2.发光二极管(light emitting diode,简称:led)是一种能发光的半导体电子元件,由于其体积小、亮度高、能耗低等特点,吸引了越来越多研究者的注意。

3.传统的gaas基发光二极管中通常含有键合层,用于与透明衬底蓝宝石键合,当前主流的键合层材料为氧化硅、氮化硅、氧化铝等氧化物,当使用以上的氧化物作为键合层材料去与透明衬底蓝宝石键合时,在led芯片制造过程中,由于gaas基发光二极管中的p-gap窗口层粗化形貌难以控制,较难得到理想的金字塔形,导致氧化物与p-gap窗口层的接触面存在大量的空洞,经后续高温、高压的芯片制程后,氧化物与p-gap窗口层的接触面极易出现裂纹、缝隙。

4.另外,采用cmp抛光较难得到均匀性高、粗糙度低,洁净无损伤的氧化物表面,这将导致氧化物与透明衬底蓝宝石键合时,接触面出现大量未键合上的空洞,极易出现蓝宝石键合脱层,甚至键合不上的问题。

技术实现要素:

5.基于此,本发明的目的是提供一种发光二极管及制作方法,旨在解决现有技术中,氧化物键合层与蓝宝石之间较难形成键合以及键合后结合力弱的问题。

6.根据本发明实施例当中的一种发光二极管,其特征在于,包括外延层衬底、外延层、薄膜层和蓝宝石衬底,所述外延层外延生长在所述外延层衬底上,所述薄膜层沉积于所述外延层上,所述蓝宝石衬底贴合于所述薄膜层上,其中,所述薄膜层包括ito薄膜和金属薄膜,所述ito薄膜沉积于所述外延层上,所述金属薄膜中至少包括两种不相同的金属层,所述金属层依次沉积于所述ito薄膜上,所述蓝宝石衬底上附着有所述金属薄膜中远离所述ito薄膜一端相同金属材料的所述金属层,所述蓝宝石衬底上附着有所述金属层的一侧贴合于所述金属薄膜上。

7.优选地,所述外延层衬底为gaas衬底,所述外延层包括buffer层、gainp截止层、n-gaas层、n-alinp层、mqw层、p-alinp层、p-gap光窗口层,其中,所述buffer层、所述gainp截止层、所述n-gaas层、所述n-alinp层、所述mqw层、所述p-alinp层、所述p-gap光窗口层依次外延生长在所述gaas衬底上。

8.优选地,所述ito薄膜的厚度由gaas基flip-chip芯片的波长决定,所述厚度的计算公式为:

9.d=m(1λ/4n)

10.其中,d为ito薄膜目标厚度,m为增透系数,λ为所述gaas基flip-chip芯片的波长,n为ito薄膜的折射率。

11.优选地,所述金属薄膜的厚度不超过15nm。

12.根据本发明实施例当中的一种发光二极管的制作方法,用于制备上述的发光二极管,发光二极管的制作方法包括:

13.提供一生长所需的外延层衬底;

14.在所述外延层衬底上生长外延层;

15.将薄膜层沉积于所述外延层上;

16.在蓝宝石衬底上蒸镀金属层;

17.将所述蓝宝石衬底带有所述金属层的一侧贴合于所述薄膜层上;

18.其中,所述薄膜层包括ito薄膜和金属薄膜,所述ito薄膜沉积于所述外延层上,所述金属薄膜中至少包括两种不相同的金属层,所述金属层依次沉积于所述ito薄膜上,所述蓝宝石衬底上附着有所述金属薄膜中远离所述ito薄膜一端相同金属材料的所述金属层,所述蓝宝石衬底上附着有所述金属层的一侧贴合于所述金属薄膜上。

19.优选地,所述发光二极管的制作方法还包括:

20.所述外延层衬底为gaas衬底,所述外延层包括buffer层、gainp截止层、n-gaas层、n-alinp层、mqw层、p-alinp层、p-gap光窗口层,其中,所述buffer层、所述gainp截止层、所述n-gaas层、所述n-alinp层、所述mqw层、所述p-alinp层、所述p-gap光窗口层依次外延生长在所述gaas衬底上。

21.优选地,所述将所述蓝宝石衬底带有所述金属层的一侧贴合于所述薄膜层上的步骤之后还包括:

22.去除所述gaas衬底、所述buffer层与所述gainp截止层,使所述n-gaas层裸露;

23.从所述n-gaas层端进行刻蚀,蚀刻至所述p-gap光窗口层;

24.在所述p-gap光窗口层制作p电极,在所述n-gaas层上制作n电极,并分别形成欧姆接触;

25.整体沉积钝化保护层;

26.将所述p电极、所述n电极上的所述钝化保护层蚀刻出孔洞;

27.在所述p电极、所述n电极上方的所述孔洞内填充焊盘电极。

28.优选地,所述ito薄膜为in2o3与sno2的混合物,所述in2o3为所述ito薄膜组分的95%,所述sno2为所述ito薄膜组分的5%。

29.优选地,所述将薄膜层沉积于所述外延层上的步骤具体包括:

30.将所述ito薄膜进行蒸镀,所述蒸镀的方式为eb电子束蒸发的方式,所述蒸镀条件为蒸镀温度250℃-350℃,真空度为1e-6-8e-6torr,蒸镀速率为0.35a/s-1a/s。

31.优选地,所述将薄膜层沉积于所述外延层上的步骤具体还包括:

32.将所述金属薄膜进行蒸镀,所述蒸镀的方式为eb电子束蒸发的方式,所述蒸镀条件为冷蒸,真空1e-4-1e-3pa,蒸镀速率0.5a/s-2a/s。

33.与现有技术相比:通过在外延层衬底上依次生成外延层、ito薄膜、金属薄膜和蓝宝石衬底,其中,薄膜层包括ito薄膜和金属薄膜,ito薄膜沉积于外延层上,金属薄膜中至少包括两种不相同的金属层,金属层依次沉积于ito薄膜上,且蓝宝石衬底上附着有金属薄膜中远离ito薄膜一端相同金属材料的金属层,最终将蓝宝石衬底上附着有所述金属层的一侧贴合于所述金属薄膜上,由于金属互融能力强,同时,互融后的界面的结合力很强,所以有效解决了氧化物键合层与蓝宝石之间较难形成键合以及键合后结合力弱的问题。

附图说明

34.图1为本发明实施例一当中的发光二极管的结构示意图;

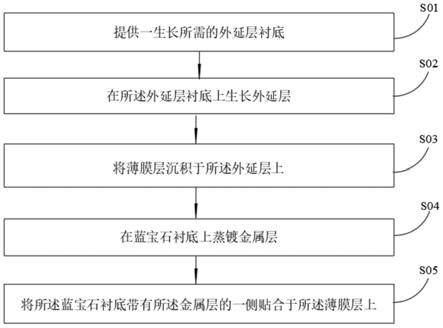

35.图2为本发明实施例二当中的发光二极管的制作方法的流程图;

36.图3为本发明实施例三提出的发光二极管的制作方法的流程图;

37.图4为为本发明实施例三提出的发光二极管的结构示意图。

38.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

39.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的若干实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

40.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

41.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

42.实施例一

43.请参阅图1,所示为本发明实施例一中的发光二极管的结构示意图,包括外延层衬底、外延生长在外延层衬底上的外延层、沉积于外延层上的薄膜层和与薄膜层贴合的蓝宝石衬底。

44.在本实施例当中,外延层衬底为gaas衬底1,外延层包括buffer层2、gainp截止层3、n-gaas层4、n-alinp层5、mqw层6、p-alinp层7、p-gap光窗口层8,其中,buffer层1、gainp截止层2、n-gaas层3、n-alinp层4、mqw层5、p-alinp层6、p-gap光窗口层7依次外延生长在gaas衬底1上。

45.具体的,薄膜层包括ito薄膜9和金属薄膜,ito薄膜9为in2o3和sno2的混合物,需要说明的是,ito薄膜的厚度由gaas基flip-chip芯片的波长决定,所述厚度的计算公式为:

46.d=m(1λ/4n)

47.其中,d为ito薄膜9目标厚度,m为增透系数,可以理解的,m取奇数时,例如为1、3、5等,可以达到增透的效果,具体m的取值可根据ito薄膜9需求厚度进行设定,λ为所述gaas基flip-chip芯片的波长,n为ito薄膜9的折射率。

48.在本实施例当中,金属薄膜包括ni层10、cu层11和ag层12,其中,ito薄膜9沉积于外延层上,ito薄膜9和蓝宝石衬底13之间依次沉积ni层10、cu层11和ag层12,蓝宝石衬底13贴合于ag层12上,可以理解的,ni层10、cu层11和ag层12各层厚度的累加不超过15nm。

49.示例而非限定,在本实施例一些较佳实施例当中,薄膜层中金属薄膜中可替代的组合金属材料为ni、cu和au,al、cu和au,al、cu和ag,ni和au,al和ag,可以理解的,当金属薄膜中远离ito薄膜9沉积的金属层为au层时,蓝宝石衬底13的一侧上也应附着有au金属层。

50.实施例二

51.请参阅图2,所示为本发明实施例二提出的一种发光二极管的制作方法,用于制备上述实施例一当中的发光二极管,所述方法具体包括步骤s01至步骤s05,其中:

52.步骤s01,提供一生长所需的外延层衬底。

53.在本实施例当中,外延层衬底为gaas衬底。

54.步骤s02,在所述外延层衬底上生长外延层。

55.其中,所述外延层包括buffer层、gainp截止层、n-gaas层、n-alinp层、mqw层、p-alinp层、p-gap光窗口层,需要说明的是,buffer层、gainp截止层、n-gaas层、n-alinp层、mqw层、p-alinp层、p-gap光窗口层依次外延生长在gaas衬底上。

56.步骤s03,将薄膜层沉积于所述外延层上。

57.具体的,薄膜层包括ito薄膜和金属薄膜,ito薄膜为in2o3和sno2的混合物,需要说明的是,in2o3占ito薄膜组分的95%,sno2占ito薄膜组分的5%,将ito薄膜沉积于p-gap光窗口层上的方法为蒸镀法,目前ito蒸镀方式有eb电子束蒸发、sputtering磁控溅射、rpd反应等离子体沉积等,在本实施例当中,使用的是eb电子束蒸发的方式,蒸发后的ito薄膜的透过率要大于99%,蒸镀温度为250℃-350℃,真空度为1e-6-8e-6torr,蒸镀速率为0.35a/s-1a/s。

58.在本实施例当中,金属薄膜包括ni、cu和ag,其中,ni、cu和ag依次沉积于ito薄膜上,需要说明的是,将金属薄膜沉积于ito薄膜上的方法为蒸镀法,在本实施例当中,使用的是eb电子束蒸发的方式,该方式的条件为冷蒸,真空1e-4-1e-3pa,蒸镀速率0.5a/s-2a/s,一次蒸镀完成,膜层蒸镀完成前不可接触大气,使用eb电子束蒸发的方式可以获得表面较为光滑的金属薄膜。

59.可以理解的,ni、cu和ag可蒸镀不同的厚度,三种金属的厚度之和不超过15nm,因为随着金属厚度的增加,粗糙度增加,其吸光系数会随之增加,导致透过率会大幅度的下降。

60.示例而非限定,在本实施例一些较佳实施例当中,ni占金属薄膜组分的8%~10%,例如为8%、9%、10%等;cu占金属薄膜组分的18%~20%,例如为18%、9%、20%等;ag占金属薄膜组分的70%~74%,例如为70%、70%、72%、73%、74%等。

61.步骤s04,在蓝宝石衬底上蒸镀金属层。

62.具体的,在蓝宝石衬底贴合于金属薄膜层前,需要先在蓝宝石衬底上蒸镀一层与金属薄膜中远离ito薄膜一端相同金属材料的金属层,便于融合,在本实施例当中,ni、cu和ag依次沉积于ito薄膜上,可以理解的,在蓝宝石衬底上需要蒸镀ag层,该蒸镀方式采用eb电子束蒸发的方式,冷蒸,当蓝宝石衬底上蒸镀的ag层与金属薄膜中的ag层融合后,ni、cu和ag三层金属层的总厚度不超过15nm,ag占金属薄膜组分的70%~74%。

63.步骤s05,将所述蓝宝石衬底带有所述金属层的一侧贴合于所述薄膜层上。

64.在本实施例当中,通过高温高压的方式将蒸镀上ni/cu/ag的外延层和蒸镀上ag层蓝宝石衬底贴合到一起,由于金属互融结合的界面的结合力要大于二氧化硅与蓝宝石直接的结合力,从而更容易获得高良率的键合效果。

65.综上,本发明实施例当中的发光二极管及制作方法,通过在外延层衬底上依次生成外延层、ito薄膜、金属薄膜和蓝宝石衬底,其中,薄膜层包括ito薄膜和金属薄膜,ito薄

膜沉积于外延层上,金属薄膜中至少包括两种不相同的金属层,金属层依次沉积于ito薄膜上,且蓝宝石衬底上附着有金属薄膜中远离ito薄膜一端相同金属材料的金属层,最终将蓝宝石衬底上附着有所述金属层的一侧贴合于所述金属薄膜上,由于金属互融能力强,同时,互融后的界面的结合力很强,所以有效解决了氧化物键合层与蓝宝石之间较难形成键合以及键合后结合力弱的问题。

66.实施例三

67.请参阅图3和图4,图3所示为本发明实施例三提出的一种发光二极管的制作方法,图4所示为本发明实施例三提出的一种发光二极管的结构示意图,所述方法用于制备上述实施例一当中的发光二极管,所述方法具体包括步骤s10至步骤s20。

68.步骤s10,提供一生长所需的外延层衬底。

69.步骤s11,在所述外延层衬底上生长外延层。

70.步骤s12,将薄膜层沉积于所述外延层上。

71.步骤s13,在蓝宝石衬底上蒸镀金属层。

72.步骤s14,将所述蓝宝石衬底带有所述金属层的一侧贴合于所述薄膜层上。

73.步骤s15,去除所述gaas衬底、所述buffer层与所述gainp截止层,使所述n-gaas层裸露。

74.其中,通过湿法溶液去除gaas衬底、buffer层与gainp截止层,裸露出n-gaas层4。

75.步骤s16,从所述n-gaas层端进行刻蚀,蚀刻至所述p-gap光窗口层。

76.具体的,从n-gaas层4端开始,通过图形光刻和icp刻蚀,将外延层蚀刻至mqw层6下的p-gap光窗口层8。

77.步骤s17,在所述p-gap光窗口层制作p电极,在所述n-gaas层上制作n电极,并分别形成欧姆接触。

78.需要说明的是,当在p-gap光窗口层8制作p电极后,需先经退火形成欧姆接触,再在n-gaas层4上制作n电极,同样进行退火处理,形成欧姆接触。

79.步骤s18,整体沉积钝化保护层。

80.具体的,在进行下一步工艺前需要对整体沉积一层钝化保护层,示例而非限定,在本实施例一些较佳实施例当中,钝化保护层的材质可为二氧化硅、氮化硅、或氧化硅氧化钛交错生长的薄膜。

81.步骤s19,将所述p电极、所述n电极上的所述钝化保护层蚀刻出孔洞。

82.在本实施例当中,通过图形光刻和icp刻蚀,在p电极、n电极上将钝化层蚀刻出孔洞。

83.步骤s20,在所述p电极、所述n电极上方的所述孔洞内填充焊盘电极。

84.具体的,通过图形光刻和蒸镀,在p电极、n电极上方的钝化层孔洞内填充焊盘电极,该焊盘电极用于与外部电源连接。

85.实施例四

86.本实施例当中,在gaas衬底上生长外延层,通过eb电子束蒸发的方式蒸镀ito薄膜,其中,ito薄膜的蒸镀条件为腔体温度设定270℃,镀率0.4a/s,真空度4e-6torr,冷蒸。当ito薄膜蒸镀完成后,再在ito薄膜上蒸镀金属薄膜,依次蒸镀ni层、cu层和ag层,其中,ni镀率为0.5a/s,厚度为13.5a,cu镀率为1a/s,厚度为28.5a,ag镀率为1a/s,厚度为54a。当金

属薄膜蒸镀完成后,再在蓝宝石衬底上采用eb电子束蒸发的方式蒸镀ag层,冷蒸,其中,ag镀率为1a/s,厚度为54a,最终芯片键合良率可达98%。

87.实施例五

88.本实施例当中,在gaas衬底上生长外延层,通过eb电子束蒸发的方式蒸镀ito薄膜,其中,ito薄膜的蒸镀条件为腔体温度设定300℃,镀率0.8a/s,真空度4e-6torr,冷蒸。当ito薄膜蒸镀完成后,再在ito薄膜上蒸镀金属薄膜,依次蒸镀ni层、cu层和ag层,其中,ni镀率为0.5a/s,厚度为11.7a,cu镀率为1a/s,厚度为24.7a,ag镀率为1a/s,厚度为41.8a。当金属薄膜蒸镀完成后,再在蓝宝石衬底上采用eb电子束蒸发的方式蒸镀ag层,冷蒸,其中,ag镀率为1a/s,厚度为41.8a,最终芯片键合良率可达97%。

89.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1